# **CRT Display Video Output Amplifier**

#### **Features**

- · Active load circuits

- Wide bandwidth and high output voltage. Optimal for use in  $f_H$  (horizontal deflection frequency) = 90 kHz class ultrahigh precision monitors.

- Single 15-pin SIP molded package houses three channels.

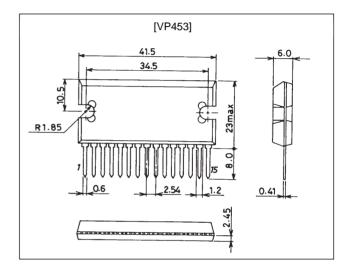

# **Package Dimensions**

unit: mm

#### 2127A

# **Specifications**

### Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter                    | Symbol              | Conditions                           | Ratings     | Unit |

|------------------------------|---------------------|--------------------------------------|-------------|------|

| Maximum supply voltage       | V <sub>CC</sub> max |                                      | 90          | V    |

| Allowable power dissipation  | Pd max              | With an ideal heat sink at Ta = 25°C | 25          | W    |

| Maximum junction temperature | Tj max              |                                      | 150         | °C   |

| Maximum case temperature     | Tc max              |                                      | 100         | °C   |

| Storage temperature          | Tstg                |                                      | -20 to +110 | °C   |

#### Operating Conditions at $Ta = 25^{\circ}C$

| Parameter                  | Symbol          | Conditions | Ratings | Unit |

|----------------------------|-----------------|------------|---------|------|

| Recommended supply voltage | V <sub>CC</sub> |            | 80      | V    |

#### Electrical Characteristics at Ta = 25°C (For a single channel, with Rin = 560 $\Omega$ , Rip = 22 $\Omega$ , Cip = 47 pF)

| Parameter                         | Symbol              | Conditions                                                                                                                                              | Ratings |     |     | Unit   |

|-----------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|-----|--------|

| Farameter                         | Symbol              | Conditions                                                                                                                                              | min     | typ | max | Offic  |

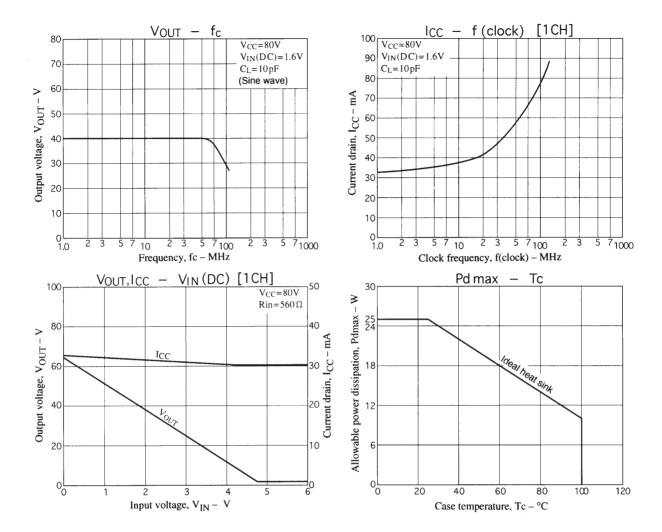

| Clock frequency bandwidth (-3 dB) | f (clock)           | V <sub>CC</sub> = 80 V, C <sub>L</sub> = 10 pF                                                                                                          |         | 190 |     | MHz    |

| Frequency bandwidth (-3 dB)       | f <sub>c</sub>      | $V_{IN}$ (DC) = 1.6 V, $V_{OUT}$ (p-p) = 40 V                                                                                                           |         | 90  |     | MHz    |

| Pulse response                    | t <sub>r</sub>      | V <sub>CC</sub> = 80 V, C <sub>L</sub> = 10 pF                                                                                                          |         | 4.0 |     | ns     |

|                                   | t <sub>f</sub>      | $V_{IN}$ (DC) = 1.6 V, $V_{OUT}$ (p-p) = 40 V                                                                                                           |         | 3.6 |     | ns     |

| Voltage gain                      | VG (DC)             |                                                                                                                                                         | 11      | 13  | 15  | Double |

| Current drain                     | I <sub>CC</sub> (1) | $V_{CC} = 80 \text{ V}, V_{IN} \text{ (DC)} = 1.6 \text{ V}, f = 10 \text{ MHz}$<br>clock, $C_L = 10 \text{ pF}, V_{OUT} \text{ (p-p)} = 40 \text{ V}$  |         | 35  |     | mA     |

|                                   | I <sub>CC</sub> (2) | $V_{CC} = 80 \text{ V}, V_{IN} \text{ (DC)} = 1.6 \text{ V}, f = 100 \text{ MHz}$<br>clock, $C_L = 10 \text{ pF}, V_{OUT} \text{ (p-p)} = 40 \text{ V}$ |         | 77  |     | mA     |

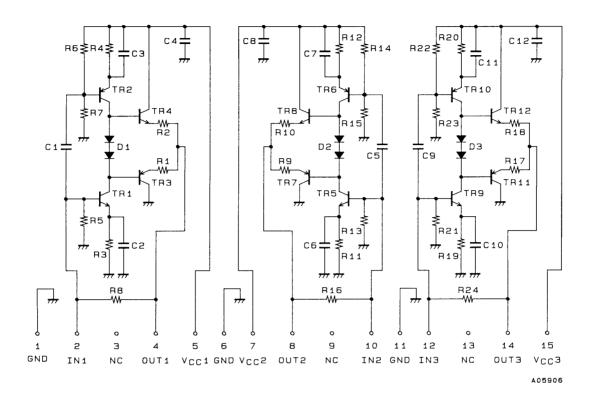

## **Internal Equivalent Circuit**

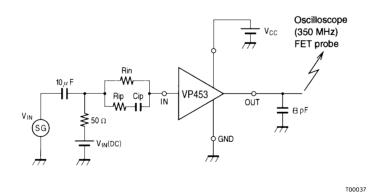

### Test Circuit (for a single channel)

#### **Thermal Design**

Thermal design requires that the two conditions T<sub>1</sub> (max)  $\leq$  150°C and Tc  $\leq$  100°C be met.

(a) Concerning Tj (max), the chip temperature Tj for each transistor is given by equation (1).

$$Tj = (Tri) = \theta j - c (Tri) \times P_C (Tri) + \Delta Tc + Ta (^{\circ}C) \dots (1)$$

$\theta$ j–c (Tri): The thermal resistance of each transistor chip itself

P<sub>C</sub> (Tri): The collector loss for each transistor

$\Delta$ Tc: Increase in the case temperature

Ta: Ambient temperature

$\theta$ j–c (Tri) for each chip will be:

$$\theta_{j-c}$$

(Tr1) to (Tr4) = 35°C/W .....(2)

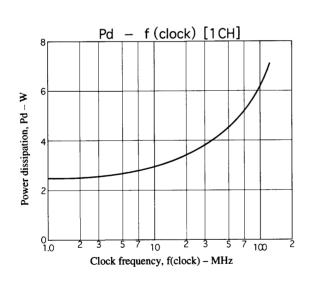

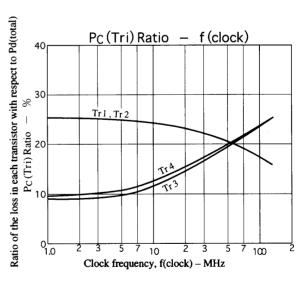

The loss in transistors in a video pack varies with frequency. The loss increases with the frequency.

For example, if the maximum frequency will be 120 MHz (clock), then the transistors with the largest losses will be transistors 3 and 4 in the emitter-follower (EF) stage. From the Pd - f (clock) figure, we see that that loss will be 25% of the total for a single channel. That is:

$$P_C$$

(EF stage)  $_{f = 120 \text{ MHz}} = Pd$  (1ch)  $_{f = 120 \text{ MHz}} \times 0.25 \text{ [W]}$ .....(3)

The thermal design must assure that Tj does not exceed 150°C at this time.

(b) Concerning Tc(max), the relationship between  $\theta$ h and  $\Delta$ Tc is:

$$\Delta Tc = Pd (total) \times \theta h$$

.....(4)

Taking the increase due to Ta into account, the condition the thermal design must meet becomes  $Tc = \Delta Tc + Ta < 100^{\circ}C$ .

Next we design thermal conditions for the VP453 that meet the conditions in sections (a) and (b) above.

#### Sample Thermal Design for the VP453

Conditions: For an  $f_H = 95$  kHz class monitor,  $f_V = 120$  MHz (clock).

$$V_{CC} = 80 \text{ V}, V_{OUT} = 40 \text{ Vp-p } (C_L = 10 \text{ pF})$$

Here we consider the case where such a monitor is to be operated at ambient temperatures up to  $Ta = 60^{\circ}C$  and at a maximum frequency of f = 100 MHz (clock).

As mentioned previously, the chips with the maximum loss will be transistors 3 and 4 in the emitter-follower stage. Equation (5) follows from deriving that value from the figure below and equation (3).

$$P_C (Tr3, 4)_{f = 120 \text{ MHz}} = 6.9 \times 0.25 \approx 1.72 \text{ [W]}...$$

(5)

However, the actual usage conditions include a blanking period. If we calculate the power during this period approximately at a 1-MHz power ratio, from Pd - f(clock) and  $P_C$  (Tri)Ratio - f (clock) figures, we see that  $P_C$  (BLK) for transistors 3 and 4 will be:

$$P_C$$

BLK (Tr3, 4) = 2.6 × 0.08 = 0.21 [W].....(6)

If the blanking period is 20% of the total, from the data of equation (5) and formula (6) we see that the loss in transistors 3 and 4 will be:

$$P_{C}\left(Tr3,\,4\right) = P_{C}\left(Tr3,\,4\right)_{\,f\,=\,120\,MHz} \times 0.8 + P_{C}BLK\left(Tr3,\,4\right) \times 0.2 \approx 1.42\,\left[W\right]...(7)$$

Next, applying the value of  $\theta j$ –c to equation (7), shows  $\Delta T j$  to be:

$$\Delta Tj = 1.42 \times 35 \approx 50$$

[°C]

Since  $\Delta Tj \leq 50^{\circ}C$ , it suffices to only consider the  $Tc \leq 100^{\circ}C$  condition in the thermal design. That is, in the thermal design we design  $\theta h$  so that Tc will be under  $100^{\circ}C$  when Pd (total) = Pd (1ch)  $\times$  3 for the time when all three channels are operating at their maximum levels.

$$\Delta Tc$$

will be:  $\Delta Tc = 100 - 60 = 40$ °C

$$\theta h = \Delta Tc \div Pd \text{ (total)} = 40 \div \{(6.9 \times 0.8 + 3.5 \times 0.2) \times 3\} = 2.1$$

Thus:

$$\theta h = 2.1^{\circ}C/W$$

In actual use, due to the actual ambient temperature, the operating conditions, and other factors, it will be possible to use a heat sink smaller than the one required by the above design. Users should design an optimal heat sink using the data presented above and their actual conditions.

| V <sub>CC</sub> (V) | V <sub>OUT</sub> (V) | V <sub>O</sub> (center) |

|---------------------|----------------------|-------------------------|

| 80                  | 40                   | 40                      |

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of January, 1997. Specifications and information herein are subject to change without notice.