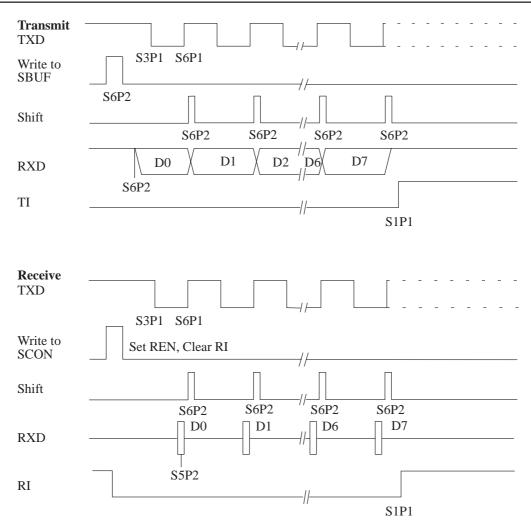

# **Extended 8–bit Microcontroller** with Serial Communication Interfaces

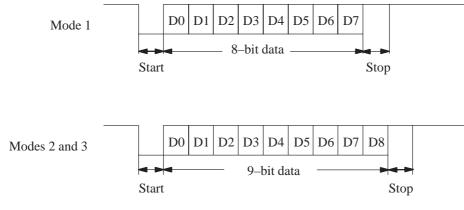

Design Guide – October 1998

# **Design Guide Information**

TEMIC reserves the right to make changes in the products or specifications contained in this document in order to improve design or performance and to supply the best possible products. TEMIC also assumes no responsibility for the use of any circuits described herein, conveys no license under any patents or other rights, and makes no representations that the circuits are free from patent infringement. Applications for any integrated circuits contained in this publication are for illustration purposes only and TEMIC makes no representation or warranty that such applications will be suitable for the use specified without further testing or modification. Reproduction of any portion hereof without the prior written consent of TEMIC is prohibited.

# **On line information**

World Wide Web: http://www.temic-semi.de

# **Factory Technical Support**

| Email Products: | c251@temic.fr      |

|-----------------|--------------------|

| Email Tools:    | x51_tools@temic.fr |

### Publisher

MHS S.A. La Chantrerie – Route de Gachet, BP 70602 44306 NANTES Cedex 03 France Phone: 33 2 40 18 18 18 Fax: +33 2 40 18 19 60

Copyright TEMIC Semiconductors 1997. Copyright INTEL Corporation 1994. Portions reprinted by permission of INTEL Corporation. "I<sup>2</sup>C" is a trademark of PHILIPS. "SPI" is a trademark of MOTOROLA. "µWire" is a trademark of NATIONAL Semiconductor.

Purchase of TEMIC  $I^2C$  components conveys a license under the Philips  $I^2C$  Patent Rights to use these components in an  $I^2C$  system, provided that the system conforms to the  $I^2C$  Standard Specification as defined by Philips.

# Section 1

# Introduction

# **Table of Contents**

| 1. Guide to this Manual                     | I–1 |

|---------------------------------------------|-----|

| 1.1. Introduction                           | I–1 |

| 1.2. Manual Contents                        | I–1 |

| 1.3. Notational Conventions and Terminology | I–1 |

| 1.4. Related Documents and tools            | I–2 |

| 2. Product Overview                         | I–4 |

| 2.1. Typical Applications                   | I–4 |

| 2.2. Features                               | I–5 |

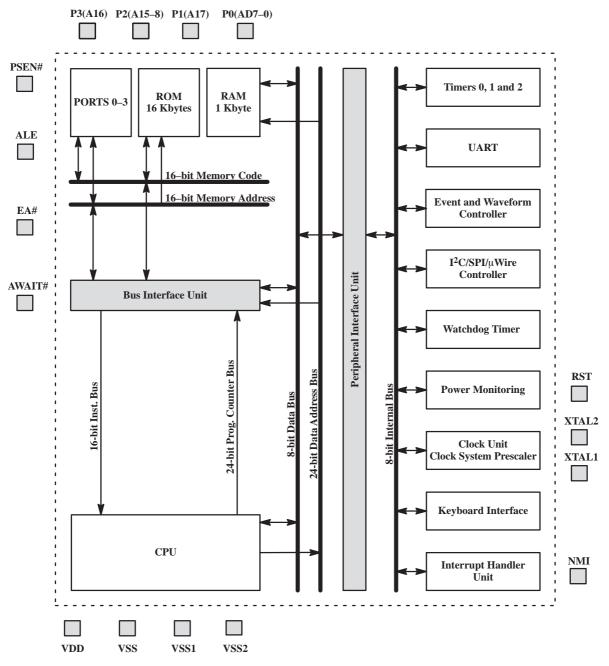

| 2.3. Block Diagram                          | I–6 |

# 1. Guide to this Manual

# **1.1. Introduction**

This manual describes the TSC80251G1D embedded microcontroller, which is a member of the TEMIC TSC80251 microcontroller family. This manual is intended for use by both software and hardware designers familiar with the principles of microcontrollers.

# **1.2. Manual Contents**

This manual contains 2 sections and 2 appendices, the paragraphs hereafter summarize the content of these sections and appendices.

# 1.2.1. "Introduction" Section

### Chapter 1 (this chapter), "Guide to this manual"

Provides an overview of the manual. It summarizes the contents of the remaining chapters. The remainder of this chapter describes notational conventions and terminology used throughout the manual and provides references to related documentation.

#### Chapter 2, "Product Overview"

Summarizes the features of the TEMIC TSC80251G1D microcontroller devices.

### 1.2.2. "Design Information" Section

### Chapter 1, "Address Spaces"

Describes the memory address space and the special function register (SFR) space of the TSC80251G1D microcontroller. It also provides a map of the SFR space showing the location of the SFRs and their reset values.

### Chapter 2, "Device Configuration"

Describes microcontroller features that are configured at device reset, including the external memory interface (the number of external address bits, the number of wait states, memory regions for asserting RD#, WR#, and PSEN#, page mode), binary/source opcodes, interrupt mode, and the mapping of a portion of on–chip code memory to data memory. It describes the configuration bytes and how to program them for the desired configuration. It also describes how internal memory space maps into external memory.

### Chapter 3, "External Memory Interface"

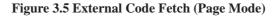

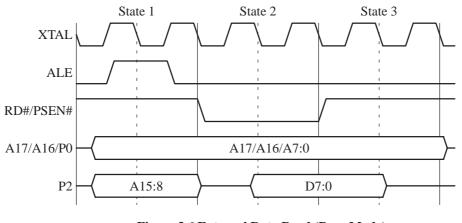

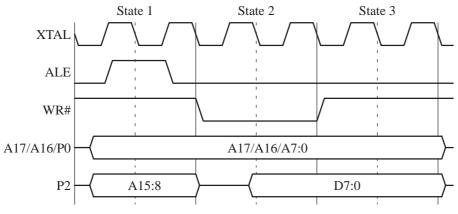

Describes the external memory signals and bus cycles. It provides waveform diagrams for the bus cycles, bus cycles with wait states, and the configuration byte bus cycles.

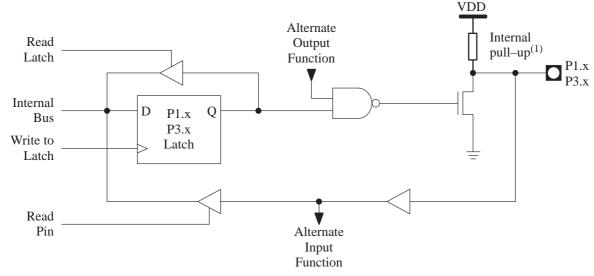

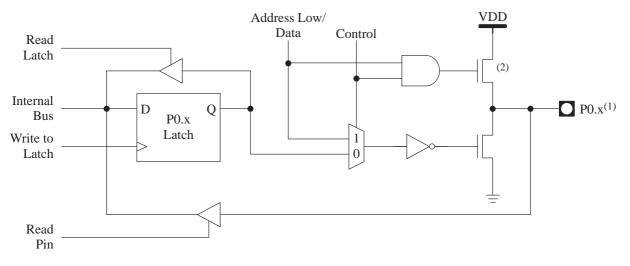

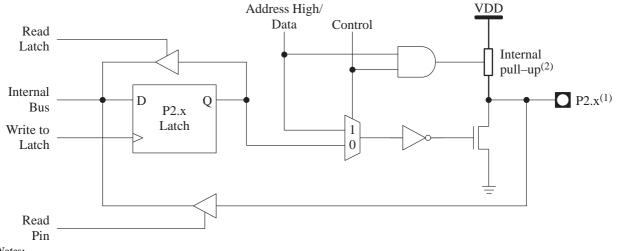

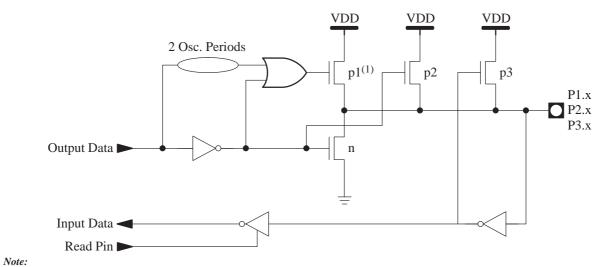

### Chapter 4, "Input/Output Ports"

Describes the four 8-bit I/O ports (ports 0 to 3) and discusses their configuration for general-purpose I/O, external memory accesses (ports 0, 2), and alternative special functions.

#### Chapter 5, "Timer/Counters"

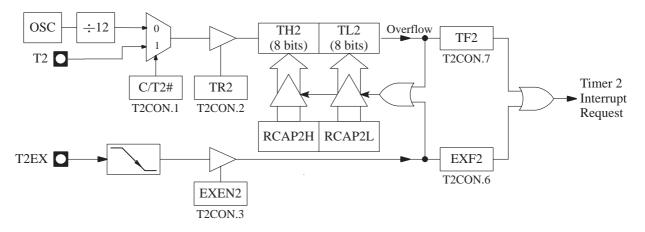

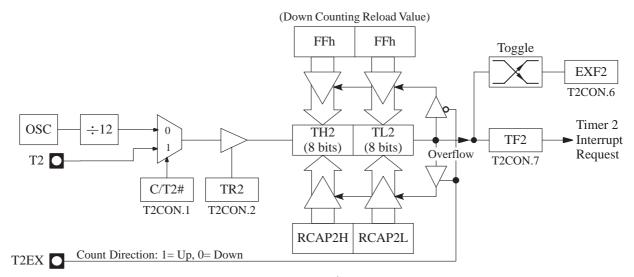

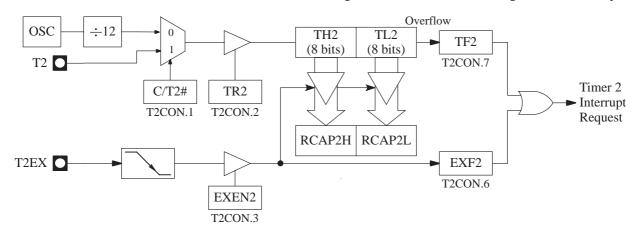

Describes the three on-chip timer/counters and discusses their application.

#### Chapter 6, "Serial I/O Port"

Describes the full–duplex serial I/O port and explains how to program it to communicate with external peripherals. This chapter also discusses baud rate generation (through timer 1, timer 2 and specific baud rate generator), framing error detection, multiprocessor communications, and automatic address recognition.

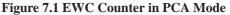

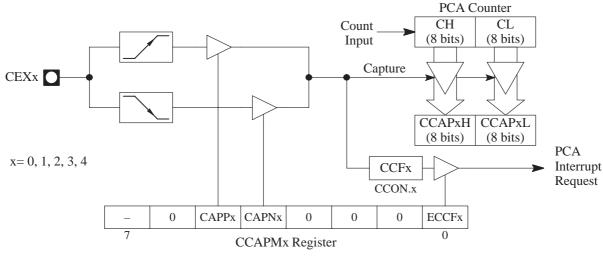

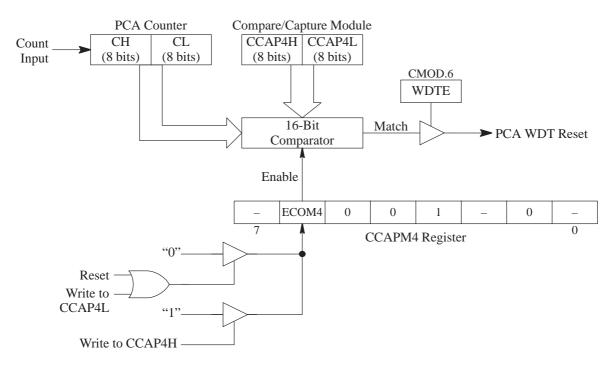

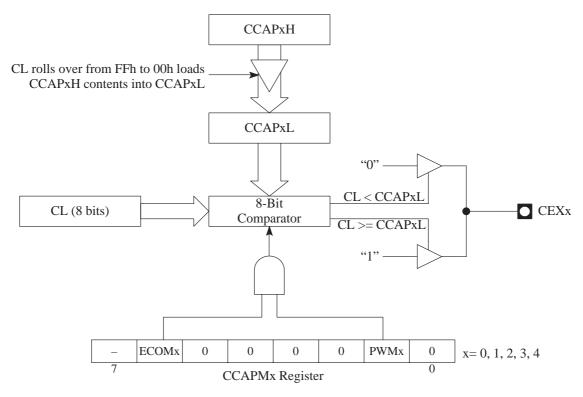

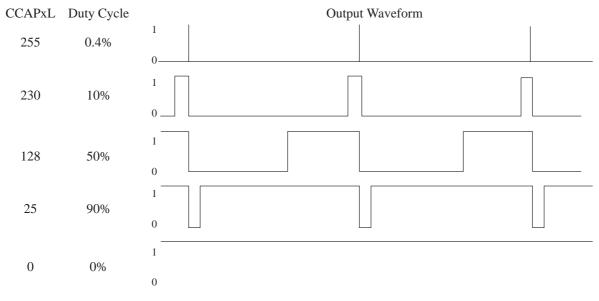

#### Chapter 7, "Event and Waveform Controller"

Describes the PCA on-chip peripheral and explains how to configure it for general-purpose applications (timers and counters) and special applications (programmable WDT and pulse-width modulator).

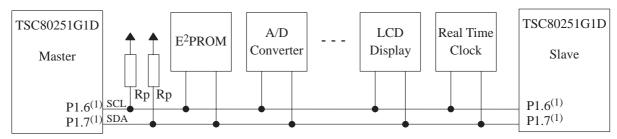

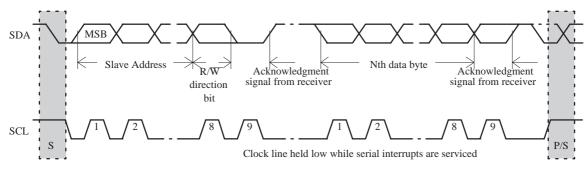

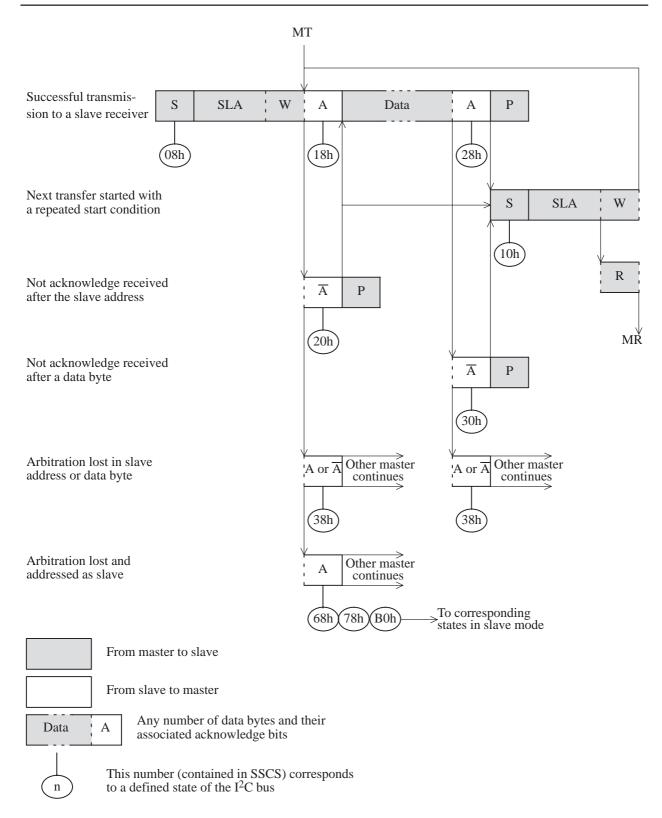

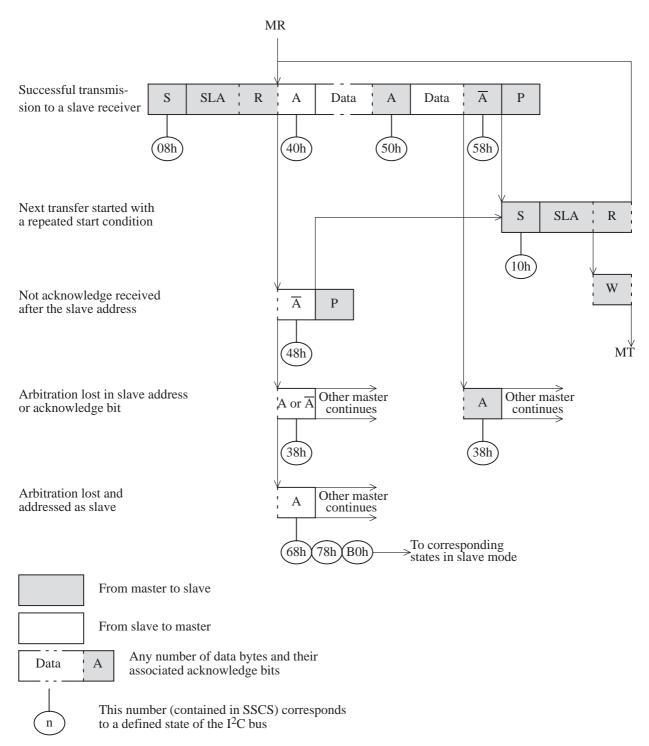

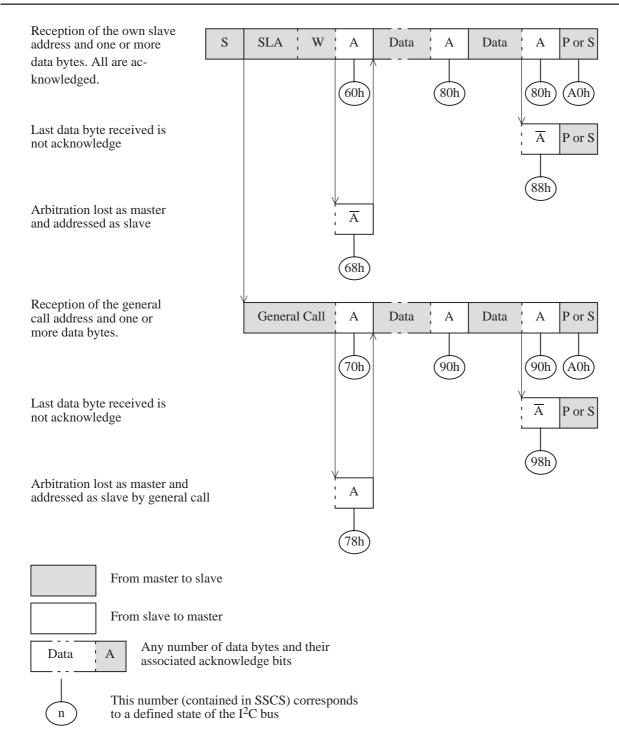

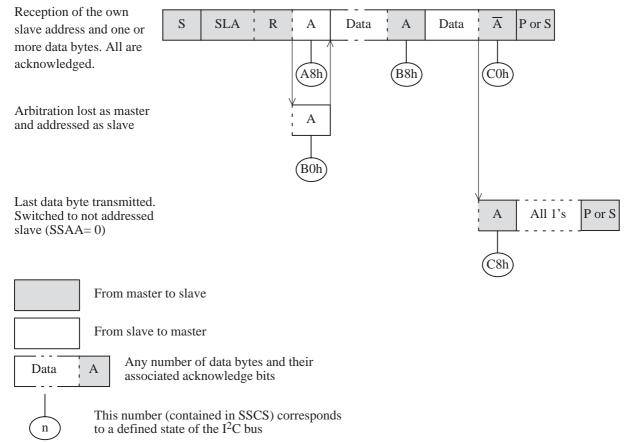

### Chapter 8, "SSLC/Inter–Integrated Circuit Interface (I<sup>2</sup>C)"

Describes the synchronous serial link controller when configured in I<sup>2</sup>C mode.

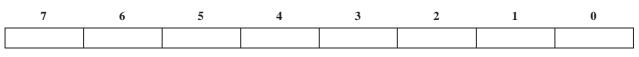

#### Chapter 9, "SSLC/Synchronous Peripheral Interface (µWire/SPI)"

Describes the synchronous serial link controller when configured in  $\mu$ Wire/SPI mode.

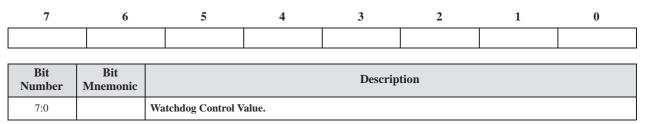

#### Chapter 10, "WatchDog Timer"

Describes the hardware watchdog timer (WDT). This chapter also provides instructions for using the WDT and describes the operation of the WDT during the idle and power-down modes.

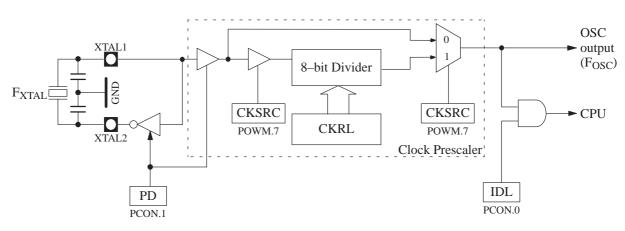

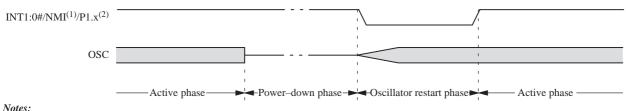

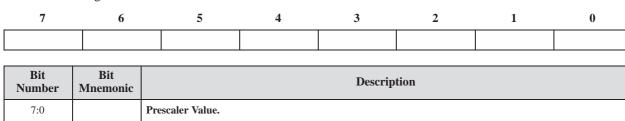

### Chapter 11, "Power Monitoring and Management"

Describes the TSC80251G1D power monitoring and management circuitry which provides a power–on reset, a power–fail reset, a power off flag, a clock prescaler, an idle mode, and a power–down mode.

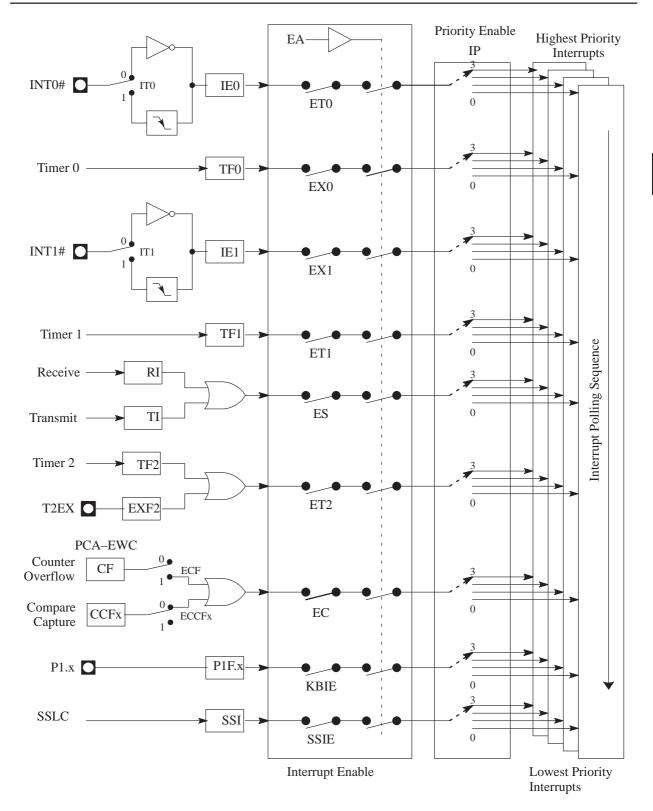

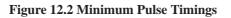

#### Chapter 12, "Interrupt System"

Describes the TSC80251G1D interrupt circuitry which provides a TRAP instruction interrupt, a non maskable external interrupt, nine maskable interrupts: two external interrupts, three timer interrupts, an EWC–PCA interrupt, a serial port interrupt, a synchronous serial interface interrupt, and a keyboard interrupt. This chapter also discusses the interrupt priority scheme, the external interrupt inputs, the NMI input, and the keyboard interface.

### 1.2.3. Appendices

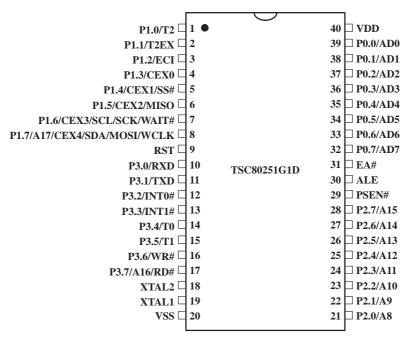

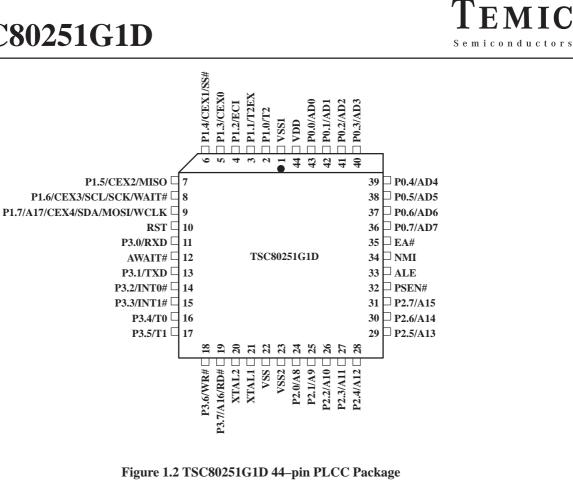

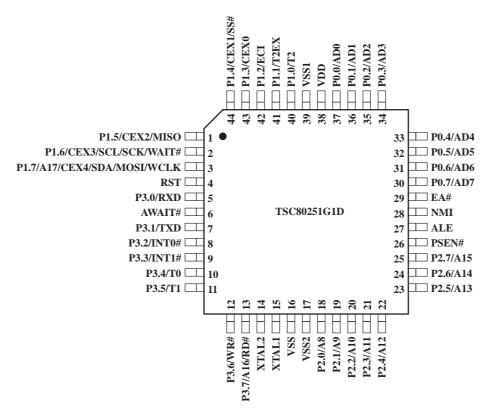

#### Appendix A, "Signal Descriptions"

Provides device pinouts and describes the function(s) of each pin. Descriptions are listed alphabetically by signal name.

#### Appendix B, "Registers"

Accumulates, for convenient reference, copies of the register definition figures that appear throughout the manual.

# 1.3. Notational Conventions and Terminology

The following notations and terminology are used in this manual.

| #                   | The pound symbol (#) appended to a signal name means that the signal is active low.                                                                                                                                                                                                                                                                                                                  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XXXX                | Uppercase X (no italics) represents an unknown value or a "don't care" state or condition. The value may be either binary or hexadecimal, depending on the context. For example, 2XAFh (hex) indicates that bits 11:8 are unknown; 10XX in binary context indicates that the two LSBs are unknown.                                                                                                   |

| Assert and Deassert | The terms assert and deassert refer to the act of making a signal active (enabled) and inactive (disabled), respectively. The active polarity (high/low) is defined by the signal name. Active–low signals are designated by a pound symbol (#) suffix; active–high signals have no suffix. To assert RD# is to drive it low; to assert ALE is to drive it high; to deassert RD# is to drive it low. |

| Logic 0 (Low)       | An input voltage level equal to or less than the maximum value of $V_{IL}$ or an output voltage level equal to or less than the maximum value of $V_{OL}$ . See datasheet for values.                                                                                                                                                                                                                |

| Logic 1 (High)      | An input voltage level equal to or greater than the minimum value of $V_{IH}$ or an output voltage level equal to or greater than the minimum value of $V_{OH}$ . See datasheet for values.                                                                                                                                                                                                          |

| Numbers             | Hexadecimal numbers are represented by a string of hexadecimal digits followed by the char-<br>acter h. Binary numbers are represented by a string of binary digits followed by the character<br>b. Decimal numbers are represented by their customary notations. That is, 255 is a decimal<br>number, FFh is an hexadecimal number and 1111 1111b is a binary number.                               |

| Register Bits       | Bit locations are indexed by 7:0 for byte registers where bit 0 is the least–significant bit and 7 most significant bit. An individual bit is represented by the register name, followed by a period and the bit number. For example, PCON.4 is bit 4 of the power control register. In some discussions, bit names are used. For example, the name of PCON.4 is POF, the power–off flag.            |

| Register Names      | Register names are shown in upper case. For example, PCON is the power control register. If a register name contains a lowercase character, it represents more than one register. For example, CCAPMx represents the five registers: CCAPM0 through CCAPM4.                                                                                                                                          |

EMIC

Semiconductors

| Reserved Bits    | Some registers contain reserved bits. These bits are not used in this device, but they may be used in future implementations. In most cases value read from a reserved bit is indeterminate. Do not write a "1" to a reserved bit after reading it to "0".                                                                                      |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Set and Clear    | The terms set and clear refer to the value of a bit or the act of giving it a value. If a bit is set, its value is "1"; setting a bit gives it a "1" value. If a bit is clear, its value is "0"; clearing a bit gives it a "0" value.                                                                                                           |  |  |  |

| Signal Names     | Signal names are shown in upper case. When several signals share a common name, an individual signal is represented by the signal name followed by a number. Port pins are represented by the port abbreviation, a period, and the pin number (e.g., P0.0, P0.1). A pound symbol (#) appended to a signal name identifies an active–low signal. |  |  |  |

| Units of Measure | The following abbreviations are used to represent units of measure:KbitkilobitsKbytekilobytesMbytemegabytesMHzmegahertzmsmillisecondsnsnanoseconds                                                                                                                                                                                              |  |  |  |

# **1.4. Related Documents and tools**

### 1.4.1. Datasheet

The "TSC80251G1D Datasheet" contains quick reference to the product, it also includes all the DC and AC parameters, the packages information, and the ordering information.

### **1.4.2.** Programmer's Guide

The "TSC80251 Extended 8-bit Microcontrollers Programmer's Guide" contains all information for the programmer (architecture, Memory Mapping and instruction set).

### 1.4.3. Starter Kit

TEMIC proposes a starter kit for the TSC80251G1D to be evaluated by the designer. The starter kit content is:

- C-Compiler (limited to 2 Kbytes of code)

- Assembler

- Linker

- TSC80251G1 Simulator

- TSC80C251G1 Evaluation Board with ROM–Monitor

### **1.4.4. Development Tools**

Up to date information concerning development tools for TEMIC TSC80251 devices is available on the TEMIC web site.

# 1.4.5. World Wide Web

TEMIC offers a variety of technical information through the Word Wide Web: http://www.temic-semi.de

### **1.4.6.** Application support

TEMIC offers through E-mail a technical hotline dedicated to the TSC80251 microcontroller family: C251@temic.fr. TEMIC also offers through E-mail a technical hotline dedicated to the development tools: x51\_tools@temic.fr.

# 2. Product Overview

The TSC80251G1D products are derivatives of the TEMIC Microcontroller family based on the extended 8–bit C251 Architecture. This family of products is tailored to 8–bit microcontroller applications requiring an increased instruction throughput, a reduced operating frequency or a larger addressable memory space. The architecture can provide a significant code size reduction when compiling C programs while fully preserving the legacy of C51 assembly routines.

The TSC80251G1D derivatives are pin–out and software compatible with standard 80C51/Fx/Rx with extended on–chip data memory (1 Kbyte RAM) and up to 256 Kbytes of external code and data. Additionally, the TSC83251G1D provides on–chip code memory (16 Kbytes ROM).

They provide transparent enhancements to Intel's 8xC251Sx family with an additional Synchronous Serial Link Controller (SSLC supporting I<sup>2</sup>C,  $\mu$ Wire and SPI protocols), a Keyboard interrupt interface and Power Monitoring and Management features.

More information on the TSC80251 architecture is provided in the "TSC80251 Extended 8-bit Microcontroller Programmer's Guide".

Pinouts and signals description are provided in Appendix A, "Signals Description".

# **2.1. Typical Applications**

- ISDN terminals

- High–Speed modems

- PABX (SOHO)

- Networking

- Line cards

- Computer peripherals

- Printers

- Plotters

- Scanners

- Banking machines

- Barcode readers

- Smart cards readers

- High-end digital monitors

- High-end joysticks

# 2.2. Features

- Pin–Out and software compatibility with standard 80C51 products and 80C51FA/FB/RA/RB

- Plug-in replacement of Intel's 80C251Sx

- C251 core: Intel's MCS<sup>®</sup>251 D-step compliant

- 40–byte Register File

- Registers Accessible as Bytes, Words or Dwords

- Single–state Pipeline with 16–bit Internal Code Fetch

- Enriched C51 Instruction Set

- 16-bit and 32-bit ALU

- Compare and Conditional Jump Instructions

- Expanded Set of Move Instructions

- Linear Addressing

- 1 Kbyte of on-chip RAM

- External memory space (Code/Data) programmable from 64 Kbytes to 256 Kbytes

- TSC83251G1D: 16 Kbytes of on-chip masked ROM (Engineering and fast production with TSC87251G1A OTP/EPROM version)

- TSC80251G1D: ROMless version

- Four 8–bit parallel I/O Ports (Ports 0, 1, 2 and 3 of the standard 80C51)

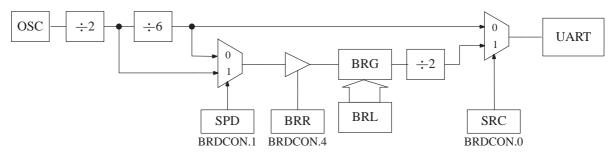

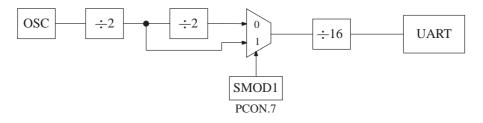

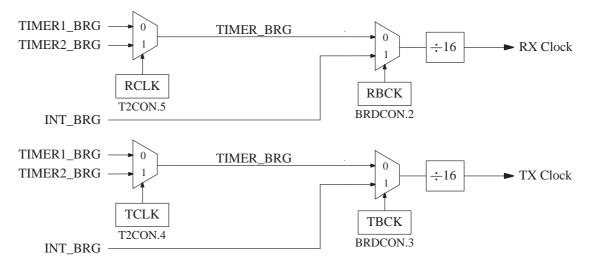

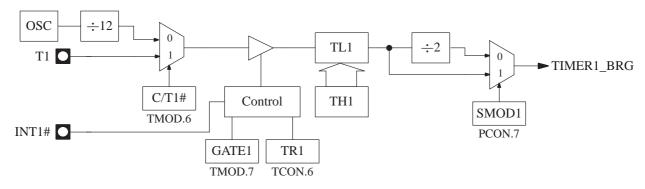

- Serial I/O Port: full duplex UART (80C51 compatible) with independent Baud Rate Generator

- SSLC: Synchronous Serial Link Controller

- I<sup>2</sup>C multi–master protocol

- µWire and SPI master and slave protocols

- Three 16–bit Timers/Counters (Timers 0, 1 and 2 of the standard 80C51)

- EWC: Event and Waveform Controller

- Compatible with Intel's Programmable Counter Array (PCA)

- Common 16-bit Timer/Counter reference with four possible clock sources (Fosc/4, Fosc/12, Timer 1 and external input)

- Five modules, each with four programmable modes:

- 16-bit software Timer/Counter

- 16-bit Timer/Counter Capture Input and software pulse measurement

- High-speed output and 16-bit software Pulse Width Modulation (PWM)

- 8-bit hardware PWM without overhead

- 16–bit Watchdog Timer/Counter capability

- Secure 14-bit Hardware Watchdog Timer

- Power Monitoring and Management

- Power–Fail reset

- Power–On reset (integrated on the chip)

- Power–Off flag (cold and warm resets)

- Software programmable system clock

- Idle and Power–Down modes

- Keyboard interrupt interface on Port 1

- Non Maskable Interrupt input (NMI)

- Real-time Wait states inputs (WAIT#/AWAIT#)

- ONCE mode and full speed Real-Time In-Circuit Emulation support (Third Party Vendors)

# 2.3. Block Diagram

# Section 2

# **Design Information**

# **Table of Contents**

| 1. Address Spaces                                      |       |

|--------------------------------------------------------|-------|

| 1.1. Introduction                                      |       |

| 1.2. TSC80251G1D Memory Space                          |       |

| 1.3. Special Function Registers                        |       |

| 2. Device Configuration                                |       |

| 2.1. Configuration Overview                            |       |

| 2.2. Device Configuration                              |       |

| 2.3. The Configuration Bits                            |       |

| 2.4. Configuring the External Memory Interface         |       |

| 2.5. Registers                                         | II–13 |

| 3. External Memory Interface                           | II–15 |

| 3.1. Introduction                                      | II–15 |

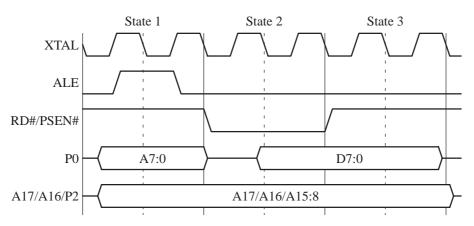

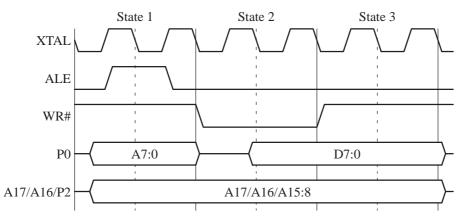

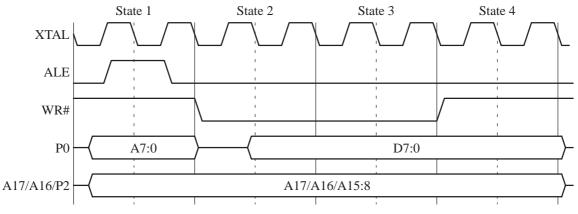

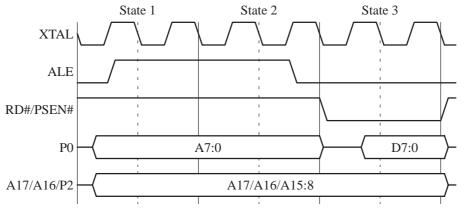

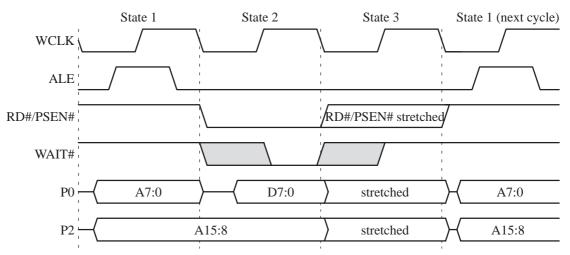

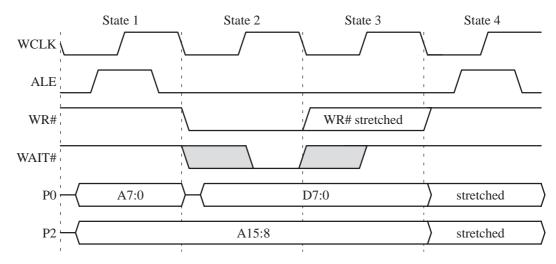

| 3.2. External Bus Cycles                               | II–17 |

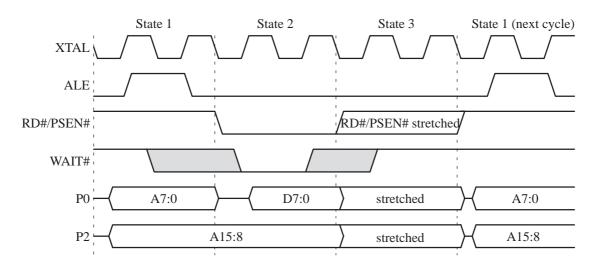

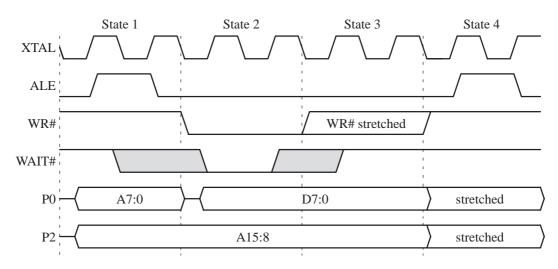

| 3.3. Wait States                                       | II–20 |

| 3.4. External Bus Cycles with Configurable Wait States | II–20 |

| 3.5. External Bus Cycles with Real–Time Wait States    | II–21 |

| 3.6. Configuration Byte Bus Cycles                     | II–24 |

| 3.7. Port 0 and Port 2 Status                          | II–24 |

| 3.8. Registers                                         | II–25 |

| 4. Input/Output Ports                                  | II–26 |

| 4.1. Introduction                                      | II–26 |

| 4.2. I/O Configurations                                | II–28 |

| 4.3. Port 1 and Port 3                                 | II–28 |

| 4.4. Port 0 and Port 2                                 | II–28 |

| 4.5. Read–Modify–Write Instructions                    | II–29 |

| 4.6. Quasi–Bidirectional Port Operation                | II–30 |

| 4.7. Port Loading                                      | II–31 |

| 5. Timers/Counters                                     | II–32 |

| 5.1. Introduction                                      | II–32 |

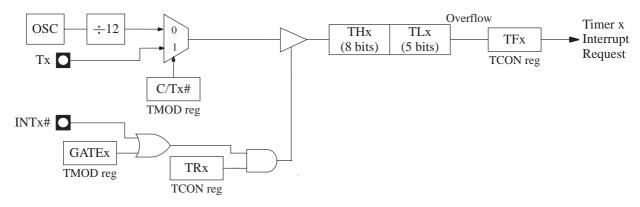

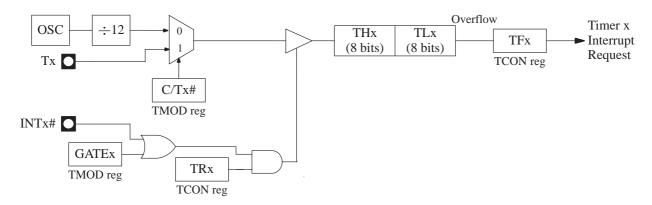

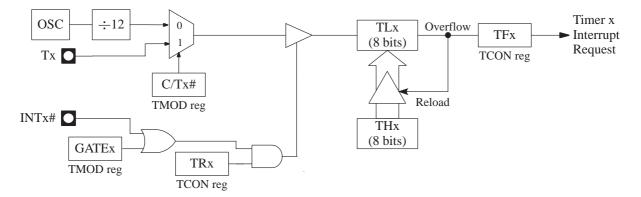

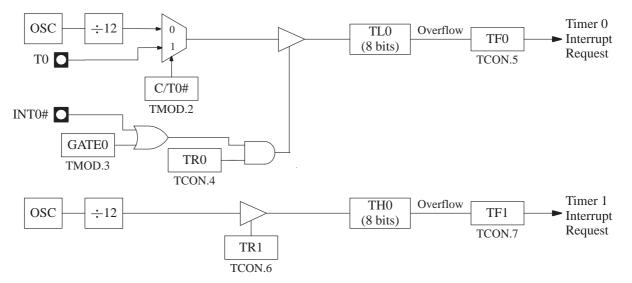

| 5.2. Timer/Counter Operations                          | II–32 |

| 5.3. Timer 0                                           | II–33 |

| 5.4. Timer 1                                           |       |

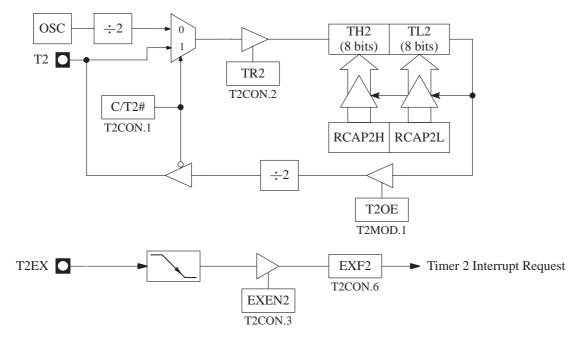

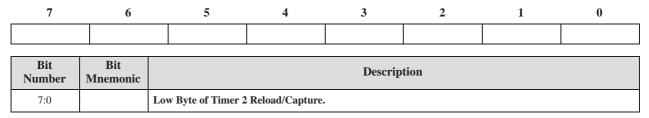

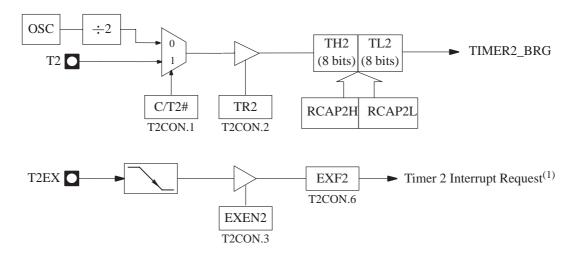

| 5.5. Timer 2                                           | II–36 |

| 5.6. Registers                                         | II–40 |

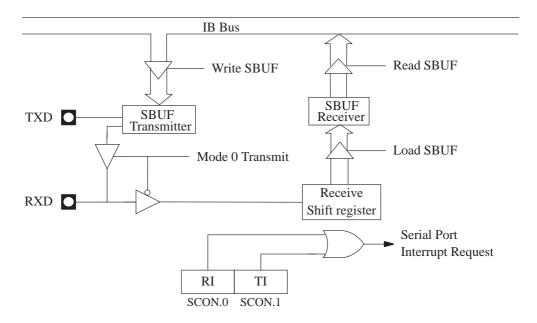

| 6. Serial I/O Port                                     |       |

| 6.1. Introduction                                      | II–46 |

|                                                        |       |

| 6.2. Modes of Operation                              |        |

|------------------------------------------------------|--------|

| 6.3. Framing Bit Error Detection (Modes 1, 2 and 3)  |        |

| 6.4. Overrun Error Detection (Modes 1, 2 and 3)      |        |

| 6.5. Multiprocessor Communication (Modes 2 and 3)    | II–50  |

| 6.6. Automatic Address Recognition                   | II–51  |

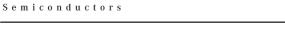

| 6.7. Baud Rates                                      | II–52  |

| 6.8. Registers                                       | II–60  |

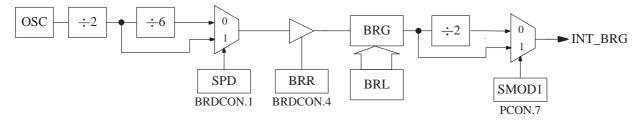

| 7. Event and Waveform Controller                     | II–63  |

| 7.1. Introduction                                    |        |

| 7.2. Description                                     |        |

| 7.3. Registers                                       | II–70  |

| 8. SSLC/Inter–Integrated Circuit (I2C) Interface     | II–75  |

| 8.1. Introduction                                    | II–75  |

| 8.2. Description                                     | II–75  |

| 8.3. Registers                                       | II–89  |

| 9. SSLC/Synchronous Peripheral Interface (mWire/SPI) | II–92  |

| 9.1. Introduction                                    | II–92  |

| 9.2. Description                                     |        |

| 9.3. Configuration                                   | II–96  |

| 9.4. Registers                                       | II–100 |

| 10. Hardware Watchdog Timer                          |        |

| 10.1. Introduction                                   | II–102 |

| 10.2. Description                                    | II–102 |

| 10.3. Using the Hardware WDT                         | II–103 |

| 10.4. Hardware WDT during Idle and Power–Down Modes  | II–103 |

| 10.5. Registers                                      | II–103 |

| 11. Power Monitoring and Management                  | II–104 |

| 11.1. Introduction                                   | II–104 |

| 11.2. Power–On Reset                                 | II–104 |

| 11.3. Power–Fail Detector                            | II–105 |

| 11.4. Power–Off Flag                                 | II–105 |

| 11.5. Clock Prescaler                                | II–105 |

| 11.6. Idle Mode                                      | II–106 |

| 11.7. Power–Down Mode                                | II–107 |

| 11.8. Registers                                      | II–109 |

| 12. Interrupt System                                 | II–111 |

| 12.1. Introduction                                   | II–111 |

| 12.2. Interrupt System Priorities                    | II–112 |

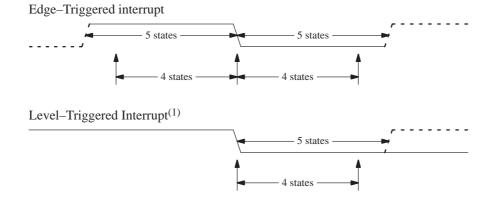

| 12.3. External Interrupts                            | II–114 |

| 12.4. Keyboard Interface                             | II–115 |

| 12.5. Registers                                      | II–116 |

# 1. Address Spaces

# **1.1. Introduction**

The TSC80251G1D derivatives have three address spaces: a memory space, a special function register (SFR) space and register file. This chapter describes the memory and SFR address spaces as they apply to TSC80251G1D. Register file information and address spaces comparison of the C251 Architecture versus the C51 Architecture are described in the TSC80251 Programmer's Guide.

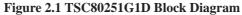

# 1.2. TSC80251G1D Memory Space

The usable memory of the TSC80251G1D consists of four 64 Kbytes regions: 00:, 01:, FE:, and FF:,. Code can execute from all four regions; code execution begins at FF:0000h. Regions 02:–FD: are reserved. Reading a location in the reserved area returns an unspecified value. Software must avoid writing to the reserved area to not spuriously write to the other existing regions.

All four regions of the memory space are available at the same time. The maximum number of external address lines is 18, which limits external memory to a maximum of four regions (256 Kbytes).

Notes:

1. Eight-byte configuration array (FF:FFF8h - FF:FFFFh).

2. Four banks of registers R0-R7 (32 BYTES, 00:0000h - 00:001Fh).

#### Figure 1.1 Memory Mapping in the TSC80251G1D Address Space

Figure 1.1 shows how on-chip RAM, on-chip ROM, and external memory are mapped in the TSC80251G1D address space. The first 32 bytes of on-chip RAM store banks 0–3 of the register file.

# 1.2.1. On-chip General-purpose Data RAM

On-chip RAM (1 Kbyte) is provided for general data storage (Figure 1.1). Instructions cannot execute from on-chip data RAM. The data is accessible by direct, indirect and displacement addressing. Locations 00:0020h–00:007Fh are also bit addressable.

# 1.2.2. On-chip Code Memory

The TSC80251G1D derivatives are available with 16 Kbytes of on-chip ROM (TSC83251G1D) or as well as without on-chip code memory (TSC80251G1D) The on-chip ROM is intended primarily for code storage, although its contents can also be read as data with the indirect and displacement addressing modes. Following a chip reset, program execution begins at FF:0000h.

A code fetch within the address range of the on-chip ROM accesses the on-chip ROM only if EA#= 1. For EA#= 0, a code fetch in this address range accesses external memory. The value of EA# is latched when the chip leaves the reset state. Code is fetched faster from on-chip code memory than from external memory. Table 1.1 lists the minimum times to fetch two bytes of code from on-chip memory and external memory.

### Table 1.1 Minimum Times to Fetch Two Bytes of Code

| Type of Code Memory             | State Times |

|---------------------------------|-------------|

| On-chip Code Memory             | 1           |

| External Memory (page mode)     | 2           |

| External Memory (non-page mode) | 4           |

Note:

If your program executes exclusively from on-chip ROM (not from external memory), beware of executing code from the upper eight bytes of the on-chip ROM (FF:3FF8h-FF:3FFFh). Because of its pipeline capability, the TSC80251G1D may attempt to prefetch code from external memory (at an address above FF:3FFFh) and thereby disrupt I/O ports 0 and 2. Fetching code constants from these eight bytes does not affect ports 0 and 2. If your program executes from both on-chip ROM and external memory, your code can be placed in the upper eight bytes of the on-chip ROM. As the TSC80251G1D fetches bytes above the top address in the on-chip ROM, the code fetches automatically become external bus cycles. In other words, the rollover from on-chip ROM to external code memory is transparent to the user.

### 1.2.2.1. Accessing On-chip Code Memory in Region 00:

The TSC83251G1D can be configured so that the upper half of the 16 Kbytes on–chip code memory can also be read as near data at locations in the top of region 00:. That is, locations FF:2000h–FF:3FFFh can also be accessed at locations 00:E000h–00:FFFFh. This is useful for accessing code constants stored in ROM and leads to faster code execution to retrieve these constants. Note, however, that all of the following three conditions must hold for this mapping to be effective:

- The device is configured with EMAP#= 0 in the UCONFIG1 register

- EA#= 1

- The access to this area of region 00: is a data read, not a code fetch.

If one or more of these conditions do not hold, accesses to the locations in region 00: are referred to external memory.

# 1.2.3. External Memory

Regions 01:, FE:, and portions of regions 00: and FF: of the memory space are implemented as external memory. For discussions of external memory see paragraph 2.4. "Configuring the External Memory Interface" and chapter 3. "External Memory Interface".

# **1.3. Special Function Registers**

SFRs are placed in a reserved on-chip memory region S: which is not represented in the address space mapping (Figure 1.1). The relative addresses within S: of these SFRs are provided together with their reset values in Table 1.11. They are upward compatible with the SFRs of the standard 80C51 and the Intel's 80C251Sx family. In this table, the C251 core registers are in italics and are described in the TSC80251 Programmer's Guide. All the SFRs are accessible by direct and bit addressing.

The Special Function Registers (SFRs) of the TSC80251G1D derivatives fall into the categories detailed in Table 1.2 to Table 1.10.

| Table | 1.2 | C251 | Core SI | <b>FRs</b> |

|-------|-----|------|---------|------------|

|-------|-----|------|---------|------------|

| Mnemonic           | Name                       | Mnemonic            | Name                                                  |

|--------------------|----------------------------|---------------------|-------------------------------------------------------|

| ACC <sup>(1)</sup> | Accumulator                | SPH <sup>(1)</sup>  | Stack Pointer High – MSB of SPX                       |

| B <sup>(1)</sup>   | B Register                 | DPL <sup>(1)</sup>  | Data Pointer Low byte - LSB of DPTR                   |

| PSW                | Program Status Word        | DPH <sup>(1)</sup>  | Data Pointer High byte – MSB of DPTR                  |

| PSW1               | Program Status Word 1      | DPXL <sup>(1)</sup> | Data Pointer Extended Low byte of DPX – Region number |

| SP <sup>(1)</sup>  | Stack Pointer – LSB of SPX |                     |                                                       |

Note:

1. These SFRs can also be accessed by their corresponding registers in the register file.

#### Table 1.3 I/O Port SFRs

| Mnemonic | Name   | Mnemonic | Name   |

|----------|--------|----------|--------|

| P 0      | Port 0 | P 2      | Port 2 |

| P 1      | Port 1 | P 3      | Port 3 |

#### **Table 1.4 Timers SFRs**

| Mnemonic | Name                          | Mnemonic | Name                                     |

|----------|-------------------------------|----------|------------------------------------------|

| TL0      | Timer/Counter 0 Low Byte      | TMOD     | Timer/Counter 0 and 1 Modes              |

| TH0      | Timer/Counter 0 High Byte     | T2CON    | Timer/Counter 2 Control                  |

| TL1      | Timer/Counter 1 Low Byte      | T2MOD    | Timer/Counter 2 Mode                     |

| TH1      | Timer/Counter 1 High Byte     | RCAP2L   | Timer/Counter 2 Reload/Capture Low Byte  |

| TL2      | Timer/Counter 2 Low Byte      | RCAP2H   | Timer/Counter 2 Reload/Capture High Byte |

| TH2      | Timer/Counter 2 High Byte     | WDTRST   | WatchDog Timer Reset                     |

| TCON     | Timer/Counter 0 and 1 Control |          |                                          |

#### Table 1.5 Serial I/O Port SFRs

| Mnemonic | Name               | Mnemonic | Name              |

|----------|--------------------|----------|-------------------|

| SCON     | Serial Control     | SADDR    | Slave Address     |

| SBUF     | Serial Data Buffer | BRL      | Baud Rate Reload  |

| SADEN    | Slave Address Mask | BDRCON   | Baud Rate Control |

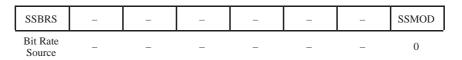

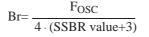

### Table 1.6 SSLC SFRs

| Mnemonic | Name                                  | Mnemonic | Name                        |

|----------|---------------------------------------|----------|-----------------------------|

| SSCON    | Synchronous Serial control            | SSADR    | Synchronous Serial Address  |

| SSDAT    | Synchronous Serial Data               | SSBR     | Synchronous Serial Bit Rate |

| SSCS     | Synchronous Serial Control and Status |          |                             |

## Table 1.7 Event Waveform Control SFRs

| Mnemonic | Name                                             | Mnemonic | Name                                           |

|----------|--------------------------------------------------|----------|------------------------------------------------|

| CCON     | EWC-PCA Timer/Counter Control                    | CCAP1L   | EWC-PCA Compare Capture Module 1 Low Register  |

| CMOD     | EWC-PCA Timer/Counter Mode                       | CCAP2L   | EWC-PCA Compare Capture Module 2 Low Register  |

| CL       | EWC-PCA Timer/Counter Low Register               | CCAP3L   | EWC-PCA Compare Capture Module 3 Low Register  |

| СН       | EWC-PCA Timer/Counter High Register              | CCAP4L   | EWC-PCA Compare Capture Module 4 Low Register  |

| CCAPM0   | EWC-PCA Timer/Counter Mode 0                     | CCAP0H   | EWC-PCA Compare Capture Module 0 High Register |

| CCAPM1   | EWC-PCA Timer/Counter Mode 1                     | CCAP1H   | EWC-PCA Compare Capture Module 1 High Register |

| CCAPM2   | EWC-PCA Timer/Counter Mode 2                     | CCAP2H   | EWC-PCA Compare Capture Module 2 High Register |

| CCAPM3   | EWC-PCA Timer/Counter Mode 3                     | ССАРЗН   | EWC-PCA Compare Capture Module 3 High Register |

| CCAPM4   | EWC-PCA Timer/Counter Mode 4                     | CCAP4H   | EWC-PCA Compare Capture Module 4 High Register |

| CCAP0L   | EWC–PCA Compare Capture Module 0 Low<br>Register |          | ·                                              |

#### Table 1.8 System Management SFRs

| Mnemonic | Name             | Mnemonic | Name                                     |

|----------|------------------|----------|------------------------------------------|

| PCON     | Power Control    | CKRL     | Clock Reload                             |

| POWM     | Power Management | WCON     | Synchronous Real-Time Wait State Control |

| PFILT    | Power Filter     |          |                                          |

### **Table 1.9 Interrupt SFRs**

| Mnemonic | Name                              | Mnemonic | Name                              |

|----------|-----------------------------------|----------|-----------------------------------|

| IE0      | Interrupt Enable Control 0        | IPL0     | Interrupt Priority Control Low 0  |

| IE1      | Interrupt Priority Control 1      | IPH1     | Interrupt Priority Control High 1 |

| IPH0     | Interrupt Priority Control High 0 | IPL1     | Interrupt Priority Control Low 1  |

### Table 1.10 Keyboard Interface SFRs

| Mnemonic | Name                          | Mnemonic | Name                   |

|----------|-------------------------------|----------|------------------------|

| P1IE     | Port 1 Interrupt Input Enable | P1LS     | Port 1 Level Selection |

| P1F      | Port 1 Flag                   |          |                        |

#### **Table 1.11 SFR Addresses and Reset Values**

|     | 0/8                             | 1/9                              | 2/A                             | 3/B                             | 4/C                              | 5/D                 | 6/E                             | 7/F               | _   |

|-----|---------------------------------|----------------------------------|---------------------------------|---------------------------------|----------------------------------|---------------------|---------------------------------|-------------------|-----|

| F8h |                                 | CH<br>0000 0000                  | CCAP0H<br>0000 0000             | CCAP1H<br>0000 0000             | CCAP2H<br>0000 0000              | CCAP3H<br>0000 0000 | CCAP4H<br>0000 0000             |                   | FFh |

| F0h | B <sup>(1)</sup><br>0000 0000   |                                  |                                 |                                 |                                  |                     |                                 |                   | F7h |

| E8h |                                 | CL<br>0000 0000                  | CCAP0L<br>0000 0000             | CCAP1L<br>0000 0000             | CCAP2L<br>0000 0000              | CCAP3L<br>0000 0000 | CCAP4L<br>0000 0000             |                   | EFh |

| E0h | ACC <sup>(1)</sup><br>0000 0000 |                                  |                                 |                                 |                                  |                     |                                 |                   | E7h |

| D8h | CCON<br>00X0 0000               | CMOD<br>00XX X000                | CCAPM0<br>X000 0000             | CCAPM1<br>X000 0000             | CCAPM2<br>X000 0000              | CCAPM3<br>X000 0000 | CCAPM4<br>X000 0000             |                   | DFh |

| D0h | PSW <sup>(1)</sup><br>0000 0000 | PSW1 <sup>(1)</sup><br>0000 0000 |                                 |                                 |                                  |                     |                                 |                   | D7h |

| C8h | T2CON<br>0000 0000              | T2MOD<br>XXXX XX00               | RCAP2L<br>0000 0000             | RCAP2H<br>0000 0000             | TL2<br>0000 0000                 | TH2<br>0000 0000    |                                 |                   | CFh |

| C0h |                                 |                                  |                                 |                                 |                                  |                     |                                 |                   | C7h |

| B8h | IPL0<br>X000 0000               | SADEN<br>0000 0000               |                                 |                                 |                                  |                     | SPH <sup>(1)</sup><br>0000 0000 |                   | BFh |

| B0h | P3<br>1111 1111                 | IE1<br>XX0X XXX0                 | IPL1<br>XX0X XXX0               | IPH1<br>XX0X XXX0               |                                  |                     |                                 | IPH0<br>X000 0000 | B7h |

| A8h | IE0<br>0000 0000                | SADDR<br>0000 0000               |                                 |                                 |                                  |                     |                                 |                   | AFh |

| A0h | P2<br>1111 1111                 |                                  |                                 |                                 |                                  |                     | WDTRST<br>1111 1111             | WCON<br>XXXX XX00 | A7h |

| 98h | SCON<br>0000 0000               | SBUF<br>XXXX XXXX                | BRL<br>0000 0000                | BDRCON<br>XXX0 0000             | P1LS<br>0000 0000                | P1IE<br>0000 0000   | P1F<br>0000 0000                |                   | 9Fh |

| 90h | P1<br>1111 1111                 |                                  | SSBR<br>0000 0000               | SSCON<br>(2)                    | SSCS<br>(3)                      | SSDAT<br>0000 0000  | SSADR<br>0000 0000              |                   | 97h |

| 88h | TCON<br>0000 0000               | TMOD<br>0000 0000                | TL0<br>0000 0000                | TL1<br>0000 0000                | TH0<br>0000 0000                 | TH1<br>0000 0000    | CKRL<br>0000 1000               | POWM<br>0XXX 0XXX | 8Fh |

| 80h | P0<br>1111 1111                 | SP<br>0000 0111                  | DPL <sup>(1)</sup><br>0000 0000 | DPH <sup>(1)</sup><br>0000 0000 | DPXL <sup>(1)</sup><br>0000 0001 |                     | PFILT<br>XXXX XXXX              | PCON<br>0000 0000 | 87h |

|     | 0/8                             | 1/9                              | 2/A                             | 3/B                             | 4/C                              | 5/D                 | 6/E                             | 7/F               | -   |

reserved

Notes:

These registers are described in the TSC80251 Programmer's Guide (C251 core registers).

In I<sup>2</sup>C and SPI modes, SSCON is splitted in two separate registers. SSCON reset value is 0000 0000 in I<sup>2</sup>C mode and 0000 0100 in SPI mode.

2. In read and write modes, SSCS is splitted in two separate registers. SSCS reset value is 1111 1000 in read mode and 0000 0000 in write mode.

# 2. Device Configuration

The TSC80251G1D derivatives provide user design flexibility by configuring certain operating features at device reset. These features fall into the following categories:

- external memory interface (page mode, address bits, pre-programmed wait states and the address range for RD#, WR#, and PSEN#)

- source mode/binary mode opcodes

- selection of bytes stored on the stack by an interrupt

- mapping of the upper portion of on-chip code memory to region 00:

You can specify a 16-bit, 17-bit, or 18-bit external address bus (64 to 256 Kbytes external address space). Wait state configurations provide pre-programmed 0, 1, 2, or 3 wait states.

This chapter provides a detailed discussion of the TSC80251G1D device configuration. It describes the configuration bytes and provides information to help user in selecting a suitable configuration for his application. It discusses the choices involved in configuring the external memory interface and shows how the internal memory maps into the external memory.

# 2.1. Configuration Overview

The configuration of the microcontroller is established after the reset sequence based on information stored in configuration bytes. The TSC80251G1D derivatives store configuration information in two configuration bytes.

# 2.2. Device Configuration

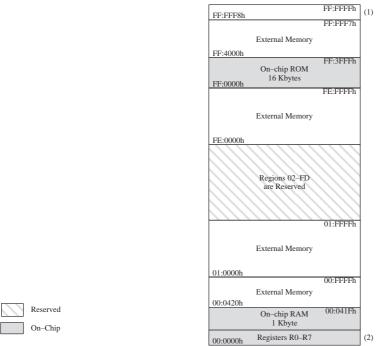

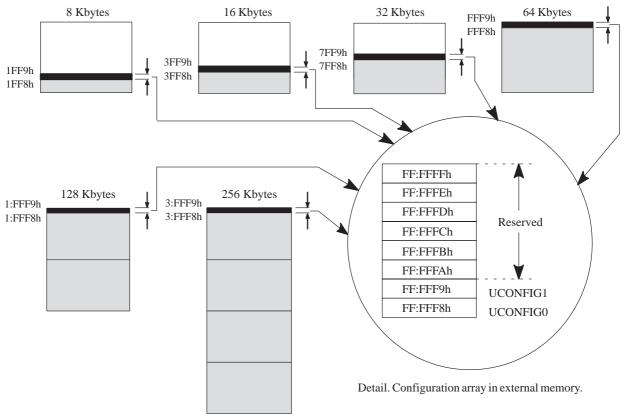

The TSC80251G1D derivatives reserve the top eight bytes of the memory address map (FF:FFF8h-FF:FFFh) for an eight–byte configuration array. The two lowest bytes of the configuration array are assigned to the user configuration bytes UCONFIG0 (FF:FFF8H) and UCONFIG1 (FF:FFF9H). Bit definitions of UCONFIG0 and UCONFIG1 are provided in Figure 2.7 and Figure 2.8. The upper 6 bytes of the configuration array are reserved for future use.

# **2.2.1. ROMless Devices**

For devices without on–chip code memory (TSC80251G1D), configuration information is fetched from external memory system using internal addresses FF:FFF8h and FF:FFF9h. User configuration bytes UCONFIG0 and UCONFIG1 should be stored in an eight–byte configuration array located at the highest addresses implemented in external code memory (see Table 2.1 and Figure 2.2). Paragraph 3.6. "Configuration Byte Bus Cycle" discusses on how the configuration bytes are retrieved from external memory.

# 2.2.2. ROM Devices

For devices with on-chip code memory (TSC83251G1D), configuration information is fetched from a dedicated on-chip non-volatile memory at addresses FF:FFF8h and FF:FFF9h (see Figure 2.1). User configuration bytes UCONFIG0 and UCONFIG1 are programmed at the factory using customer's configuration data supplied with the code file. *Note:*

ROM devices used with EA# pin = 0 operate as ROMless devices.

Caution:

The eight highest addresses in the memory address space (FF:FFF8h-FF:FFFFh) are reserved for the configuration array. Do not read or write these locations. These addresses are also used to access the configuration array in external memory, so the same restrictions apply to the eight highest addresses implemented in external memory. Instructions that might inadvertently cause these addresses to be accessed due to call returns or prefetches should not be located at addresses immediately below the configuration array. Use an EJMP instruction, five or more addresses below the configuration array, to continue execution in other areas of memory.

Detail. Dedicated on-chip configuration array.

#### Note:

For EA#= 1, the TSC83251G1D obtains configuration information from a dedicated on-chip non-volatile memory at addresses FF:FFF8h and FF:FFF9h.

Figure 2.1 Configuration Array (On-chip)

#### Note:

For EA#= 0, the TSC80251G1D derivatives obtain configuration information from configuration bytes in external memory using internal addresses FF:FFF8h and FF:FFF9h. In external memory, the eight-byte configuration array is located at the highest addresses implemented.

Figure 2.2 Configuration Array (External)

2

| Size of External Address Bus (Bits) | Address of Configuration Array on<br>External Bus <sup>(2)</sup> | Address of Configuration Bytes on<br>External Bus <sup>(1)</sup> |

|-------------------------------------|------------------------------------------------------------------|------------------------------------------------------------------|

| 16                                  | FFF8h-FFFFh                                                      | UCONFIG1: FFF9h<br>UCONFIG0: FFF8h                               |

| 17                                  | 1FFF8h-1FFFFh                                                    | UCONFIG1: 1FFF9h<br>UCONFIG0: 1FFF8h                             |

| 18                                  | 3FFF8h-3FFFFh                                                    | UCONFIG1: 3FFF9h<br>UCONFIG0: 3FFF8h                             |

#### Table 2.1 External Addresses for Configuration Array

Notes:

1. When EA#= 0, the reset routine retrieves UCONFIG0 and UCONFIG1 from external memory using internal addresses FF:FFF8h and FF:FFF9h, which appear on the microcontroller external address bus (A17, A16, A15:0).

2. The upper six bytes of the configuration array are reserved for future use.

# **2.3.** The Configuration Bits

This paragraph provides a brief description of the configuration bits contained in the configuration bytes (Figure 2.7 and Figure 2.8). UCONFIG0 and UCONFIG1 have five wait state bits: WSA1:0#, WSB1:0#, and WSB.

- SRC. Selects source mode or binary mode opcode configuration.

- INTR. Selects the bytes pushed onto the stack by interrupts.

- EMAP#. Maps on-chip code memory (16-Kbyte devices only) to memory region 00:.

The following bits configure the external memory interface.

- PAGE#. Selects page/non-page mode and specifies the data port.

- RD1:0. Selects the number of external address bus pins and the address range for RD#, WR, and PSEN#.

- XALE#. Extends the ALE pulse.

- WSA1:0#. Selects 0, 1, 2, or 3 pre-programmed wait states for all regions except 01:.

- WSB1:0#. Selects 0 3 pre–programmed wait states for memory region 01:.

- EMAP#. Affects the external memory interface in that, when asserted, addresses in therange 00:E000H-00:FFFH access on-chip memory.

# 2.4. Configuring the External Memory Interface

This paragraph describes the configuration options that affect the external memory interface. The configuration bits described here determine the following interface features:

- page mode or non-page mode (PAGE#)

- the number of external address pins (16, 17, or 18) (RD1:0)

- the memory regions assigned to the read signals RD# and PSEN# (RD1:0)

- the external wait states (WSA1:0#, WSB1:0#, XALE#)

- mapping a portion of on-chip code memory to data memory (EMAP#)

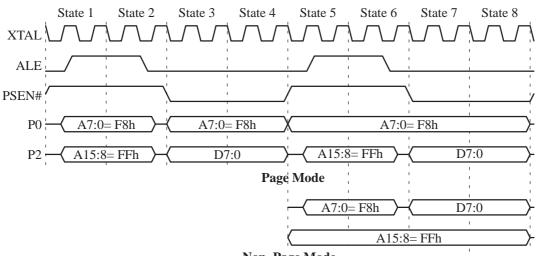

### 2.4.1. Page Mode and Non-Page Mode (PAGE#)

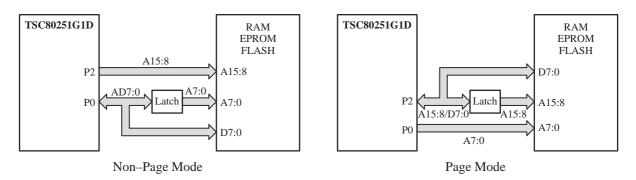

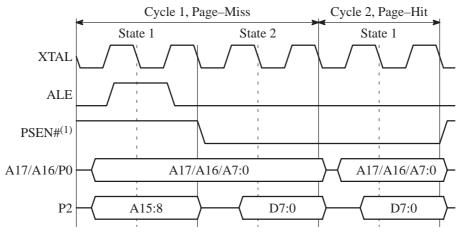

The PAGE# bit (UCONFIG0.1) determines whether code fetches use page mode or non-page mode and whether data is transmitted on P2 or P0. See paragraph 3.2.3. "Page Mode Bus Cycles", for a description of the bus structure and page mode operation.

- Non-Page Mode: PAGE#= 1. The bus structure is the same as for the MCS 51 architecture with data D7:0 multiplexed with A7:0 on P0. External code fetches require two state times (4Tosc).

- Page Mode: PAGE#= 0. The bus structure differs from the bus structure in MCS 51 controllers. Data D7:0 is multiplexed with A15:8 on P2. Under certain conditions, external code fetches require only one state time (2Tosc).

#### Caution:

When TSC83251G1D is not used in romless mode (EA#= 1), then Port 2 is used as I/O port. In this configuration, PAGE# bit must be set to logic 1 to select non-page mode (see paragraph 3.7. "Port 0 and Port 2 Status".

# 2.4.2. Configuration Bits RD1:0

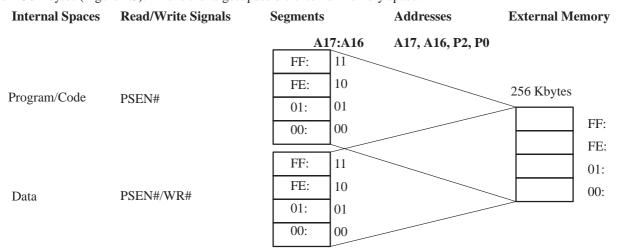

The RD1:0 configuration bits (UCONFIG0.3:2) determine the number of external address signals and the address ranges for asserting the read signals PSEN#/RD# and the write signal WR#. These selections offer different ways of addressing external memory. Figure 2.3 to Figure 2.6 show how internal memory maps into external memory for the four values of RD1:0.

A key to the memory interface is the relationship between internal memory a dresses and external memory addresses. While the TSC80251G1D has 24 internal address bits, the number of external address lines is less than 24 (i.e., 16, 17, or 18 depending on the values of RD1:0). This means that reads/writes to different internal memory addresses can access the same location in external memory.

For example, if the TSC80251G1D is configured for 17 external address lines, a write to location 01:6000h and a write to location FF:6000h accesses the same 17–bit external address (1:6000h) because A16= 1 for both internal addresses. In other words, regions 01: and FF: map into the same 64 Kbytes region in external memory.

In some situations, however, a multiple mapping from internal memory to external memory does not preclude using more than one region. For example, for a device with on-chip ROM configured for 17 address bits and with EA#= 1, an access to FF:0000h-FF:3FFFh (16 Kbytes) accesses the on-chip ROM, while an access to 01:0000h-01:3FFFh is to external memory. In this case, you could execute code from these lo-cations in region FF: and store data in the corresponding locations in region 01: without conflict.

### 2.4.2.1. RD1:0= 00 (18 External Address Bits)

The selection RD1:0= 00 provides 18 external address bits: A15:0 (ports P0 and P2), A16 (from P3.7/RD#/A16), and A17 (from P1.7/CEX4/A17/WCLK). Bits A16 and A17 can select four 64–Kbyte regions of external memory for a total of 256 Kbytes (Figure 2.3). This is the largest possible external memory space.

Figure 2.3 Internal/External Memory Segments (RD1:0=00)

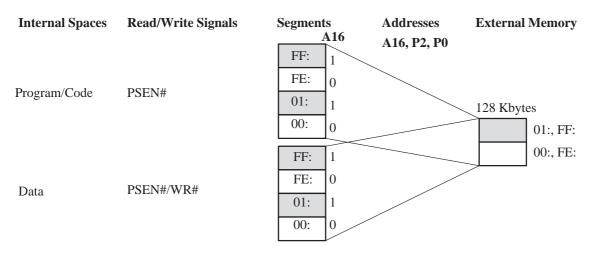

### 2.4.2.2. RD1:0= 01 (17 External Address Bits)

The selection RD1:0=01 provides 17 external address bits: A15:0 (ports P0 and P2) and A16 (from P3.7/RD#/A16). Bit A16 can select two 64–Kbyte regions of external memory for a total of 128 Kbytes (Figure 2.4). Regions 00: and FE: (each having A16=0) map into the same 64–Kbyte region in external memory. This duplication also occurs for regions 01: and FF:

2

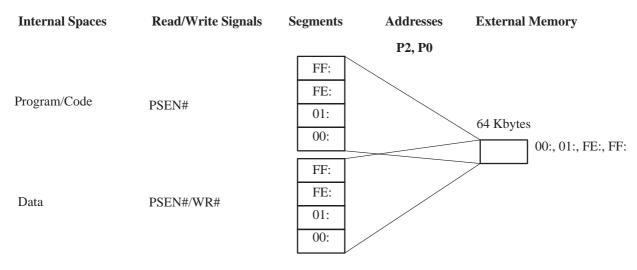

### 2.4.2.3. RD1:0= 10 (16 External Address Bits)

For RD1:0= 10, the 16 external address bits (A15:0 on ports P0 and P2) provide a single 64–Kbyte region in external memory (Figure 2.5). This selection provides the smallest external memory space; however, pin P3.7/RD#/A16 is available for general I/O and pin P1.7 is available for general I/O, PCA I/O, SSLC I/O, and synchronous real–time wait clock output. This selection is useful when the availability of these pins is required and/or a small amount of external memory is sufficient.

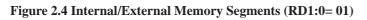

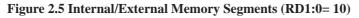

### 2.4.2.4. RD1:0= 11 (Compatible with MCS<sup>®</sup> 51 Microcontrollers)

The selection RD1:0=11 provides only 16 external address bits (A15:0 on ports P0 and P2). However, PSEN# is the read signal for regions FE:-FF:, while RD# is the read signal for regions 00:-01: (Figure 2.6). The two read signals effectively expand the external memory space to two 64–Kbyte regions. WR# is asserted only for writes to regions 00:-01:. This selection provides compatibility with MCS 51 microcontrollers, which have separate external memory spaces for code and data.

Figure 2.6 Internal/External Memory Segments (RD1:0=11)

Notes:

1. PSEN# is asserted instead of RD# when reading data in regions FE: and FF:.

2. Writing in region FE: and region FF: corresponds to writing in region 00: and region 01: respectively.

### 2.4.3. Wait State Configuration Bits

You can add wait states to external bus cycles by extending the RD#/WR#/PSEN# pulse and/or extending the ALE pulse. Each additional wait state extends the pulse by  $2T_{OSC}$ . A separate wait state specification for external accesses via region 01: permits a slow external device to be addressed in region 01: without slowing accesses to other external devices. Table 2.2 summarizes the wait state selections for RD#,WR#,PSEN#. For waveform diagrams showing wait states see "External Bus Cycles with Configurable Wait States".

#### 2.4.3.1. Configuration Bits WSA1:0#, WSB1:#

The WSA1:0# wait state bits (UCONFIG0.6:5) permit RD#, WR#, and PSEN# to be extended by 1, 2, or 3 wait states for accesses to external memory via all regions except region 01:. The WSB1:0# wait state bits (UCONFIG1.2:1) permit RD#, WR#, and PSEN# to be extended by 1, 2, or 3 wait states for accesses to external memory via region 01:.

### 2.4.3.2. Configuration Bit WSB

Use the WSB bit only for A-stepping compatibility. The WSB wait state bit (UCONFIG1.3) permits RD#, WR#, and PSEN# to be extended by one wait state for accesses to external memory via region 01:.

#### 2.4.3.3. Configuration Bit XALE#

Clearing XALE# (UCONFIG0.4) extends the time ALE is asserted from  $T_{OSC}$  to  $3T_{OSC}$ . THis accommodates an address latch that is too slow for the normal ALE signal. Paragraph 3.4.2. "Extending ALE", shows an external bus cycle with ALE extended.

| Regions     | Configur                  | ation bits                | Number of Wait States        |

|-------------|---------------------------|---------------------------|------------------------------|

| 00: FE: FF: | WSA1#<br>0<br>0<br>1<br>1 | WSA0#<br>0<br>1<br>0<br>1 | 3 WS<br>2 WS<br>1 WS<br>0 WS |

| 01:         | WSB1#<br>0<br>0<br>1<br>1 | WSB0#<br>0<br>1<br>0<br>1 | 3 WS<br>2 WS<br>1 WS<br>0 WS |

| Table 2.2 RD# | , WR#, | <b>PSEN# External</b> | Wait States |

|---------------|--------|-----------------------|-------------|

|---------------|--------|-----------------------|-------------|

# 2.4.4. Opcode Configurations (SRC)

The SRC configuration bit (UCONFIG0.0) selects the source mode or binary mode opcode arrangement.

Refer to TSC80251 Programmer's Guide for information on source mode and binary mode.

# 2.4.5. Mapping On-chip Code Memory to Data Memory (EMAP#)

The EMAP# bit (UCONFIG1.0) provides the option of accessing the upper half of on–chip code memory as data memory. This allows code constants to be accessed as data in region 00: using direct addressing. See paragraph 1.2.2.1. "Accessing On–chip Code Memory in Region 00:", for the exact conditions required for this mapping to be effective.

$EMAP \#= 0. \ For \ TSC 80251G1D, the \ upper \ 8 \ Kbytes \ of \ on-chip \ code \ memory \ (FF: 2000h-FF: 3FFFh) \ are \ mapped \ to \ locations \ 00: E000h-00: FFFFh.$

EMAP#= 1. Mapping of on-chip code memory to region 00: does not occur. Addresses in the range 00:E000h-00:FFFFh access external RAM.

# 2.4.6. Interrupt Mode (INTR)

The INTR bit (UCONFIG1.4) determines what bytes are stored on the stack when an interrupt occurs and how the RETI (Return from Interrupt) instruction restores operation.

For INTR= 0, an interrupt pushes the two lower bytes of the PC onto the stack in the following order: PC.7:0, PC.15:8. The RETI instruction pops these two bytes in the reverse order and uses them as the 16–bit return address in region FF:.

For INTR= 1, an interrupt pushes the three PC bytes and the PSW1 register onto the stack in the following order: PSW1, PC.23:16, PC.7:0, PC.15:8. The RETI instruction pops these four bytes and then returns to the specified 24–bit address, which can be anywhere in the 16 Mbytes address space.

# 2.5. Registers

## **UCONFIG0**

Configuration Byte 0

| 7 | 6     | 5     | 4     | 3   | 2   | 1     | 0   |

|---|-------|-------|-------|-----|-----|-------|-----|

| _ | WSA1# | WSA0# | XALE# | RD1 | RD0 | PAGE# | SRC |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                          |  |  |

|---------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7             | _               | Reserved<br>Set this bit when writing to UCONFIG0.                                                                                                                                                                   |  |  |

| 6             | WSA1#           | <ul> <li>Wait State A bits         Select the number of wait states for RD#, WR# and PSEN# signals for external memory accesses (all regions except 01:).     </li> <li>WSA1# WSA0# Number of wait states</li> </ul> |  |  |

| 5             | WSA0#           | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                 |  |  |

| 4             | XALE#           | <b>Extend ALE bit</b><br>Clear to extend the time of the ALE pulse from $T_{OSC}$ to $3 \times T_{OSC}$ .<br>Set to keep the time of the ALE pulse to $T_{OSC}$ .                                                    |  |  |

| 3             | RD1             | Memory Signal Select bits                                                                                                                                                                                            |  |  |

| 2             | RD0             | Codes specify a 18-bit, 17-bit or 16-bit external address bus and address ranges for RD#, WR# and PSEN# signals (see Table 2.3).                                                                                     |  |  |

| 1             | PAGE#           | Page Mode Select bit <sup>(1)</sup><br>Clear for page mode with A15:8/D7:0 on Port 2 and A7:0 on Port 0.<br>Set for non-page mode <sup>(2)</sup> with A15:8 on Port 2 and A7:0/D7:0 on Port 0.                       |  |  |

| 0             | SRC             | Source Mode/Binary Mode Select bit<br>Clear for binary mode.<br>Set for source mode.                                                                                                                                 |  |  |

Notes:

1. UCONFIG0 is fetched twice so it can be properly read both in Page or Non–Page modes. If P2.1 is cleared during the first data phase, a page mode configuration is used, otherwise the subsequent fetches are performed in Non–Page mode (see paragraph 3.6. "Configuration Byte Bus Cycle".

This selection provides compatibility with the standard 80C51 hardware which is multiplexing the address LSB and the data on Port 0.

#### Figure 2.7 Configuration Byte 0

The following Table describes in detail the address range selected with RDx bits.

#### Table 2.3 Memory Signal Selections (RD1:0)

| RD1 | RD0 | P1.7    | P3.7/RD#                                             | PSEN#                                                | WR#                                                   | External<br>Memory       |

|-----|-----|---------|------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------|--------------------------|

| 0   | 0   | A17     | A16                                                  | Read signal for all external memory locations        | Write signal for all external memory locations        | 256 Kbytes               |

| 0   | 1   | I/O pin | A16                                                  | Read signal for all external memory locations        | Write signal for all external memory locations        | 128 Kbytes               |

| 1   | 0   | I/O pin | I/O pin                                              | Read signal for all external memory locations        | Write signal for all external memory locations        | 64 Kbytes                |

| 1   | 1   | I/O pin | Read signal for regions 00:<br>and 01: (data memory) | Read signal for regions FE:<br>and FF: (code memory) | Write signal for regions 00:<br>and 01: (data memory) | 64 Kbytes <sup>(1)</sup> |

Note:

1. This selection provides compatibility with C51 microcontrollers which have separate external memory space for data and code.

# UCONFIG1

Configuration Byte 1

| 7 | 6 | 5 | 4    | 3   | 2     | 1     | 0     |

|---|---|---|------|-----|-------|-------|-------|

| - | - | - | INTR | WSB | WSB1# | WSB0# | EMAP# |

| Bit<br>Number | Bit<br>Mnemonic | Description                                                                                                                                                                                                                                                                             |  |  |  |

|---------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7             | -               | Reserved<br>Set this bit when writing to UCONFIG1.                                                                                                                                                                                                                                      |  |  |  |

| 6             | -               | Reserved<br>Set this bit when writing to UCONFIG1.                                                                                                                                                                                                                                      |  |  |  |

| 5             | -               | Reserved<br>Set this bit when writing to UCONFIG1.                                                                                                                                                                                                                                      |  |  |  |

| 4             | INTR            | <b>terrupt Mode bit</b> <sup>(1)</sup><br>Clear so that the interrupts push two bytes onto the stack (the two lower bytes of the PC register).<br>Set so that the interrupts push four bytes onto the stack (the three bytes of the PC register and the PSW1 register).                 |  |  |  |

| 3             | WSB             | Wait State B bit <sup>(2)</sup><br>Clear to generate one wait state for memory region 01:.<br>Set for no wait states for memory region 01:.                                                                                                                                             |  |  |  |

| 2             | WSB1#           | <ul> <li>Wait State B bits         Select the number of wait states for RD#, WR# and PSEN# signals for external memory accesses         (only region 01:).     </li> <li>WSB1# WSB0# Number of wait states</li> </ul>                                                                   |  |  |  |

| 1             | WSB0#           | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                   |  |  |  |

| 0             | EMAP#           | On-Chip Code Memory Map bit<br>Clear to map the upper 8 Kbytes of on-chip code memory (FF:2000h-FF:3FFFh) to<br>(00:E000h-00:FFFFh).<br>Set to not map the upper 8 Kbytes of on-chip code memory (FF:2000h-FF:3FFFh).<br>Locations (00:E000h-00:FFFFh) are implemented by external RAM. |  |  |  |

Notes:

1. Two or four bytes are transparently popped according to INTR when using the RETI instruction. INTR must be set if interrupts are used with code executing outside region FF:.

2. Use only for Step A compatibility; set this bit when WSB1:0# are used.

# Figure 2.8 Configuration Byte 1

# **3. External Memory Interface**

# **3.1. Introduction**

The external memory interface comprises the external bus (ports 0 and 2) as well as the bus control signals (RD#, WR#, PSEN# and ALE). Chip configuration bytes (see chapter 2. "Device Configuration") determine several interface options: page mode or non–page mode for external code fetches; the number of external address bits (16, 17, or 18); the address ranges for RD#, WR#, and PSEN#; and the number of preprogrammed external wait states to extend RD#, WR#, PSEN# or ALE. Two kinds of real–time wait states are available: the asynchronous always enabled and the synchronous that can be enabled with special function register WCON.1:0. You can use these options to tailor the interface to your application. See also paragraph 2.4. "Configuring the External Memory Interface".

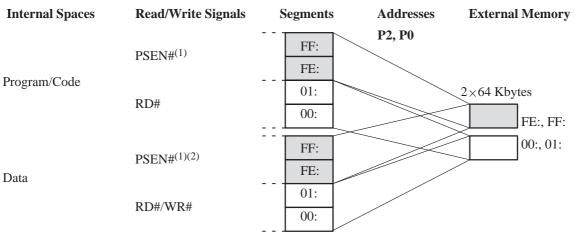

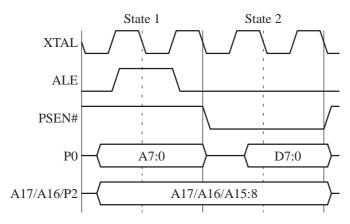

The external memory interface operates in either page mode or non–page mode. Page mode provides increased performance by reducing the time for external code fetches. Page mode does not apply to code fetches from on–chip memory. The reset routine configures the TSC80251G1D for operation in page mode or non–page mode according to bit 1 of configuration byte UCONFIG0. Figure 3.1 shows the structure of the external address bus for page and non–page mode operation. P0 carries address A7:0 while P2 carries address A15:8. Data D7:0 is multiplexed with A7:0 on P0 in non–page mode and with A15:8 on P2 in page mode. Table 3.1 describes the external memory interface signals. The address and data signals (AD7:0 on port 0 and A15:8 on port 2) are defined for non–page mode.

Figure 3.1 Bus Structure in Non–Page Mode and Page Mode

## **Table 3.1 External Memory Interface Signals**

| Signal Name                                  | Туре | Description                                                                                                                                                                                                                                                                                                                                                                     | Alternative Function |

|----------------------------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| A17                                          | 0    | 18 <sup>th</sup> Address Bit                                                                                                                                                                                                                                                                                                                                                    | P1.7                 |

|                                              |      | Output to memory as 18th external address bit (A17) in extended bus applications, depending on the values of bits RD0 and RD1 in UCONFIG0 byte.                                                                                                                                                                                                                                 |                      |

| A16                                          | 0    | 17 <sup>th</sup> Address Bit                                                                                                                                                                                                                                                                                                                                                    | P3.7                 |

|                                              |      | Output to memory as 17th external address bit (A16) in extended bus applications, depending on the values of bits RD0 and RD1 in UCONFIG0 byte (see also RD#).                                                                                                                                                                                                                  |                      |

| A15:8 <sup>(1)</sup>                         | 0    | Address Lines                                                                                                                                                                                                                                                                                                                                                                   | P2.7:0               |

|                                              |      | Upper address lines for the external bus (non-page mode).                                                                                                                                                                                                                                                                                                                       |                      |

| AD7:0 <sup>(1)</sup>                         | I/O  | Address/Data Lines                                                                                                                                                                                                                                                                                                                                                              | P0.7:0               |

|                                              |      | Multiplexed lower address lines and data for the external memory (non-page mode).                                                                                                                                                                                                                                                                                               |                      |

| ALE                                          | 0    | Address Latch Enable                                                                                                                                                                                                                                                                                                                                                            | -                    |

|                                              |      | ALE signals the start of an external bus cycle and indicates that valid address infor-<br>mation are available onlines A16/A17 and A7:0.                                                                                                                                                                                                                                        |                      |

| AWAIT#                                       | Ι    | Real-time Asynchronous Wait States Input                                                                                                                                                                                                                                                                                                                                        | -                    |

|                                              |      | When this pin is active (low level), the memory cycle is stretched until it becomes high.                                                                                                                                                                                                                                                                                       |                      |

| EA#                                          | Ι    | External Access Enable                                                                                                                                                                                                                                                                                                                                                          | -                    |

|                                              |      | EA# directs program memory accesses to on-chip or off-chip code memory.<br>For EA#= 0, all program memory accesses are off-chip.<br>For EA#= 1, an access is on-chip ROM if the address is within the range of the on-<br>chip ROM; otherwise the access is off-chip. The value of EA# is latched at reset.<br>For devices without ROM on-chip, EA# must be strapped to ground. |                      |

| PSEN# O Program Store Enable/Read signal out |      | Program Store Enable/Read signal output                                                                                                                                                                                                                                                                                                                                         | -                    |

|                                              |      | PSEN# is asserted for a memory address range that depends on bits RD0 and RD1 in UCONFIG0 byte (see also RD#).                                                                                                                                                                                                                                                                  |                      |

|                                              |      | $ \begin{array}{c cccc} \text{RD1} & \text{RD0} & \text{Addresses Range for Assertion} \\ 0 & 0 & \text{All addresses} \\ 0 & 1 & \text{All addresses} \\ 1 & 0 & \text{All addresses} \\ 1 & 1 & \text{All addresses} \geq 80:0000 \text{h.} \\ \end{array} $                                                                                                                  |                      |

| <b>DD</b> #                                  | 0    | <b>Read or <math>17^{\text{th}}</math> Address Bit (A16)</b>                                                                                                                                                                                                                                                                                                                    | D2 7                 |

| RD#                                          | 0    | Read or 17th Address Bit (A16)Read signal output to external data memory or $17^{th}$ external address bit (A16), depending on the values of bits RD0 and RD1 in UCONFIG0 byte (see also PSEN#).RD1RD0Function00The pin functions as A16 only01The pin functions as A16 only10The pin functions as P3.7 only11RD# asserted for reads at all addresses $\leq$ 7F:FFFFh.          | P3.7                 |

| WAIT#                                        | Ι    | Real-time Synchronous Wait States Input                                                                                                                                                                                                                                                                                                                                         | P1.6                 |

|                                              |      | The real-time synchronous WAIT# input is enabled by setting RTWE bit in WCON (S:A7h). During bus cycles, the external memory system can signal 'system ready' to the microcontroller in real time by controlling the WAIT# input signal on the port 1.6 input.                                                                                                                  |                      |

| WCLK                                         | 0    | Wait Clock Output                                                                                                                                                                                                                                                                                                                                                               | P1.7                 |

|                                              |      | The real-time WCLK output is enabled by setting RTWCE bit in WCON (S:A7h).<br>When enabled, the WCLK output produces a square wave signal with a period of one<br>half the oscillator frequency on the port P1.7 output.                                                                                                                                                        |                      |

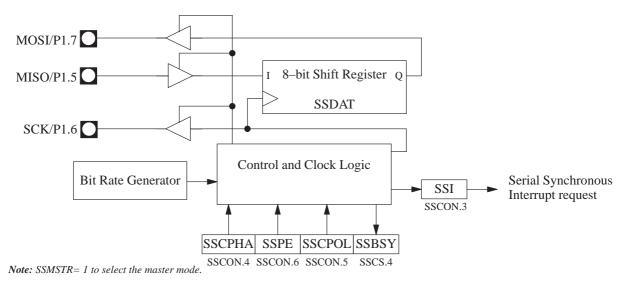

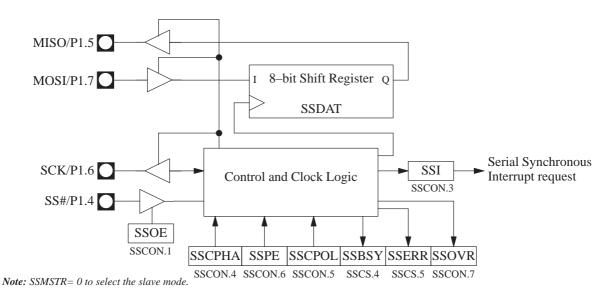

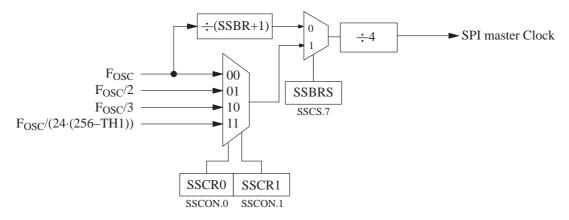

| WR#                                          | 0    | Write                                                                                                                                                                                                                                                                                                                                                                           | P3.6                 |