## 256K (32K × 8) CMOS UV ERASABLE PROM

- FAST ACCESS TIME: 150ns, 170ns, 200ns, 250ns, 300ns.

- COMPATIBLE TO HIGH SPEED MICROPROCESSORS ZERO WAIT STATE

- 28-PIN JEDEC APPROVED PIN-OUT

- LOW POWER CONSUMPTION: ACTIVE 30mA MAX STANDBY 1mA MAX

- PROGRAMMING VOLTAGE 12.5V

- HIGH SPEED PROGRAMMING

- ELECTRONIC SIGNATURE

- WILL BE PROPOSED IN PLASTIC PACKAGE (OTP)

## **PIN CONNECTIONS**

## DESCRIPTION

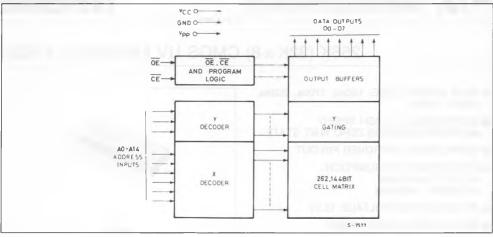

The TS27C256 is a high speed 262,144 bit UV erasable and electrically reprogrammable EPROM ideally suited for applications where fast turnaround and pattern experimentation are important requirements.

The TS27C256 is packaged in a 28-pin dual-in-line package with transparent lid. The transparent lid allows the user to expose the chip to ultraviolet light to erase the bit pattern. A new pattern can then be written into the device by following the programming procedure.

#### **PIN NAMES**

| A0-A14 | ADDRESS       |  |

|--------|---------------|--|

| CE     | CHIP ENABLE   |  |

| ŌE     | OUTPUT ENABLE |  |

| 00-07  | OUTPUTS       |  |

## **BLOCK DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS(1)**

| Symbol                         | Parameter                                               |          | Value                                                         | Unit |

|--------------------------------|---------------------------------------------------------|----------|---------------------------------------------------------------|------|

| Tamb                           | Operating temperature range<br>TS27C256CQ<br>TS27C256VQ |          | T <sub>L</sub> to T <sub>H</sub><br>0 to + 70<br>- 40 to + 85 |      |

| T <sub>stg</sub>               | Storage temperature range                               |          | - 65 to + 125                                                 | °C   |

| V <sub>PP</sub> <sup>(2)</sup> | Supply voltage                                          |          | -0.6 to +14                                                   | V    |

| V <sub>IN</sub> <sup>(2)</sup> | Input voltages<br>Except V <sub>PP</sub> ,              | A9<br>A9 | - 0.6 to + 13.5<br>- 0.6 to + 6.25                            | V    |

| PD                             | Max power dissipation                                   |          | 1.5                                                           | W    |

|                                | Lead temperature<br>(Soldering: 10 seconds)             |          | + 300                                                         | °C   |

Notes: 1. "Maximum ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating temperature range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical characteristics" provides conditions for actual device operation.

With respect to GND

#### **OPERATING MODES**

| PINS                                | CE<br>(20) | OE<br>(22) | A9<br>(24)         | V <sub>PP</sub><br>(1) | V <sub>CC</sub><br>(28) | OUTPUTS<br>(11-13 15-19) |

|-------------------------------------|------------|------------|--------------------|------------------------|-------------------------|--------------------------|

| READ                                | VIL        | VIL        | X                  | V <sub>CC</sub>        | V <sub>CC</sub>         | D <sub>OUT</sub>         |

| OUTPUT DISABLE                      | VIL        | VIH        | Х                  | V <sub>CC</sub>        | Vcc                     | Hi-Z                     |

| STANDBY                             | VIH        | х          | Х                  | V <sub>CC</sub>        | V <sub>CC</sub>         | Hi-Z                     |

| HIGH SPEED PROGRAMMING              | VIL        | VIH        | X                  | VPP                    | V <sub>CC</sub>         | D <sub>IN</sub>          |

| PROGRAM VERIFY                      | VIH        | VIL        | X                  | VPP                    | V <sub>CC</sub>         | DOUT                     |

| PROGRAM INHIBIT                     | VIH        | VIH        | Х                  | Vpp                    | V <sub>CC</sub>         | Hi-Z                     |

| ELECTRONIC SIGNATURE <sup>(3)</sup> | VIL        | VIL        | V <sub>H</sub> (2) | Vcc                    | V <sub>CC</sub>         | CODE                     |

Notes: 1 - X can be either VIL or VIH — 2 - VH = 12.0V  $\pm 0.5V$

3 - All address lines at VIL except A9 and A0 that is toggled from VIL (manufacturer code: 9B) to VIH (type code: 04).

## **READ OPERATION**

| Symbol          | Parameter                                           | Test Conditions                                                               | Min.                        | Typ. <sup>(1)</sup> | Max.               | Unit |

|-----------------|-----------------------------------------------------|-------------------------------------------------------------------------------|-----------------------------|---------------------|--------------------|------|

| ILI             | Input Load Current                                  | VIN = VCC or GND                                                              |                             |                     | 10                 | μA   |

| ILO             | Output Leakage Current                              | $V_{OUT} = V_{CC} \text{ or } V_{SS},$<br>CE = V <sub>IH</sub>                |                             |                     | 10                 | μΑ   |

| VPP             | VPP Read Voltage                                    |                                                                               | V <sub>CC</sub> - 0.7       |                     | Vcc                | V    |

| VIL             | Input Low Voltage                                   |                                                                               | - 0.1                       |                     | 0.8                | V    |

| VIH             | Input High Voltage                                  |                                                                               | 2.0                         |                     | V <sub>CC</sub> +1 | V    |

| V <sub>OL</sub> | Output Low Voltage                                  | I <sub>OL</sub> = 2.1 mA<br>I <sub>OL</sub> = 0 μA                            |                             |                     | 0.45<br>0.1        | V    |

| VOH             | Output High Voltage                                 | $I_{OH} = -400 \ \mu A$<br>$I_{OH} = 0 \ \mu A$                               | 2.4<br>V <sub>CC</sub> -0.1 |                     |                    | V    |

| ICC2            | V <sub>CC</sub> Supply Active Current<br>TTL Levels | $CE = OE = V_{IL}$ , Inputs = $V_{IH}$ or<br>$V_{IL}$ , f = 5 MHz, I/O = 0 mA |                             | 10                  | 30                 | mA   |

| CCSB1           | V <sub>CC</sub> Supply Standby Current              | VIH or VIL                                                                    |                             | 0.05                | 1                  | mA   |

| ICCSB2          | V <sub>CC</sub> Supply Standby Current              | V <sub>CC</sub> - 0.1V or V <sub>SS</sub> + 0.1V                              |                             | 1                   | 10                 | μA   |

| IPP1            | VPP Read Current                                    | $V_{PP} = V_{CC} = 5.5V$                                                      |                             |                     | 10                 | μA   |

DC CHARACTERISTICS (Tamb = Tr to Tu, Vcc = 5V + 10%, Vcs = 0V; Unless otherwise specified)<sup>(5)</sup>

Note: 1. Typical conditions are for operation at: Tamb = +25°C, VCC = 5V, Vpp = VCC, and VSS = 0V

## AC CHARACTERISTICS(1)(Tamb = TL to TH)(5)

| Symbol Paramete                  | Parameter                                                          | Test Conditions                          | 27C256<br>-15 |     | 27C256<br>-17 |     | 5 27C25<br>-20 |     | 27C256<br>-25 |     | 27C256<br>-30 |     | Unit |

|----------------------------------|--------------------------------------------------------------------|------------------------------------------|---------------|-----|---------------|-----|----------------|-----|---------------|-----|---------------|-----|------|

|                                  |                                                                    |                                          | Min           | Max | Min           | Max | Min            | Max | Min           | Max | Min           | Max |      |

| tACC                             | Address to Output Delay                                            | CE = OE = VIL                            |               | 150 |               | 170 |                | 200 |               | 250 |               | 300 | ns   |

| tCE                              | CE to Output Delay                                                 | $\overline{OE} = V_{ L}$                 |               | 150 |               | 170 |                | 200 |               | 250 | 300           | ns  |      |

| <sup>t</sup> OE                  | Output Enable to<br>Output Delay                                   | CE = V <sub>IL</sub>                     |               | 75  |               | 75  |                | 75  |               | 100 |               | 120 | ns   |

| t <sub>DF</sub> <sup>(2,4)</sup> | OE or CE High to<br>output float                                   |                                          | 0             | 50  | 0             | 50  | 0              | 55  | 0             | 60  | 0             | 75  | ns   |

| tон                              | Output Hold from<br>addresses, CE or OE<br>whichever occured first | $\overline{CE} = \overline{OE} = V_{ L}$ | 0             |     | 0             |     | 0              |     | 0             |     | 0             |     | ns   |

## CAPACITANCE Tamb = + 25°C, f = 1 MHz (Note 3)

| Symbol | Parameter          | Conditions            | Min. | Тур. | Max. | Unit |

|--------|--------------------|-----------------------|------|------|------|------|

| Cin    | Input Capacitance  | $V_{IN} = 0V$         |      | 4    | 6    | pF   |

| Cout   | Output Capacitance | V <sub>OUT</sub> = 0V |      | 8    | 12   | pF   |

Notes: 1. V<sub>CC</sub> must be applied at the same time or before Vpp and removed after or at the same time as Vpp-Vpp may be connected to V<sub>CC</sub> except during program.

to V<sub>CC</sub> except ourning program 2. The t<sub>DF</sub> compare level is determined as follows: High to THREE-STATE, the measured V<sub>OH</sub>(DC) - 0.1VLow to THREE-STATE the measured V<sub>OH</sub>(DC) + 0.1V.

Capacitance is guaranteed By periodic testing. T<sub>amb</sub> = +25°C, f = 1MHz.

T<sub>DF</sub>, is specified from OE or CE whichever occurs first. This parameter is only sampled and not 100% tested.

All parameters are specified at V<sub>CC</sub> = 5V ±5% for 27C256-15X, 27C256-17X, 27C256-20X, 27C256-25X and 27C256-30X.

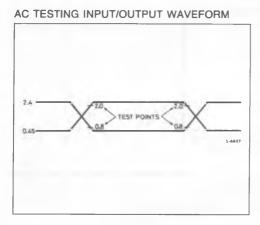

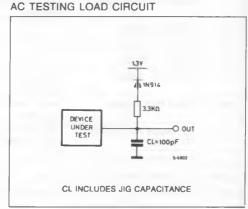

## AC TEST CONDITIONS

Output Load: 1 TTL gate and CL = 100 pF Input Rise and Fall Times ≤20 ns Input pulse levels: 0.45V to 2.4V Timing Measurement Reference Level Inputs, Outputs 0.8V and 2V

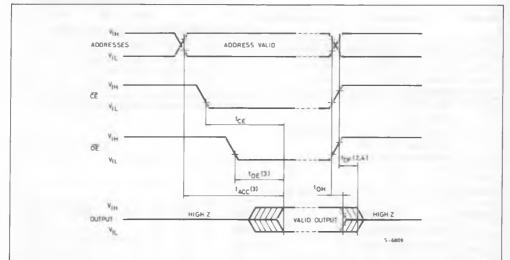

## AC WAVEFORMS

#### Notes:

- 1. Typical values are for  $T_{amb} = 25^{\circ}C$  and nominal supply voltage 2. This parameter is only sampled and not 100% tested.

- OE may be delayed up to tacc toE after the falling edge CE without impact on tacc

toFis specified form OE or CE whichever occurs first

#### **DEVICE OPERATION**

The seven modes of operation of the TS27C256 are listed in the Operating Modes table. A single 5V power supply is required in the read mode. All inputs are TTL levels except for  $V_{pp}$ .

#### READ MODE

The TS27C256 has two control functions, both of wich must be logically active in order to obtain data at the outputs. Chip Enable (CE) is the power control and should be used for device selection. Output Enable (OE) is the output control and should be used to gate data to the output pins, independent of device selection. Assuming that addresses are stable, address access time ( $t_{ACC}$ ) is equal to the outputs after a delay of  $t_{OE}$  from the falling edge of OE, assuming that CE has been low and addresses have been stable for at least  $t_{ACC}$ -toE.

#### STANDBY MODE

The TS27C256 has a standby mode which reduces the maximum power dissipation to 5.5 mW. The TS27C256 is placed in the standby mode by applying a TTL high signal to the CE input. When in standby mode, the outputs are in a high impedance state, independent of the OE input.

#### **OUTPUT OR-TYING**

Because EPROMs are usually used in larger memory arrays, we have provided two control lines which accomodate this multiple memory connection. The two control lines allow for:

- a) the lowest possible memory power dissipation, and

- b) complete assurance that output bus contention will not occur.

To use these control lines most efficiently, CE (pin 20) should be decoded and used as the primary device selecting function, while OE (pin 22) should be made a common connection to all devices in the array and connected to the READ line from the system control bus. This assures that all deselected memory devices are in their low power standby modes and that the output pins are active only when data is desired from a particular memory device.

#### PROGRAMMING MODES

#### Caution: Exceeding 14V on pin 1 (V<sub>pp</sub>) will damage the TS27C256.

Initially, and after each erasure, all bits of the TS27C256 are in the "1" state. Data is introduced by selectively programming "0s" into the desired bit locations. Although only "0s" will be programmed, both "1s" and "0s" can be presented in the data word. The only way to change a "0" to a "1" is by ultraviolet light erasure.

The TS27C256 is in the programming mode when the V<sub>pp</sub> input is at 12.5 V and CE is at TTL Low. It is required that a 0.1  $\mu$ F capacitor be placed across V<sub>pp</sub>, V<sub>CC</sub> and ground to suppress spurious voltage transients which may damage the device. The data to be programmed is applied 8 bits in parallel to the data output pins. The levels required for the address and data inputs are TTL.

Programming of multiple TS27C256s in parallel with the same data can be easily accomplished due to the simplicity of the programming requirements. Like inputs of the parallel TS27C256s may be connected together when they are programmed with the same data. A low level TTL pulse applied to the CE input programs the paralleled TS27C256s.

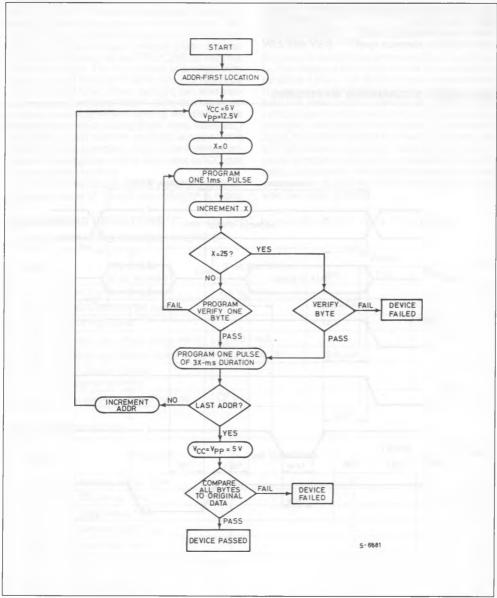

#### HIGH SPEED PROGAMMING

The high speed programming algorithm described in the flow chart rapidly programs TS27C256 using an efficient and reliable method particularly suited to the production programming environment. Typical programming times for individual devices are on the order of 5 minutes.

#### **PROGRAM INHIBIT**

Programming of multiple TS27C256s in parallel with different data is also easily accomplished by using the program inhibit mode. A high level on CE input inhibits the other TS27C256s from being programmed. Except for CE, all like inputs (including OE) of the parallel TS27C256s may be common. A TTL low-level pulse applied to a TS27C256 CE input with  $V_{pp}$  at 12.5 V will program that TS27C256.

#### PROGRAM VERIFY

A verify may be performed on the programmed bits to determine that they were correctly programmed. The verify is performed with OE at  $V_{IL}$ , CE at  $V_{IH}$  and  $V_{DD}$  at 12.5 V.

#### ELECTRONIC SIGNATURE MODE

Electronic signature mode allows the reading out of a binary code that will indentify the EPROM manufacturer and type. This mode is intended for use by programming equipment for the purpose of automatically matching the device to be programmed with its corresponding programming algorithm. This mode is functional in the  $25^{\circ}C \pm 5^{\circ}C$  ambient temperature range that is required when programming the TS27C256. To activate this mode the programming equipment must force 11.5V to 12.5V on address line A9 (pin 24) of the TS27C256. Two bytes may then be sequenced from the device outputs by toggling address line A0 (pin 10) from V<sub>IL</sub> to V<sub>IH</sub>. All other address lines must be held at V<sub>IL</sub> during electonic signature mode.

#### ERASING

The TS27C256 is erased by exposure to high intensity ultraviolet light through the transparent window. This exposure discharges the floating gate to its initial state through induced photo current. It is recommended that the TS27C256 be kept out of direct sunlight. The UV content of sunlight may cause a partial erasure of some bits in a relatively short period of time. Direct sunlight can also cause temporary functional failure. Extended exposure to room level fluorescent lighting will also cause erasure. An opaque coating (paint, tape, label, etc.) should be placed over the package window if this product is to be operated under these lighting conditions. Covering the window also reduces ICC due to photodiode currents.

An ultraviolet source of 2537A yielding a total integrated dosage of 15 watt-seconds/cm<sup>2</sup> is required. This will erase the part in approximately 15 to 20 minutes if a UV lamp with a 12,000  $\mu$ W/cm<sup>2</sup> power rating is used. The TS27C256 to be erased should be placed 1 inch from the lamp and no filters should be used.

An erasure system should be calibrated periodically. The distance from lamp to unit should be maintained at 1 inch. The erasure time is increased by the square of the distance (if the distance is doubled the erasure time goes up by a factor of 4). Lamps lose intensity as they age. When a lamp is changed, the distance is changed, or the lamp is aged, the system should be checked to make certain full erasure is occuring. Incomplete erasure will cause symptoms that can be misleading. Programmers, components, and system designs have been erroneously suspected when incomplete erasure was the basic problem.

## **PROGRAMMING OPERATIONS**<sup>(1)</sup>( $T_{amb} = 25 \pm 5^{\circ}C$ , $V_{CC} = 6.0V \pm 0.25V$ , $V_{PP} = 12.5V \pm 0.3V$ )

## DC AND OPERATING CHARACTERISTICS

| Symbol         | Parameter                                            | Test Oreditions                                     |       | 11-14 |                     |      |

|----------------|------------------------------------------------------|-----------------------------------------------------|-------|-------|---------------------|------|

|                | Parameter                                            | Test Conditions                                     | Min.  | Тур.  | Max.                | Unit |

| l <sub>l</sub> | Input Current (all inputs)                           | V <sub>I</sub> = V <sub>IL</sub> or V <sub>IH</sub> |       |       | 10                  | μA   |

| VIL            | Input Low Level (all inputs)                         |                                                     | - 0.1 |       | 0.8                 | V    |

| VIH            | Input High Level                                     |                                                     | 2.0   |       | V <sub>CC</sub> + 1 | V    |

| VOL            | Output low voltage during verify                     | I <sub>OL</sub> = 2.1 mA                            |       |       | 0.45                | V    |

| VOH            | Output high voltage during verify                    | $I_{OH} = -400 \ \mu A$                             | 2.4   |       |                     | V    |

| ICC3           | V <sub>CC</sub> Supply current<br>(Program & Verify) |                                                     |       |       | 30                  | mA   |

| IPP2           | V <sub>PP</sub> supply current (Program)             | CE = VIL                                            |       |       | 30                  | mA   |

### AC CHARACTERISTICS

| Symbol              | Parameter                           | Test Ore distant |      | 11-10 |       |      |

|---------------------|-------------------------------------|------------------|------|-------|-------|------|

| Symbol              | Parameter                           | Test Conditions  | Min. | Тур.  | Max.  | Unit |

| t <sub>AS</sub>     | Address Set-up Time                 |                  | 2    |       |       | μS   |

| tOES                | OE Set-up Time                      |                  | 2    |       |       | μS   |

| tDS                 | Data Set-up Time                    |                  | 2    |       |       | μS   |

| t <sub>AH</sub>     | Address Hold Time                   |                  | 0    |       |       | μS   |

| tDH                 | Data Hold Time                      |                  | 2    |       |       | μS   |

| tDFP                | Output enable to output float delay |                  | 0    |       | 130   | ns   |

| tvps                | V <sub>PP</sub> set-up time         |                  | 2    |       |       | μS   |

| tvcs                | V <sub>CC</sub> set-up time         |                  | 2    |       |       | μS   |

| tpw                 | PGM initial program pulse width     |                  | 0.95 | 1.0   | 1.05  | ms   |

| topw <sup>(2)</sup> | PGM overprogram pulse width         |                  | 2.85 |       | 78.75 | ms   |

| tOE                 | Data valid from OE                  |                  |      |       | 150   | ns   |

Notes: 1. V<sub>CC</sub> must be applied simultaneously or before V<sub>PP</sub> and removed simultaneously or after V<sub>PP</sub>.

2. t<sub>OPW</sub> is defined in flow chart.

## AC TEST CONDITIONS

| Input rise and fall times (10% t | o 90%) ≤20ns  |

|----------------------------------|---------------|

| Input pulse levels               | 0.45V to 2.4V |

| Input timing reference level     | 0.8V and 2.0V |

| Output timing reference level    | 0.8V and 2.0V |

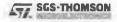

## HIGH SPEED PROGRAMMING WAVEFORMS

1. The input timing reference level is 0.8 for VIL and 2.0V for VIH

2. top and topp are characteristics of the device but must be accommodate by the programmer.

3. When programming the TS27C256, a 0.1 µF capacitor is required across Vpp and ground to suppress spurious voltage transiens which can damage the device.

## HIGH SPEED PROGRAMMING FLOW CHART

## ORDERING INFORMATION

| Part Number    | Access Time | Supply Voltage | Temp. Range    | Package |

|----------------|-------------|----------------|----------------|---------|

| TS27C256-15XCQ | 150 ns      | 5V± 5%         | 0 to + 70°C    | DIP-28  |

| TS27C256-17XCQ | 170 ns      | 5V± 5%         | 0 to + 70°C    | DIP-28  |

| TS27C256-20XCQ | 200 ns      | 5V± 5%         | 0 to + 70°C    | DIP-28  |

| TS27C256-25XCQ | 250 ns      | 5V± 5%         | 0 to + 70°C    | DIP-28  |

| TS27C256-30XCQ | 300 ns      | 5V± 5%         | 0 to + 70°C    | DIP-28  |

| TS27C256-17CQ  | 170 ns      | 5V ± 10%       | 0 to + 70°C    | DIP-28  |

| TS27C256-20CQ  | 200 ns      | 5V ± 10%       | 0 to +70°C     | DIP-28  |

| TS27C256-25CQ  | 250 ns      | 5V ± 10%       | 0 to + 70°C    | DIP-28  |

| TS27C256-30CQ  | 300 ns      | 5V ± 10%       | 0 to + 70°C    | DIP-28  |

| TS27C256-15VQ  | 150 ns      | 5V ± 5%        | - 40 to + 85°C | DIP-28  |

| TS27C256-17VQ  | 170 ns      | 5V ± 10%       | - 40 to + 85°C | DIP-28  |

| TS27C256-20VQ  | 200 ns      | 5V ± 10%       | - 40 to + 85°C | DIP-28  |

| TS27C256-25VQ  | 250 ns      | 5V ± 10%       | - 40 to + 85°C | DIP-28  |

| TS27C256-30VQ  | 300 ns      | 5V ± 10%       | - 40 to + 85°C | DIP-28  |

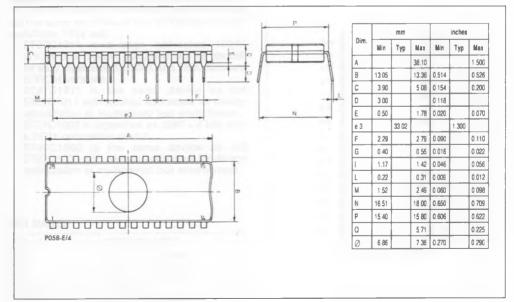

## PACKAGE MECHANICAL DATA

28-PIN CERAMIC DIP BULL'S EYE