Order

Now

#### TPS23880

SLUSD53A-MARCH 2018-REVISED MAY 2018

# TPS23880 High-Power, 8-Channel, Power-over-Ethernet PSE With Programmable SRAM

Technical

Documents

### 1 Features

- IEEE 802.bt (Draft) PSE Solution for Type 3 or Type 4 PoE Applications

- Eight Independent PSE Channels

- SRAM Programmable Memory

- Selectable 2-Pair or 4-Pair Port Power Allocations

15.4 W, 30 W, 45 W, 60 W, 75 W, or 90 W

- Single and Dual Signature PD Compatibility

- Dedicated 14-BitCurrent A2Ds Per Port

- Inherent Filtering

- 2% Current Sensing Accuracy

- 100-ms Rolling Port Current Averaging

- Noise Immune MPS for DC Disconnect

- 1- and 3-Bit Fast Port Shutdown Input

- "Never Fooled" 4-Point Detection

- Programmable Power Limiting Accuracy +/- 3%

- Inrush and Operational Foldback Protection

- 425-mA and 1.25-A Selectable Current Limit

- Port Re-Mapping

- Auto-Class Discovery and Power Measurement

- 8-Bit or 16-Bit 1 MHz I<sup>2</sup>C Communication

- Flexible Processor Controlled Operating Modes

Auto, Semi Auto, and Manual / Diagnostic

- Per Port Voltage Monitoring and Telemetry

- -40°C to +125°C Temperature Operation

# 2 Applications

- Enterprise and SoHO Switches and Routers

- Connected Ceiling LED Lighting Switches

- PoE Pass-Through Power Modules

- Network Video Recorders (NVRs)

- Wireless Backhaul and Small Cell Networking

# 3 Description

Tools &

Software

The TPS23880 is an 8-channel power sourcing equipment (PSE) controller engineered to insert power onto Ethernet cables in accordance with the IEEE 802.3bt (draft) standard. The eight individual power channels can be configured in any combination of 2-Pair (1-channel) or 4-Pair (2-channels) PoE Ports. The PSE controller can detect powered devices (PDs) that have a valid signature, determine the power requirements of the devices according to their classification, and apply power.

Support &

Community

20

Programmable SRAM enables in field firmware upgradability over I<sup>2</sup>C to ensure maximum interoperability with the latest PoE enabled devices. The external FET architecture allows designs to balance size, efficiency, thermal, and solution cost requirements. The programmable port power limit provides stable power limiting over the entire operating voltage range, and accurate telemetry ensures reliable system level power management control. The Fast Shutdown (OSS) input provides up to eight levels of per port shutdown priority for applications requiring immediate disabling of multiple ports.

Port remapping and pin-to-pin compatibility with the TPS2388 eases migration from previous generation PSE designs and enables interchangeable 2-layer PCB designs to accommodate different system PoE power configurations.

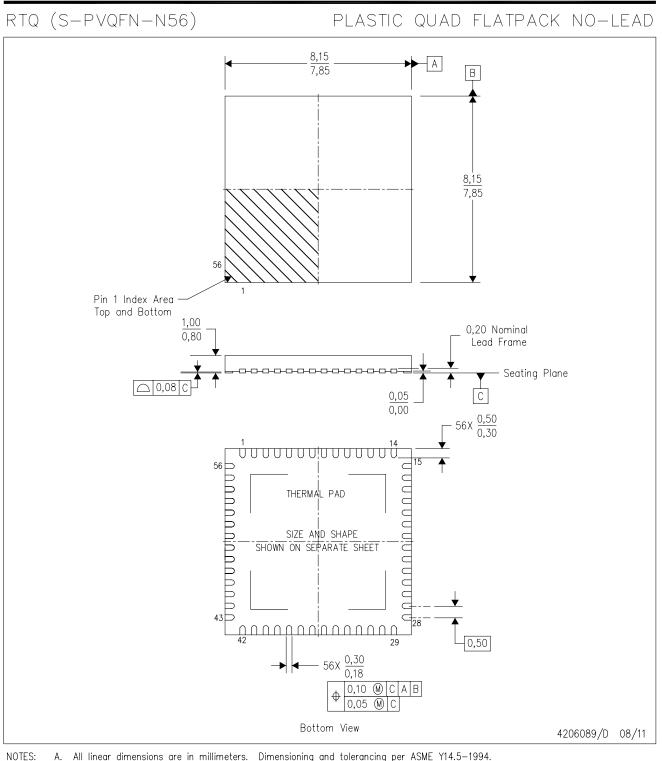

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |  |  |  |  |

|-------------|-----------|-------------------|--|--|--|--|

| TPS23880    | VQFN (56) | 8.00 mm × 8.00 mm |  |  |  |  |

For all available packages, see the orderable addendum at the end of the data sheet.

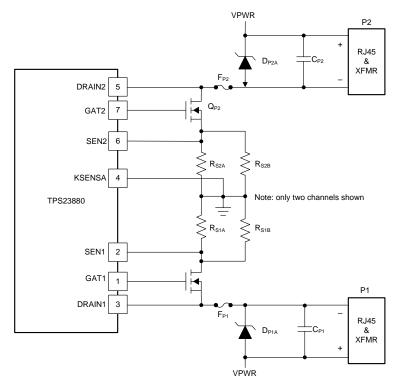

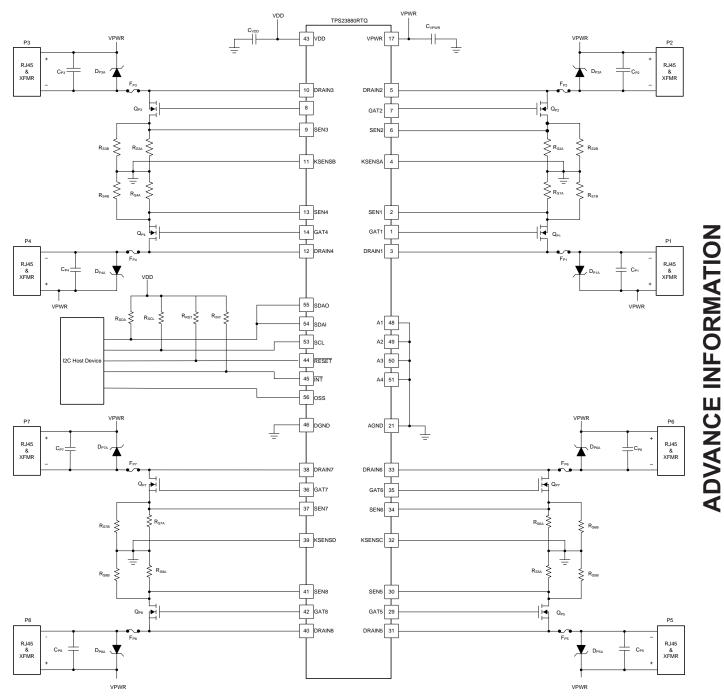

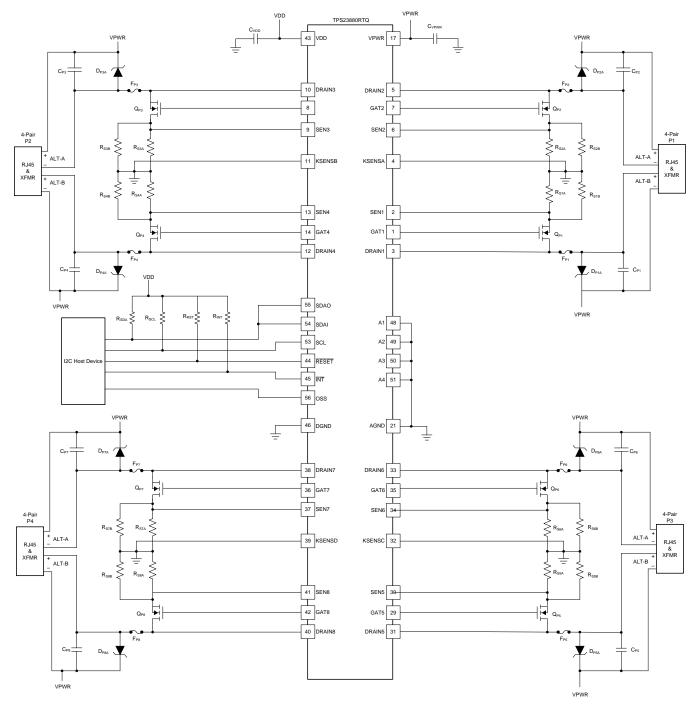

#### +3.3 1 RJ45 & XFrm DRAI RAIN3 H R 145 & XEm AT3 EN3 SEN 2P Port #2 0.255 Ω **≤** 255 0 0.1 μF 100 V RJ45 & XFrm \_\_\_\_\_\_ .255 Ω 0 255 0 SEL L. :Δ**Τ**Δ GAT 2P Port #3 DRAIN RAIN. RJ45 & XFrr 4P Port #2 Alt A RJ45 & XFrmr 2P Port #4 Alt B RJ45 & XFm

### **Simplified Schematic**

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. ADVANCE INFORMATION for pre-production products; subject to change without notice.

# **Table of Contents**

8

9

11.1

11.2

11.3

11.4

12

| 1 | Feat | tures 1                            |

|---|------|------------------------------------|

| 2 | Арр  | lications 1                        |

| 3 | Des  | cription 1                         |

| 4 | Rev  | ision History 2                    |

| 5 | Pin  | Configuration and Functions 3      |

|   | 5.1  | Detailed Pin Description 4         |

| 6 | Spe  | cifications6                       |

|   | 6.1  | Absolute Maximum Ratings 6         |

|   | 6.2  | ESD Ratings 6                      |

|   | 6.3  | Recommended Operating Conditions 6 |

|   | 6.4  | Thermal Information 6              |

|   | 6.5  | Electrical Characteristics7        |

| 7 | Deta | ailed Description 13               |

|   | 7.1  | Overview 13                        |

|   | 7.2  | Functional Block Diagram 15        |

|   | 7.3  | Feature Description 16             |

|   | 7.4  | Device Functional Modes 18         |

|   | 7.5  | Programming 19                     |

|   |      |                                    |

#### Revision History 4

| Cł | nanges from Original (March 2018) to Revision A Pa                        | age |

|----|---------------------------------------------------------------------------|-----|

| •  | Changed from Restricted Advance Information to Public Advance Information | 1   |

| Copyright © 2018, | Texas Instruments | Incorporated |

|-------------------|-------------------|--------------|

#### EXAS **ISTRUMENTS**

7.6 Register Maps ...... 22 Application and Implementation ...... 88

10.1 Layout Guidelines ...... 95 11 Device and Documentation Support ...... 98

Receiving Notification of Documentation Updates 98

Mechanical, Packaging, and Orderable

www.ti.com

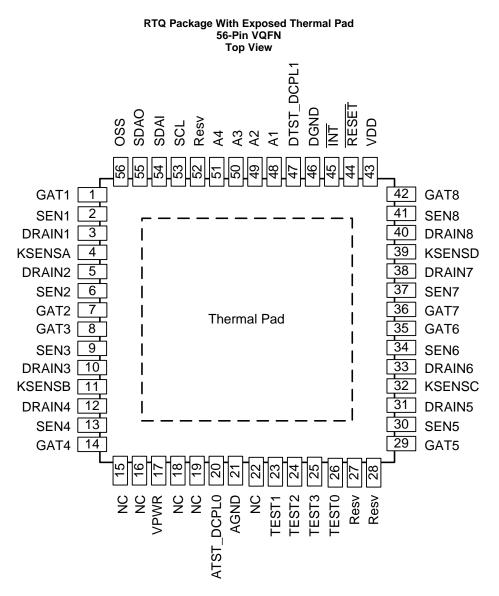

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN        |                                 | 1/0 | DESCRIPTION                                                                                                         |

|------------|---------------------------------|-----|---------------------------------------------------------------------------------------------------------------------|

| NAME       | NO.                             | 1/0 | DESCRIPTION                                                                                                         |

| A1-4       | 48–51                           | Т   | I <sup>2</sup> C A1-A4 address lines. These pins are internally pulled up to VDD.                                   |

| AGND       | 21                              | —   | Analog ground. Connect to GND plane and exposed thermal pad.                                                        |

| ATST_DCPL0 | 20                              | 0   | Used for internal test purposes, no bypass capacitor is needed.                                                     |

| DGND       | 46                              | —   | Digital ground. Connect to GND plane and exposed thermal pad.                                                       |

| DRAIN1-8   | 3, 5, 10, 12, 31,<br>33, 38, 40 | I   | Channel 1-8 output voltage monitor.                                                                                 |

| DTST_DCPL1 | 47                              | 0   | Used for internal test purposes, no bypass capacitor is needed.                                                     |

| GAT1-8     | 1, 7, 8, 14, 29,<br>35, 36, 42  | 0   | Channel 1-8 gate drive output.                                                                                      |

| INT        | 45                              | 0   | Interrupt output. This pin asserts low when a bit in the interrupt register is asserted. This output is open-drain. |

| KSENSA/B   | 4, 11                           | Т   | Kelvin point connection for SEN1-4                                                                                  |

| KSENSC/D   | 32, 39                          | Ι   | Kelvin point connection for SEN5-8                                                                                  |

Copyright © 2018, Texas Instruments Incorporated

**NSTRUMENTS**

FXAS

### Pin Functions (continued)

| PIN<br>NAME NO. |                                | 1/0 | DECODIDEION                                                                                                                              |

|-----------------|--------------------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------|

|                 |                                | 1/0 | DESCRIPTION                                                                                                                              |

| NC              | 15, 16, 18, 19                 | 0   | No connect pins. These pins are internally biased at 1/3 and 2/3 of VPWR in order to control the voltage gradient from VPWR. Leave open. |

| 22              |                                | —   | No connect pin. Leave open.                                                                                                              |

| OSS             | 56                             | I   | Channel 1-8 fast shutdown. This pin is internally pulled down to DGND.                                                                   |

| RESET           | 44                             | Ι   | Reset input. When asserted low, the TPS23880 is reset. This pin is internally pulled up to VDD.                                          |

| Resv            | 27, 28, 52                     | —   | Reserved. No connect pins. Leave open.                                                                                                   |

| SCL             | 53                             | I   | Serial clock input for I <sup>2</sup> C bus.                                                                                             |

| SDAI            | 54                             | I   | Serial data input for I <sup>2</sup> C bus. This pin can be connected to SDAO for non-isolated systems.                                  |

| SDAO            | 55                             | 0   | Serial data output for I <sup>2</sup> C bus. This pin can be connected to SDAI for non-isolated systems. This output is open-<br>drain.  |

| SEN1-8          | 2, 6, 9, 13, 30,<br>34, 37, 41 | I   | Channel 1-8 current sense input.                                                                                                         |

| TEST0-3         | 23, 24, 25, 26                 | I/O | Used internally for test purposes only. Leave open.                                                                                      |

| Thermal pad     | —                              | _   | The DGND and AGND terminals must be connected to the exposed thermal pad for proper operation.                                           |

| VDD             | 43                             | —   | Digital supply. Bypass with 0.1 µF to DGND pin.                                                                                          |

| VPWR            | 17                             | _   | Analog 54-V positive supply. Bypass with 0.1 µF to AGND pin.                                                                             |

### 5.1 Detailed Pin Description

The following descriptions refer to the pinout and the functional block diagram.

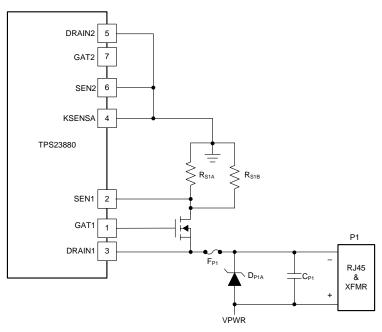

**DRAIN1-DRAIN8:** Channels 1-8 output voltage monitor and detect sense. Used to measure the port output voltage, for port voltage monitoring, port power good detection and foldback action. Detection probe currents also flow into this pin.

The TPS23880 uses an innovative 4-point technique to provide reliable PD detection. The discovery is performed by sinking two different current levels via the DRAINn pin, while the PD voltage is measured from VPWR to DRAINn. The 4-point measurement provides the capability to avoid powering a capacitive or legacy load. Also, while in semiauto mode, if prior to starting a new detection cycle the port voltage is >2.5 V, an internal 100-k $\Omega$  resistor is connected in parallel with the port and a 400-ms detect backoff period is applied to allow the port capacitor to be discharged before the detection cycle starts.

There is an internal resistor between each DRAINn pin and VPWR in any operating mode except during detection or while the port is ON. If the port n is not used, DRAINn can be left floating or tied to AGND.

**GAT1-GAT8:** Channels 1-8 gate drive outputs are used for external N-channel MOSFET gate control. At port turn on, it is driven positive by a low current source to turn the MOSFET on. GATn is pulled low whenever any of the input supplies are low or if an overcurrent timeout has occurred. GATn is also pulled low if the port is turned off by use of manual shutdown inputs. Leave floating if unused.

For a robust design, a current foldback function limits the power dissipation of the MOSFET during low resistance load or a short-circuit event. During inrush, the foldback mechanism measures the port voltage across VPWR and DRAINn to reduce the current limit threshold.

While a port is on and its  $P_{CUT}$  threshold is exceeded, a timer starts. During that time, linear current limiting ensures the current does not exceed  $I_{LIM}$  combined with current foldback action. When the timer reaches the  $t_{OVLD}$  (or  $t_{START}$  if at port turn on) limit, the port shuts off. When the port current goes below  $P_{CUT}$ , the counter counts down at a rate  $1/16^{th}$  of the increment rate and the counter must reach a count of 0 before the port can be turned on again.

The fast overload protection is for major faults like a direct short. This forces the MOSFET into current limit in less than a microsecond.

The circuit leakage paths between the GATn pin and any nearby DRAINn pin, GND or Kelvin point connection must be minimized (< 250 nA), to ensure correct MOSFET control.

**INT:** This interrupt output pin asserts low when a bit in the interrupt register is asserted. This output is open-drain.

### Detailed Pin Description (continued)

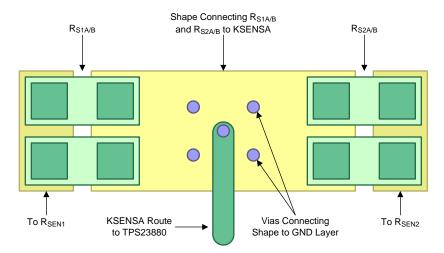

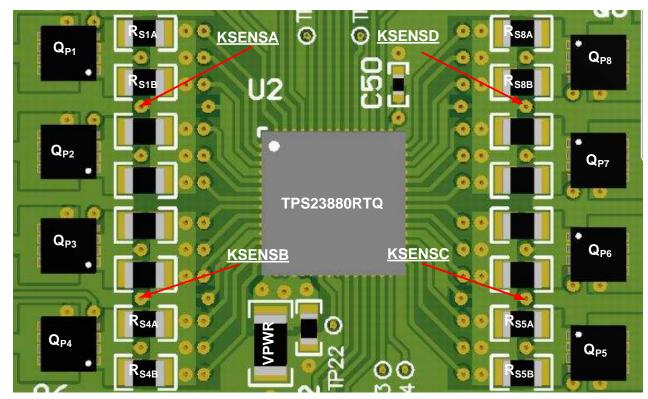

**KSENSA, KSENSB, KSENSC, KSENSD:** Kelvin point connection used to perform a differential voltage measurement across the associated current sense resistors.

Each KSENS is shared between two neighbor SEN pins as following: KSENSA with SEN1 and SEN2, KSENSB with SEN3 and SEN4, KSENSC with SEN5 and SEN6, KSENSD with SEN7 and SEN8. To optimize the measurement accuracy, ensure proper PCB layout practices are followed. See the *Port Current Kelvin Sensing* section for more details.

**OSS:** Fast shutdown, active high. This pin is internally pulled down to DGND, with an internal 1-µs to 5-µs deglitch filter.

The turn off procedure is similar to a port reset using Reset command (1Ah register). The 3-bit OSS function allows for a series of pulses on the OSS pin to turn off individual or multiple ports with up to 8 levels of priority.

**RESET:** Reset input, active low. When asserted, the TPS23880 resets, turning off all ports and forcing the registers to their power-up state. This pin is internally pulled up to VDD, with internal 1-µs to 5-µs deglitch filter. The designer can use an <u>external</u> RC network to delay the turn-on. There is also an internal power-on-reset which is independent of the RESET input.

**SCL:** Serial clock input for I<sup>2</sup>C bus.

**SDAI:** Serial data input for I<sup>2</sup>C bus. This pin can be connected to SDAO for non-isolated systems.

**SDAO:** Open-drain I<sup>2</sup>C bus output data line. Requires an external resistive pull-up. The TPS23880 uses separate SDAO and SDAI lines to allow optoisolated I<sup>2</sup>C interface. SDAO can be connected to SDAI for non-isolated systems.

A4-A1: I<sup>2</sup>C bus address inputs. These pins are internally pulled up to VDD. See *Pin Status Register* for more details.

**SEN1-8:** Channel current sense input relative to KSENSn (see KSENSn description). A differential measurement is performed using KSENSA-D Kelvin point connection. Monitors the external MOSFET current by use of a 0.255- $\Omega$  current sense resistor connected to DGND. Used by current foldback engine and also during classification. Can be used to perform load current monitoring via A/D conversion.

When the TPS23880 performs the classification measurements, the current flows through the external MOSFETs. This avoids heat concentration in the device and makes it possible for the TPS23880 to perform classification measurements on multiple ports at the same time. For the current limit with foldback function, there is an internal 2- $\mu$ S analog filter on the SEN1-8 pins to provide glitch filtering. For measurements through an A/D converter, an anti-aliasing filter is present on the SEN1-8 pins. This includes the port-powered current monitoring, port policing, and DC disconnect.

If the port is not used, tie SENn to AGND.

**VDD:** 3.3-V logic power supply input.

**VPWR:** High voltage power supply input. Nominally 54 V.

**TPS23880**

SLUSD53A - MARCH 2018 - REVISED MAY 2018

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                        | MIN  | MAX | UNIT |

|------------------|----------------------------------------|------|-----|------|

|                  | VPWR                                   | -0.3 | 70  | V    |

|                  | VDD                                    | -0.3 | 4   | V    |

|                  | OSS, RESET, A1-A4                      | -0.3 | 4   | V    |

|                  | SDAI, SDAO, SCL, INT                   | -0.3 | 4   | V    |

| Voltage          | SEN1-8, KSENSA, KSENSB, KSENSC, KSENSD | -0.3 | 3   | V    |

|                  | GATE1-8                                | -0.3 | 12  | V    |

|                  | DRAIN1-8                               | -0.3 | 70  | V    |

|                  | TEST0-3, ATST_DCPL0, DTST_DCPL1        | -0.3 | 4   | V    |

|                  | AGND                                   | -0.3 | 0.3 | V    |

| Sink Current     | INT, SDA                               |      | 20  | mA   |

| Lead Temperat    | ure 1/6mm from case for 10 seconds     |      | 260 | °C   |

| T <sub>stg</sub> | Storage temperature                    | -65  | 150 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Rating may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Condition. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                                         | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------------------------|-------|------|

| V                  | Electrostatio discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, allpins <sup>(1)</sup>              | ±2000 | V    |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specificationJESD22-C101, all pins <sup>(2)</sup> | ± 500 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                                     | MIN | NOM | MAX | UNIT |

|-------------------------------------|-----|-----|-----|------|

| V <sub>VDD</sub>                    | 3   | 3.3 | 3.6 | V    |

| V <sub>VPWR</sub>                   | 44  | 54  | 57  | V    |

| Voltage Slew rate on VPWR           |     |     | 1   | V/µs |

| T <sub>J</sub> Junction temperature | -40 |     | 125 | °C   |

### 6.4 Thermal Information

|                       |                                              | TPS23880           |      |

|-----------------------|----------------------------------------------|--------------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RTQ Package (VQFN) | UNIT |

|                       |                                              | 56 PINS            |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 25.3               | °C/W |

| $R_{\theta JC(top)}$  | Junction-to-case (top) thermal resistance    | 9.7                | °C/W |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 3.7                | °C/W |

| $\Psi_{\text{JT}}$    | Junction-to-top characterization parameter   | 0.2                | °C/W |

| $\Psi_{JB}$           | Junction-to-board characterization parameter | 3.7                | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 0.5                | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 6.5 Electrical Characteristics

|                           | PARAMETER                                          | TEST CONDITIONS                                                                                                            | MIN   | TYP   | MAX   | UNIT   |

|---------------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|

| INPUT SUPPL               | LY VPWR                                            | ·                                                                                                                          |       |       |       |        |

| I <sub>VPWR</sub>         | VPWR Current consumption                           | VVPWR = 54 V                                                                                                               |       | 10    | 12.5  | mA     |

| V <sub>UVLOPW_F</sub>     | VPWR UVLO falling threshold                        | Check internal oscillator stops operating                                                                                  | 14.5  |       | 17.5  | V      |

| V <sub>UVLOPW_R</sub>     | VPWR UVLO rising threshold                         |                                                                                                                            | 15.5  |       | 18.5  | V      |

| V <sub>PUV_F</sub>        | VPWR Undervoltage falling threshold                | VPUV threshold                                                                                                             | 25    | 26.5  | 28    | V      |

| INPUT SUPPL               | LY VDD                                             | · · · · · ·                                                                                                                |       |       |       |        |

| I <sub>VDD</sub>          | VDD Current consumption                            |                                                                                                                            |       | 6     | 12    | mA     |

| V <sub>UVDD_F</sub>       | VDD UVLO falling threshold                         | For channel deassertion                                                                                                    | 2.1   | 2.25  | 2.4   | V      |

| V <sub>UVDD_R</sub>       | VDD UVLO rising threshold                          |                                                                                                                            | 2.45  | 2.6   | 2.75  | V      |

| V <sub>UVDD_HYS</sub>     | Hysteresis VDD UVLO                                |                                                                                                                            |       | 0.35  |       | V      |

| V <sub>UVW_F</sub>        | VDD UVLO warning threshold                         |                                                                                                                            | 2.6   | 2.8   | 3     | V      |

| A/D CONVER                | TERS                                               |                                                                                                                            |       |       |       |        |

| T <sub>CONV_I</sub>       | Conversion time                                    | All ranges, each channel                                                                                                   | 0.64  | 0.8   | 0.96  | ms     |

| T <sub>CONV_V</sub>       | Conversiontime                                     | All ranges, each channel                                                                                                   | 0.82  | 1.03  | 1.2   | ms     |

| T <sub>INT_CUR</sub>      | Integration time, Current                          | Each channel, channel ON current                                                                                           | 82    | 102   | 122   | ms     |

| T <sub>INT DET</sub>      | Integration time, Detection                        |                                                                                                                            | 13.1  | 16.6  | 20    | ms     |

| T <sub>INT_channelV</sub> | Integration time, Channel Voltage                  | channel powered                                                                                                            | 3.25  | 4.12  | 4.9   | ms     |

| T <sub>INT_inV</sub>      | Integration time, Input Voltage                    |                                                                                                                            | 3.25  | 4.12  | 4.9   | ms     |

|                           | Input voltage conversion scale factor and accuracy | VVPWR = 57 V                                                                                                               | 15175 | 15565 | 15955 | Counts |

|                           |                                                    |                                                                                                                            | 55.57 | 57    | 58.43 | V      |

|                           |                                                    | VVPWR = 44 V                                                                                                               | 11713 | 12015 | 12316 | Counts |

|                           |                                                    |                                                                                                                            | 42.89 | 44    | 45.10 | V      |

|                           |                                                    | VVPWR - VDRAINn = 57 V                                                                                                     | 15175 | 15565 | 15955 | Counts |

|                           | Powered Channel voltage conversion                 |                                                                                                                            | 55.57 | 57    | 58.43 | V      |

|                           | scale factor and accuracy                          | VVPWR - VDRAINn = 44 V                                                                                                     | 11713 | 12015 | 12316 | Counts |

|                           |                                                    |                                                                                                                            | 42.89 | 44    | 45.10 | V      |

| $\delta V/V_{Channel}$    | Voltage reading accuracy                           |                                                                                                                            | -3    |       | 3     | %      |

| σV                        | Voltage Reading Repeatability                      | Full-scale reading                                                                                                         | -18   |       | 18    | mV     |

|                           |                                                    |                                                                                                                            | 10750 | 10970 | 11190 | Counts |

|                           | Powered Channel current conversion                 | Channel current = 770 mA                                                                                                   | 754.5 | 770   | 785.4 | mA     |

|                           | scale factor and accuracy                          |                                                                                                                            | 85    | 107   | 130   | Counts |

|                           |                                                    | Channel Current = 7.5 mA                                                                                                   | 5.966 | 7.5   | 9.125 | mA     |

|                           |                                                    | Channel Current =50 mA                                                                                                     | -3    |       | 3     |        |

| δl/I <sub>Channel</sub>   | Current reading accuracy                           | Channel Current =770 mA                                                                                                    | -2    |       | 2     | %      |

|                           | Powered Channel current ful scale                  |                                                                                                                            | 14959 | 15671 | -     | Counts |

|                           | output                                             | Channel currents = 1.15 A                                                                                                  | 1.05  | 1.1   |       | A      |

| σΙ                        | Current Reading Repeatability                      | Full Scale reading                                                                                                         | -7.5  |       | 7.5   | mA     |

| δR/R <sub>Channel</sub>   | Resistance reading accuracy                        | $15 \text{ k}\Omega \le \text{R}_{\text{Channel}} \le 33 \text{ k}\Omega, \text{ C}_{\text{Channel}} \le 0.25 \mu\text{F}$ | -7    |       | 7     | %      |

| I <sub>bias</sub>         | Sense Pin bias current                             | Channel ON or during class                                                                                                 | -2.5  |       | 0     | μA     |

#### **Electrical Characteristics (continued)**

|                          | PARAMETER                                                                               | TEST CONDITIONS                                                                                              | MIN  | TYP  | MAX  | UNIT   |

|--------------------------|-----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------|------|------|--------|

| GATE 1-8                 |                                                                                         |                                                                                                              |      |      |      |        |

| V <sub>GOH</sub>         | Gate drive voltage                                                                      | $V_{GATEn}$ , $I_{GATE}$ = -1 $\mu$ A                                                                        | 10   |      | 12.5 | V      |

| I <sub>GO-</sub>         | Gate sinking current with Power-on<br>Reset, OSS detected or channel turnoff<br>command | V <sub>GATEn</sub> = 5 V                                                                                     | 60   | 100  | 190  | mA     |

| I <sub>GO short-</sub>   | Gate sinking current with channel short-<br>circuit                                     | $V_{GATEn} = 5 V,$<br>$V_{SENn} \ge V_{short}$ (or $V_{short2X}$ if 2X mode)                                 | 60   | 100  | 190  | mA     |

| I <sub>GO+</sub>         | Gate sourcing current                                                                   | $V_{GATEn} = 0 V$ , default selection                                                                        | 39   | 50   | 63   | μA     |

| t <sub>D_off_OSS</sub>   | Gate turnoff time from 1-bit OSS input                                                  | From OSS to VGATEn < 1 V,<br>VSENn = 0 V, MbitPrty = 0                                                       | 1    |      | 5    | μs     |

| toss_off                 | Gate turnoff time from 3-bit OSS input                                                  | From Start bit falling edge to VGATEn <<br>1 V,<br>VSENn = 0 V, MbitPrty = 1                                 | 72   |      | 104  | μs     |

| $t_{P_off\_CMD}$         | Gate turnoff time from channel turnoff command                                          | From Channel off command to $V_{GATEn}$ < 1 V, $V_{SENn}$ = 0 V                                              |      |      | 300  | μs     |

| t <sub>P_off_RST</sub>   | Gate turnoff time with /RESET                                                           | From /RESET low to $V_{GATEn} < 1 V$ ,<br>$V_{SENn} = 0 V$                                                   | 1    |      | 5    | μs     |

| DRAIN 1-8                | ·                                                                                       | · · · · · ·                                                                                                  |      |      |      |        |

| V <sub>PGT</sub>         | Power-Good threshold                                                                    | Measured at V <sub>DRAINn</sub>                                                                              | 1    | 2.13 | 3    | V      |

| V <sub>SHT</sub>         | Shorted FET threshold                                                                   | Measured at V <sub>DRAINn</sub>                                                                              | 4    | 6    | 8    | V      |

| R <sub>DRAIN</sub>       | Resistance from DRAINn to VPWR                                                          | Any operating mode except during<br>detection or while the Channel is ON,<br>including in device RESET state | 80   | 100  | 190  | kΩ     |

| AUTOCLASS                |                                                                                         |                                                                                                              |      |      |      |        |

| t <sub>Class_ACS</sub>   | Start of Autoclass Detection                                                            | Measured from the start of Class                                                                             | 90   |      | 100  | ms     |

|                          |                                                                                         | Measured from the end of Inrush                                                                              | 1.4  |      | 1.6  | S      |

| t <sub>AUTO_PSE1</sub>   | Start of Autoclass Power Measurement                                                    | Measured from setting the MACx bit while channel is already powered                                          |      |      | 10   | ms     |

| t <sub>AUTO</sub>        | Duration of Autoclass Power<br>Measurement                                              |                                                                                                              | 1.7  | 1.8  | 1.9  | S      |

| t <sub>AUTO_window</sub> | Autoclass Power Measurement Sliding Window                                              |                                                                                                              | 0.15 |      | 0.3  | s      |

| D                        | Autoclass Channel Power conversion                                                      | VPWR = 52 V, VDRAINn = 0 V,<br>Channel current = 770 mA                                                      | 76   | 80   | 84   | Counts |

| P <sub>AC</sub>          | scale factor and accuracy                                                               | VPWR = 50 V, VDRAINn = 0 V,<br>Channel current = 100 mA                                                      | 9    | 10   | 11   |        |

#### **Electrical Characteristics (continued)**

| PARAMETER                |                                           | TEST CONDITIONS                                                         | MIN  | TYP  | MAX  | UNIT |

|--------------------------|-------------------------------------------|-------------------------------------------------------------------------|------|------|------|------|

| DETECTION                | I                                         |                                                                         |      |      |      |      |

|                          | Detection ourrent                         | First and 3rd detection points<br>VVPWR - VDRAINn = 0 V                 | 145  | 160  | 190  | ۵    |

| DISC                     | Detection current                         | 2nd and 4th detection points VVPWR -<br>VDRAINn = 0 V                   | 235  | 270  | 300  | μA   |

| $\Delta I_{\text{DISC}}$ | 2nd – 1st detection currents              | VVPWR - VDRAINn = 0 V                                                   | 98   | 110  | 118  | μA   |

| V <sub>det_open</sub>    | Open circuit detection voltage            | Measured as VVPWR - VDRAINn                                             | 23.5 | 26   | 29   | V    |

| R <sub>REJ_LOW</sub>     | Rejected resistance low range             |                                                                         | 0.86 |      | 15   | kΩ   |

| R <sub>REJ_HI</sub>      | Rejected resistance high range            |                                                                         | 33   |      | 100  | kΩ   |

| R <sub>ACCEPT</sub>      | Accepted resistance range                 |                                                                         | 19   | 25   | 26.5 | kΩ   |

| R <sub>SHORT</sub>       | Shorted Channel threshold                 |                                                                         |      |      | 360  | Ω    |

| R <sub>OPEN</sub>        | Open Channel Threshold                    |                                                                         | 400  |      |      | kΩ   |

| t <sub>DET</sub>         | Detection Duration                        | Time to complete a detection, $4Pxx = 0$                                | 275  | 350  | 425  | ms   |

| t <sub>CC</sub>          | Connection Check Duration                 | Time to complete connection check after a valid detection, $4Pxx = 1$   |      | 150  | 400  | ms   |

|                          | Detect backoff pause between discovery    | VVPWR - VDRAINn > 2.5 V                                                 | 300  | 400  | 500  | ms   |

| <sup>t</sup> DET_BOFF    | attempts                                  | VVPWR - VDRAINn < 2.5 V                                                 | 20   |      | 100  | ms   |

| t <sub>DET_DLY</sub>     | Detection delay                           | From command or PD attachment to<br>Channel detection complete 4Pxx = 0 |      |      | 590  | ms   |

| CLASSIFIC/               | ATION                                     |                                                                         |      |      |      |      |

| V <sub>CLASS</sub>       | Classification Voltage                    | VVPWR - VDRAINn, VSENn ≥ 0 mV<br>I <sub>channel</sub> ≥ 180 μA          | 15.5 | 18.5 | 20.5 | V    |

| I <sub>CLASS_Lim</sub>   | Classification Current Limit              | VVPWR - VDRAINn = 0 V                                                   | 65   | 80   | 90   | mA   |

|                          |                                           | Class 0-1                                                               | 5    |      | 8    | mA   |

|                          |                                           | Class 1-2                                                               | 13   |      | 16   | mA   |

| I <sub>CLASS_TH</sub>    | Classification Threshold Current          | Class 2-3                                                               | 21   |      | 25   | mA   |

|                          |                                           | Class 3-4                                                               | 31   |      | 35   | mA   |

|                          |                                           | Class 4-Class overcurrent                                               | 45   |      | 51   | mA   |

| t <sub>LCE</sub>         | Classification Duration (1st Finger)      | From detection complete                                                 | 95   |      | 105  | ms   |

| t <sub>CLE2-5</sub>      | Classification Duration (2nd- 5th Finger) | From Mark complete                                                      | 6.5  |      | 12   | ms   |

| MARK                     |                                           | ·                                                                       |      |      |      |      |

| V <sub>MARK</sub>        | Mark Voltage                              | 4 mA ≥ IChannel ≥ 180 μA<br>VVPWR - VDRAINn                             | 7    |      | 10   | V    |

| I <sub>MARK_Lim</sub>    | Mark Sinking Current Limit                | VVPWR - VDRAINn = 0 V                                                   | 10   | 70   | 90   | mA   |

| t <sub>ME</sub>          | Mark Duration                             |                                                                         | 6    |      | 12   | ms   |

SLUSD53A-MARCH 2018-REVISED MAY 2018

www.ti.com

**NSTRUMENTS**

EXAS

## **Electrical Characteristics (continued)**

|                                     | PARAMETER                                     | TEST CONDITIONS                                                           | MIN  | TYP    | MAX   | UNIT |

|-------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------|------|--------|-------|------|

| DC DISCONN                          | IECT                                          | · · · · · ·                                                               |      |        |       |      |

|                                     |                                               | DCDTxx = 0                                                                | 1.02 | 1.6575 | 2.295 | mV   |

| V <sub>IMIN</sub>                   | DC disconnect threshold                       | DCDTxx = 1                                                                | 0.51 | 1.1475 | 1.785 |      |

|                                     |                                               | TMPDO = 00                                                                | 320  |        | 400   | ms   |

|                                     | PD Maintain Power signature dropout           | TMPDO = 01                                                                | 75   |        | 100   |      |

| t <sub>MPDO</sub>                   | time limit                                    | TMPDO = 10                                                                | 150  |        | 200   |      |

|                                     |                                               | TMPDO = 11                                                                | 600  |        | 800   |      |

| t <sub>MPS</sub>                    | PD Maintain Power Signature time for validity |                                                                           |      | 2.5    | 3     | ms   |

| PORT POWE                           | R POLICING                                    |                                                                           |      |        |       |      |

|                                     | PCUT limit, 2P POL = 0000, 1000b              |                                                                           | 4    |        | 5     |      |

|                                     | PCUT limit, 2P POL = 0000, 1110b              | Measured at VVPWR = 48 V and 57 V                                         | 7    |        | 8     |      |

|                                     | PCUT limit, 2P POL = 0001, 1111b              |                                                                           | 15.5 |        | 17.1  |      |

|                                     | PCUT limit, 2P POL = 0011, 1100b              | Measured at VVPWR = 50 V and 57 V                                         | 30   |        | 33    |      |

| P <sub>CUT</sub>                    | PCUT limit, 4P POL = 0101, 1010b              | Summed 4-Pair single signature Power<br>Measured at VVPWR = 50 V and 57 V | 45   |        | 50    | W    |

| 001                                 | PCUT limit, 4P POL = 0111, 1000b              | Summed 4-Pair single signature Power<br>Measured at VVPWR = 50 V and 57 V | 60   |        | 66    |      |

|                                     | PCUT limit, 4P POL = 1001, 0110b              | Summed 4-Pair single signature Power<br>Measured at VVPWR = 50 V and 57 V | 75   |        | 83    |      |

|                                     | PCUT limit, 4P POL = 1011, 0100b              | Summed 4-Pair single signature Power<br>Measured at VVPWR = 50 V and 57 V | 90   |        | 100   |      |

| δΡ <sub>CUT</sub> /Ρ <sub>CUT</sub> | PCUT tolerance                                |                                                                           | -5   |        | 5     | %    |

|                                     |                                               | TOVLD = 00                                                                | 50   |        | 70    |      |

| ·                                   | PCUT time limit                               | TOVLD = 01                                                                | 25   |        | 35    | ms   |

| OVLD                                |                                               | TOVLD = 10                                                                | 100  |        | 140   | 1115 |

|                                     |                                               | TOVLD = 11                                                                | 200  |        | 280   |      |

| I <sub>CUT_MAX</sub>                | Internal ICUT Clamp                           | Measured per channel<br>POL = 1111 1111b                                  | 1    | 1.025  | 1.050 | А    |

| PORT CURRI                          | ENT INRUSH                                    |                                                                           |      |        |       |      |

|                                     |                                               | VVPWR - VDRAINn = 1 V                                                     | 25   | 38     | 51    |      |

|                                     |                                               | VVPWR - VDRAINn = 10 V                                                    | 25   | 38     | 51    |      |

|                                     | IInrush limit, ALTIRNn = 0                    | VVPWR - VDRAINn = 15 V                                                    | 43   | 56     | 69    |      |

|                                     |                                               | VVPWR - VDRAINn = 30 V                                                    | 102  |        | 114.7 |      |

|                                     |                                               | VVPWR - VDRAINn = 55 V                                                    | 102  |        | 114.7 |      |

| VInrush                             |                                               | VVPWR - VDRAINn = 1 V                                                     | 25   | 38     | 51    | mV   |

|                                     |                                               | VVPWR - VDRAINn = 10 V                                                    | 47   | 60     | 73    |      |

|                                     | IInrush limit, ALTIRNn = 1                    | VVPWR - VDRAINn = 15 V                                                    | 69   | 82     | 95    |      |

|                                     |                                               | VVPWR - VDRAINn = 30 V                                                    | 102  |        | 114.7 |      |

|                                     |                                               | VVPWR - VDRAINn = 55 V                                                    | 102  |        | 114.7 |      |

|                                     |                                               | TSTART = 00                                                               | 50   |        | 70    |      |

| START                               | Maximum current limit duration in start-      | TSTART = 01                                                               | 25   |        | 35    | μs   |

|                                     | up                                            | TSTART = 10                                                               | 100  |        | 140   | •    |

#### TPS23880 SLUSD53A – MARCH 2018 – REVISED MAY 2018

#### www.ti.com

#### **Electrical Characteristics (continued)**

|                        | PARAMETER                                                                                                             | TEST CONDITIONS                                            | MIN | TYP | MAX   | UNIT |

|------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|-----|-----|-------|------|

| PORT CURI              | RENT FOLDBACK                                                                                                         | · · · · ·                                                  |     |     |       |      |

|                        |                                                                                                                       | VDRAINn = 1 V                                              | 102 |     | 114.7 |      |

|                        |                                                                                                                       | VDRAINn = 15 V                                             | 102 |     | 114.7 |      |

|                        | ILIM 1X limit, $2xFB = 0$ and $ALTFBn = 0$                                                                            | VDRAINn = 30 V                                             | 69  | 76  | 84    |      |

|                        |                                                                                                                       | VDRAINn = 50 V                                             | 30  | 38  | 46    | .,   |

| V <sub>LIM</sub>       |                                                                                                                       | VDRAINn = 1 V                                              | 102 |     | 114.7 | mV   |

|                        |                                                                                                                       | VDRAINn = 25 V                                             | 102 |     | 114.7 |      |

|                        | ILIM 1X limit, 2xFB = 0 and ALTFBn = 1                                                                                | VDRAINn = 40 V                                             | 63  | 70  | 77    |      |

|                        |                                                                                                                       | VDRAINn = 50 V                                             | 30  | 38  | 46    |      |

|                        |                                                                                                                       | VDRAINn = 1 V                                              | 313 | 319 | 334   |      |

|                        |                                                                                                                       | VDRAINn = 10 V                                             | 200 | 220 | 240   |      |

|                        | ILIM 2X limit, $2xFB = 1$ and $ALTFBn = 0$                                                                            | VDRAINn = 30 V                                             | 69  | 76  | 84    |      |

|                        |                                                                                                                       | VDRAINn = 50 V                                             | 30  | 38  | 46    | .,   |

| V <sub>LIM2X</sub>     |                                                                                                                       | VDRAINn = 1 V                                              | 313 | 319 | 334   | mV   |

|                        |                                                                                                                       | VDRAINn = 20 V                                             | 183 | 193 | 203   |      |

|                        | ILIM 2X limit, 2xFB = 1 and ALTFBn = 1                                                                                | VDRAINn = 40 V                                             | 63  | 70  | 77    |      |

|                        |                                                                                                                       | VDRAINn = 50 V                                             | 30  | 38  | 46    |      |

|                        | ILIM time limit                                                                                                       | 2xFBn = 0                                                  | 55  | 60  | 65    |      |

|                        |                                                                                                                       | TLIM = 00                                                  | 55  | 60  | 65    |      |

| t <sub>LIM</sub>       |                                                                                                                       | TLIM = 01                                                  | 15  | 16  | 17    | ms   |

|                        | 2xFBn = 1                                                                                                             | TLIM = 10                                                  | 10  | 11  | 12    |      |

|                        |                                                                                                                       | TLIM = 11                                                  | 6   | 6.5 | 7     |      |

| SHORT CIR              | CUIT DETECTION                                                                                                        |                                                            |     |     |       |      |

| V <sub>short</sub>     | I <sub>SHORT</sub> threshold in 1X mode and during inrush                                                             |                                                            | 234 |     | 306   | mV   |

| V <sub>short2X</sub>   | I <sub>SHORT</sub> threshold in 2X mode                                                                               |                                                            | 357 |     | 408   |      |

|                        |                                                                                                                       | 2xFBn = 0, VDRAINn = 1 V<br>From VSENn pulsed to 0.425 V.  |     |     | 0.9   |      |

| t <sub>D_off_SEN</sub> | Gate turnoff time from SENn input                                                                                     | 2xFBn = 1, VDRAINn = 1 V<br>From VSENn pulsed to 0.62 V.   |     |     | 0.9   | μs   |

| CURRENT I              | FAULT RECOVERY (BACKOFF) TIMING                                                                                       | · · ·                                                      |     |     |       |      |

| t <sub>ed</sub>        | Error delay timing. Delay before next<br>attempt to power a channel following<br>power removal due to error condition | $P_{CUT}$ , $I_{LIM}$ or $I_{Inrush}$ fault Semi-auto mode | 0.8 | 1   | 1.2   | S    |

| δl <sub>fault</sub>    | Duty cycle of I <sub>channel</sub> with current fault                                                                 |                                                            | 5.5 |     | 6.7   | %    |

| THERMAL                | SHUTDOWN                                                                                                              | · · · · · ·                                                |     |     |       |      |

|                        | Shutdown temperature                                                                                                  | Temperature rising                                         | 135 | 146 |       | °C   |

|                        | Hysteresis                                                                                                            |                                                            |     | 7   |       | °C   |

SLUSD53A-MARCH 2018-REVISED MAY 2018

www.ti.com

### **Electrical Characteristics (continued)**

|                       | PARAMETER                                                              | TEST CONDITIONS                                                               | MIN  | TYP | MAX  | UNIT |

|-----------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------|------|-----|------|------|

| DIGITAL I/O           | (SCL, SDAI, A1-A4, /RESET, OSS unless of                               | otherwise stated)                                                             |      |     |      |      |

| V <sub>IH</sub>       | Digital input High                                                     |                                                                               | 2.1  |     |      | V    |

| V <sub>IL</sub>       | Digital input Low                                                      |                                                                               |      |     | 0.9  | V    |

| V <sub>IT_HYS</sub>   | Input voltage hysteresis                                               |                                                                               | 0.17 |     |      | V    |

|                       | Digital output Low                                                     | SDAO at 9mA                                                                   |      |     | 0.4  | V    |

| V <sub>OL</sub>       | Digital output Low                                                     | /INT at 3mA                                                                   |      |     | 0.4  | V    |

| R <sub>pullup</sub>   | Pullup resistor to VDD                                                 | /RESET, A1-A4, TEST0                                                          | 30   | 50  | 80   | kΩ   |

| R <sub>pulldown</sub> | Pulldown resistor to DGND                                              | OSS, TEST1, TEST2                                                             | 30   | 50  | 80   | kΩ   |

| t <sub>FLT_INT</sub>  | Fault to /INT assertion                                                | Time to internally register an Interrupt fault, from Channel turn off         |      | 50  | 500  | μs   |

| T <sub>RESETmin</sub> | /RESET input minimum pulse width                                       |                                                                               |      |     | 5    | μs   |

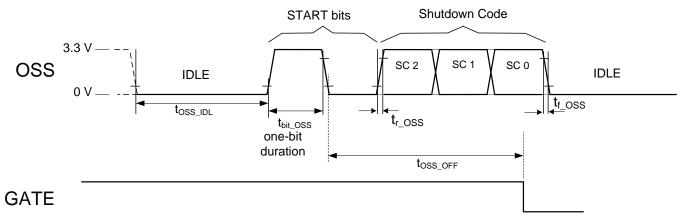

| T <sub>bit_OSS</sub>  | 3-bit OSS bit period                                                   | MbitPrty = 1                                                                  | 24   | 25  | 26   | μs   |

| t <sub>OSS_IDL</sub>  | Idle time between consecutive shutdown code transmission in 3-bit mode | MbitPrty = 1                                                                  | 48   | 50  |      | μs   |

| t <sub>r_OSS</sub>    | Input rise time of OSS in 3-bit mode                                   | $0.8 \text{ V} \rightarrow 2.3 \text{ V}$ , MbitPrty = 1                      | 1    |     | 300  | ns   |

| t <sub>f OSS</sub>    | Input fall time of OSS in 3-bit mode                                   | $2.3 \text{ V} \rightarrow 0.8 \text{ V}$ , MbitPrty = 1                      | 1    |     | 300  | ns   |

| I2C TIMING            | REQUIREMENTS                                                           | ·                                                                             |      |     |      |      |

| t <sub>POR</sub>      | Device power-on reset delay                                            |                                                                               |      |     | 20   | ms   |

| f <sub>SCL</sub>      | SCL clock frequency                                                    |                                                                               | 10   |     | 1000 | kHz  |

| t <sub>LOW</sub>      | LOW period of the clock                                                |                                                                               | 0.5  |     |      | μs   |

| t <sub>HIGH</sub>     | HIGH period of the clock                                               |                                                                               | 0.26 |     |      | μs   |

|                       |                                                                        | SDAO, 2.3 V $\rightarrow$ 0.8 V, Cb = 10 pF, 10 k $\Omega$ pull-up to 3.3 V   | 21   |     | 120  | ns   |

| t <sub>fo</sub>       | SDAO output fall time                                                  | SDAO, 2.3 V $\rightarrow$ 0.8 V, Cb = 400 pF, 1.3 k $\Omega$ pull-up to 3.3 V | 21   |     | 120  | ns   |

| C <sub>I2C</sub>      | SCL capacitance                                                        |                                                                               |      |     | 10   | pF   |

| C <sub>I2C_SDA</sub>  | SDAI, SDAO capacitance                                                 |                                                                               |      |     | 6    | pF   |

| t <sub>SU,DATW</sub>  | Data setup tme (Write operation)                                       |                                                                               | 50   |     |      | ns   |

| t <sub>HD,DATW</sub>  | Data hold time (Write operation)                                       |                                                                               | 0    |     |      | ns   |

| t <sub>HD,DATR</sub>  | Data hold time (Read operation)                                        | SDAO, VDD/2 threshold, Cb = 10 pF, 1.3 k $\Omega$ pull-up to 3.3 V            | 150  |     | 400  | ns   |

| t <sub>fSDA</sub>     | Input fall times of SDAI                                               | $2.3 \text{ V} \rightarrow 0.8 \text{ V}$                                     | 20   |     | 120  | ns   |

| t <sub>rSDA</sub>     | Input rise times of SDAI                                               | $0.8 \text{ V} \rightarrow 2.3 \text{ V}$                                     | 20   |     | 120  | ns   |

| t <sub>r</sub>        | Input rise time of SCL                                                 | $0.8 \text{ V} \rightarrow 2.3 \text{ V}$                                     | 20   |     | 120  | ns   |

| t <sub>f</sub>        | Input fall time of SCL                                                 | $2.3 \text{ V} \rightarrow 0.8 \text{ V}$                                     | 20   |     | 120  | ns   |

| t <sub>BUF</sub>      | Bus free time between a STOP and START condition                       |                                                                               | 0.5  |     |      | μs   |

| t <sub>HD,STA</sub>   | Hold time After (Repeated) START condition                             |                                                                               | 0.26 |     |      | μs   |

| t <sub>SU,STA</sub>   | Repeated START condition setup time                                    |                                                                               | 0.26 |     |      | μs   |

| t <sub>SU,STO</sub>   | STOP condition setup time                                              |                                                                               | 0.26 |     |      | μs   |

| t <sub>DG</sub>       | Suppressed spike pulse width, SDAI and SCL                             |                                                                               | 50   |     |      | ns   |

| t <sub>WDT_I2C</sub>  | I2C Watchdog trip delay                                                |                                                                               | 1.1  | 2.2 | 3.3  | sec  |

# 7 Detailed Description

### 7.1 Overview

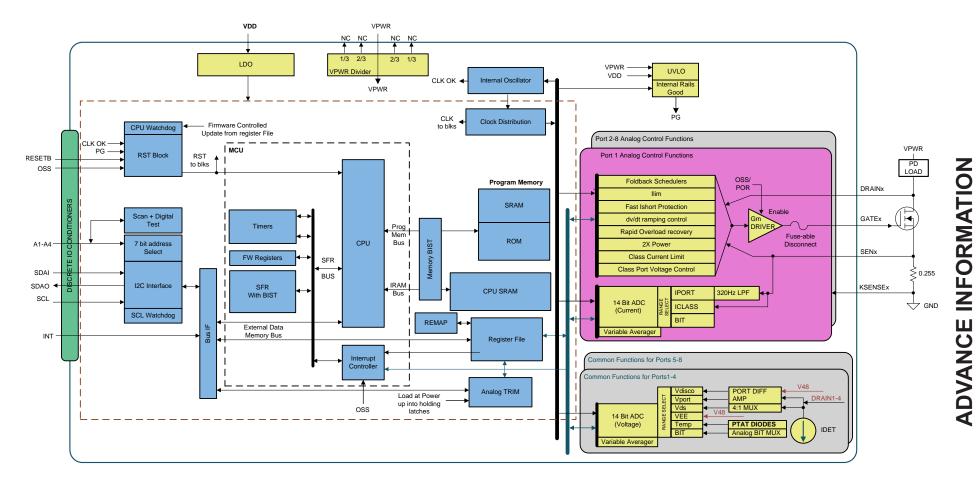

The TPS23880 is an eight-channel PSE for power over Ethernet applications. Each of the eight channels provides detection, classification, protection, and shutdown in compliance with the IEEE 802.3bt (draft) standard.

Basic PoE features include the following:

- Performs high-reliability 4-point load detection

- Performs classification including type-3/4 (three, four or five -fingers) of up to Class 8 loads

- Recognizes single signature and dual signature PDs

- Enables power with protective fold-back current limiting, and an adjustable P<sub>CUT</sub> threshold

- Shuts down during faults such as overcurrent or outputs shorts

- Performs a maintain power signature function to ensure power is removed if the load is disconnected

- Undervoltage lockout occurs if VPWR falls below V<sub>PUV F</sub> (typical 26.5 V).

Enhanced features include the following:

- Programable SRAM memory

- Dedicated 14-bit integrating current A2Ds per port

- Port re-mapping capability

- 8- and 16-bit access mode selectable

- 1- and 3-bit port shutdown priority

#### 7.1.1 Operating Modes

#### 7.1.1.1 Auto

The port performs detection and classification (if valid detection occurs) continuously. Registers are updated each time a detection or classification occurs. The port power is automatically turned on based on the Power Allocation settings in register 0x29 if a valid classification is measured.

#### 7.1.1.2 Semiauto

The port performs detection and classification (if valid detection occurs) continuously. Registers are updated each time a detection or classification occurs. The port power is not automatically turned on. A Power Enable command is required to turn on the port.

#### 7.1.1.3 Manual/Diagnostic

#### The use of this mode is intended for system diagnostic purposes only in the event that ports are not performing as expected in Semiauto or Auto modes.

The port performs the functions as configured in the registers. There is no automatic state change. Singular detection and classification measurements will be performed when commanded. Ports will be turned on immediately after a Power Enable command without any detection or classification measurements. Even though multiple classification events may be provided, the port voltage will reset immediately after the last finger, resetting the PD.

### 7.1.1.4 Power Off

The port is powered off and does not perform a detection, classification, or power-on. In this mode, Status and Enable bits for the associated port are reset.

#### 7.1.2 Channel versus Port Terminology

Throughout this document the use of the terms port and channel will be used regularly, but these terms are **not** interchangeable. Instead the term port will be used to refer to the PSE PI (Power Interface), which is most commonly associated with a RJ45 connector, whereas the term *channel* will be used to refer to the individual power path or paths associated with each port.

#### **TPS23880** SLUSD53A - MARCH 2018 - REVISED MAY 2018

#### **Overview (continued)**

Previous PSE devices commonly equated the number of controlled outputs as *ports* as each output would be dedicated to providing power on either the ALT-A **or** Alt-B pair set of a RJ45 jack/Ethernet port. However, with the adoption of 4-Pair power delivery sending power down both the ALT-A **and** ALT-B pair sets, there is now a need to differentiate between 2-pair and 4-pair capable PoE *ports*. Even more so, with the requirement to provide individual current limiting per pair set, any 4-pair *port* will now use two *channels* per 4-pair *port* to ensure safe and reliable delivery of power down each pair set.

As the TPS23880 is an 8-*channel* PSE controller. It can be configured to support up to eight 2-pair PoE *ports* or four 4-pair PoE *ports*, or any combination thereof where each 2-pair *port* accounts for one *channel*, and each 4-pair *port* accounts for 2 *channels*.

#### 7.1.3 Power Allocation and Power Demotion

The Power Allocation setting for a port sets the maximum power level a port will power on. Settings for each Class level from 2-pair 4 W (Class 1) up to 4-pair 90 W (Class 8) have been provided to maximize system design flexibility.

During a turn on attempt, if a PD presents a classification level greater than the power allocation setting for a port, the TPS23880 limits the number of classification fingers presented to the PD prior to turn on based on the power allocation settings in register 0x29. This behavior is called *Power Demotion* as it is the number of fingered presented to the PD that sets the maximum level of power the PD is allowed to draw before the PSE is allowed to disable it.

#### NOTE

Power Demotion on a port is limited to the Type boundaries as the only means of communication from the PSE to the PD is the number of classification fingers prior to turn on.

1 finger = 15.4 W, 3 fingers = 30 W, 4 fingers = 60 W, and 5 fingers = 90W

#### 7.1.4 Requested Class versus Assigned Class

The *requested* class is the classification the PSE measures during mutual identification prior to turnon, whereas the *assigned* class is the classification level the channel was powered on with based on the power allocation setting in register 0x29h. In most cases where the power allocation equals or exceeds the *requested* class, the *requested* and *assigned* classes will be the same. However, in the case of power demotion, these values will differ.

For example: If a Class 8 PD is connected to a 60 W (Class 6) limited PSE port, the *requested* class reports "Class 8", while the *assigned* class reports "Class 6".

The requested classification results are available in registers 0x0C-0F

The assigned classification results are available in registers 0x4C-4F

# 7.2 Functional Block Diagram

### 7.3 Feature Description

### 7.3.1 Port Remapping

The TPS23880 provides port remapping capability, from the logical ports to the physical channels and pins.

The remapping is between any channel of a 4-port group (1 to 4, 5 to 8).

The following example is applicable to 0x26 register = 00111001, 00111001b.

- Logical port 1 (5)  $\leftrightarrow$  Physical channel 2 (6)

- Logical port 2 (6) ↔ Physical channel 3 (7)

- Logical port 3 (7)  $\leftrightarrow$  Physical channel 4 (8)

- Logical port 4 (8)  $\leftrightarrow$  Physical channel 1 (5)

#### NOTE

The device ignores any remapping command unless all four ports are in off mode.

If the TPS23880 receives an incorrect configuration, it ignores the incorrect configuration and retains the previous configuration. The ACK is sent as usual at the end of communication. For example, if the same remapping code is received for more than one port, then a read back of the Re-Mapping register (0x26) would be the last valid configuration.

Note that if an IC reset command (1Ah register) is received, the port remapping configuration is kept unchanged. However, if there is a Power-on Reset or if the RESET pin is activated, the Re-Mapping register is reinitialized to a default value.

### 7.3.2 Port Power Priority

The TPS23880 supports 1- and 3-bit shutdown priority, which are selected with the MbitPrty bit of General Mask register (0x17).

The 1-bit shutdown priority works with the Port Power Priority (0x15) register. An OSSn bit with a value of 1 indicates that the corresponding port is treated as low priority, while a value of 0 corresponds to a high priority. As soon as the OSS input goes high, the low-priority ports are turned off.

The 3-bit shutdown priority works with the Multi Bit Power Priority (0x27/28) register, which holds the priority settings. A port with "000" code in this register has highest priority. Port priority reduces as the 3-bit value increases, with up to 8 priority levels. See Figure 1.

The multi bit port priority implementation is defined as the following:

- OSS code ≤ Priority setting (0x27/28 register): Port is disabled

- OSS code > Priority setting (0x27/28 register): Port remains active

#### Feature Description (continued)

#### TPS23880 SLUSD53A – MARCH 2018 – REVISED MAY 2018

#### NOTE

Prior to setting the MbitPrty bit from 0 to 1, make sure the OSS input is in the idle (low) state for a minimum of 200  $\mu$ s, to avoid any port misbehavior related to loss of synchronization with the OSS bit stream.

#### NOTE

The OSS input has an internal  $1-\mu s$  to  $5-\mu s$  deglitch filter. From the idle state, a pulse with a longer duration is interpreted as a valid start bit. Ensure that the OSS signal is noise free.

#### NOTE

To ensure both channels of a 4-pair port are disabled during and OSS event, make sure both channel have the same configurations in the 0x15 or 0x27/28 registers.

#### 7.3.3 A/D Converter

The TPS23880 features 10 multi-slope integrating converters. Each of the first eight converters is dedicated to current measurement for one port and operate independently to perform measurements during classification and when the port is powered on. When the port is powered, the converter is used for current (100-ms averaged) monitoring, port policing, and DC disconnect. Each of the last two converters are shared within a group of four ports for discovery (16.6-ms averaged), port powered voltage monitoring, power-good status, and FET short detection. These converters are also used for general-purpose measurements including input voltage (1 ms) and die temperature.

The A/D converter type used in the TPS23880 differs from other similar types of converters in that the A/D converter continuously converts while the input signal is sampled by the integrator, providing inherent filtering over the conversion period. The typical conversion time of the current converters is 800 µs, while the conversion time is 1 ms for the other converters. Powered-device detection is performed by averaging 16 consecutive samples which provides significant rejection of noise at 50-Hz or 60-Hz line frequency. While a port is powered, digital averaging provides a port current measurement integrated over a 100-ms time period. Note that an anti-aliasing filter is present for port powered current monitoring.

#### NOTE

During powered mode, current conversions are performed continuously. Also, in powered mode, the  $t_{\text{START}}$  timer must expire before any current or voltage A/D conversion can begin.

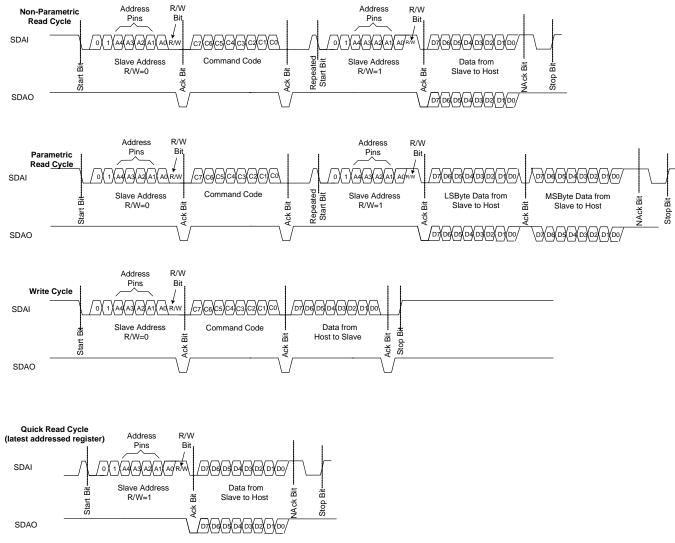

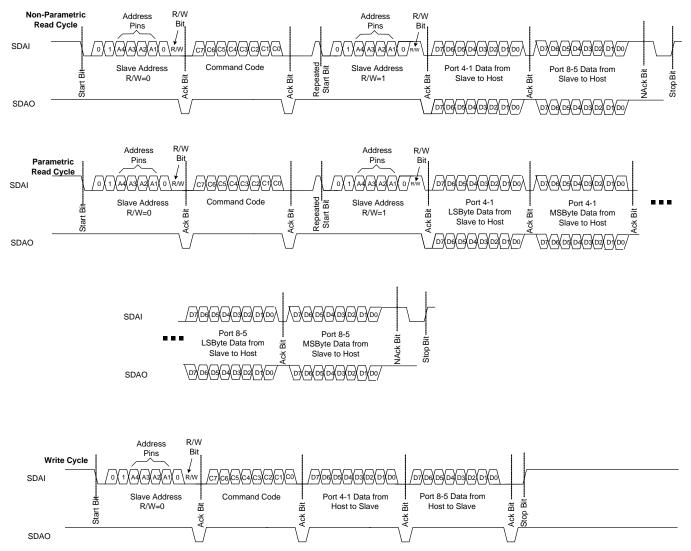

### 7.3.4 I<sup>2</sup>C Watchdog