# HDMI COMPANION CHIP WITH STEP-UP DC-DC CONVERTER, LEVEL-SHIFTER, AND ESD CLAMP

Check for Samples: TPD5S115

#### **FEATURES**

- Conforms to HDMI Compliance Tests Without any External Components

- Supports HDMI 1.4 and HDMI 1.3 Standards

- Matches HDMI Connector Pin Mapping

- Internal DC-DC Converter to Generate 5 V From a Battery Voltage as Low as 2.3 V

- Auto-direction Sensing Level Shifting and Buffering in the CEC, SDA, and SCL Paths

- IEC 61000-4-2 (Level 4) System Level ESD Compliance

- Reverse Current Blocking and Short-circuit Protection to Protect Against Fault Conditions

- Industrial Temperature Range: –40°C to 85°C

## APPLICATIONS

- Smart Phones

- eBook

- Digital Camcorders

- Portable Game Console

- Digital Still Cameras

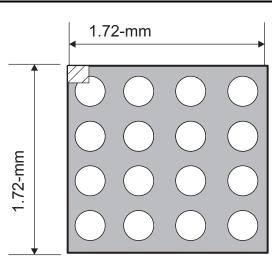

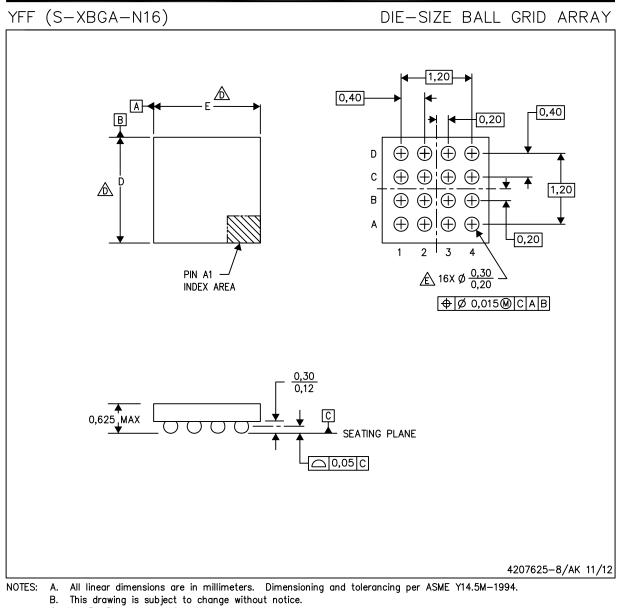

#### TPD5S115YFFR Pin Mapping (TOP VIEW)

#### **16-YFF Pin Mapping**

|   | i i i i i i i i i i i i i i i i i i i |       |       |       |  |  |  |  |  |

|---|---------------------------------------|-------|-------|-------|--|--|--|--|--|

|   | 1                                     | 2     | 3     | 4     |  |  |  |  |  |

| Α | SCL_B                                 | GND   | HPD_B | VCCA  |  |  |  |  |  |

| В | CEC_B                                 | SDA_B | LS_OE | HPD_A |  |  |  |  |  |

| С | 5VOUT                                 | SW    | EN    | SD_A  |  |  |  |  |  |

| D | PGND                                  | VBAT  | CEC_A | SCL_A |  |  |  |  |  |

### DESCRIPTION

The TPD5S115 is an integrated HDMI companion chip solution. The device provides a regulated 5 V output (5VOUT) for sourcing the HDMI power line. The regulated 5 V output supplies up to 55 mA to the HDMI receiver. The TPD5S115 features two control signals EN and LS\_OE. The control of 5VOUT and the hot plug detect (HPD) circuitry is independent of the LS\_OE control signal and is controlled by the EN pin. The EN pin allows the detection scheme (5VOUT + HPD) to be active before turning on the whole HDMI link. The LS\_OE activates the internal LDO, CEC, SCL, and SDA buffers only when EN is also activated. This dual stage enable scheme ensures optimized power saving for portable applications.

There are three non-inverting bi-directional translation circuits for the SDA, SCL, and CEC lines. Each have a common power rail (VCCA) on the A side from 1.1 V to 3.6 V. On the B side, the SCL\_B and SDA\_B each have an internal 1.75 k $\Omega$  pull-up connected to the regulated 5 V rail (5VOUT). The DDC (SCL\_B and SDA\_B) pins meet the I2C specification and drive up to 750 pF loads. The CEC\_B pin has an internal 27 k $\Omega$  pull-up to an internal 3.3 V supply. The TPD5S115 exceeds the IEC61000-4-2 (Level 4) ESD protection level. This device is offered in a space saving 1.72 mm × 1.72 mm WCSP package with 0.4 mm pitch.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# TPD5S115

www.ti.com

#### SLVSBL2B-OCTOBER 2012-REVISED MARCH 2013

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **ORDERING INFORMATION**

| T <sub>A</sub> | PACKAGE <sup>(1)(2)</sup> |               | ORDERABLE PART<br>NUMBER | TOP-SIDE<br>MARKING |

|----------------|---------------------------|---------------|--------------------------|---------------------|

| –40°C to 85°C  | YFF                       | Tape and reel | TPD5S115YFFR             | RE115               |

(1) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

(2) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

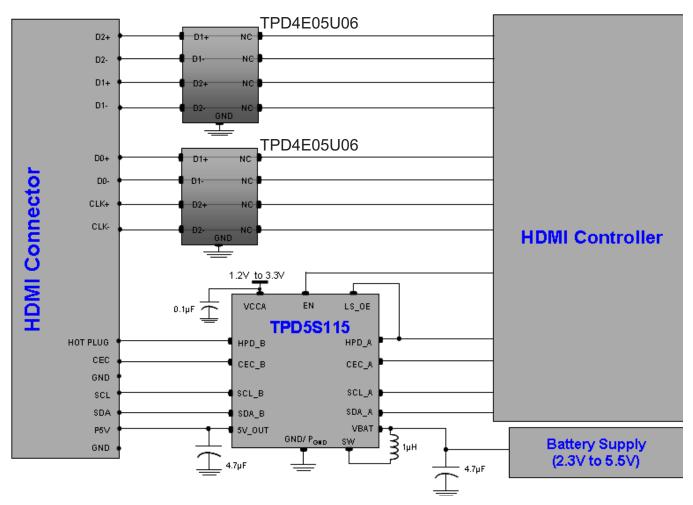

#### SYSTEM LEVEL BLOCK DIAGRAM

Figure 1. Application Schematics for HDMI Controllers with one GPIO for HDMI Interface Control

Some HDMI controllers may have only one GPIO to control the HDMI interface. Refer to Figure 1, HDMI Driver Chip is controlling the TPD5S115 via only one control line (EN). In this mode the HPD\_A to LS\_OE pin are connected shown in the above oval dotted line.

SLVSBL2B-OCTOBER 2012-REVISED MARCH 2013

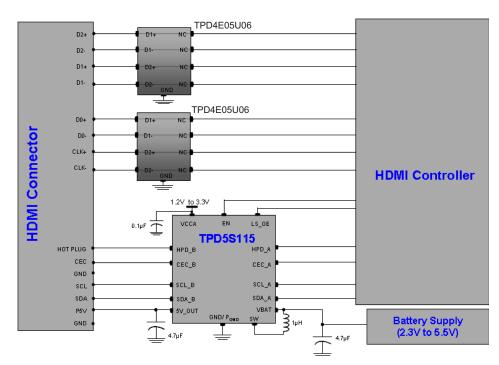

#### Figure 2. Application Schematics for HDMI Controllers with Two GPIOs for HDMI Interface Control

Some HDMI driver chips may have two GPIOs to control the HDMI interface chip. In this case a flexible power saving mode can be implemented. The LS\_OE and EN are active-high enable pins. They control the TPD5S115 power saving options according to the following tables:

| LS_OE | EN | VCCA  | VBAT  | 5VOUT  | A-Side<br>Pull-ups | DCC, B-Side<br>Pull-ups | CEC, B-Side<br>Pull-ups |

|-------|----|-------|-------|--------|--------------------|-------------------------|-------------------------|

| L     | L  | 1.8 V | 5.0 V | Off    | Off                | Off                     | Off                     |

| L     | н  | 1.8 V | 5.0 V | On     | On                 | On                      | Off                     |

| н     | L  | 1.8 V | 5.0 V | Off    | Off                | Off                     | Off                     |

| н     | н  | 1.8 V | 5.0 V | On     | On                 | On                      | On                      |

| X     | X  | 0 V   | 0 V   | High-Z | High-Z             | High-Z                  | High-Z                  |

| X     | X  | 1.8 V | 0 V   | Low    | Low                | High-Z                  | High-Z                  |

| X     | x  | 0 V   | 5.0 V | High-Z | High-Z             | High-Z                  | High-Z                  |

| LS_OE | EN | CEC<br>LDO | DC/DC &<br>HPD | DDC/CEC<br>VLTs | ICCA<br>Typ | ICC<br>VBAT<br>Typ | Comment             |

|-------|----|------------|----------------|-----------------|-------------|--------------------|---------------------|

| L     | L  | Off        | Off            | Off & High-Z    | 1 µA        | 1 µA               | Fully Disabled      |

| L     | н  | Off        | On             | Off & High-Z    | 1 µA        | 30 µA              | DC/DC (30<br>µA) on |

| н     | L  | Off        | Off            | Off & High-Z    | 1 µA        | 1 µA               | Not Valid<br>State  |

| н     | н  | On         | On             | On              | 13 µA       | 225 µA             | Fully On            |

| Х     | Х  | Off        | Off            | High-Z          | 0           | 0                  | Power down          |

| x     | Х  | Off        | Off            | High-Z          | 0           | 0                  | Power down          |

| x     | х  | Off        | Off            | High-Z          | 0           | 0                  | Power down          |

TEXAS INSTRUMENTS

SLVSBL2B-OCTOBER 2012-REVISED MARCH 2013

www.ti.com

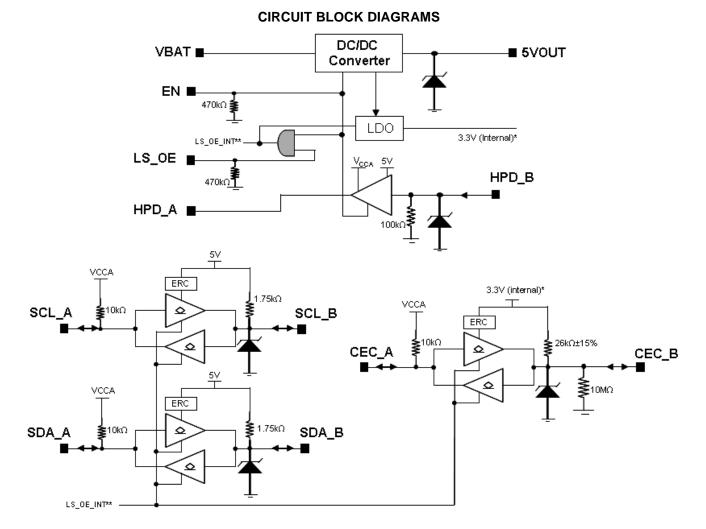

\* 3.3V (Internal) is an internal 3.3V supply rail which is generated from 5VOUT when EN=H and LS\_OE=H

\*\* LS\_OE\_INT is an internal control signal generated from EN and LS\_\_OE signals. LS\_OE\_INT is active when both EN=H and LS\_OE=H

| PIN | FU | NC. | τιο | NS |

|-----|----|-----|-----|----|

|     |    |     |     |    |

| TERMINAL        | TYPE                            | DESCRIPTION                                                                                                                |

|-----------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| NAME            | TIFE                            | DESCRIPTION                                                                                                                |

| SCL_A,<br>SDA_A | LS System side<br>IO            | System Side Input/Output for I2C Bus. These pins are bi-directional and referenced to $V_{CCA}$ .                          |

| CEC_A           | LS System side<br>IO            | System Side CEC Bus I/O. This pin is bi-directional and referenced to $V_{CCA}$ .                                          |

| HPD_A           | Output                          | System Side Output for the Hot Plug Detect. This pin is unidirectional and is referenced to V <sub>CCA</sub> .             |

| SCL_B,<br>SDA_B | LS HDMI<br>Connector side<br>IO | HDMI side Input/Output for I2C Bus. These pins are bi-directional and referenced to 5VOUT.                                 |

| CEC_B           | LS HDMI<br>Connector side<br>IO | HDMI Side CEC Bus I/O. This pin is bi-directional and referenced to the 3.3V internal supply.                              |

| HPD_B           | Input                           | HDMI Side Input for the Hot Plug Detect. This pin is unidirectional and is referenced to 5VOUT.                            |

| EN              | Control Pin                     | <b>DC/DC Enable.</b> Enables the DC/DC converter and HPD circuitry when EN = H. The EN is referenced based off $V_{CCA}$ . |

#### www.ti.com

#### PIN FUNCTIONS (continued)

| TERMINAL | ТҮРЕ                | DESCRIPTION                                                                                                                                                                                                |  |  |  |

|----------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME     | TIPE                | JESCRIPTION                                                                                                                                                                                                |  |  |  |

| LS_OE    | Control Pin         | <b>Level Shifter Enable.</b> This pin is referenced to VCCA. Enables level shifters and LDO when EN = H and LS_OE = H.                                                                                     |  |  |  |

| VBAT     | Supply              | Battery Supply. This voltage is typically 2.3 V - 5.5 V.                                                                                                                                                   |  |  |  |

| 5VOUT    | Power Output<br>Pin | <b>DC/DC Output.</b> The +5 V Power pin can supply 55 mA regulated current to the HDMI receiver.<br>Separate dc/dc converter control pin EN disables the dc/dc converter when operating at low-power mode. |  |  |  |

| SW       | Power Input         | Switch Input. This pin is the inductor input for the dc/dc converter.                                                                                                                                      |  |  |  |

| VCCA     | Supply              | System Side Supply. This voltage is typically 1.2 V to 3.3 V from the core microcontroller.                                                                                                                |  |  |  |

| GND      | Ground              | Device Ground.                                                                                                                                                                                             |  |  |  |

| PGND     | Analog Ground       | <b>DC/DC Converter Ground.</b> These pins are isolated from the GND pins. This pin should be tied to system GND.                                                                                           |  |  |  |

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

|                     |                                                        |                               | MIN  | MAX            | UNIT |

|---------------------|--------------------------------------------------------|-------------------------------|------|----------------|------|

| V <sub>CCA</sub>    | Supply voltage range                                   |                               |      | 4.0            | V    |

| V <sub>BAT</sub>    | Supply voltage range                                   |                               | -0.3 | 6.0            | V    |

| VI                  |                                                        | SCL_A, SDA_A, CEC_A           | -0.3 | 4.0            |      |

|                     | Input voltage range <sup>(2)</sup>                     | SCL_B, SDA_B, CEC_B,<br>HPD_B | -0.3 | 6.0            | V    |

|                     |                                                        | EN, LS_OE                     | -0.3 | 4.0            |      |

|                     | Voltage range applied to any output in the high-       | SCL_A, SDA_A, CEC_A           | -0.3 | 4.0            | V    |

| Vo                  | mpedance or power-off state <sup>(2)</sup>             | SCL_B, SDA_B, CEC_B           | -0.3 | 6.0            | V    |

|                     | Voltage range applied to any output in the high or low | SCL_A, SDA_A, CEC_A           | -0.3 | VCCA +<br>0.3  | V    |

| Vo                  | state <sup>(2)(3)</sup>                                | SCL_B, SDA_B, CEC_B           | -0.3 | 5VOUT +<br>0.3 | V    |

| I <sub>IK</sub>     | Input clamp current                                    | IV < 0                        |      | -50            | mA   |

| I <sub>OK</sub>     | Output clamp current                                   | VO < 0                        |      | -50            | mA   |

| I <sub>OUTMAX</sub> | Continuous current through 5VOUT, or GND               |                               |      | ±100           | mA   |

(1) Stresses beyond those listed under "ABSOLUTE MAXIMUM RATINGS" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability.

(2) The input and output voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

(3) The package thermal impedance is calculated in accordance with JESD 51-7.

Instruments

EXAS

www.ti.com

#### **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                                    | PARA                               | METER                | SUPPLY                                      | MIN                                      | TYP                  | MAX                                          | UNIT                        |

|------------------------------------|------------------------------------|----------------------|---------------------------------------------|------------------------------------------|----------------------|----------------------------------------------|-----------------------------|

| V <sub>CCA</sub>                   | Supply voltage                     |                      |                                             | 1.2                                      |                      | 3.6                                          | V                           |

| V <sub>BAT</sub>                   | Supply voltage                     |                      |                                             | 2.3                                      |                      | 5.5                                          | V                           |

|                                    |                                    | SCL_A, SDA_A         | $V_{CCA}$ = 1.2 V to 3.6 V                  | $0.7 \times V_{CCA}$                     |                      | V <sub>CCA</sub>                             |                             |

|                                    |                                    | CEC_A                | V <sub>CCA</sub> = 1.2 V to 3.6 V           | $0.7 \times V_{CCA}$                     |                      | V <sub>CCA</sub>                             |                             |

|                                    |                                    | EN, LS_OE            | V <sub>CCA</sub> = 1.2 V to 3.6 V           | 1.0                                      |                      | V <sub>CCA</sub>                             |                             |

| V <sub>IH</sub>                    | High-level input voltage           | SCL_B, SDA_B         | 5VOUT = 5.0 V                               | 0.7 ×<br>5VOUT                           |                      | 5VOUT                                        | V                           |

|                                    |                                    | CEC_B                | 5VOUT = 5.0 V                               | 0.7 × 3.3 V<br>(internal) <sup>(1)</sup> |                      | 3.3 V<br>(internal) <sup>(1)</sup>           |                             |

|                                    |                                    | HPD_B                | 5VOUT = 5.0 V                               | 2.0                                      |                      | . , ,                                        |                             |

|                                    | Low-Level input<br>voltage         | SCL_A, SDA_A         | $V_{CCA} = 1.2 \text{ V to } 3.6 \text{ V}$ | -0.5                                     |                      | 0.082 ×<br>V <sub>CCA</sub>                  |                             |

|                                    |                                    |                      | CEC_A                                       | $V_{CCA}$ = 1.2 V to 3.6 V               | -0.5                 |                                              | 0.082 ×<br>V <sub>CCA</sub> |

| M                                  |                                    | EN, LS_OE            | $V_{CCA}$ = 1.2 V to 3.6 V                  | -0.5                                     |                      | 0.4                                          | V                           |

| V <sub>IL</sub>                    |                                    | voltage              | SCL_B, SDA_B                                | 5VOUT = 5.0 V                            | -0.5                 |                                              | 0.3 ×<br>5VOUT              |

|                                    |                                    | CEC_B                | 5VOUT = 5.0 V                               | -0.5                                     |                      | $0.3 \times 3.3 V$ (internal) <sup>(1)</sup> |                             |

|                                    |                                    | HPD_B                | 5VOUT = 5.0 V                               | 0                                        |                      | 0.8                                          |                             |

| V <sub>ILC</sub>                   | (contention)<br>Low-level input vo | Itage                |                                             | -0.5                                     |                      | 0.065 ×<br>V <sub>CCA</sub>                  | V                           |

| V <sub>OL</sub> - V <sub>ILC</sub> | Delta between V <sub>OI</sub>      | and V <sub>ILC</sub> | V <sub>IO</sub> = 2.5 V                     |                                          | $0.1 \times V_{CCA}$ |                                              | V                           |

| T <sub>A</sub>                     | Operating free-air                 | temperature          |                                             | -40                                      |                      | 85                                           | °C                          |

| Passive C                          | omponents                          |                      |                                             |                                          |                      |                                              |                             |

| L <sub>IN</sub>                    | External Inductor,                 | 0805 foot-print      |                                             |                                          | 1                    |                                              | μH                          |

| C <sub>IN</sub>                    | Input Capacitor, 0                 | 603 foot-print       |                                             |                                          | 4.7                  |                                              | μF                          |

| C <sub>OUT</sub>                   | Output Capacitor,                  | 0603 foot-print      |                                             |                                          | 4.7                  |                                              | μF                          |

| C <sub>VCCA</sub>                  | Input Capacitor, 04                | 402 foot-print       |                                             |                                          | 0.1                  |                                              | μF                          |

(1) "3.3V (internal)" is an internally generated voltage node for the CEC\_B output buffer supply reference. An LDO generates this 3.3 V from 5VOUT when LS\_OE = H & EN = H.

| ESD Table                       |                                         |      |      |  |  |  |  |  |  |

|---------------------------------|-----------------------------------------|------|------|--|--|--|--|--|--|

| PARAMETER                       | SIGNALS                                 | ТҮР  | UNIT |  |  |  |  |  |  |

| HBM JESD22A114-B                | SCL_A, SDA_A, CEC_A, EN, LS_OE,<br>VCCA | 2    | kV   |  |  |  |  |  |  |

| CDM JESD22 C101                 | ALL                                     | 1000 | V    |  |  |  |  |  |  |

| IEC 61000-4-2 Contact Discharge | SCL_B, SDA_B, CEC_B, HPD_B, 5VOUT       | ±14  | kV   |  |  |  |  |  |  |

| IEC 61000-4-2 Air-gap Discharge | SCL_B, SDA_B, CEC_B, HPD_B, 5VOUT       | ±16  | V    |  |  |  |  |  |  |

Submit Documentation Feedback

6

#### www.ti.com

### ELECTRICAL CHARACTERISTICS

| PARAMETER              |                                |                          | TEST CONDITIONS                                                                                                                      | MIN  | TYP  | MAX                                                                                      | UNIT  |

|------------------------|--------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|------|------------------------------------------------------------------------------------------|-------|

| SUPPLY CU              | IRRENT                         |                          |                                                                                                                                      |      |      |                                                                                          |       |

|                        | Standby                        | VCCA                     | I/O's = High                                                                                                                         |      |      | 2                                                                                        | μA    |

| I <sub>CCA</sub>       | Active                         | VCCA                     | I/O's = High                                                                                                                         |      |      | 15                                                                                       | μA    |

|                        | Standby                        | VBAT                     | EN = L<br>LS_OE = L                                                                                                                  |      | 0.5  |                                                                                          | μΑ    |

| I <sub>CCB</sub>       | DC/DC and HPD Active           | VBAT                     | EN = H<br>LS_OE = L                                                                                                                  |      | 30   | 50                                                                                       | μA    |

|                        | DC/DC, HPD, DDC,<br>CEC Active | VBAT                     | EN = H<br>LS_OE = L<br>I/O's = H                                                                                                     |      | 225  | 300                                                                                      | μA    |

| DC-DC Conv             | verter                         | •                        | -                                                                                                                                    |      |      |                                                                                          |       |

| V <sub>BAT</sub>       | Input Voltage Range            |                          |                                                                                                                                      | 2.3  |      | 5.5                                                                                      | V     |

| 5VOUT                  | Total DC Output Voltage        | 3                        | Includes voltage references, DC load /<br>line regulations, process and<br>temperature                                               | 4.90 | 5.0  | 5.13                                                                                     | V     |

| T <sub>OVA</sub>       | Total Output Voltage Accuracy  |                          | Includes voltage references, DC load /<br>line regulations, transient load / line<br>regulations, ripple, process and<br>temperature | 4.80 | 5.0  | 5.3                                                                                      | V     |

| V                      | Output Voltage Ripple, Loaded  |                          | I <sub>O</sub> = 65 mA                                                                                                               |      | 50.6 |                                                                                          | mV    |

| V <sub>IO_Ripple</sub> | Output voltage Ripple, L       | loaded                   | I <sub>O</sub> = 150 mA                                                                                                              |      | 16   |                                                                                          | (p-p) |

| F_clk                  | Internal operating freque      | ncy                      | V <sub>BAT</sub> = 2.3 V - 5.5<br>V                                                                                                  |      | 3.5  |                                                                                          | MHz   |

| t <sub>start</sub>     | Startup time                   |                          | From EN input to 5 V Power Output 90% point.                                                                                         |      | 187  |                                                                                          | μs    |

|                        | Output Current                 |                          | V <sub>BAT</sub> = 2.3 V to 5.5<br>V                                                                                                 | 55   |      |                                                                                          | mA    |

| 10                     | Reverse Leakage Currer         | nt V <sub>O</sub>        | EN= L, VO = 5.5 V                                                                                                                    |      |      | 5.5   5.0 5.13   5.0 5.3   50.6 1   16 3.5   187 1   2.5 5.0   2.0 2.1   17.1 1   63.5 1 | μA    |

|                        | Leakage Current from B         | attery to V <sub>O</sub> | EN= L                                                                                                                                |      |      | 5.0                                                                                      | μA    |

| V                      | Lindor voltogo Lookout T       | 'hrochold                | Falling                                                                                                                              |      | 2.0  |                                                                                          | V     |

| V <sub>BATUV</sub>     | Under voltage Lockout T        | nresnoia                 | Rising                                                                                                                               |      | 2.1  |                                                                                          | V     |

|                        | Line Transient Response        |                          | $V_{BAT}$ = 3.4 V, a pulse of 217 Hz 600 mVp-p square wave.<br>IO = 20/ 65 mA                                                        |      | 17.1 |                                                                                          | mVpk  |

|                        | Load Transient Respons         | e                        | $V_{BAT}$ = 3.4 V, IO = 5 - 65 mA, pulse of 10 $\mu Sec,$ TRise = TFall = 0.1 $\mu s$                                                |      | 63.5 |                                                                                          | mVpk  |

| l_inrush<br>(startup)  | inrush current, average o      | over T_startup time      | Vbat = 2.3 V - 5.5 V lout = 65 mA                                                                                                    |      | 168  |                                                                                          | mA    |

| I <sub>SC</sub>        | Short Circuit Current Lin      | nit from Output          |                                                                                                                                      |      | 90   |                                                                                          | mA    |

www.ti.com

#### **ELECTRICAL CHARACTERISTICS**

|                       | PARAMETER                                                       | TEST CO                                                             | NDITIONS                              | V <sub>CCA</sub> | –40°C to 85°C              |                            | 0    | UNIT |  |

|-----------------------|-----------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------|------------------|----------------------------|----------------------------|------|------|--|

|                       |                                                                 |                                                                     |                                       |                  | MIN                        | TYP                        | MAX  |      |  |

| V <sub>OHA</sub>      |                                                                 | I <sub>OH</sub> = −10 μA                                            | $V_I = V_{IH}$                        | 1.2 V to 3.6 V   | V <sub>CCA</sub> × 0.80    |                            |      | V    |  |

| V <sub>OLA</sub>      |                                                                 | I <sub>OL</sub> = 10 μA                                             | $V_I = V_{IL}$                        | 1.2 V to 3.6 V   |                            | V <sub>CCA</sub> ×<br>0.16 |      | V    |  |

| V <sub>OHB</sub>      |                                                                 | I <sub>OH</sub> = −10 μA                                            | $V_{I} = V_{IH}$                      |                  |                            |                            |      | V    |  |

| V <sub>OLB</sub>      |                                                                 | I <sub>OL</sub> = 3 mA                                              | $V_{I} = V_{IL}$                      |                  |                            |                            | 0.4  | V    |  |

| RPU                   | Internal pull-up                                                | SCL_A,<br>SDA_A                                                     | Pull-up<br>connected to<br>VCCA rail  |                  |                            | 10                         |      | kΩ   |  |

| RPU                   | internai puil-up                                                | SCL_B,<br>SDA_B                                                     | Pull-up<br>connected to 5 V<br>rail   |                  |                            | 1.75                       |      | K12  |  |

| I <sub>PULLUPAC</sub> | Transient Boosted Pull-up<br>Current (rise-time<br>accelerator) | SCL_B,<br>SDA_B                                                     | Pull-up<br>connected to 5 V<br>rail   |                  |                            | 15                         |      | mA   |  |

|                       | A port                                                          | $VCCA = 0 V, V_1 or$                                                | $V_0 = 0 \text{ to } 3.6 \text{ V}$   | 0 V              |                            |                            | ±5   |      |  |

| l <sub>off</sub>      | B port                                                          | 5VOUT = 0 V, V <sub>1</sub> 0                                       | or $V_0 = 0$ to 5.5 V                 | 0 V to 3.6 V     |                            |                            | ±5   |      |  |

|                       | A port                                                          | $V_{O} = V_{CCO} \text{ or } GND$ $V_{I} = V_{CCI} \text{ or } GND$ |                                       | 1.2 V to 3.6 V   |                            |                            | ±5   | μA   |  |

| I <sub>OZ</sub>       | B port                                                          |                                                                     |                                       | 1.2 V to 3.6 V   |                            | ±!                         | ±5   |      |  |

| Voltage Le            | vel Shifter CEC Line (x_A &                                     | x_B ports)                                                          |                                       |                  |                            |                            |      |      |  |

| V <sub>OHA</sub>      |                                                                 | I <sub>OH</sub> = −10 μA                                            | $V_I = V_{IH}$                        | 1.2 V to 3.6 V   | V <sub>CCA</sub> ×<br>0.80 |                            |      | V    |  |

| V <sub>OLA</sub>      |                                                                 | I <sub>OL</sub> = 10 μA                                             | $V_{I} = V_{IL}$                      | 1.2 V to 3.6 V   |                            | V <sub>CCA</sub> ×<br>0.16 |      | V    |  |

| V <sub>OHB</sub>      |                                                                 | I <sub>OH</sub> = -20 μA                                            | $V_{I} = V_{IH}$                      |                  | V <sub>CCA</sub> × 0.80    |                            |      | V    |  |

| V <sub>OLB</sub>      |                                                                 | I <sub>OL</sub> = 3 mA                                              | $V_{I} = V_{IL}$                      |                  |                            |                            | 0.4  | V    |  |

| P                     |                                                                 | CEC_A                                                               | Pull-up<br>connected to<br>VCCA rail  |                  |                            | 10                         |      | 1-0  |  |

| R <sub>PU</sub>       | Internal pull-up                                                | CEC_B                                                               | Pull-up<br>connected to 3.3<br>V rail |                  | 22                         | 26                         | 30   | kΩ   |  |

| R <sub>PD</sub>       | Internal pull-down                                              | CEC_B                                                               | Pull-up<br>connected to<br>GND        |                  |                            | 14                         |      | MΩ   |  |

|                       | A port                                                          | $VCCA = 0 V, V_{I} or$                                              | $V_{\rm O} = 0$ to 3.6 V              | 0 V              |                            |                            | ±5   |      |  |

| I <sub>off</sub>      | B port                                                          | 5VOUT = 0 V, V <sub>I</sub> 0                                       | or $V_0 = 0$ to 5.5 V                 | 0 V to 3.6 V     |                            |                            | ±1.8 |      |  |

|                       | A port                                                          | $V_{O} = V_{CCO}$ or GNI                                            | )                                     | 1.2 V to 3.6 V   |                            |                            | ±5   | μA   |  |

| I <sub>OZ</sub>       | B port                                                          | $V_{I} = V_{CCI}$ or GND                                            |                                       | 1.2 V to 3.6 V   |                            |                            | ±5   |      |  |

#### SLVSBL2B-OCTOBER 2012-REVISED MARCH 2013

### ELECTRICAL CHARACTERISTICS (continued)

over operating free-air temperature range (unless otherwise noted)

|                                              | PARAMETER          | TEST C                  | CONDITIONS                     | V <sub>CCA</sub> | –40°C to 85°C          |     |     | UNIT |  |  |  |

|----------------------------------------------|--------------------|-------------------------|--------------------------------|------------------|------------------------|-----|-----|------|--|--|--|

|                                              |                    |                         |                                |                  | MIN                    | ТҮР | MAX |      |  |  |  |

| Voltage Level Shifter - HPD Line (X_A & x_B) |                    |                         |                                |                  |                        |     |     |      |  |  |  |

| V <sub>OHA</sub>                             |                    | I <sub>OH</sub> = -3 mA | $V_{I} = V_{IH}$               | 1.2 V to 3.6 V   | V <sub>CCA</sub> × 0.7 |     |     | V    |  |  |  |

| V <sub>OLA</sub>                             |                    | I <sub>OL</sub> = 3 mA  | $V_{I} = V_{IL}$               | 1.2 V to 3.6 V   |                        |     | 0.4 | V    |  |  |  |

| R <sub>PD</sub>                              | Internal pull-down | HPD_B                   | Pull-up<br>connected to<br>GND |                  |                        | 100 |     | kΩ   |  |  |  |

| I <sub>OZ</sub>                              | A port             | $V_I = V_{CCI}$ or GN   | D                              | 3.6 V            |                        |     | ±5  | μA   |  |  |  |

| LS_OE,                                       | EN                 |                         |                                |                  |                        |     |     |      |  |  |  |

| I <sub>I</sub>                               |                    | $V_I = V_{CCA}$ or GN   | ID                             | 1.2 V to 3.6 V   |                        |     | ±12 |      |  |  |  |

### ELECTRICAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|          | PARAMETER           | TEST CONDITIONS                                                | Supply & EN Signal                                                                            | -40 | UNIT |     |    |

|----------|---------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----|------|-----|----|

|          |                     |                                                                |                                                                                               | MIN | TYP  | MAX |    |

| I/O Cap  | acitances           |                                                                |                                                                                               |     |      |     |    |

|          | EN, LS_OE           | V <sub>BIAS</sub> = 1.8 V, f = 1 MHz, 30 mVp-<br>p ac signal   | V <sub>CCA</sub> = 3.6 V VBAT= 5 V                                                            |     | 7.1  | 9.5 | pF |

|          | SCL_A, SDA_A, CEC_A | V <sub>BIAS</sub> = 1.8 V, f = 1 MHz, 30 mVp-<br>p ac signal   | $\label{eq:VCCA} \begin{array}{l} V_{CCA} = 3.6 \; V \; VBAT = 5 \; V, \\ EN = L \end{array}$ |     | 7    |     | pF |

| <u> </u> | HPD_A, HPD_B        | V <sub>BIAS</sub> = 1.8 V, f = 1 MHz, 30 mVp-<br>p ac signal   | $\label{eq:VCCA} \begin{array}{l} V_{CCA} = 3.6 \; V \; VBAT = 5 \; V, \\ EN = L \end{array}$ |     | 4    |     | pF |

| С        | SCL_B, SDA_B        | V <sub>BIAS</sub> = 2.5 V, f = 100 kHz, 3.5<br>Vp-p ac signal  | V <sub>CCA</sub> = 3.6 V VBAT = 5 V,<br>EN = L, LS_OE = H                                     |     | 10   |     | pF |

|          | CEC_B               | V <sub>BIAS</sub> = 1.65 V, f = 100 kHz, 2.5<br>Vp-p ac signal | V <sub>CCA</sub> = 3.6 V VBAT = 5 V,<br>EN=L, LS_OE = H                                       |     | 7    |     | pF |

|          | CEC_B               | $V_{BIAS}$ = 1.65 V, f = 100 kHz, 2.5 Vp-p ac signal           | V <sub>CCA</sub> = 0 V 5V_IN = 0 V                                                            |     | 7    |     | pF |

#### SWITCHING CHARACTERISTICS

|          | PARAMETER                     | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|----------|-------------------------------|-----------------|-----|-----|-----|------|

| <u>_</u> | Bus Load Capacitance (B side) |                 |     |     | 750 | - 5  |

| CL       | Bus Load Capacitance (A side) |                 |     |     | 15  | р⊦   |

#### SWITCHING CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|                   |                                     | PINS        | TEST CONDITIONS      | MIN TYP        | MAX | UNIT |

|-------------------|-------------------------------------|-------------|----------------------|----------------|-----|------|

| Voltage           | Level Shifter- SCL, SDA Lines (x_A  |             |                      |                |     |      |

| Tonage            |                                     | A to B      | DDC channels enabled | 394            |     | ns   |

| TPHL              | Propagation delay                   | B to A      | DDC channels enabled | 347            |     | ns   |

|                   |                                     | A to B      | DDC channels enabled | 504            |     | ns   |

| TPLH              | TPLH Propagation delay              |             | DDC channels enabled | 171            |     | ns   |

| T <sub>FALL</sub> | A port fall time                    | A-Port      | DDC channels enabled | 146            |     | ns   |

| T <sub>FALL</sub> | B port fall time                    | B-Port      | DCC channels enabled | 135            |     | ns   |

| T <sub>RISE</sub> | A port rise time                    | A-Port      | DCC channels enabled | 190            |     | ns   |

| T <sub>RISE</sub> | B port rise time                    | B-Port      | DCC channels enabled | 93             |     | ns   |

| FMAX              | Maximum switching frequency         |             | DCC channels enabled | 400            |     | kHz  |

| Voltage           | Level Shifter- CEC Line (x_A & x_B  | ports) VC   |                      |                |     |      |

|                   |                                     | A to B      | CEC channels enabled | 550            |     | ns   |

| TPHL              | Propagation delay                   | B to A      | CEC channels enabled | 350            |     | ns   |

|                   |                                     | A to B      | CEC channels enabled | 13             |     | μs   |

| TPLH              | Propagation delay                   | B to A      | CEC channels enabled | 290            |     | ns   |

| T <sub>FALL</sub> | A port fall time                    | A-Port      | CEC channels enabled | 146            |     | ns   |

| T <sub>FALL</sub> | B port fall time                    | B-Port      | CEC channels enabled | 200            |     | ns   |

| T <sub>RISE</sub> | A port rise time                    | A-Port      | CEC channels enabled | 190            |     | ns   |

| T <sub>RISE</sub> | B port rise time                    | B-Port      | CEC channels enabled | 16.4           |     | μs   |

|                   | Level Shifter- HPD Line (x_A & x_B  | ports) VC   |                      |                |     |      |

| TPHL              | Propagation delay                   | B to A      | CEC channels enabled | 10.4           |     | ns   |

| TPLH              | Propagation delay                   | B to A      | CEC channels enabled | 9.9            |     | ns   |

| T <sub>FALL</sub> | A port fall time                    | A-Port      | CEC channels enabled | 0.7            |     | ns   |

| T <sub>RISE</sub> | A port rise time                    | A-Port      | CEC channels enabled | 0.8            |     | ns   |

|                   | Level Shifter- SCL, SDA Lines (x_A  | & x_B por   | ts) VCCA = 1.5V      | - <del> </del> | ŀ   |      |

|                   |                                     | A to B      | DDC channels enabled | 375            |     | ns   |

| TPHL              | Propagation delay                   | B to A      | DDC channels enabled | 272            |     | ns   |

|                   |                                     | A to B      | DDC channels enabled | 488            |     | ns   |

| TPLH              | Propagation delay                   | B to A      | DDC channels enabled | 166            |     | ns   |

| T <sub>FALL</sub> | A port fall time                    | A-Port      | DDC channels enabled | 114            |     | ns   |

| T <sub>FALL</sub> | B port fall time                    | B-Port      | DCC channels enabled | 135            |     | ns   |

| T <sub>RISE</sub> | A port rise time                    | A-Port      | DCC channels enabled | 186            |     | ns   |

| T <sub>RISE</sub> | B port rise time                    | B-Port      | DCC channels enabled | 93             |     | ns   |

| FMAX              | Maximum switching frequency         |             | DCC channels enabled | 400            |     | kHz  |

|                   | 3.2B (Voltage Level Shifter- CEC Li | ne (x_A & x |                      | 1              |     |      |

| ייוסד             | Dranagation dolars                  | A to B      | CEC channels enabled | 536            |     | ns   |

| TPHL              | Propagation delay                   | B to A      | CEC channels enabled | 272            |     | ns   |

| ייוסד             |                                     | A to B      | CEC channels enabled | 13             |     | μs   |

| TPLH              | Propagation delay                   | B to A      | CEC channels enabled | 285            |     | ns   |

| T <sub>FALL</sub> | A port fall time                    | A-Port      | CEC channels enabled | 113            |     | ns   |

| T <sub>FALL</sub> | B port fall time                    | B-Port      | CEC channels enabled | 201            |     | ns   |

| T <sub>RISE</sub> | A port rise time                    | A-Port      | CEC channels enabled | 187            |     | ns   |

www.ti.com

www.ti.com

### SWITCHING CHARACTERISTICS (continued)

|                        | PARAMETER                            | PINS        | TEST CONDITIONS              | MIN TYP MAX | UNIT |

|------------------------|--------------------------------------|-------------|------------------------------|-------------|------|

| T <sub>RISE</sub>      | B port rise time                     | B-Port      | CEC channels enabled         | 16          | μs   |

| Section                | 3.2C (Voltage Level Shifter- HPD Li  | ne (x_A & x | k_B ports) VCCA = 1.5V       |             |      |

| TPHL                   | Propagation delay                    | B to A      | CEC channels enabled         | 10          | ns   |

| TPLH                   | Propagation delay                    | B to A      | CEC channels enabled         | 10          | ns   |

| T <sub>FALL</sub>      | A port fall time                     | A-Port      | CEC channels enabled         | 0.46        | ns   |

| T <sub>RISE</sub>      | A port rise time                     | A-Port      | CEC channels enabled         | 0.5         | ns   |

| Section                | 3.3A (Voltage Level Shifter- SCL, SI | DA Lines () | <_A & x_B ports) VCCA = 1.8V |             |      |

| TPHL                   | Propagation delay                    | A to B      | DDC channels enabled         | 370         | ns   |

|                        | r topagation delay                   | B to A      | DDC channels enabled         | 230         | ns   |

| TPLH                   | Propagation delay                    | A to B      | DDC channels enabled         | 480         | ns   |

|                        |                                      | B to A      | DDC channels enabled         | 163         | ns   |

| T <sub>FALL</sub>      | A port fall time                     | A-Port      | DDC channels enabled         | 100         | ns   |

| T <sub>FALL</sub>      | B port fall time                     | B-Port      | DCC channels enabled         | 135         | ns   |

| T <sub>RISE</sub>      | A port rise time                     | A-Port      | DCC channels enabled         | 180         | ns   |

| T <sub>RISE</sub>      | B port rise time                     | B-Port      | DCC channels enabled         | 93          | ns   |

| FMAX                   | Maximum switching frequency          |             | DCC channels enabled         | 400         | kHz  |

| Section                | 3.3B (Voltage Level Shifter- CEC Li  | ne (x_A & x | CB ports) VCCA = 1.8V        | +           | •    |

| TPHL Propagation delay | Dranagation dalay                    | A to B      | CEC channels enabled         | 530         | ns   |

|                        | Propagation delay                    | B to A      | CEC channels enabled         | 230         | ns   |

| TPLH                   | Propagation delay                    | A to B      | CEC channels enabled         | 13          | μs   |

|                        |                                      | B to A      | CEC channels enabled         | 280         | ns   |

| T <sub>FALL</sub>      | A port fall time                     | A-Port      | CEC channels enabled         | 98          | ns   |

| T <sub>FALL</sub>      | B port fall time                     | B-Port      | CEC channels enabled         | 200         | ns   |

| T <sub>RISE</sub>      | A port rise time                     | A-Port      | CEC channels enabled         | 180         | ns   |

| T <sub>RISE</sub>      | B port rise time                     | B-Port      | CEC channels enabled         | 16          | μs   |

| Section                | 3.3C (Voltage Level Shifter- HPD Lii | ne (x_A & x | CB ports) VCCA = 1.8V        |             |      |

| TPHL                   | Propagation delay                    | B to A      | CEC channels enabled         | 10          | ns   |

| TPLH                   | Propagation delay                    | B to A      | CEC channels enabled         | 10          | ns   |

| T <sub>FALL</sub>      | A port fall time                     | A-Port      | CEC channels enabled         | 0.41        | ns   |

| T <sub>RISE</sub>      | A port rise time                     | A-Port      | CEC channels enabled         | 0.41        | ns   |

|                        | 3.4A (Voltage Level Shifter- SCL, SI | DA Lines (x | <_A & x_B ports) VCCA = 2.5V |             |      |

| TPHL                   | Propagation dalay                    | A to B      | DDC channels enabled         | 370         | ns   |

| IPHL                   | Propagation delay                    | B to A      | DDC channels enabled         | 185         | ns   |

| TPLH                   | Propagation delay                    | A to B      | DDC channels enabled         | 467         | ns   |

|                        | r ropagation delay                   | B to A      | DDC channels enabled         | 160         | ns   |

| T <sub>FALL</sub>      | A port fall time                     | A-Port      | DDC channels enabled         | 80          | ns   |

| T <sub>FALL</sub>      | B port fall time                     | B-Port      | DCC channels enabled         | 135         | ns   |

| T <sub>RISE</sub>      | A port rise time                     | A-Port      | DCC channels enabled         | 179         | ns   |

| T <sub>RISE</sub>      | B port rise time                     | B-Port      | DCC channels enabled         | 93          | ns   |

| FMAX                   | Maximum switching frequency          |             | DCC channels enabled         | 400         | kHz  |

## SWITCHING CHARACTERISTICS (continued)

over operating free-air temperature range (unless otherwise noted)

| over ope          | erating nee-an temperature range    | (uniess or  | nerwise noted)               | Γ         |     |      |

|-------------------|-------------------------------------|-------------|------------------------------|-----------|-----|------|

|                   | PARAMETER                           | PINS        | TEST CONDITIONS              | MIN TYP N | IAX | UNIT |

| Section           | 3.4B (Voltage Level Shifter- CEC Li | ne (x_A & : | x_B ports) VCCA = 2.5V       | Ι         |     |      |

| TPHL              | Propagation delay                   | A to B      | CEC channels enabled         | 530       |     | ns   |

|                   | r ropagation aolay                  | B to A      | CEC channels enabled         | 185       |     | ns   |

| TPLH              | Propagation delay                   | A to B      | CEC channels enabled         | 13        |     | μs   |

|                   | r ropagation aolay                  | B to A      | CEC channels enabled         | 275       |     | ns   |

| T <sub>FALL</sub> | A port fall time                    | A-Port      | CEC channels enabled         | 80        |     | ns   |

| T <sub>FALL</sub> | B port fall time                    | B-Port      | CEC channels enabled         | 200       |     | ns   |

| T <sub>RISE</sub> | A port rise time                    | A-Port      | CEC channels enabled         | 180       |     | ns   |

| T <sub>RISE</sub> | B port rise time                    | B-Port      | CEC channels enabled         | 16        |     | μs   |

| Section           | 3.4C (Voltage Level Shifter- HPD Li | ne (x_A & : | x_B ports) VCCA = 2.5V       |           |     |      |

| TPHL              | Propagation delay                   | B to A      | CEC channels enabled         | 10        |     | ns   |

| TPLH              | Propagation delay                   | B to A      | CEC channels enabled         | 10        |     | ns   |

| T <sub>FALL</sub> | A port fall time                    | A-Port      | CEC channels enabled         | 0.35      |     | ns   |

| T <sub>RISE</sub> | A port rise time                    | A-Port      | CEC channels enabled         | 0.35      |     | ns   |

| Section           | 3.5A (Voltage Level Shifter- SCL, S | DA Lines (x | x_A & x_B ports) VCCA = 3.3V | -         |     |      |

| TPHL              | Propagation delay                   | A to B      | DDC channels enabled         | 370       |     | ns   |

|                   | Flopagation delay                   | B to A      | DDC channels enabled         | 160       |     | ns   |

| TPLH              | Dranagation dalay                   | A to B      | DDC channels enabled         | 460       |     | ns   |

|                   | Propagation delay                   | B to A      | DDC channels enabled         | 155       |     | ns   |

| T <sub>FALL</sub> | A port fall time                    | A-Port      | DDC channels enabled         | 75        |     | ns   |

| T <sub>FALL</sub> | B port fall time                    | B-Port      | DCC channels enabled         | 135       |     | ns   |

| T <sub>RISE</sub> | A port rise time                    | A-Port      | DCC channels enabled         | 180       |     | ns   |

| T <sub>RISE</sub> | B port rise time                    | B-Port      | DCC channels enabled         | 93        |     | ns   |

| FMAX              | Maximum switching frequency         |             | DCC channels enabled         | 400       |     | kHz  |

| Section           | 3.5B (Voltage Level Shifter- CEC Li | ne (x_A & : | x_B ports) VCCA = 3.3V       |           |     |      |

| трии              | Drana nation dalary                 | A to B      | CEC channels enabled         | 530       |     | ns   |

| TPHL              | Propagation delay                   | B to A      | CEC channels enabled         | 160       |     | ns   |

|                   | Dranagation dalay                   | A to B      | CEC channels enabled         | 13        |     | μs   |

| TPLH              | Propagation delay                   | B to A      | CEC channels enabled         | 275       |     | ns   |

| T <sub>FALL</sub> | A port fall time                    | A-Port      | CEC channels enabled         | 73        |     | ns   |

| T <sub>FALL</sub> | B port fall time                    | B-Port      | CEC channels enabled         | 200       |     | ns   |

| T <sub>RISE</sub> | A port rise time                    | A-Port      | CEC channels enabled         | 180       |     | ns   |

| T <sub>RISE</sub> | B port rise time                    | B-Port      | CEC channels enabled         | 16        |     | μs   |

| Section           | 3.5C (Voltage Level Shifter- HPD Li | ne (x_A & x | x_B ports) VCCA = 3.3V       |           |     |      |

| TPHL              | Propagation delay                   | B to A      | CEC channels enabled         | 10        |     | ns   |

| TPLH              | Propagation delay                   | B to A      | CEC channels enabled         | 10        |     | ns   |

| T <sub>FALL</sub> | A port fall time                    | A-Port      | CEC channels enabled         | 0.34      |     | ns   |

| T <sub>RISE</sub> | A port rise time                    | A-Port      | CEC channels enabled         | 0.36      |     | ns   |

|                   | •                                   | 1           | l.                           | l.        |     |      |

www.ti.com

300

4.98

4.96

4.94 4.92

4.88

4.80

5.3

Voltage (V)

5VOUT 4.90

SLVSBL2B-OCTOBER 2012-REVISED MARCH 2013

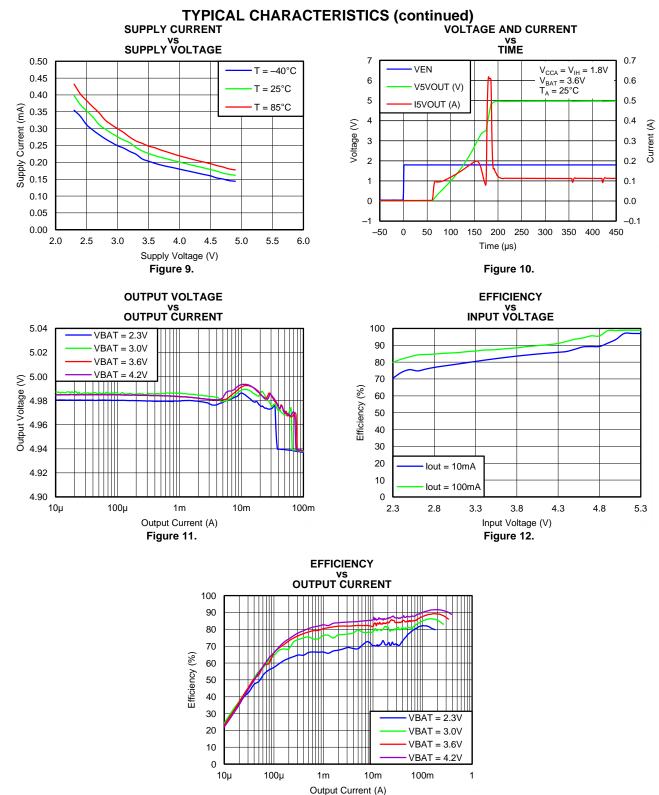

#### **TYPICAL CHARACTERISTICS** VOLTAGE VOLTAGE VS TIME VS TIME 6 6 EN EN 5VOUT @ 55mA 5VOUT @ 55mA 5 5 5VOUT @ 65mA 5VOUT @ 65mA 4 4 Voltage (V) Voltage (V) 3 3 2 2 1 1 0 0 = V<sub>IH</sub> = 2.5V, V<sub>BAT</sub> = 3.6V V<sub>CCA</sub> = V<sub>IH</sub> = 2.5V, V<sub>BAT</sub> = 3.6V VCCA ±1 ±1 2500 0 500 1000 1500 2000 3000 3500 4000 ±50 0 50 100 150 200 250 Time (s) Time (s) Figure 3. Figure 4. CURRENT VOLTAGE vs TIME vs TIME 4.0 5.04 75 5.5 70 65 15VOUT 5.4 3.9 5.02 5.3 3.8 5.00 V5VOUT 60 5.2 2.1 (m) 5.0 0, 2.0 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2.1 0, 2 3.7 I<sub>5VOUT</sub> Current (mA) 5 2 0 2 0 4 2 0 2 0 5 2 0 2 0 4 0 4 0 0 2 0 € 3.6 25 20 3.1 4.86 VBAT 15 4.3 3.0 4.84 10 4.2 5VOUT (20mA) 2.9 4.82 5 4.1 5VOUT (65mA) 0 4.0 2.8 0 2 4 6 8 10 12 14 16 18 20 0 500 1000 1500 2000 2500 3000 3500 4000 4500 5000 Time(µs) Time (µs) Figure 5. Figure 6. OUTPUT VOLTAGE FREQUENCY vs OUTPUT CURRENT VS 5.0 5.16 lout = 65mA 4.5 5.12 lout = 100 mA4.0 € 5.08 3.5 3.0 2.5 2.0 1.5 V<sub>5VOUT</sub> Output Voltage 5.04 5.00 4.96 4.92 4.88 1.0 VBAT = 3V 4.84 0.5 VBAT = 4V0.0 4.80 150 2.6 3.5 3.8 4.1 4.4 5.0 100 200 250 300 350 400 450 500 2.3 2.9 3.2 4.7 Output Current (mA) V<sub>BAT</sub> Input Voltage (V) Figure 7. Figure 8.

TEXAS INSTRUMENTS

www.ti.com

SLVSBL2B-OCTOBER 2012-REVISED MARCH 2013

Figure 13.

SLVSBL2B-OCTOBER 2012-REVISED MARCH 2013

#### **APPLICATION INFORMATION**

#### **DDC/CEC Level Shift Circuit Operation**

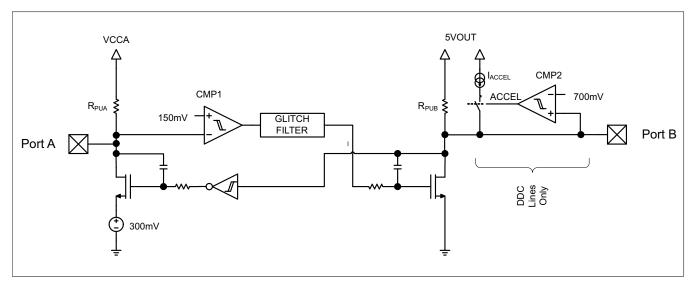

The TPD5S115 enables DDC translation from VCCA (system side) voltage levels to 5 V (HDMI cable side) voltage levels without degradation of system performance. The TPD5S115 contains 2 bidirectional open-drain buffers specifically designed to support up-translation/down-translation between the low voltage, VCCA side DDC-bus and the 5 V DDC-bus. The port B I/Os are over-voltage tolerant to 5.5 V even when the device is unpowered. After power-up and with the LS\_OE and EN pins HIGH, a LOW level on port A (below approximately V<sub>ILC</sub> = 0.08 × VCCA V) turns the corresponding port B driver (either SDA or SCL) on and drives port B down to VOLB V. When port A rises above approximately 0.10 × VCCA V, the port B pull-down driver is turned off and the internal pull-up resistor pulls the pin HIGH. When port B falls first and goes below 0.3 × 5VOUT, a CMOS hysteresis input buffer detects the falling edge, turns on the port A driver, and pulls port A down to approximately VOLA = 0.16 × VCCA V. The port B pull-down driver is enabled unless the port A voltage goes below VILC. If the port A low voltage goes below VILC, the port B pull-down driver is enabled until port A rises above (V<sub>ILC</sub> +  $\Delta V_{T-HYSTA}$ ), then port B, if not externally driven LOW, will continue to rise being pulled up by the internal pull-up resistor.

Figure 14. DDC/CEC Level Shifter Block Diagram

### DDC/CEC Level Shifter Operational Notes for VCCA=1.8V

- The threshold of CMP1 is ~150 mV ± the 40 mV of total hysteresis.

- The comparator will trip for a falling waveform at ~130 mV

- The comparator will trip for a rising waveform at ~170 mV

- To be recognized as a zero, the level at Port A must first go below 130 mV ( $V_{ILC}$  in spec) and then stay below 170 mV ( $V_{ILA}$  in spec)

- To be recognized as a one, the level at A must first go above 170mV and then stay above 130 mV

- VILC is set to 110 mV in Electrical Characteristics Table to give some margin to the 130 mV

- VILA is set to 140 mV in the Electrical Characteristics Table to give some margin to the 170 mV

- VIHA is set to 70% of VCCA to be consistent with standard CMOS levels

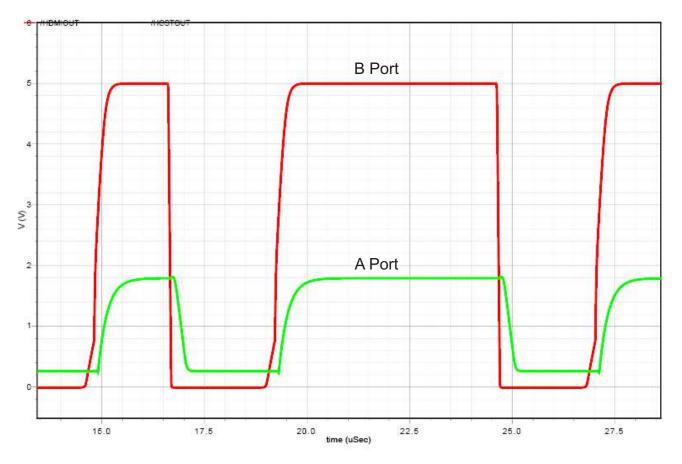

Figure 15. DDC Level Shifter Operation (B to A Direction)

#### **Rise-Time Accelerators**

The HDMI cable side of the DDC lines incorporates rise-time accelerators to support the high capacitive load on the HDMI cable side. The rise time accelerator boosts the cable side DDC signal independent of which side of the bus is releasing the signal.

SLVSBL2B-OCTOBER 2012-REVISED MARCH 2013

Figure 16. Receiving and transmitting interaction

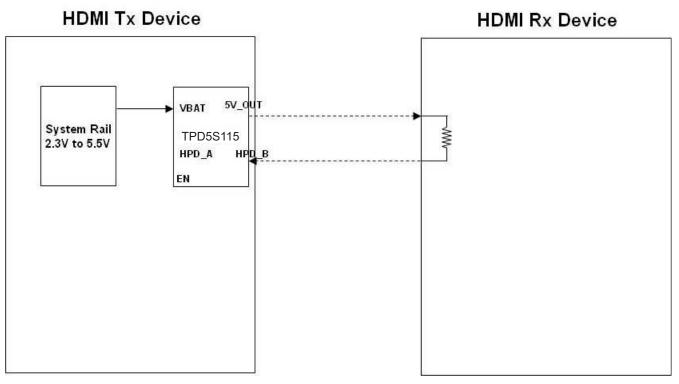

#### Hot Plug Detect

Once TPD5S115's DCDC converter and HPD block are enabled through the EN pin, it is ready for continual HDMI receiver detection. Once a HDMI cable connects receiving and transmitting device together, the 5V signal from the DCDC output flows through the receiving device's internal resistor and into HPD's input. The HPD buffer's output then goes high, indicating to the transmitter that a receiving device is connected. To save power, periodic detection can be done by turning on and off the DCDC converter before a receiving device is connected.

**Remark:** Ground offset between the TPD5S115 ground and the ground of devices on port A of the TPD5S115 must be avoided. The reason for this cautionary remark is that a CMOS/NMOS open-drain capable of sinking 3 mA of current at 0.4 V will have an output resistance of 133  $\Omega$  or less (R = E / I). Such a driver will share enough current with the port A output pull-down of the TPD5S115 to be seen as a LOW as long as the ground offset is zero. If the ground offset is greater than 0V, then the driver resistance must be less. Since V<sub>ILC</sub> can be as low as 90 mV at cold temperatures and the low end of the current distribution, the maximum ground offset should not exceed 50 mV. Bus repeaters that use an output offset are not interoperable with the port A of the TPD5S115 as their output LOW levels will not be recognized by the TPD5S115 as a LOW. If the TPD5S115 is placed in an application where the VIL of port A of the TPD5S115 does not go below its V<sub>ILC</sub> it will pull port B LOW initially when port A input transitions LOW but the port B will return HIGH, so it will not reproduce the port A input on port B. Such applications should be avoided. Port B is interoperable with all I2C-bus slaves, masters and repeaters.

#### **CEC Level Shift Operation**

The CEC level shift function operates in the same manner as the DDC lines except that the CEC line does not need the rise time accelerator function.

#### **Resistor Pull-Up Value Selection**

The system is designed to work properly with no external pull-up resistors on the DDC, CEC, and HPD lines.

www.ti.com

#### **Power-Save Mode**

The TPD5S115 integrates a power save mode to improve efficiency at light load. In power save mode the converter only operates when the output voltage trips below a set threshold voltage. It ramps up the output voltage with several pulses and goes into power save mode once the output voltage exceeds the set threshold voltage. The PFM mode is left and PWM mode entered in case the output current can not longer be supported in PFM mode.

#### **Under-Voltage Lockout**

The under voltage lockout circuit prevents the dc/dc converter from malfunctioning at low input voltages and from excessive discharge of the battery. It disables the output stage of the converter once the falling VIN trips the under-voltage lockout threshold VBATUV. The under-voltage lockout threshold V<sub>BATUV</sub> for falling VIN is typically 2.0 V. The device starts operation once the rising VIN trips under-voltage lockout threshold V<sub>BATUV</sub> again at typ. 2.1 V.

#### Enable

The dc/dc converter is enabled when the EN is set to high. At first, the internal reference is activated and the internal analog circuits are settled. Afterwards, the soft start is activated and the output voltage is ramped up. The output voltage reaches its nominal value in typically 250  $\mu$ s after the device has been enabled. The EN input can be used to control power sequencing in a system with various DC/DC converters. The EN pin can be connected to the output of another converter, to drive the EN pin high and getting a sequencing of supply rails. With EN = GND, the dc/dc enters shutdown mode.

#### Soft Start

The DC/DC converter has an internal soft start circuit that controls the ramp up of the output voltage. The output voltage reaches its nominal value within  $t_{Start}$  of typically 250 µs after EN pin has been pulled to high level. The output voltage ramps up from 5% to its nominal value within  $t_{Ramp}$  of typ. 300 µs. This limits the inrush current in the converter during start up and prevents possible input voltage drops when a battery or high impedance power source is used. During soft start, the switch current limit is reduced to 300 mA until the output voltage reaches VIN. Once the output voltage trips this threshold, the device operates with its nominal current limit ILIMF.

#### **Input Capacitor**

Due to the nature of the boost converter having a pulsating input current, a low ESR input capacitor is required to prevent large voltage transients that can cause misbehavior of the device or interferences with other circuits in the system. At least 1.2  $\mu$ F input capacitor is recommended to improve transient behavior of the regulator and EMI behavior of the total power supply circuit. It is recommended to place a ceramic capacitor as close as possible to the VIN and GND pins and better to use a 4.7  $\mu$ F capacitor, in order to improve the input noise filtering.

#### **Output Capacitor**

For the output capacitor, it is recommended to use small ceramic capacitors placed as close as possible to the VOUT and GND pins of the IC. If, for any reason, the application requires the use of large capacitors which can not be placed close to the IC, using a smaller ceramic capacitor in parallel to the large one is recommended. This small capacitor should be placed as close as possible to the VOUT and GND pins of the IC. To get an estimate of the recommended minimum output capacitance, Equation 1 can be used.

$$C_{min} = \frac{I_{OUT} \times (V_{OUT} - V_{IN})}{f \times \Delta V \times V_{OUT}}$$

(1)

Parameter f is the switching frequency and  $\Delta V$  is the maximum allowed ripple. With a chosen ripple voltage of 10 mV, a minimum effective capacitance of 2.7  $\mu$ F is needed. The total ripple is larger due to the ESR of the output capacitor. This additional component of the ripple can be calculated using:

$$\Delta V_{\rm ESR} = I_{\rm OUT} \times R_{\rm ESR}$$

A capacitor with a value in the range of the calculated minimum should be used. This is required to maintain control loop stability. There are no additional requirements regarding minimum ESR. There is no upper limit for the output capacitance value. Larger capacitors cause lower output voltage ripple as well as lower output voltage drop during load transients.

Note that ceramic capacitors have a DC Bias effect, which will have a strong influence on the final effective capacitance needed. Therefore the right capacitor value has to be chosen very carefully. Package size and voltage rating in combination with material are responsible for differences between the rated capacitor value and the effective capacitance. The minimum effective capacitance value should be 1.2  $\mu$ F but preferred value is about 4.7  $\mu$ F

| Component | Component Min |     | onent Min Target Max |    |  |  |  |

|-----------|---------------|-----|----------------------|----|--|--|--|

| CIN       | 1.2           | 4.7 | 6.5                  | μF |  |  |  |

| COUT      | 1.2           | 4.7 | 10                   | μF |  |  |  |

| LIN       | 0.7           | 1.0 | 1.3                  | μH |  |  |  |

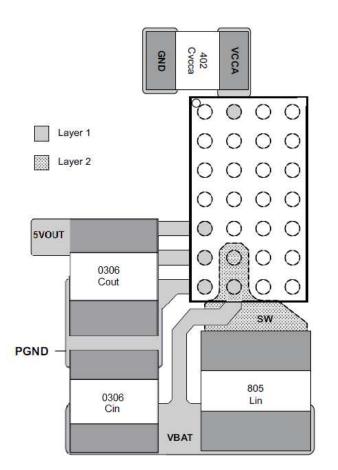

#### **TPD5S115 Board layout**

Figure 17. Board Layout (DC-DC Components) (Top View)

List of components:

- $L_{IN} = MURATA LQM21PN1R0MC0 (1.0 \mu H, 800 mA, 0805, Shielded)$

- $C_{IN} = C_{OUT} = MURATA LLL31MR70J475MA01 (4.7 \mu F, Low ESL type, 6.3 V, 0306, X7R)$

- C<sub>VCCA</sub> = MURATA GRM155R60J475ME87D (0.1 μF, 6.3 V, 0402, X5R)

# **REVISION HISTORY**

| Changes from Revision A (February 2013) to Revision B |                              |    |  |  |  |

|-------------------------------------------------------|------------------------------|----|--|--|--|

| •                                                     | Changed Board Layout section | 19 |  |  |  |

www.ti.com

7-Mar-2013

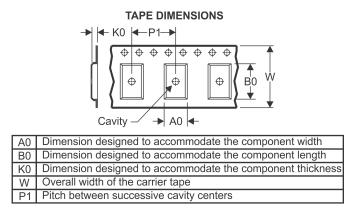

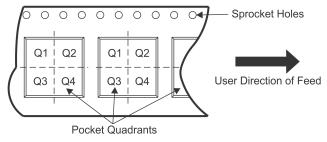

### PACKAGING INFORMATION

| Orderable Device | Status | Package Type | Package | Pins | Package Qty | Eco Plan                   | Lead/Ball Finish | MSL Peak Temp      | Op Temp (°C) | Top-Side Markings | Samples |

|------------------|--------|--------------|---------|------|-------------|----------------------------|------------------|--------------------|--------------|-------------------|---------|

|                  | (1)    |              | Drawing |      |             | (2)                        |                  | (3)                |              | (4)               |         |

| TPD5S115YFFR     | ACTIVE | DSBGA        | YFF     | 16   | 3000        | Green (RoHS<br>& no Sb/Br) | SNAGCU           | Level-1-260C-UNLIM | -40 to 85    | RE115             | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between

the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> Only one of markings shown within the brackets will appear on the physical device.