# 32-Bit TX System RISC TX39 Family TMPR3916

**TOSHIBA CORPORATION**

MIPS16, application Specific Extensions and R3000A are a trademark of MIPS Technologies, Inc.

The information contained herein is subject to change without notice.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

The products described in this document contain components made in the United States and subject to export control of the U.S. authorities. Diversion contrary to the U.S. law is prohibited.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress.

It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications.

Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

The Toshiba products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.).

These Toshiba products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of Toshiba products listed in this document shall be made at the customer's own risk.

The products described in this document may include products subject to the foreign exchange and foreign trade laws.

# **Preface**

This document describes the basic functions of TMPR3916F "Capricorn2". This document is meant to provide all information, which is needed to program and operate the device from a software developer's point of view.

October 2002

# **Table of Contents**

# **Handling precautions**

# **TMPR3916**

| 1. The                 | e TMPR3916                                 | 1-1  |

|------------------------|--------------------------------------------|------|

| 1.1                    | Applications and References                | 1-1  |

| 1.2                    | Features                                   | 1-2  |

| 1.3                    | Differences Between TX3903AF and TMPR3916  | 1-3  |

| 1.4                    | Structure of TMPR3916 and a System Example | 1-4  |

| 1.5                    | Address Map                                | 1-6  |

| 1.6                    | Clocks                                     | 1-8  |

| 1.7                    | Resets                                     | 1-9  |

| 1.8                    | Time-Out-Error Control Unit                | 1-10 |

| 1.9                    | Operating Modes of TMPR3916                | 1-10 |

| 1.10                   | Chip Configuration Register (CCR)          | 1-11 |

| 2. Me                  | emory Controller (MC)                      | 2-1  |

| 2.1                    | Structure of Memory Controller             | 2-2  |

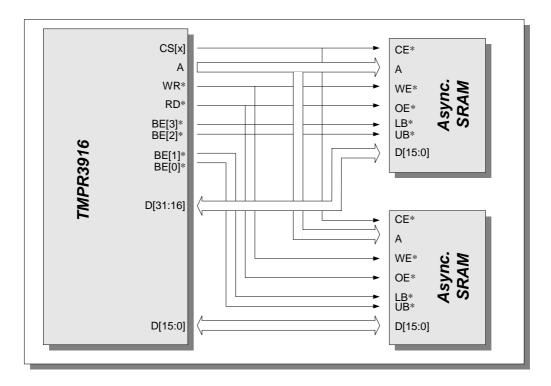

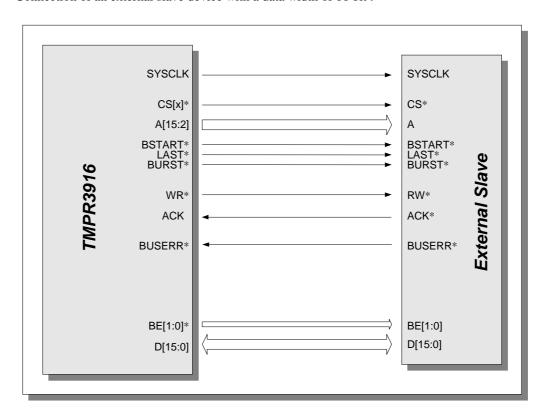

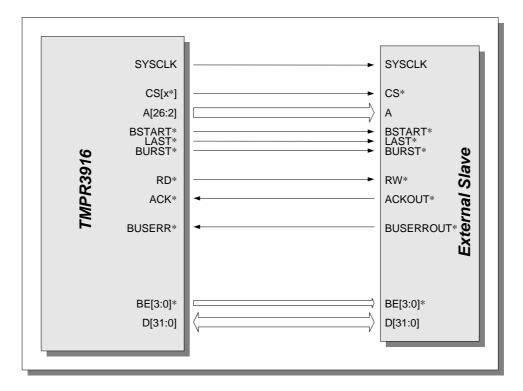

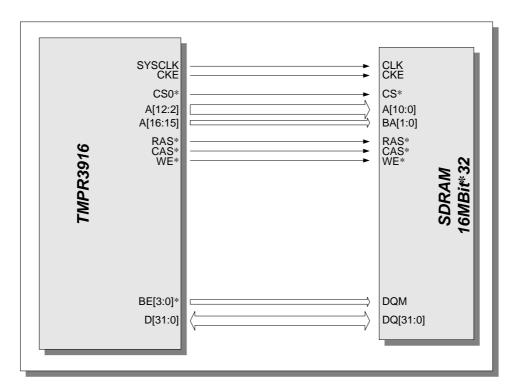

| 2.2                    | Example Memory Configuration               | 2-3  |

| 2.3                    | Ports of Memory Controller                 | 2-6  |

| 2.4                    | Registers                                  | 2-6  |

| 2.5                    | SDRAMC Functions                           | 2-7  |

| 2.6                    | MEMC Function                              | 2-20 |

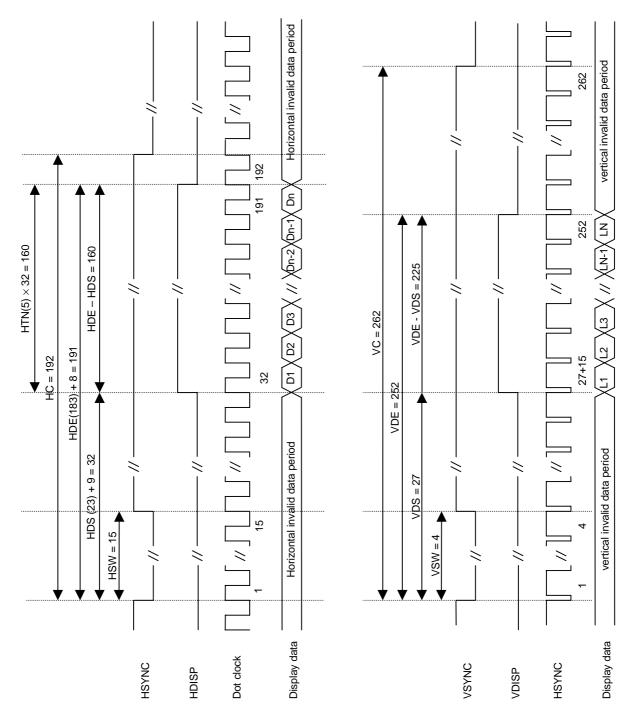

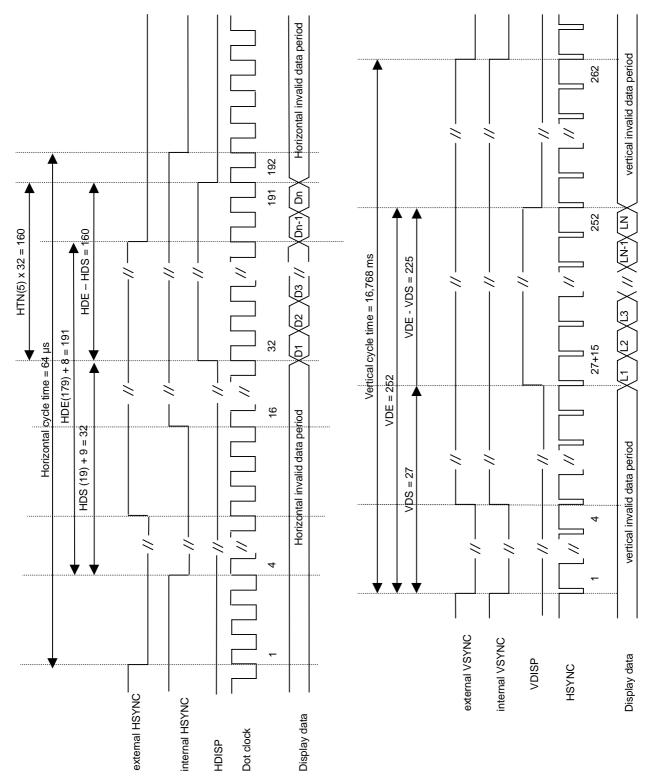

| 3. Gra                 | aphics Display Controller (GDC)            | 3-1  |

| 3.1                    | GDC Structure                              | 3-2  |

| 3.2                    | Scrolling                                  | 3-9  |

| 3.3                    | Internal Blockdiagram                      | 3-12 |

| 3.4                    | Registers                                  | 3-13 |

| 3.5                    | Setting Examples                           | 3-21 |

| 4. Inte                | errupt Controller (INTC)                   | 4-1  |

| 4.1                    | Basic Interrupt Handling                   | 4-1  |

| 4.2                    | Registers                                  | 4-2  |

| 4.3                    | Non Maskable Interrupt                     | 4-4  |

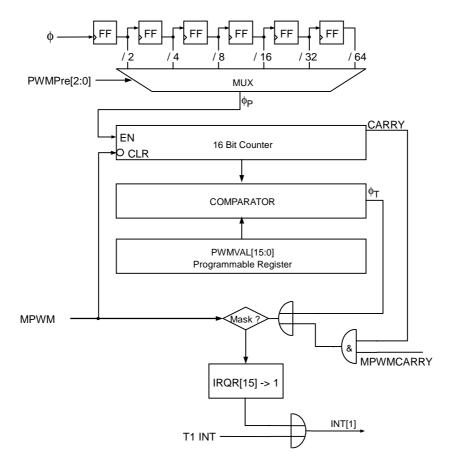

| 5. TIN                 | MER                                        | 5-1  |

| 5.1                    | PWM Timer                                  |      |

| 5.2                    | Periodic Timers                            |      |

|                        | rect Memory Access Controller (DMAC)       |      |

| 6.1                    | Programming the DMA Controller             |      |

| 6.2                    | Registers                                  |      |

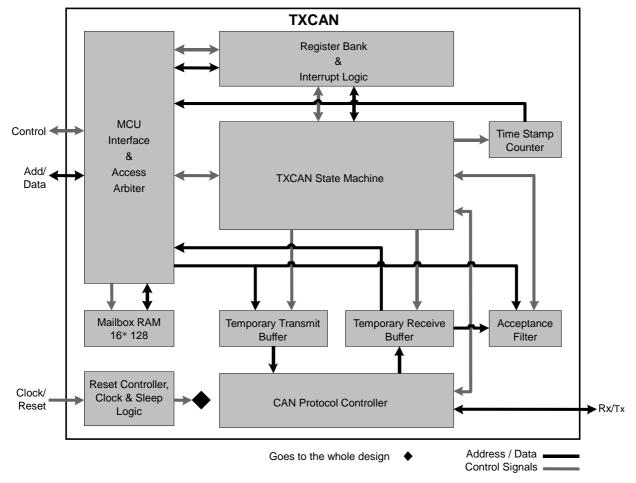

|                        | N Module (TXCAN)                           |      |

|                        | Block Diagram                              |      |

| 7.1<br>7.2             | TXCAN Registers                            |      |

| 7.2                    | TXCAN RegistersTXCAN Interrupt Logic       |      |

| 7.3<br>7.4             | TXCAN Interrupt Logic                      |      |

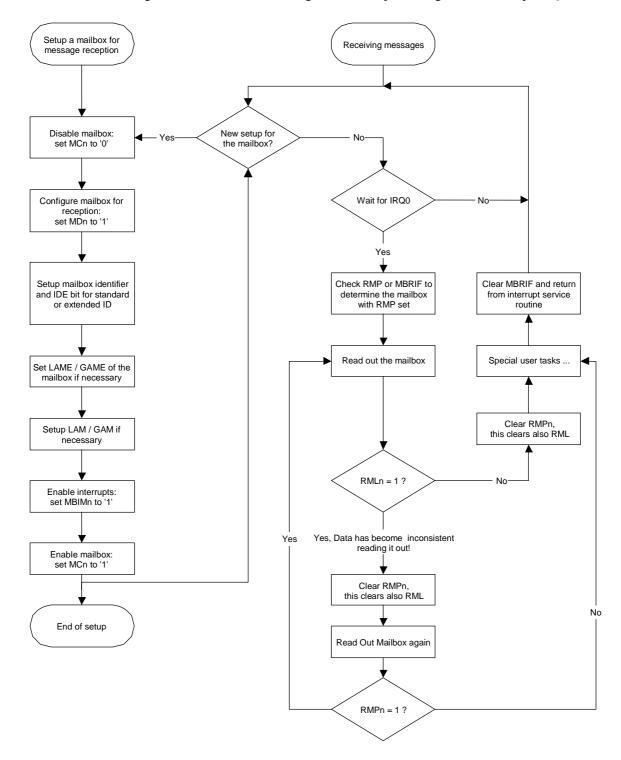

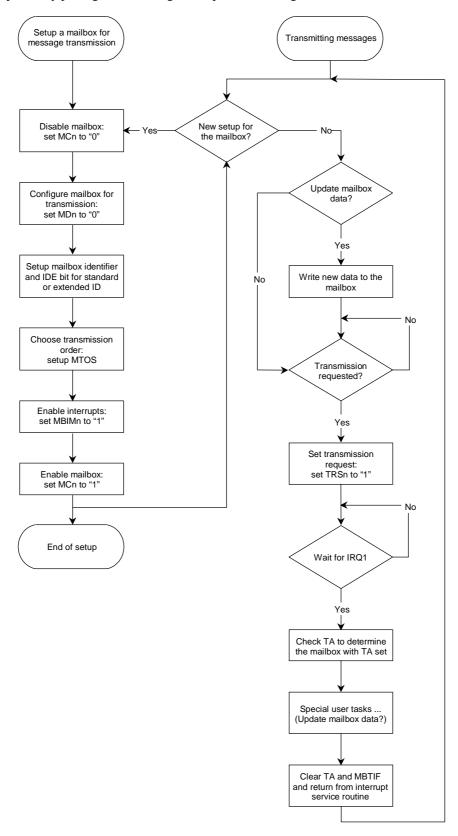

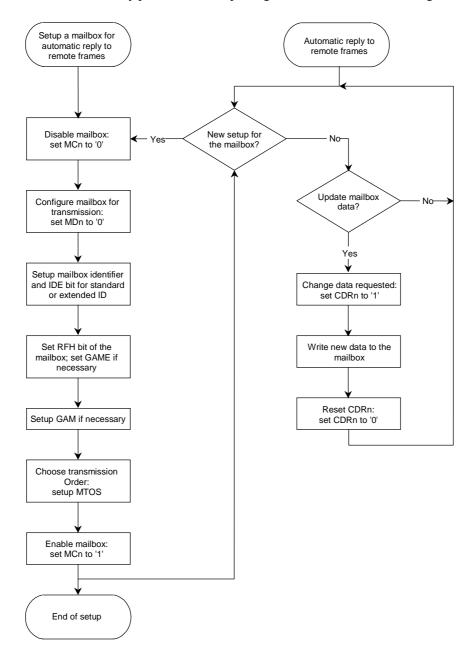

| 7. <del>4</del><br>7.5 | Handling of Message-Objects                |      |

|                        |                                            |      |

| 8. Par                 | rallel Interface (PORT)                    | 8-1  |

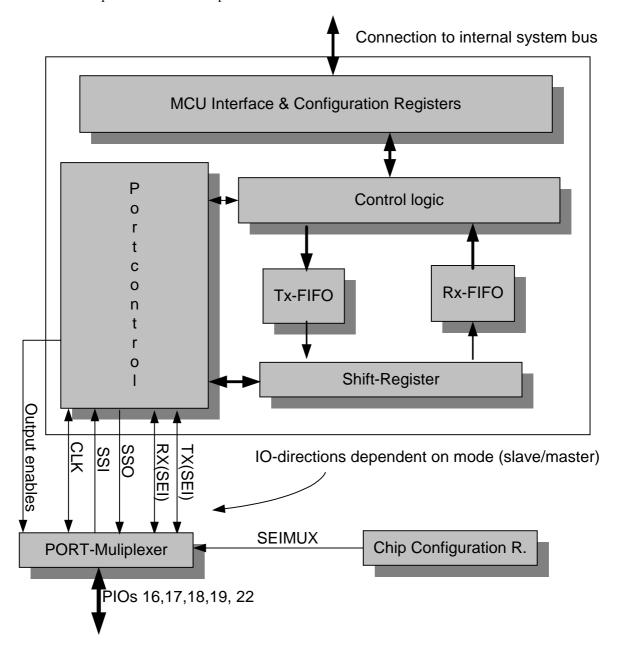

| 9. Sync  | chronous Serial I/O (TXSEI)       | 9-1   |

|----------|-----------------------------------|-------|

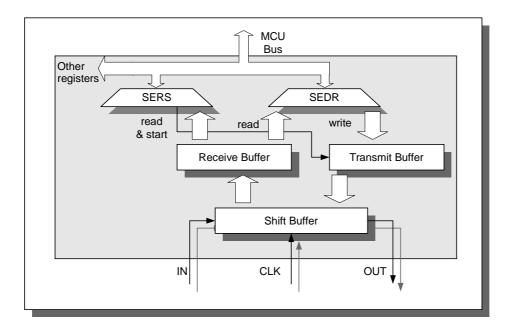

| 9.1      | TXSEI Structure                   | 9-2   |

| 9.2      | Registers                         | 9-3   |

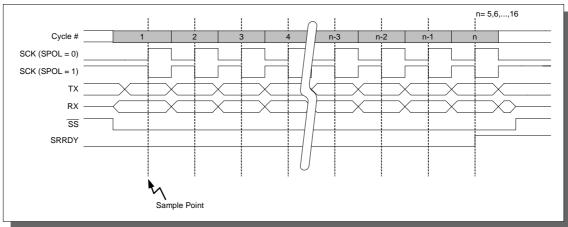

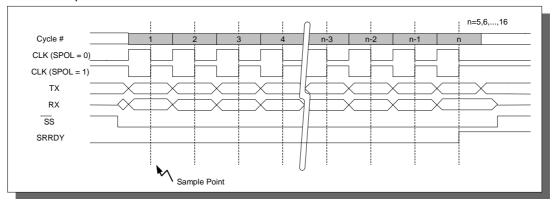

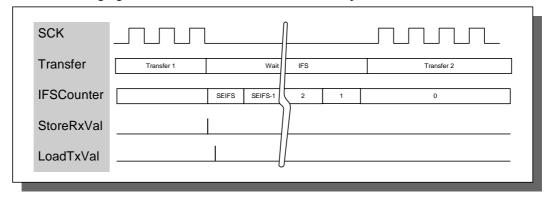

| 9.3      | TXSEI Operations                  | 9-15  |

| 9.4      | Interrupts                        | 9-19  |

| 10. Asyı | nchronous Serial Interface (UART) | 10-1  |

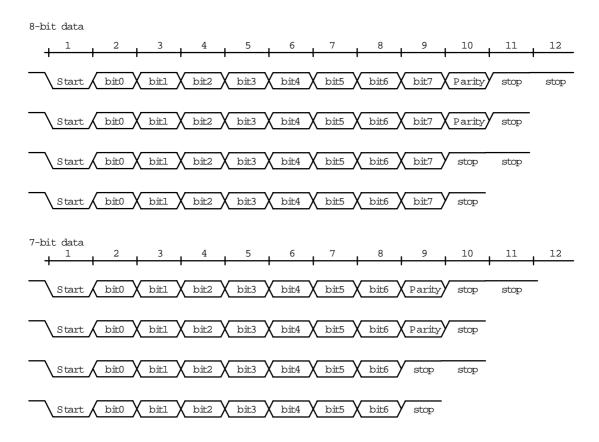

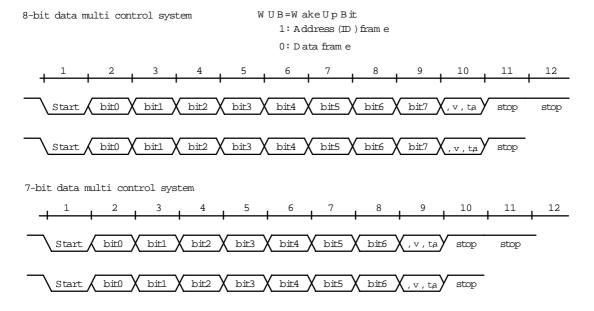

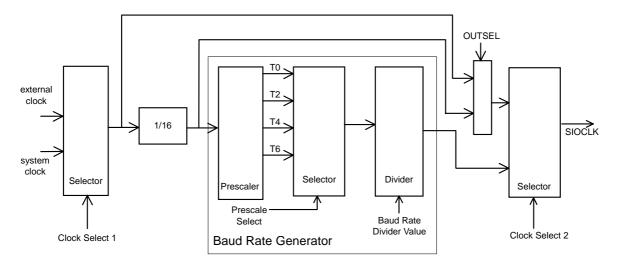

| 10.1     | Operations on Serial Interface    | 10-1  |

| 10.2     | Registers                         | 10-10 |

| 10.3     | Timings                           | 10-19 |

| 10.4     | Flow Charts                       | 10-21 |

| 11. Elec | trical Characteristics            | 11-1  |

| 11.1     | DC Characteristics of TMPR3916    | 11-1  |

| 11.2     | Power Up Sequence                 | 11-2  |

| 11.3     | Crystal Oscillator                | 11-3  |

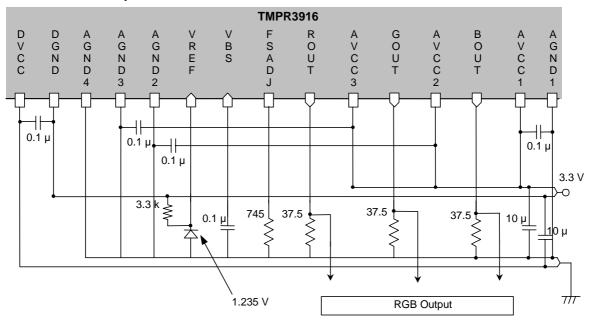

| 11.4     | View DAC                          | 11-4  |

| 11.5     | Standby Mode Timing               | 11-5  |

| 11.6     | Boot Device                       | 11-5  |

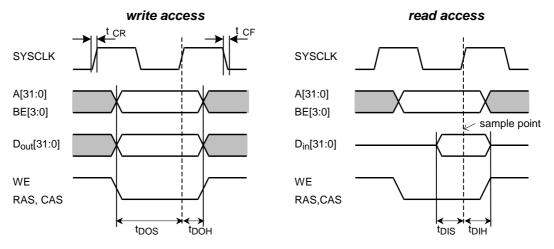

| 11.7     | SDRAM Timing                      | 11-6  |

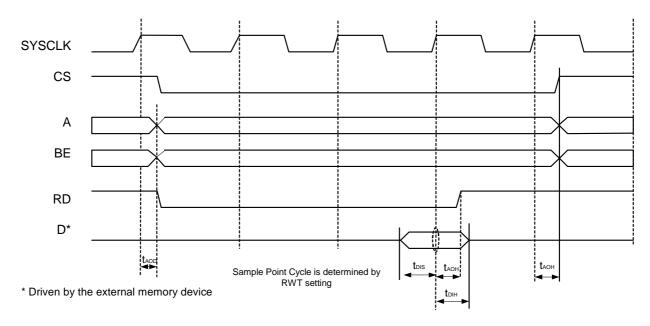

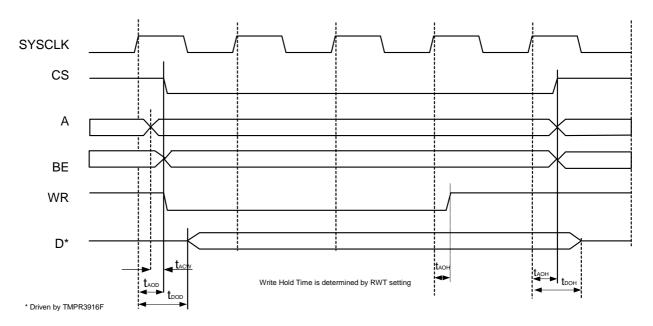

| 11.8     | ROM / SRAM Timing                 | 11-7  |

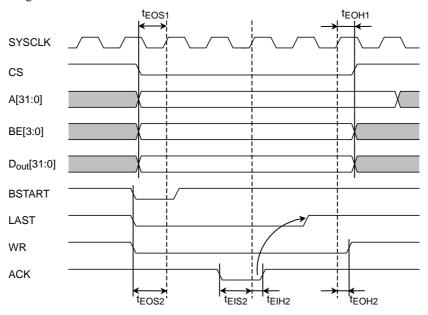

| 11.9     | External Slave                    | 11-8  |

| 11.10    | External Interrupts and NMI       | 11-10 |

| 11.11    | General Purpose I/O (PORT Module) | 11-10 |

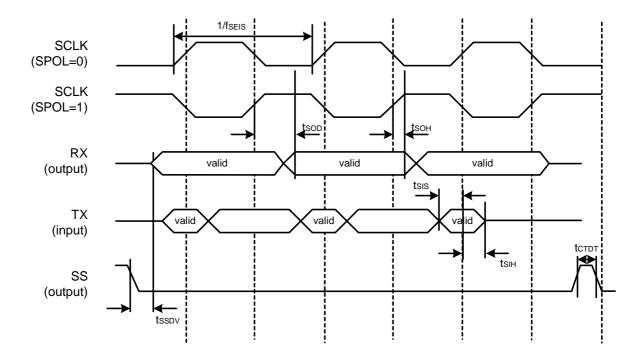

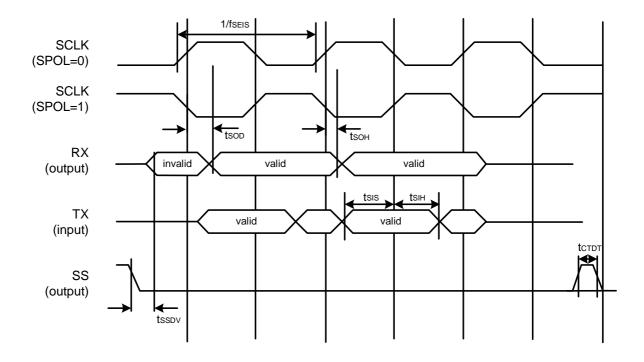

| 11.12    | TXSEI Timing                      | 11-11 |

| 12. Pack | age Dimension                     | 12-1  |

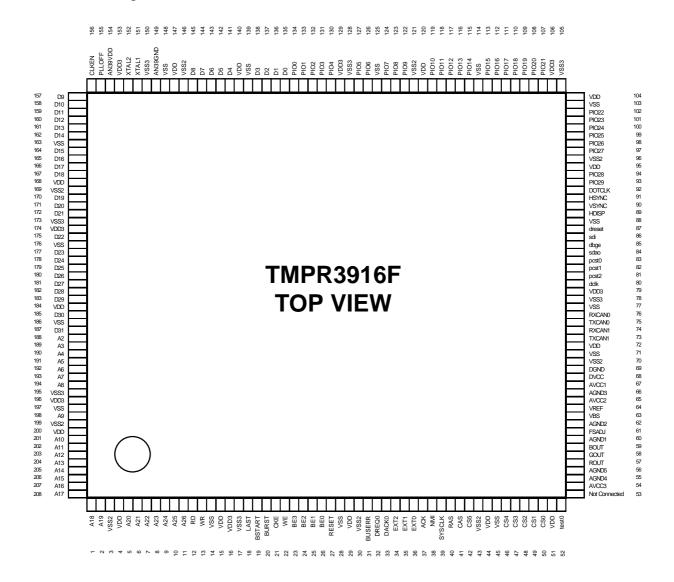

| 12.1     | Pin Assignment                    | 12-1  |

| 12.2     | Pin Functions                     | 12-5  |

| Annendi  | v Δ Register Overview of TMPR3016 | Δ_1   |

# 1. Using Toshiba Semiconductors Safely

TOSHIBA are continually working to improve the quality and the reliability of their products.

Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

# 2. Safety Precautions

This section lists important precautions which users of semiconductor devices (and anyone else) should observe in order to avoid injury and damage to property, and to ensure safe and correct use of devices.

Please be sure that you understand the meanings of the labels and the graphic symbol described below before you move on to the detailed descriptions of the precautions.

# [Explanation of labels]

Indicates an imminently hazardous situation which will result in death or serious injury if you do not follow instructions.

Indicates a potentially hazardous situation which could result in death or serious injury if you do not follow instructions.

Indicates a potentially hazardous situation which if not avoided, may result in minor injury or moderate injury.

# [Explanation of graphic symbol]

| Graphic symbol | Meaning                                                               |

|----------------|-----------------------------------------------------------------------|

| <b>▲</b>       | Indicates that caution is required (laser beam is dangerous to eyes). |

# 2.1 General Precautions regarding Semiconductor Devices

# **ACAUTION**

Do not use devices under conditions exceeding their absolute maximum ratings (e.g. current, voltage, power dissipation or temperature).

This may cause the device to break down, degrade its performance, or cause it to catch fire or explode resulting in injury.

Do not insert devices in the wrong orientation.

Make sure that the positive and negative terminals of power supplies are connected correctly. Otherwise the rated maximum current or power dissipation may be exceeded and the device may break down or undergo performance degradation, causing it to catch fire or explode and resulting in injury.

When power to a device is on, do not touch the device's heat sink.

Heat sinks become hot, so you may burn your hand.

Do not touch the tips of device leads.

Because some types of device have leads with pointed tips, you may prick your finger.

When conducting any kind of evaluation, inspection or testing, be sure to connect the testing equipment's electrodes or probes to the pins of the device under test before powering it on.

Otherwise, you may receive an electric shock causing injury.

Before grounding an item of measuring equipment or a soldering iron, check that there is no electrical leakage from it.

Electrical leakage may cause the device which you are testing or soldering to break down, or could give you an electric shock.

Always wear protective glasses when cutting the leads of a device with clippers or a similar tool.

If you do not, small bits of metal flying off the cut ends may damage your eyes.

# 2.2 Precautions Specific to Each Product Group

# 2.2.1 Optical semiconductor devices

# **A DANGER**

When a visible semiconductor laser is operating, do not look directly into the laser beam or look through the optical system. This is highly likely to impair vision, and in the worst case may cause blindness.

If it is necessary to examine the laser apparatus, for example to inspect its optical characteristics, always wear the appropriate type of laser protective glasses as stipulated by IEC standard IEC825-1.

Ensure that the current flowing in an LED device does not exceed the device's maximum rated current.

This is particularly important for resin-packaged LED devices, as excessive current may cause the package resin to blow up, scattering resin fragments and causing injury.

When testing the dielectric strength of a photocoupler, use testing equipment which can shut off the supply voltage to the photocoupler. If you detect a leakage current of more than 100  $\mu$ A, use the testing equipment to shut off the photocoupler's supply voltage; otherwise a large short-circuit current will flow continuously, and the device may break down or burst into flames, resulting in fire or injury.

When incorporating a visible semiconductor laser into a design, use the device's internal photodetector or a separate photodetector to stabilize the laser's radiant power so as to ensure that laser beams exceeding the laser's rated radiant power cannot be emitted.

If this stabilizing mechanism does not work and the rated radiant power is exceeded, the device may break down or the excessively powerful laser beams may cause injury.

# 2.2.2 Power devices

Never touch a power device while it is powered on. Also, after turning off a power device, do not touch it until it has thoroughly discharged all remaining electrical charge.

Touching a power device while it is powered on or still charged could cause a severe electric shock, resulting in death or serious injury.

When conducting any kind of evaluation, inspection or testing, be sure to connect the testing equipment's electrodes or probes to the device under test before powering it on.

When you have finished, discharge any electrical charge remaining in the device.

Connecting the electrodes or probes of testing equipment to a device while it is powered on may result in electric shock, causing injury.

# **AWARNING**

Do not use devices under conditions which exceed their absolute maximum ratings (current, voltage, power dissipation, temperature etc.).

This may cause the device to break down, causing a large short-circuit current to flow, which may in turn cause it to catch fire or explode, resulting in fire or injury.

Use a unit which can detect short-circuit currents and which will shut off the power supply if a short-circuit occurs.

If the power supply is not shut off, a large short-circuit current will flow continuously, which may in turn cause the device to catch fire or explode, resulting in fire or injury.

When designing a case for enclosing your system, consider how best to protect the user from shrapnel in the event of the device catching fire or exploding.

Flying shrapnel can cause injury.

When conducting any kind of evaluation, inspection or testing, always use protective safety tools such as a cover for the device. Otherwise you may sustain injury caused by the device catching fire or exploding.

Make sure that all metal casings in your design are grounded to earth.

Even in modules where a device's electrodes and metal casing are insulated, capacitance in the module may cause the electrostatic potential in the casing to rise.

Dielectric breakdown may cause a high voltage to be applied to the casing, causing electric shock and injury to anyone touching it.

When designing the heat radiation and safety features of a system incorporating high-speed rectifiers, remember to take the device's forward and reverse losses into account.

The leakage current in these devices is greater than that in ordinary rectifiers; as a result, if a high-speed rectifier is used in an extreme environment (e.g. at high temperature or high voltage), its reverse loss may increase, causing thermal runaway to occur. This may in turn cause the device to explode and scatter shrapnel, resulting in injury to the user.

A design should ensure that, except when the main circuit of the device is active, reverse bias is applied to the device gate while electricity is conducted to control circuits, so that the main circuit will become inactive.

Malfunction of the device may cause serious accidents or injuries.

# **ACAUTION**

When conducting any kind of evaluation, inspection or testing, either wear protective gloves or wait until the device has cooled properly before handling it.

Devices become hot when they are operated. Even after the power has been turned off, the device will retain residual heat which may cause a burn to anyone touching it.

# 2.2.3 Bipolar ICs (for use in automobiles)

# **ACAUTION**

If your design includes an inductive load such as a motor coil, incorporate diodes or similar devices into the design to prevent negative current from flowing in.

The load current generated by powering the device on and off may cause it to function erratically or to break down, which could in turn cause injury.

Ensure that the power supply to any device which incorporates protective functions is stable.

If the power supply is unstable, the device may operate erratically, preventing the protective functions from working correctly. If

protective functions fail, the device may break down causing injury to the user.

# 3. General Safety Precautions and Usage Considerations

This section is designed to help you gain a better understanding of semiconductor devices, so as to ensure the safety, quality and reliability of the devices which you incorporate into your designs.

# 3.1 From Incoming to Shipping

# 3.1.1 Electrostatic discharge (ESD)

When handling individual devices (which are not yet mounted on a printed circuit board), be sure that the environment is protected against electrostatic electricity. Operators should wear anti-static clothing, and containers and other objects which come into direct contact with devices should be made of anti-static materials and should be grounded to earth via an 0.5- to 1.0-M $\Omega$  protective resistor.

Please follow the precautions described below; this is particularly important for devices which are marked "Be careful of static.".

- (1) Work environment

- When humidity in the working environment decreases, the human body and other insulators can easily become charged with static electricity due to friction. Maintain the recommended humidity of 40% to 60% in the work environment, while also taking into account the fact that moisture-proof-packed products may absorb moisture after unpacking.

- Be sure that all equipment, jigs and tools in the working area are grounded to earth.

- Place a conductive mat over the floor of the work area, or take other appropriate measures, so that the floor surface is protected against static electricity and is grounded to earth. The surface resistivity should be  $10^4$  to  $10^8$   $\Omega$ /sq and the resistance between surface and ground, 7.5  $\times$   $10^5$  to  $10^8$   $\Omega$

- Cover the workbench surface also with a conductive mat (with a surface resistivity of  $10^4$  to  $10^8~\Omega/\text{sq}$ , for a resistance between surface and ground of  $7.5\times10^5$  to  $10^8~\Omega)$ . The purpose of this is to disperse static electricity on the surface (through resistive components) and ground it to earth. Workbench surfaces must not be constructed of low-resistance metallic materials that allow rapid static discharge when a charged device touches them directly.

- Pay attention to the following points when using automatic equipment in your workplace:

- (a) When picking up ICs with a vacuum unit, use a conductive rubber fitting on the end of the pick-up wand to protect against electrostatic charge.

- (b) Minimize friction on IC package surfaces. If some rubbing is unavoidable due to the device's mechanical structure, minimize the friction plane or use material with a small friction coefficient and low electrical resistance. Also, consider the use of an ionizer.

- (c) In sections which come into contact with device lead terminals, use a material which dissipates static electricity.

- (d) Ensure that no statically charged bodies (such as work clothes or the human body) touch the devices.

- (e) Make sure that sections of the tape carrier which come into contact with installation devices or other electrical machinery are made of a low-resistance material.

- (f) Make sure that jigs and tools used in the assembly process do not touch devices.

- (g) In processes in which packages may retain an electrostatic charge, use an ionizer to neutralize the ions.

- Make sure that CRT displays in the working area are protected against static charge, for example by a VDT filter. As much as possible, avoid turning displays on and off. Doing so can cause electrostatic induction in devices.

- Keep track of charged potential in the working area by taking periodic measurements.

- Ensure that work chairs are protected by an anti-static textile cover and are grounded to the floor surface by a grounding chain. (Suggested resistance between the seat surface and grounding chain is  $7.5 \times 10^5$  to  $10^{12}\Omega$ .)

- Install anti-static mats on storage shelf surfaces. (Suggested surface resistivity is  $10^4$  to  $10^8$   $\Omega/\text{sq}$ ; suggested resistance between surface and ground is  $7.5 \times 10^5$  to  $10^8$   $\Omega$ .)

- For transport and temporary storage of devices, use containers (boxes, jigs or bags) that are made of anti-static materials or materials which dissipate electrostatic charge.

- Make sure that cart surfaces which come into contact with device packaging are made of materials which will conduct static electricity, and verify that they are grounded to the floor surface via a grounding chain.

- In any location where the level of static electricity is to be closely controlled, the ground resistance level should be Class 3 or above. Use different ground wires for all items of equipment which may come into physical contact with devices.

- (2) Operating environment

- Operators must wear anti-static clothing and conductive shoes (or a leg or heel strap).

- ullet Operators must wear a wrist strap grounded to earth via a resistor of about 1 M $\Omega$ .

- Soldering irons must be grounded from iron tip to earth, and must be used only at low voltages (6 V to 24 V).

- If the tweezers you use are likely to touch the device terminals, use anti-static tweezers and in particular avoid metallic tweezers. If a charged device touches a low-resistance tool, rapid discharge can occur. When using vacuum tweezers, attach a conductive chucking pat to the tip, and connect it to a dedicated ground used especially for anti-static purposes (suggested resistance value:  $10^4$  to  $10^8$   $\Omega$ ).

- Do not place devices or their containers near sources of strong electrical fields (such as above a CRT).

- When storing printed circuit boards which have devices mounted on them, use a board container or bag that is protected against static charge. To avoid the occurrence of static charge or discharge due to friction, keep the boards separate from one other and do not stack them directly on top of one another.

- Ensure, if possible, that any articles (such as clipboards) which are brought to any location where the level of static electricity must be closely controlled are constructed of anti-static materials.

- In cases where the human body comes into direct contact with a device, be sure to wear antistatic finger covers or gloves (suggested resistance value:  $10^8 \Omega$  or less).

- Equipment safety covers installed near devices should have resistance ratings of  $10^9 \Omega$  or less.

- If a wrist strap cannot be used for some reason, and there is a possibility of imparting friction to devices, use an ionizer.

- The transport film used in TCP products is manufactured from materials in which static charges tend to build up. When using these products, install an ionizer to prevent the film from being charged with static electricity. Also, ensure that no static electricity will be applied to the product's copper foils by taking measures to prevent static occurring in the peripheral equipment.

# 3.1.2 Vibration, impact and stress

Handle devices and packaging materials with care. To avoid damage to devices, do not toss or drop packages. Ensure that devices are not subjected to mechanical vibration or shock during transportation. Ceramic package devices and devices in canister-type packages which have empty space inside them are subject to damage from vibration and shock because the bonding wires are secured only at their ends.

Plastic molded devices, on the other hand, have a relatively high level of resistance to vibration and mechanical shock because their bonding wires are enveloped and fixed in resin. However, when any device or package type is installed in target equipment, it is to some extent susceptible to wiring disconnections and other damage from vibration, shock and stressed solder junctions. Therefore when devices are incorporated into the design of equipment which will be subject to vibration, the structural design of the equipment must be thought out carefully.

If a device is subjected to especially strong vibration, mechanical shock or stress, the package or the chip itself may crack. In products such as CCDs which incorporate window glass, this could cause surface flaws in the glass or cause the connection between the glass and the ceramic to separate.

Furthermore, it is known that stress applied to a semiconductor device through the package changes the resistance characteristics of the chip because of piezoelectric effects. In analog circuit design attention must be paid to the problem of package stress as well as to the dangers of vibration and shock as described above.

# 3.2 Storage

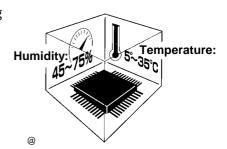

# 3.2.1 General storage

- Avoid storage locations where devices will be exposed to moisture or direct sunlight.

- Follow the instructions printed on the device cartons regarding transportation and storage.

- The storage area temperature should be kept within a temperature range of 5°C to 35°C, and relative humidity should be maintained at between 45% and 75%.

- Do not store devices in the presence of harmful (especially corrosive) gases, or in dusty conditions.

- Use storage areas where there is minimal temperature fluctuation. Rapid temperature changes can cause moisture to form on stored devices, resulting in lead oxidation or corrosion. As a result, the solderability of the leads will be degraded.

- When repacking devices, use anti-static containers.

- Do not allow external forces or loads to be applied to devices while they are in storage.

- If devices have been stored for more than two years, their electrical characteristics should be tested and their leads should be tested for ease of soldering before they are used.

# 3.2.2 Moisture-proof packing

Moisture-proof packing should be handled with care. The handling procedure specified for each packing type should be followed scrupulously. If the proper procedures are not followed, the quality and reliability of devices may be degraded. This section describes general precautions for handling moisture-proof packing. Since the details may differ from device to device, refer also to the relevant individual datasheets or databook.

- (1) General precautions Follow the instructions printed on the device cartons regarding transportation and storage.

- Do not drop or toss device packing. The laminated aluminum material in it can be rendered ineffective by rough handling.

- The storage area temperature should be kept within a temperature range of 5°C to 30°C, and relative humidity should be maintained at 90% (max). Use devices within 12 months of the date marked on the package seal.

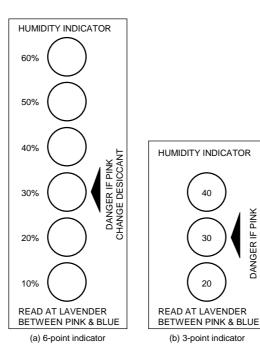

• If the 12-month storage period has expired, or if the 30% humidity indicator shown in Figure 1 is pink when the packing is opened, it may be advisable, depending on the device and packing type, to back the devices at high temperature to remove any moisture. Please refer to the table below. After the pack has been opened, use the devices in a 5°C to 30°C. 60% RH environment and within the effective usage period listed on the moisture-proof package. If the effective usage period has expired, or if the packing has been stored in a high-humidity environment, bake the devices at high temperature.

| Packing | Moisture removal                                                                                                                                                                    |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tray    | If the packing bears the "Heatproof" marking or indicates the maximum temperature which it can withstand, bake at 125°C for 20 hours. (Some devices require a different procedure.) |

| Tube    | Transfer devices to trays bearing the "Heatproof" marking or indicating the temperature which they can withstand, or to aluminum tubes before baking at 125°C for 20 hours.         |

| Таре    | Deviced packed on tape cannot be baked and must be used within the effective usage period after unpacking, as specified on the packing.                                             |

- When baking devices, protect the devices from static electricity.

- Moisture indicators can detect the approximate humidity level at a standard temperature of 25°C. 6-point indicators and 3-point indicators are currently in use, but eventually all indicators will be 3-point indicators.

Figure 1 Humidity indicator

# 3.3 Design

Care must be exercised in the design of electronic equipment to achieve the desired reliability. It is important not only to adhere to specifications concerning absolute maximum ratings and recommended operating conditions, it is also important to consider the overall environment in which equipment will be used, including factors such as the ambient temperature, transient noise and voltage and current surges, as well as mounting conditions which affect device reliability. This section describes some general precautions which you should observe when designing circuits and when mounting devices on printed circuit boards.

For more detailed information about each product family, refer to the relevant individual technical datasheets available from Toshiba.

# 3.3.1 Absolute maximum ratings

# **ACAUTION**

Do not use devices under conditions in which their absolute maximum ratings (e.g. current, voltage, power dissipation or temperature) will be exceeded. A device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user.

The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Although absolute maximum ratings differ from product to product, they essentially concern the voltage and current at each pin, the allowable power dissipation, and the junction and storage temperatures.

If the voltage or current on any pin exceeds the absolute maximum rating, the device's internal circuitry can become degraded. In the worst case, heat generated in internal circuitry can fuse wiring or cause the semiconductor chip to break down.

If storage or operating temperatures exceed rated values, the package seal can deteriorate or the wires can become disconnected due to the differences between the thermal expansion coefficients of the materials from which the device is constructed.

# 3.3.2 Recommended operating conditions

The recommended operating conditions for each device are those necessary to guarantee that the device will operate as specified in the datasheet.

If greater reliability is required, derate the device's absolute maximum ratings for voltage, current, power and temperature before using it.

# 3.3.3 Derating

When incorporating a device into your design, reduce its rated absolute maximum voltage, current, power dissipation and operating temperature in order to ensure high reliability. Since derating differs from application to application, refer to the technical datasheets available for the various devices used in your design.

# 3.3.4 Unused pins

If unused pins are left open, some devices can exhibit input instability problems, resulting in malfunctions such as abrupt increase in current flow. Similarly, if the unused output pins on a device are connected to the power supply pin, the ground pin or to other output pins, the IC may malfunction or break down.

Since the details regarding the handling of unused pins differ from device to device and from pin

to pin, please follow the instructions given in the relevant individual datasheets or databook.

CMOS logic IC inputs, for example, have extremely high impedance. If an input pin is left open, it can easily pick up extraneous noise and become unstable. In this case, if the input voltage level reaches an intermediate level, it is possible that both the P-channel and N-channel transistors will be turned on, allowing unwanted supply current to flow. Therefore, ensure that the unused input pins of a device are connected to the power supply (Vcc) pin or ground (GND) pin of the same device. For details of what to do with the pins of heat sinks, refer to the relevant technical datasheet and databook.

# 3.3.5 Latch-up

Latch-up is an abnormal condition inherent in CMOS devices, in which Vcc gets shorted to ground. This happens when a parasitic PN-PN junction (thyristor structure) internal to the CMOS chip is turned on, causing a large current of the order of several hundred mA or more to flow between Vcc and GND, eventually causing the device to break down.

Latch-up occurs when the input or output voltage exceeds the rated value, causing a large current to flow in the internal chip, or when the voltage on the Vcc (Vdd) pin exceeds its rated value, forcing the internal chip into a breakdown condition. Once the chip falls into the latch-up state, even though the excess voltage may have been applied only for an instant, the large current continues to flow between Vcc (Vdd) and GND (Vss). This causes the device to heat up and, in extreme cases, to emit gas fumes as well. To avoid this problem, observe the following precautions:

- (1) Do not allow voltage levels on the input and output pins either to rise above Vcc (Vdd) or to fall below GND (Vss). Also, follow any prescribed power-on sequence, so that power is applied gradually or in steps rather than abruptly.

- (2) Do not allow any abnormal noise signals to be applied to the device.

- (3) Set the voltage levels of unused input pins to Vcc (Vdd) or GND (Vss).

- (4) Do not connect output pins to one another.

# 3.3.6 Input/Output protection

Wired-AND configurations, in which outputs are connected together, cannot be used, since this short-circuits the outputs. Outputs should, of course, never be connected to Vcc (Vdd) or GND (Vss).

Furthermore, ICs with tri-state outputs can undergo performance degradation if a shorted output current is allowed to flow for an extended period of time. Therefore, when designing circuits, make sure that tri-state outputs will not be enabled simultaneously.

# 3.3.7 Load capacitance

Some devices display increased delay times if the load capacitance is large. Also, large charging and discharging currents will flow in the device, causing noise. Furthermore, since outputs are shorted for a relatively long time, wiring can become fused.

Consult the technical information for the device being used to determine the recommended load capacitance.

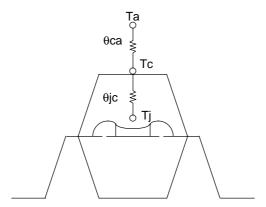

# 3.3.8 Thermal design

The failure rate of semiconductor devices is greatly increased as operating temperatures increase. As shown in Figure 2, the internal thermal stress on a device is the sum of the ambient temperature and the temperature rise due to power dissipation in the device. Therefore, to achieve optimum reliability, observe the following precautions concerning thermal design:

- (1) Keep the ambient temperature (Ta) as low as possible.

- (2) If the device's dynamic power dissipation is relatively large, select the most appropriate circuit board material, and consider the use of heat sinks or of forced air cooling. Such measures will help lower the thermal resistance of the package.

- (3) Derate the device's absolute maximum ratings to minimize thermal stress from power dissipation.

```

\thetaja = \thetajc + \thetaca

```

$\theta ja = (Tj-Ta) / P$

$\theta jc = (Tj-Tc) / P$

$\theta$ ca = (Tc-Ta) / P

in which  $\theta$ ja = thermal resistance between junction and surrounding air (°C/W)

$\theta$ jc = thermal resistance between junction and package surface, or internal thermal resistance (°C/W)

$\theta$ ca = thermal resistance between package surface and surrounding air, or external thermal resistance (°C/W)

Tj = junction temperature or chip temperature (°C)

Tc = package surface temperature or case temperature (°C)

Ta = ambient temperature (°C)

P = power dissipation (W)

Figure 2 Thermal resistance of package

# 3.3.9 Interfacing

When connecting inputs and outputs between devices, make sure input voltage (VIL/VIH) and output voltage (VOL/VOH) levels are matched. Otherwise, the devices may malfunction. When connecting devices operating at different supply voltages, such as in a dual-power-supply system, be aware that erroneous power-on and power-off sequences can result in device breakdown. For details of how to interface particular devices, consult the relevant technical datasheets and databooks. If you have any questions or doubts about interfacing, contact your nearest Toshiba office or distributor.

# 3.3.10 Decoupling

Spike currents generated during switching can cause Vcc (Vdd) and GND (Vss) voltage levels to fluctuate, causing ringing in the output waveform or a delay in response speed. (The power supply and GND wiring impedance is normally 50  $\Omega$  to 100  $\Omega$ .) For this reason, the impedance of power supply lines with respect to high frequencies must be kept low. This can be accomplished by using thick and short wiring for the Vcc (Vdd) and GND (Vss) lines and by installing decoupling capacitors (of approximately 0.01  $\mu F$  to 1  $\mu F$  capacitance) as high-frequency filters between Vcc (Vdd) and GND (Vss) at strategic locations on the printed circuit board.

For low-frequency filtering, it is a good idea to install a 10- to 100- $\mu$ F capacitor on the printed circuit board (one capacitor will suffice). If the capacitance is excessively large, however, (e.g. several thousand  $\mu$ F) latch-up can be a problem. Be sure to choose an appropriate capacitance value.

An important point about wiring is that, in the case of high-speed logic ICs, noise is caused mainly by reflection and crosstalk, or by the power supply impedance. Reflections cause increased signal delay, ringing, overshoot and undershoot, thereby reducing the device's safety margins with respect to noise. To prevent reflections, reduce the wiring length by increasing the device mounting density so as to lower the inductance (L) and capacitance (C) in the wiring. Extreme care must be taken, however, when taking this corrective measure, since it tends to cause crosstalk between the wires. In practice, there must be a trade-off between these two factors.

# 3.3.11 External noise

Printed circuit boards with long I/O or signal pattern lines are vulnerable to induced noise or surges from outside sources. Consequently, malfunctions or breakdowns can result from overcurrent or overvoltage, depending on the types of device used. To protect against noise, lower the impedance of the pattern line or insert a noise-canceling circuit. Protective measures must also be taken against surges.

For details of the appropriate protective measures for a particular device, consult the relevant databook.

# 3.3.12 Electromagnetic interference

Widespread use of electrical and electronic equipment in recent years has brought with it radio and TV reception problems due to electromagnetic interference. To use the radio spectrum effectively and to maintain radio communications quality, each country has formulated regulations limiting the amount of electromagnetic interference which can be generated by individual products.

Electromagnetic interference includes conduction noise propagated through power supply and telephone lines, and noise from direct electromagnetic waves radiated by equipment. Different measurement methods and corrective measures are used to assess and counteract each specific type of noise.

Difficulties in controlling electromagnetic interference derive from the fact that there is no method available which allows designers to calculate, at the design stage, the strength of the electromagnetic waves which will emanate from each component in a piece of equipment. For this reason, it is only after the prototype equipment has been completed that the designer can take measurements using a dedicated instrument to determine the strength of electromagnetic interference waves. Yet it is possible during system design to incorporate some measures for the

prevention of electromagnetic interference, which can facilitate taking corrective measures once the design has been completed. These include installing shields and noise filters, and increasing the thickness of the power supply wiring patterns on the printed circuit board. One effective method, for example, is to devise several shielding options during design, and then select the most suitable shielding method based on the results of measurements taken after the prototype has been completed.

### 3.3.13 Peripheral circuits

In most cases semiconductor devices are used with peripheral circuits and components. The input and output signal voltages and currents in these circuits must be chosen to match the semiconductor device's specifications. The following factors must be taken into account.

- (1) Inappropriate voltages or currents applied to a device's input pins may cause it to operate erratically. Some devices contain pull-up or pull-down resistors. When designing your system, remember to take the effect of this on the voltage and current levels into account.

- (2) The output pins on a device have a predetermined external circuit drive capability. If this drive capability is greater than that required, either incorporate a compensating circuit into your design or carefully select suitable components for use in external circuits.

### 3.3.14 Safety standards

Each country has safety standards which must be observed. These safety standards include requirements for quality assurance systems and design of device insulation. Such requirements must be fully taken into account to ensure that your design conforms to the applicable safety standards.

### Other precautions 3.3.15

- (1) When designing a system, be sure to incorporate fail-safe and other appropriate measures according to the intended purpose of your system. Also, be sure to debug your system under actual board-mounted conditions.

- (2) If a plastic-package device is placed in a strong electric field, surface leakage may occur due to the charge-up phenomenon, resulting in device malfunction. In such cases take appropriate measures to prevent this problem, for example by protecting the package surface with a conductive shield.

- (3) With some microcomputers and MOS memory devices, caution is required when powering on or resetting the device. To ensure that your design does not violate device specifications, consult the relevant databook for each constituent device.

- (4) Ensure that no conductive material or object (such as a metal pin) can drop onto and short the leads of a device mounted on a printed circuit board.

### 3.4 Inspection, Testing and Evaluation

### 3.4.1 Grounding

Ground all measuring instruments, jigs, tools and soldering irons to earth. **ACAUTION** Electrical leakage may cause a device to break down or may result in electric shock.

# 3.4.2 Inspection Sequence

# **ACAUTION**

- ① Do not insert devices in the wrong orientation. Make sure that the positive and negative electrodes of the power supply are correctly connected. Otherwise, the rated maximum current or maximum power dissipation may be exceeded and the device may break down or undergo performance degradation, causing it to catch fire or explode, resulting in injury to the user.

- ② When conducting any kind of evaluation, inspection or testing using AC power with a peak voltage of 42.4 V or DC power exceeding 60 V, be sure to connect the electrodes or probes of the testing equipment to the device under test before powering it on. Connecting the electrodes or probes of testing equipment to a device while it is powered on may result in electric shock, causing injury.

- (1) Apply voltage to the test jig only after inserting the device securely into it. When applying or removing power, observe the relevant precautions, if any.

- (2) Make sure that the voltage applied to the device is off before removing the device from the test jig. Otherwise, the device may undergo performance degradation or be destroyed.

- (3) Make sure that no surge voltages from the measuring equipment are applied to the device.

- (4) The chips housed in tape carrier packages (TCPs) are bare chips and are therefore exposed. During inspection take care not to crack the chip or cause any flaws in it. Electrical contact may also cause a chip to become faulty. Therefore make sure that nothing comes into electrical contact with the chip.

# 3.5 Mounting

There are essentially two main types of semiconductor device package: lead insertion and surface mount. During mounting on printed circuit boards, devices can become contaminated by flux or damaged by thermal stress from the soldering process. With surface-mount devices in particular, the most significant problem is thermal stress from solder reflow, when the entire package is subjected to heat. This section describes a recommended temperature profile for each mounting method, as well as general precautions which you should take when mounting devices on printed circuit boards. Note, however, that even for devices with the same package type, the appropriate mounting method varies according to the size of the chip and the size and shape of the lead frame. Therefore, please consult the relevant technical datasheet and databook.

# 3.5.1 Lead forming

- ① Always wear protective glasses when cutting the leads of a device with clippers or a similar tool. If you do not, small bits of metal flying off the cut ends may damage your eyes.

- ② Do not touch the tips of device leads. Because some types of device have leads with pointed tips, you may prick your finger.

Semiconductor devices must undergo a process in which the leads are cut and formed before the devices can be mounted on a printed circuit board. If undue stress is applied to the interior of a device during this process, mechanical breakdown or performance degradation can result. This is attributable primarily to differences between the stress on the device's external leads and the stress on the internal leads. If the relative difference is great enough, the device's internal leads, adhesive properties or sealant can be damaged. Observe these precautions during the lead-forming process (this does not apply to surface-mount devices):

- (1) Lead insertion hole intervals on the printed circuit board should match the lead pitch of the device precisely.

- (2) If lead insertion hole intervals on the printed circuit board do not precisely match the lead pitch of the device, do not attempt to forcibly insert devices by pressing on them or by pulling on their leads.

- (3) For the minimum clearance specification between a device and a printed circuit board, refer to the relevant device's datasheet and databook. If necessary, achieve the required clearance by forming the device's leads appropriately. Do not use the spacers which are used to raise devices above the surface of the printed circuit board during soldering to achieve clearance. These spacers normally continue to expand due to heat, even after the solder has begun to solidify; this applies severe stress to the device.

- (4) Observe the following precautions when forming the leads of a device prior to mounting.

- Use a tool or jig to secure the lead at its base (where the lead meets the device package) while bending so as to avoid mechanical stress to the device. Also avoid bending or stretching device leads repeatedly.

- Be careful not to damage the lead during lead forming.

- Follow any other precautions described in the individual datasheets and databooks for each device and package type.

# 3.5.2 Socket mounting

- (1) When socket mounting devices on a printed circuit board, use sockets which match the inserted device's package.

- (2) Use sockets whose contacts have the appropriate contact pressure. If the contact pressure is insufficient, the socket may not make a perfect contact when the device is repeatedly inserted and removed; if the pressure is excessively high, the device leads may be bent or damaged when they are inserted into or removed from the socket.

- (3) When soldering sockets to the printed circuit board, use sockets whose construction prevents flux from penetrating into the contacts or which allows flux to be completely cleaned off.

- (4) Make sure the coating agent applied to the printed circuit board for moisture-proofing purposes does not stick to the socket contacts.

- (5) If the device leads are severely bent by a socket as it is inserted or removed and you wish to repair the leads so as to continue using the device, make sure that this lead correction is only performed once. Do not use devices whose leads have been corrected more than once.

- (6) If the printed circuit board with the devices mounted on it will be subjected to vibration from external sources, use sockets which have a strong contact pressure so as to prevent the sockets and devices from vibrating relative to one another.

# 3.5.3 Soldering temperature profile

The soldering temperature and heating time vary from device to device. Therefore, when specifying the mounting conditions, refer to the individual datasheets and databooks for the devices used.

(1) Using a soldering iron

Complete soldering within ten seconds for lead temperatures of up to  $260^{\circ}$ C, or within three seconds for lead temperatures of up to  $350^{\circ}$ C.

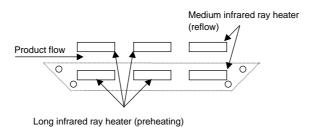

- (2) Using medium infrared ray reflow

- Heating top and bottom with long or medium infrared rays is recommended (see Figure 3).

Figure 3 Heating top and bottom with long or medium infrared rays

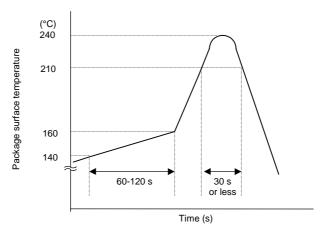

- Complete the infrared ray reflow process within 30 seconds at a package surface temperature of between 210°C and 240°C.

- Refer to Figure 4 for an example of a good temperature profile for infrared or hot air reflow.

Figure 4 Sample temperature profile for infrared or hot air reflow

- (3) Using hot air reflow

- Complete hot air reflow within 30 seconds at a package surface temperature of between 210°C and 240°C.

- For an example of a recommended temperature profile, refer to Figure 4 above.

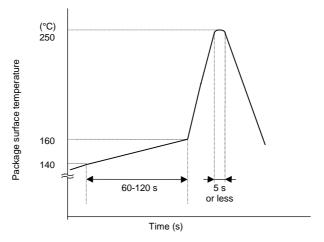

- (4) Using solder flow

- Apply preheating for 60 to 120 seconds at a temperature of 150°C.

- For lead insertion-type packages, complete solder flow within 10 seconds with the temperature at the stopper (or, if there is no stopper, at a location more than 1.5 mm from the body) which does not exceed 260°C.

- For surface-mount packages, complete soldering within 5 seconds at a temperature of 250°C or

less in order to prevent thermal stress in the device.

• Figure 5 shows an example of a recommended temperature profile for surface-mount packages using solder flow.

Figure 5 Sample temperature profile for solder flow

# 3.5.4 Flux cleaning and ultrasonic cleaning

- (1) When cleaning circuit boards to remove flux, make sure that no residual reactive ions such as Na or Cl remain. Note that organic solvents react with water to generate hydrogen chloride and other corrosive gases which can degrade device performance.

- (2) Washing devices with water will not cause any problems. However, make sure that no reactive ions such as sodium and chlorine are left as a residue. Also, be sure to dry devices sufficiently after washing.

- (3) Do not rub device markings with a brush or with your hand during cleaning or while the devices are still wet from the cleaning agent. Doing so can rub off the markings.

- (4) The dip cleaning, shower cleaning and steam cleaning processes all involve the chemical action of a solvent. Use only recommended solvents for these cleaning methods. When immersing devices in a solvent or steam bath, make sure that the temperature of the liquid is 50°C or below, and that the circuit board is removed from the bath within one minute.

- (5) Ultrasonic cleaning should not be used with hermetically-sealed ceramic packages such as a leadless chip carrier (LCC), pin grid array (PGA) or charge-coupled device (CCD), because the bonding wires can become disconnected due to resonance during the cleaning process. Even if a device package allows ultrasonic cleaning, limit the duration of ultrasonic cleaning to as short a time as possible, since long hours of ultrasonic cleaning degrade the adhesion between the mold resin and the frame material. The following ultrasonic cleaning conditions are recommended:

Frequency: 27 kHz ~ 29 kHz

Ultrasonic output power: 300 W or less (0.25 W/cm<sup>2</sup> or less)

Cleaning time: 30 seconds or less

Suspend the circuit board in the solvent bath during ultrasonic cleaning in such a way that the ultrasonic vibrator does not come into direct contact with the circuit board or the device.

# 3.5.5 No cleaning

If analog devices or high-speed devices are used without being cleaned, flux residues may cause minute amounts of leakage between pins. Similarly, dew condensation, which occurs in environments containing residual chlorine when power to the device is on, may cause between-lead leakage or migration. Therefore, Toshiba recommends that these devices be cleaned. However, if the flux used contains only a small amount of halogen (0.05W% or less), the devices may be used without cleaning without any problems.

# 3.5.6 Mounting tape carrier packages (TCPs)

- (1) When tape carrier packages (TCPs) are mounted, measures must be taken to prevent electrostatic breakdown of the devices.

- (2) If devices are being picked up from tape, or outer lead bonding (OLB) mounting is being carried out, consult the manufacturer of the insertion machine which is being used, in order to establish the optimum mounting conditions in advance and to avoid any possible hazards.

- (3) The base film, which is made of polyimide, is hard and thin. Be careful not to cut or scratch your hands or any objects while handling the tape.

- (4) When punching tape, try not to scatter broken pieces of tape too much.

- (5) Treat the extra film, reels and spacers left after punching as industrial waste, taking care not to destroy or pollute the environment.

- (6) Chips housed in tape carrier packages (TCPs) are bare chips and therefore have their reverse side exposed. To ensure that the chip will not be cracked during mounting, ensure that no mechanical shock is applied to the reverse side of the chip. Electrical contact may also cause a chip to fail. Therefore, when mounting devices, make sure that nothing comes into electrical contact with the reverse side of the chip.

If your design requires connecting the reverse side of the chip to the circuit board, please consult Toshiba or a Toshiba distributor beforehand.

# 3.5.7 Mounting chips

Devices delivered in chip form tend to degrade or break under external forces much more easily than plastic-packaged devices. Therefore, caution is required when handling this type of device.

- (1) Mount devices in a properly prepared environment so that chip surfaces will not be exposed to polluted ambient air or other polluted substances.

- (2) When handling chips, be careful not to expose them to static electricity. In particular, measures must be taken to prevent static damage during the mounting of chips. With this in mind, Toshiba recommend mounting all peripheral parts first and then mounting chips last (after all other components have been mounted).

- (3) Make sure that PCBs (or any other kind of circuit board) on which chips are being mounted do not have any chemical residues on them (such as the chemicals which were used for etching the PCBs).

- (4) When mounting chips on a board, use the method of assembly that is most suitable for maintaining the appropriate electrical, thermal and mechanical properties of the semiconductor devices used.

- \* For details of devices in chip form, refer to the relevant device's individual datasheets.

# 3.5.8 Circuit board coating

When devices are to be used in equipment requiring a high degree of reliability or in extreme environments (where moisture, corrosive gas or dust is present), circuit boards may be coated for protection. However, before doing so, you must carefully consider the possible stress and contamination effects that may result and then choose the coating resin which results in the minimum level of stress to the device.

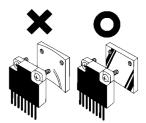

## 3.5.9 Heat sinks

- (1) When attaching a heat sink to a device, be careful not to apply excessive force to the device in the process.

- (2) When attaching a device to a heat sink by fixing it at two or more locations, evenly tighten all the screws in stages (i.e. do not fully tighten one screw while the rest are still only loosely tightened). Finally, fully tighten all the screws up to the specified torque.

- (3) Drill holes for screws in the heat sink exactly as specified. Smooth the surface by removing burrs and protrusions or indentations which might interfere with the installation of any part of the device.

- (4) A coating of silicone compound can be applied between the heat sink and the device to improve heat conductivity. Be sure to apply the coating thinly and evenly; do not use too much. Also, be sure to use a non-volatile compound, as volatile compounds can crack after a time, causing the heat radiation properties of the heat sink to deteriorate.

- (5) If the device is housed in a plastic package, use caution when selecting the type of silicone compound to be applied between the heat sink and the device. With some types, the base oil separates and penetrates the plastic package, significantly reducing the useful life of the device.

- Two recommended silicone compounds in which base oil separation is not a problem are YG6260 from Toshiba Silicone.

- (6) Heat-sink-equipped devices can become very hot during operation. Do not touch them, or you may sustain a burn.

# 3.5.10 Tightening torque

- (1) Make sure the screws are tightened with fastening torques not exceeding the torque values stipulated in individual datasheets and databooks for the devices used.

- (2) Do not allow a power screwdriver (electrical or air-driven) to touch devices.

# 3.5.11 Repeated device mounting and usage

Do not remount or re-use devices which fall into the categories listed below; these devices may cause significant problems relating to performance and reliability.

- (1) Devices which have been removed from the board after soldering

- (2) Devices which have been inserted in the wrong orientation or which have had reverse current applied

- (3) Devices which have undergone lead forming more than once

# 3.6 Protecting Devices in the Field

# 3.6.1 Temperature

Semiconductor devices are generally more sensitive to temperature than are other electronic components. The various electrical characteristics of a semiconductor device are dependent on the ambient temperature at which the device is used. It is therefore necessary to understand the temperature characteristics of a device and to incorporate device derating into circuit design. Note also that if a device is used above its maximum temperature rating, device deterioration is more rapid and it will reach the end of its usable life sooner than expected.

# 3.6.2 Humidity

Resin-molded devices are sometimes improperly sealed. When these devices are used for an extended period of time in a high-humidity environment, moisture can penetrate into the device and cause chip degradation or malfunction. Furthermore, when devices are mounted on a regular printed circuit board, the impedance between wiring components can decrease under high-humidity conditions. In systems which require a high signal-source impedance, circuit board leakage or leakage between device lead pins can cause malfunctions. The application of a moisture-proof treatment to the device surface should be considered in this case. On the other hand, operation under low-humidity conditions can damage a device due to the occurrence of electrostatic discharge. Unless damp-proofing measures have been specifically taken, use devices only in environments with appropriate ambient moisture levels (i.e. within a relative humidity range of 40% to 60%).

# 3.6.3 Corrosive gases

Corrosive gases can cause chemical reactions in devices, degrading device characteristics. For example, sulphur-bearing corrosive gases emanating from rubber placed near a device (accompanied by condensation under high-humidity conditions) can corrode a device's leads. The resulting chemical reaction between leads forms foreign particles which can cause electrical leakage.

# 3.6.4 Radioactive and cosmic rays

Most industrial and consumer semiconductor devices are not designed with protection against radioactive and cosmic rays. Devices used in aerospace equipment or in radioactive environments must therefore be shielded.

# 3.6.5 Strong electrical and magnetic fields

Devices exposed to strong magnetic fields can undergo a polarization phenomenon in their plastic material, or within the chip, which gives rise to abnormal symptoms such as impedance changes or increased leakage current. Failures have been reported in LSIs mounted near malfunctioning deflection yokes in TV sets. In such cases the device's installation location must be changed or the device must be shielded against the electrical or magnetic field. Shielding against magnetism is especially necessary for devices used in an alternating magnetic field because of the electromotive forces generated in this type of environment.

# 3.6.6 Interference from light (ultraviolet rays, sunlight, fluorescent lamps and incandescent lamps)

Light striking a semiconductor device generates electromotive force due to photoelectric effects. In some cases the device can malfunction. This is especially true for devices in which the internal chip is exposed. When designing circuits, make sure that devices are protected against incident light from external sources. This problem is not limited to optical semiconductors and EPROMs. All types of device can be affected by light.

# 3.6.7 Dust and oil

Just like corrosive gases, dust and oil can cause chemical reactions in devices, which will adversely affect a device's electrical characteristics. To avoid this problem, do not use devices in dusty or oily environments. This is especially important for optical devices because dust and oil can affect a device's optical characteristics as well as its physical integrity and the electrical performance factors mentioned above.

# 3.6.8 Fire

Semiconductor devices are combustible; they can emit smoke and catch fire if heated sufficiently. When this happens, some devices may generate poisonous gases. Devices should therefore never be used in close proximity to an open flame or a heat-generating body, or near flammable or combustible materials.

# 3.7 Disposal of Devices and Packing Materials

When discarding unused devices and packing materials, follow all procedures specified by local regulations in order to protect the environment against contamination.

# 4. Precautions and Usage Considerations

This section describes matters specific to each product group which need to be taken into consideration when using devices. If the same item is described in Sections 3 and 4, the description in Section 4 takes precedence.

# 4.1 Microcontrollers

# 4.1.1 Design

(1) Using resonators which are not specifically recommended for use

Resonators recommended for use with Toshiba products in microcontroller oscillator applications are listed in Toshiba databooks along with information about oscillation conditions. If you use a resonator not included in this list, please consult Toshiba or the resonator manufacturer concerning the suitability of the device for your application.

# (2) Undefined functions

In some microcontrollers certain instruction code values do not constitute valid processor instructions. Also, it is possible that the values of bits in registers will become undefined. Take care in your applications not to use invalid instructions or to let register bit values become undefined.

## 1. The TMPR3916

## 1.1 Applications and References

The TMPR3916 is a family member of Toshiba's 32-bit system RISC family. As an application-specific standard product (ASSP) it is designed for a wide range of applications such as:

- Car Navigation Systems

- Driver Information Displays

- Personal Digital Assistants (PDAs)

- Musical Instruments

- Electronic Book Players

The TMPR3916 uses a TX39/H core as its CPU. The TX39/H CPU core is a RISC processor developed by Toshiba based on the R3000A architecture of MIPS Technologies Inc. .

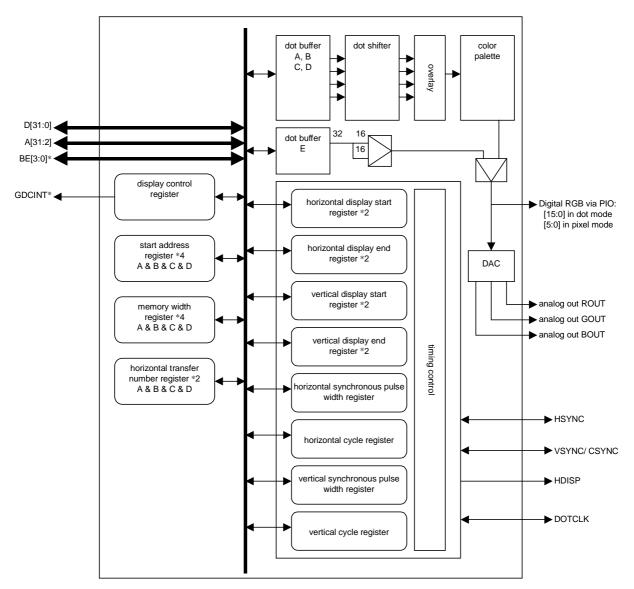

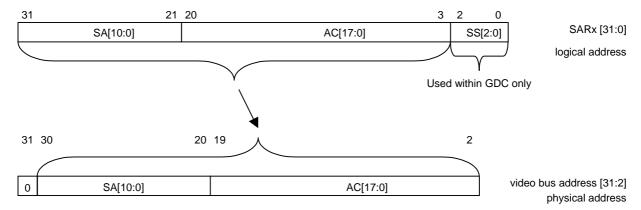

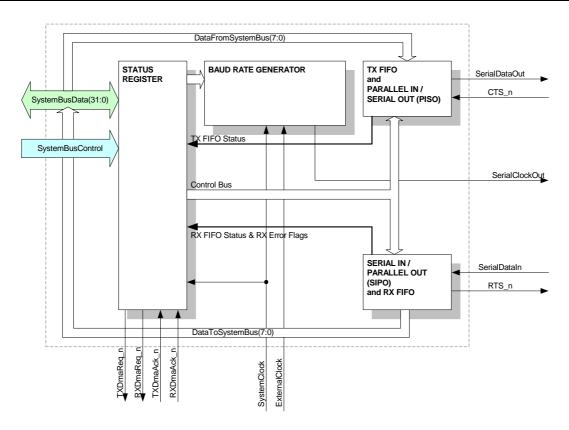

In addition to the processor core, this ASSP includes peripheral circuits such as a graphics display controller, a memory controller, a DMA controller, several serial communication interfaces, CAN-bus interfaces, interval timers and general purpose I/Os.

Please refer to the following document for information about the TX39 core architecture, including the instruction set:

32-Bit TX System RISC TX39 Family Architecture (Document Number 44137D)

### 1.2 Features

#### **Miscellaneous:**

- 60 MHz maximum operating frequency:

- 208 pin QFP package (QFP208-P-2828-0.50)

- 3.3 V power supply voltage

- ca. 1200mW Maximum Power Dissipation

- -40°C to 85°C operating ambient temperature

- Built-in clock generator

- 5V tolerant I/Os on UARTs, TXSEI and CAN-bus interface

- Unified memory architecture with a high performance dual bus structure (Video bus + CPU bus)

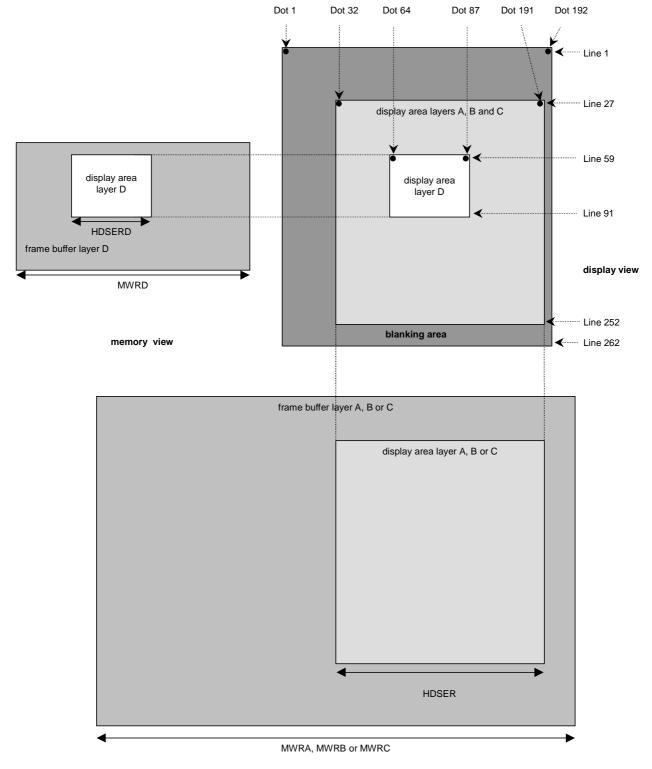

#### **Graphics Display Controller:**

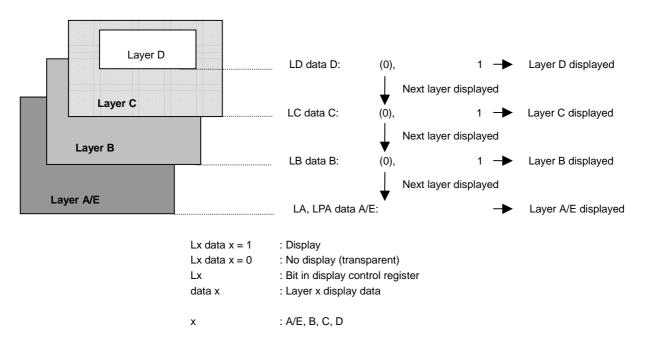

- Four-layer (A-D) overlay hardware processing with transparent color:

- Layer A, B can display 256 out of 64 K colors each

- Layer C, D can display 16 out of 64 K colors each

- Alternatively layer A may be configured in picture mode with 64K colors

- SDRAM and SRAM frame-buffer memory (SRAM recommended only for low resolutions)

- Burst access to frame-buffer memory

- 16 bytes built-in dot buffer

- Built-in color look-up tables (for plane A-D, 544 colors in total)

- Built-in three-channel 6-bit video DAC, alternatively connection to digital displays (digital RGB output)

- Dotclock, horizontal and vertical synchronisation signals can be generated internally or input from external device

### **Built-in TX39 Core:**

- Toshiba-developed TX39H core based on MIPS R3000A architecture

- 4 KB Instruction Cache, 1 KB Data Cache

- Built-in debug support unit for in-system debugging incl. real time PC-tracing

- Big-endian coding

#### **Peripheral Controllers:**

- Memory Controller (MEMC), 4 channels for SRAM, ROM, Flash

- SDRAM controller (SDRAMC), 2 channels

- DMA controller (DMAC), 2 channels

- Interrupt controller (INTC), 13 internal interrupts, 3 external interrupts, 1 non-maskable interrupt (NMI)

- Serial I/O: UART 4 channels, TXSEI 1 channel (SPI compatible, with FIFO's)

- CAN-bus controller (TXCAN), 2 channels, 16 mailboxes each

- 30 Pin General Purpose I/O's (PORT)

## 1.3 Differences Between TX3903AF and TMPR3916

In catchwords this section explains changed features of TMPR3916 in comparison to its predecessor TX3903AF. For detailed information please have a deeper look into this document.

- 60 MHz operating frequency

- added dual CAN device

- added TXSEI functionality

- added two channel SDRAM Controller

- separate Video- and CPU-bus to SDRAM in order to increase system performance

- removed EDO-DRAM channels from MEMC

- no more support of pipelined burst SRAM

- graphics display controller: increased number of colors from 16 to 256 in layer A and B

- raised number of 16 general purpose IOs to 30 and added capability of triggering interrupt

- extended timer functionality to PWM-support

- increased number of internal interrupts

- modified UART incl. register structure

- external bus-master functionality is not supported any more

# 1.4 Structure of TMPR3916 and a System Example

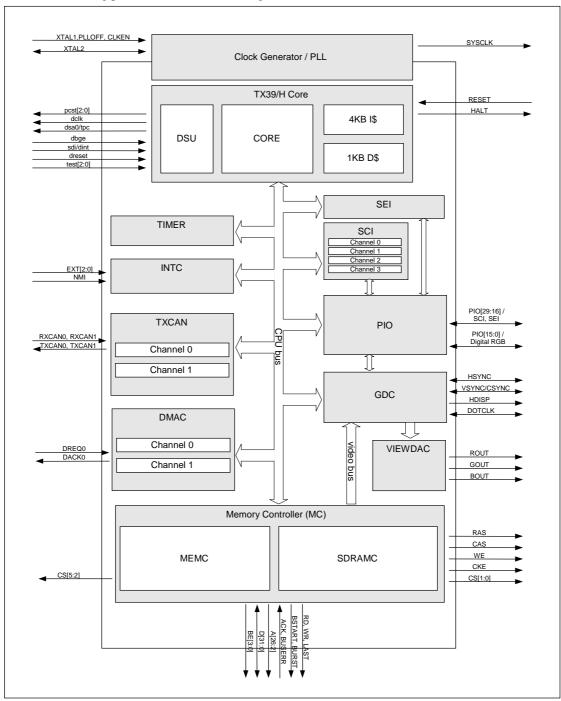

The following picture shows the block diagram of the TMPR3916:

Figure 1.4.1 Block Diagram TMPR3916

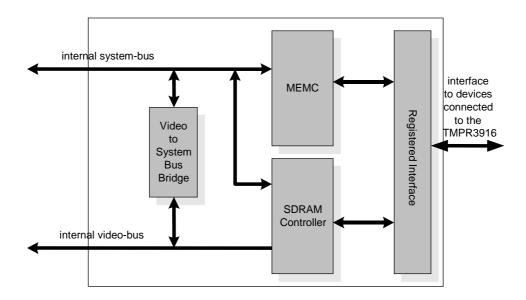

The following picture shows a system example with TMPR3916:

Figure 1.4.2 System Example Using TMPR3916

## 1.5 Address Map

The following table shows the memory map of TMPR3916.

| Memory Area of TX39-CPU                         | Physical Address | Memory Device         | Special Use in TMPR3916            |

|-------------------------------------------------|------------------|-----------------------|------------------------------------|

| Kernel<br>Uncached/ Cached<br>(kseg0, kseg1)    | 0x0000 0000      | SDRAM,<br>SRAM, ROM * | interrupt vector<br>at 0x0000 0080 |

|                                                 | 0x1C00 0000      | internal register     | devices of<br>TMPR3916             |

|                                                 | 0x1E00 0000      | SDRAM,<br>SRAM, ROM * |                                    |

|                                                 | 0x1FC0 0000      | Boot ROM              | start address after reset or NMI   |

| Inaccessible                                    | 0x2000 0000      |                       |                                    |

|                                                 | 0x4000 0000      |                       |                                    |

| User / Kernel<br>Cached<br>(kuseg)              |                  | SDRAM,<br>SRAM, ROM * |                                    |

| User / Kernel<br>Uncached<br>(kuseg - reserved) | 0xBF00 0000      |                       |                                    |

| Kernel<br>Cached<br>(kseg2)                     | 0xC000 0000      |                       |                                    |

| Kernel<br>Uncached<br>(kseg2 - reserved)        | 0xFF00 0000      |                       |                                    |

Figure 1.5.1 TMPR3916's Memory Map

\* For SDRAM, SRAM or ROM shown in the above table, the software can define the address range of the connected memory devices. For further information see chapter "Memory Controller".

The following table shows the address ranges of the internal devices:

| Address Range<br>(physical address) | Address Range<br>(virtual address) | Device                                 |

|-------------------------------------|------------------------------------|----------------------------------------|

| 0x1C00_0000<br>0x1C00_07FF          | 0xBC00_0000<br>0xBC00_07FF         | Asynchronous Serial Interface (UART)   |

| 0x1C00_8000<br>0x1C00_FFFF          | 0xBC00_8000<br>0xBC00_FFFF         | Synchronous Serial Interface (TXSEI)   |

| 0x1C01_0000<br>0x1C01_FFFF          | 0xBC01_0000<br>0xBC01_FFFF         | TIMER                                  |

| 0x1C02_0000<br>0x1C02_7FFF          | 0xBC02_0000<br>0xBC02_7FFF         | Memory Controller (MEMC)               |

| 0x1C02_8000<br>0x1C02_FFFF          | 0xBC02_8000<br>0xBC02_FFFF         | Memory Controller (SDRAMC)             |

| 0x1C03_0000<br>0x1C03_FFFF          | 0xBC03_0000<br>0xBC03_FFFF         | Parallel Interface (PORT)              |

| 0x1C04_0000<br>0x1C04_FFFF          | 0xBC04_0000<br>0xBC04_FFFF         | Interrupt Controller (INTC)            |

| 0x1C05_0000<br>0x1C05_FFFF          | 0xBC05_0000<br>0xBC05_FFFF         | Graphic Display Controller (GDC)       |

| 0x1C06_0000<br>0x1C06_FFFF          | 0xBC06_0000<br>0xBC06_FFFF         | Direct Memory Access Controller (DMAC) |

| 0x1C07_0000<br>0x1C07_7FFF          | 0xBC07_0000<br>0xBC07_7FFF         | CAN Module (TXCAN), channel 0          |

| 0x1C07_8000<br>0x1C07_FFFF          | 0xBC07_8000<br>0xBC07_FFFF         | CAN Module (TXCAN), channel 1          |

| 0x1C08_0000<br>0x1C08_FFFF          | 0xBC08_0000<br>0xBC08_FFFF         | Chip Configuration Register (CCR)      |

Figure 1.5.2 Physical and Virtual Addresses for Internal Devices

Note: Please note that addresses seen on GBUS are physical. Therefore virtual addresses can only be used in program code and will be translated before being output to the bus.

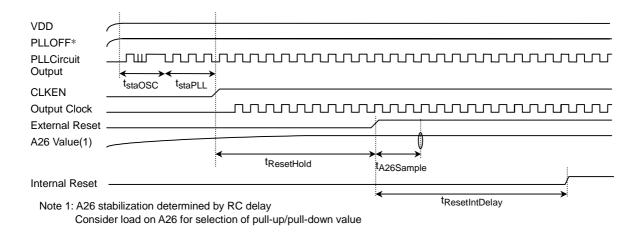

### 1.6 Clocks

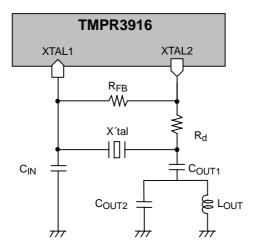

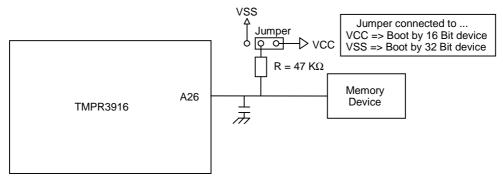

The TMPR3916 incorporates an eight-times PLL **clock generator**. Connect a crystal oscillator with 1/8 the frequency of the processor clock (processor clock = TX39 core input clock frequency). To reduce power dissipation and simplify system design, the TMPR3916 can control the TX39 core operating frequency and the bus operation reference frequency.

### **Clock Types:**

#### Master clock

Master clock regulates the TMPR3916 operations. The clock is eight times the frequency of the external crystal oscillator.

#### • Processor clock

This clock is used for TMPR3916 processor core operations. It has the same frequency as the master clock. (When using this clock, set reduced frequency indicator RF[1:0] of the core configuration register to 00. The processor clock will not operate if RF is set to any other value.)

### • System clock

The system clock regulates the TMPR3916 bus operations. It is generated from the processor clock and is of the same frequency and phase. This clock is output to pin SYSCLK.

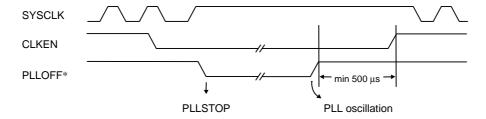

Setting the CLKEN pin to low **stops all clocks** of the device. The SYSCLK pin is set to high in this state and power-consumption is reduced to a minimum. The processor can resume its function immediately after the CLKEN pin has been asserted. For further information see chapter "Electrical Characteristics".

## 1.7 Resets

Setting RESET\* = Low resets the TMPR3916.

RESET\* should be held Low for at least 10 cycles of system clock (SYSCLK). Because the RESET\* signal is synchronized with the TMPR3916 internal clock, the RESET\* signal can be set asynchronously to system clock.

At a reset the TMPR3916 will do the following operations:

- Pipeline will be stalled, internal states reset.

- The valid and lock bits of the TX39 cache will be cleared.

During reset period the output signals have the following states:

A[31:2] = undefined D[31:0] = undefined BE[3:0]\* = "High" RD\*, WR\* = "High" BURST\* = "High" LAST\* = "High"

SYSCLK = continues outputting clock

1-9

### 1.8 Time-Out-Error Control Unit

This unit is a kind of watchdog unit for the internal CPU-bus.

When a master sends a GBSTART signal, the Time-Out Error Control Unit starts counting cycles. If no reaction has been detected on the bus, an internal acknowledging GACK is generated after 1024 cycles so that the bus is free for interaction again.

## 1.9 Operating Modes of TMPR3916

In Normal Mode, the TX39 core and peripheral circuits operate at maximum frequency.

**Halt Mode** halts the core operations and reduces power dissipation by stopping the clock in the TX39 core.

To switch to Halt mode, set the Halt bit of the Configuration Register in TX39 core.

In Halt mode, the TX39 core holds the status of the pipeline processing and stops the core operations. The write buffer does not stop. If data remains in the write buffer when Halt mode is selected, write operations continue until the write buffer becomes empty. Also SYSCLK does not stop.

The processor is released from HALT mode by using the NMI\* signal, RESET\* signal or by any kind of enabled interrupt. The corresponding exception handler is executed after the HALT mode has been released.

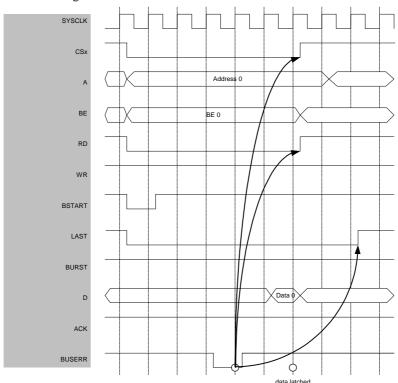

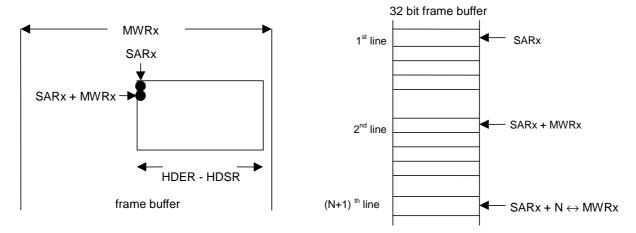

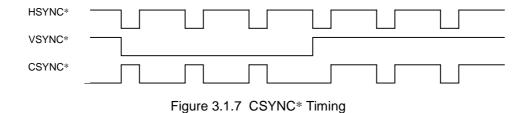

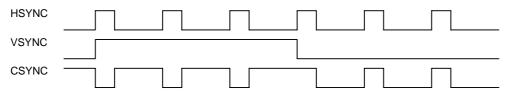

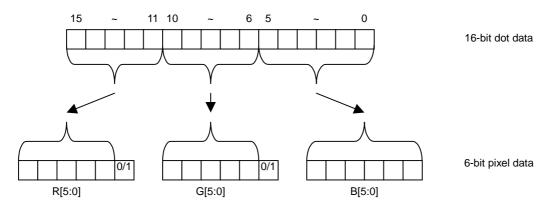

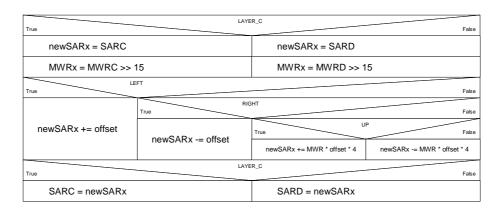

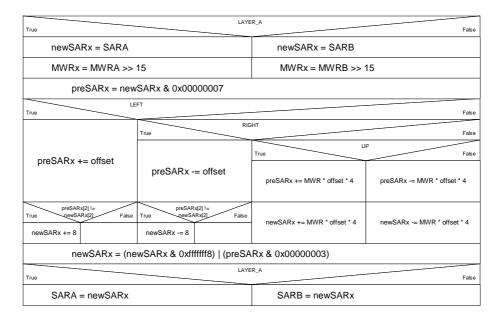

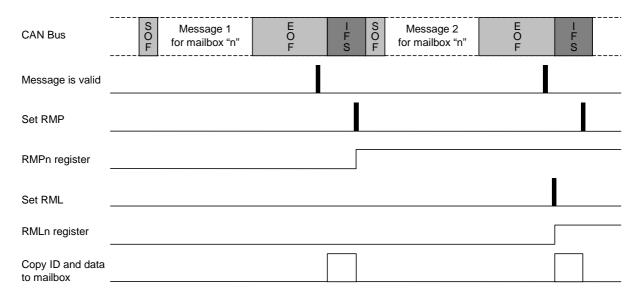

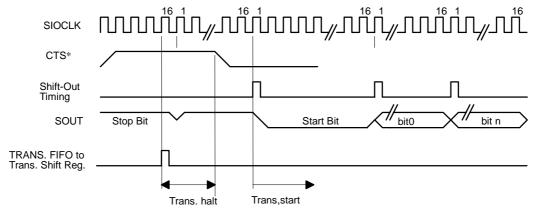

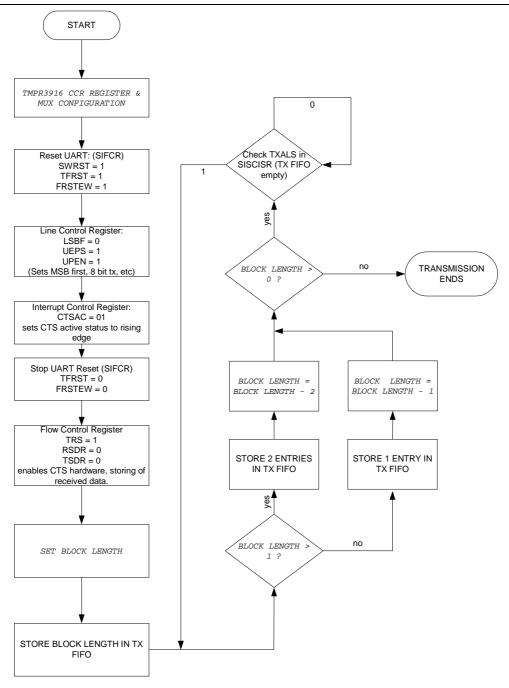

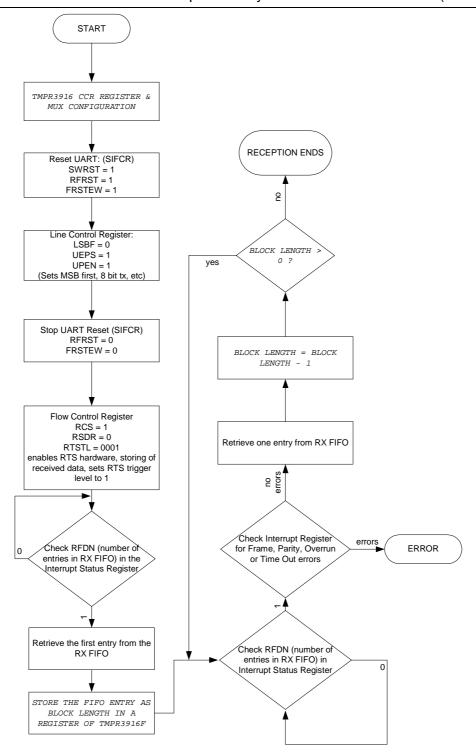

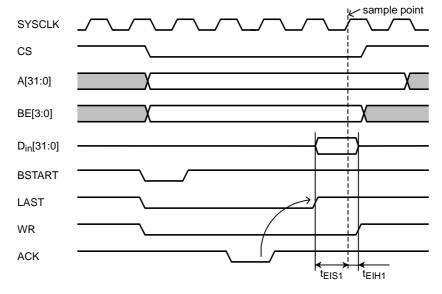

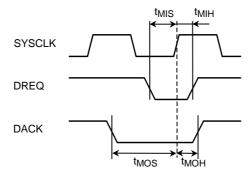

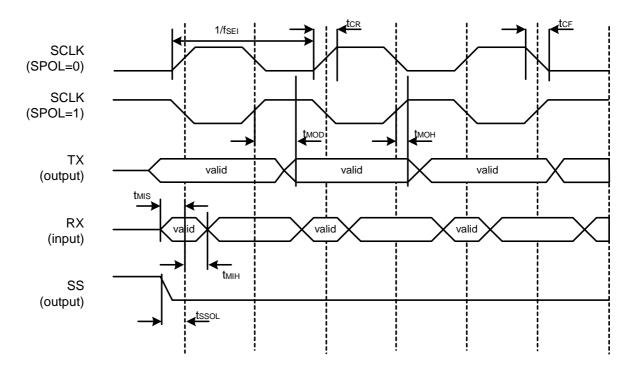

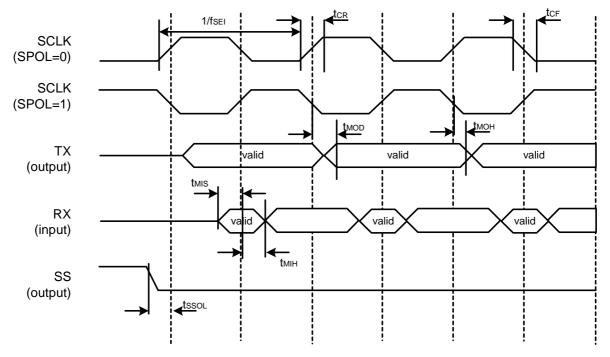

**Doze Mode** halts some TX39 core operations and reduces power dissipation. Unlike Halt mode, only some clocks in the processor core stop, allowing external bus release requests to be received. Also the peripheral blocks continue operating normally in Doze mode.