### **CMOS 8-Bit Microcomputer**

## TMP88C060F

The 88C060 is the high-speed and high-performance 8-bit microcomputer, including eight multiple timer / counters, a 10-bit A/D converter, serial interfaces (UART, I<sup>2</sup>C bus, and SIO). It can externally expand large program memory / data memory (up to 1 Mbytes linear address space).

| Part No.   | Part No. ROM |             | Package             |  |

|------------|--------------|-------------|---------------------|--|

| TMP88C060F | ROM less     | 512 × 8 bit | P-LQFP80-1212-0.50A |  |

### **Features**

- ◆8-bit microcomputer TLCS-870 / X Series.

- lacktriangle Minimum instruction execution time : 0.32  $\mu$ s (at 12.5 MHz)

- Instruction execution time can be changed to reduce power consumption.

min. 0.32  $\mu$ s, 0.64  $\mu$ s,1.28  $\mu$ s, 2.56  $\mu$ s, 5.12  $\mu$ s, 122  $\mu$ s at 12.5 MHz / 32.768 kHz

- External memory expansion

- Expanded up to 1M bytes (for both programs and data)

- Non-multiplexed bus (20 bits of address and 8 bits of data)

- Wait control

- Bus arbitration control

- ◆ 18 interrupt sources (External: 6, Internal: 12)

- Input / Output ports (42 pins)

- High current output: 8 pins (typ. 20 mA), LED direct drive

- ◆ Two 16-bit Timer / Counters

- TC1: Timer, Event counter, Programmable pulse generator output, Pulse width measurement, External trigger timer, and Window modes.

- TC2 : Timer, Event counter, and Window modes.

- ◆Four 8-bit Timer / Counters

- TC3: Timer, Event counter, and Capture for Remote control signal decoding (Pulse width / duty measurement) modes.

- TC4: Timer, Event counter, PWM outputs, and programmable divider output modes.

- TC5: Timer, PWM output, and programmable divider output modes

- TC6: Timer and Baud-rate generation for UART modes

TMP88C060F

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance/Handling Precautions.

- TOSHIBA is continually working to improve the quality and the reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to observe standards of safety, and to avoid situations in which a malfunction or failure of a TOSHIBA product could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent products specifications. Also, please keep in mind the precautions and conditions set forth in the TOSHIBA Semiconductor Reliability Handbook.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.

Purchase of TOSHIBA I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use these components in an I<sup>2</sup>C system, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips

3-60-1 1999-10-07

P-LOFP80-1212-0.50A

- ◆ Time Base Timer (Interrupt frequency: 1 kHz to 16384 kHz)

- **♦** Watchdog Timer

- ◆ Divider output (frequency: 1 kHz to 8 kHz)

- ◆ Two 8-bit Serial Interfaces

- 8-bit UART (Parity. framing. overrun error detection)

- 8-bit Serial Bus (I<sup>2</sup>C-Bus for multi-master system and SIO)

- ◆ 10-bit successive approximate type A/D converter

- 8 analog inputs

- $\bullet$  Conversion time : 59  $\mu$ s at 12.5 MHz, 44  $\mu$ s at 4.2 MHz

- ◆ Dual clock operation

- ◆ Five Power saving operating modes

- STOP mode: Oscillation stops. Battery / Capacitor back-up. Release by stop pin input.

- SLOW mode: Low power consumption operation using low-frequency clock (32.768 kHz)

- IDLE1 mode: CPU stops, and Peripherals operate using high-frequency clock. Release by interrupts. (CPU restarts)

- IDLE2 mode : CPU stops, and Peripherals operate using high and low frequency clock. Release by interrupts.

- SLEEP mode: CPU stops, and Peripherals operate using low-frequency clock. Release by interrupts.

- ◆ Wide operating voltage: 2.7 to 5.5 V at 4.2 MHz / 32.768 kHz, 4.5 to 5.5 V at 12.5 MHz / 32.768 kHz

- ◆ Emulation Pod: BM88C060F0A

3-60-2 1999-10-07

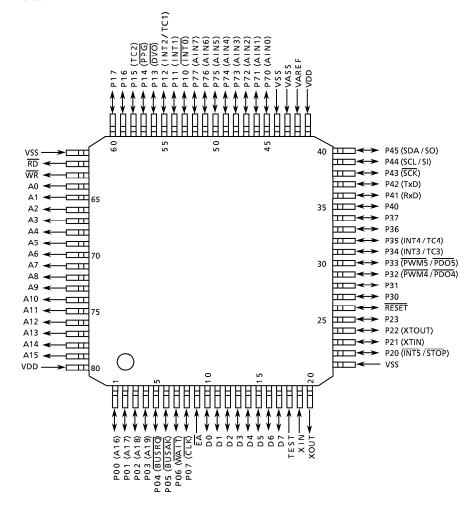

## Pin Assignments (Top View)

P-LQFP80-1212-0.50A

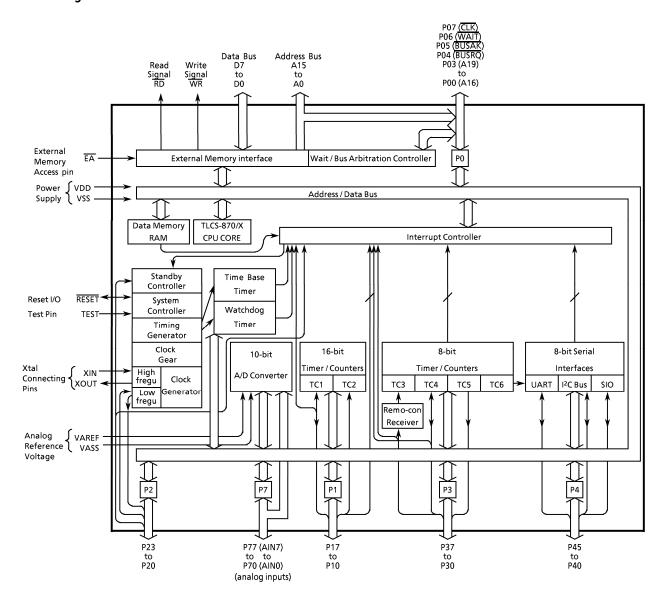

### **Block Diagram**

# **Pin Function**

| Pin name                    | Input / Output | Fi                                                                                                                                                                                                                                                           | unction                                                                      |  |  |  |  |

|-----------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--|--|--|--|

| P07 (CLK)                   | I/O (Output)   | 8-bit programmable input / output ports                                                                                                                                                                                                                      | Divided-by-4 clock output                                                    |  |  |  |  |

| P06 (WAIT)                  | I/O (Input)    | (tri-state).                                                                                                                                                                                                                                                 | Wait request input                                                           |  |  |  |  |

| P05 (BUSAK)                 | I/O (Output)   | Each bit of these ports can be individually configured as an input or an output.                                                                                                                                                                             | Bus acknowledge output                                                       |  |  |  |  |

| P04 (BUSRQ)                 | I/O (Input)    | When used as a wait request input, a bus                                                                                                                                                                                                                     | Bus request input                                                            |  |  |  |  |

| P03 (A19) to P00 (A16)      | I/O (Output)   | release request input, an external                                                                                                                                                                                                                           | Upper address bus (external memory connect)                                  |  |  |  |  |

| P17, P16                    | 1/0            | interrupt input, or a timer counter input,                                                                                                                                                                                                                   |                                                                              |  |  |  |  |

| P15 (TC2)                   | I/O (Input)    | corresponding bit must be configured as input. When used as a divided-by-4 clock                                                                                                                                                                             | Timer / Counter 2 input                                                      |  |  |  |  |

| P14 ( <del>PPG</del> )      | 1/O (Output)   | output, a bus acknowledge output, PPG                                                                                                                                                                                                                        | Programmable pulse generator output                                          |  |  |  |  |

| P13 (DVO)                   | I/O (Output)   | output, or a divider output, the output                                                                                                                                                                                                                      | Divider output                                                               |  |  |  |  |

| P12 (INT2/TC1)              |                | latch must be set to "1" and<br>corresponding bit must be configured as<br>output. After reset, P03 to P00 are                                                                                                                                               | External interrupt input 2 or Timer / Counter 1 input                        |  |  |  |  |

| P11 (INT1)                  | I/O (Input)    | address buses. When used as a port, these                                                                                                                                                                                                                    | External interrupt input 1                                                   |  |  |  |  |

| P10 ( <del>INT0</del> )     | ]              | ports must be set to the ports by EXPCR.                                                                                                                                                                                                                     | External interrupt input 0                                                   |  |  |  |  |

| P23                         | I/O            | 4-bit input / output port with latch.                                                                                                                                                                                                                        |                                                                              |  |  |  |  |

| P22 (XTOUT)                 | I/O (Output)   | When used as an input port, a resonator                                                                                                                                                                                                                      | Xtal connecting pins (32.768 kHz). For                                       |  |  |  |  |

| P21 (XTIN)                  |                | connecting pin, an external interrupt                                                                                                                                                                                                                        | inputting external clock, XTIN is used and XTOUT is opened.                  |  |  |  |  |

| P20 (INT5 / STOP)           | I/O (Input)    | input, or a STOP mode release input, the output latch must be set to "1".                                                                                                                                                                                    | External interrupt input 5 or STOP mode release signal input                 |  |  |  |  |

| P37, P36                    | I/O            |                                                                                                                                                                                                                                                              |                                                                              |  |  |  |  |

| P35 (INT4 / TC4)            |                | 8-bit input / output port (large current                                                                                                                                                                                                                     | External interrupt input 4 or Timer / Counter 4 input                        |  |  |  |  |

| P34 (INT3 / TC3)            | I/O (Input)    | output) with latch.<br>When used as an input port, PWM output,                                                                                                                                                                                               | External interrupt input 3 or Timer / Counter 3 input                        |  |  |  |  |

| P33 (PWM5 / PDO5)           | I/O (Output)   | an external interrupt input, or a timer counter input, the output latch must be                                                                                                                                                                              | 8-bit PWM output 5 or, 8-bit programmable divider output 5                   |  |  |  |  |

| P32 (PWM4 / PDO4)           |                | set to "1".                                                                                                                                                                                                                                                  | 8-bit PWM output 4 or, 8-bit programmable divider output 4                   |  |  |  |  |

| P31, P30                    | 1/0            |                                                                                                                                                                                                                                                              | aivider output 4                                                             |  |  |  |  |

| P45 (SDA / SO)              |                |                                                                                                                                                                                                                                                              | SIO data output<br>I <sup>2</sup> C bus data I/O                             |  |  |  |  |

| P44 (SCL / SI) P43 (SCK)    | 1/0 (1/0)      | 6-bit input / output port with latch.<br>When used as an input port or a serial<br>interface pin, the output latch must be set                                                                                                                               | SIO data input<br>I <sup>2</sup> C bus clock I/O<br>SIO clock input / output |  |  |  |  |

| P42 (TxD)                   |                | to "1".                                                                                                                                                                                                                                                      | UART data output                                                             |  |  |  |  |

| P41 (RxD)<br>P40            |                |                                                                                                                                                                                                                                                              | UART data input                                                              |  |  |  |  |

| P77 (AIN7)<br>to P70 (AIN0) | I/O (Input)    | 8-bit programmable input / output port (tri-state). Each bit of these ports can be individually configured as an input or an output. When used as an analog input, these ports must be set to the analog input mode by P7CR and select the channel in ADCCR. | A/D converter analog input (ch 7 to ch 0)                                    |  |  |  |  |

| Pin name    | Input / Output | Function                                                                                |

|-------------|----------------|-----------------------------------------------------------------------------------------|

| A15 to A0   | Output         | Lower address bus (external memory connect)                                             |

| D7 to D0    | I/O            | Data bus (external memory connect)                                                      |

| RD          | 0              | Read strobe to an extrnal memory                                                        |

| WR          | Output         | Write strobe to an extrnal memory                                                       |

| EA          | Input          | External memory access input. Be tied to low.                                           |

| VIN VOUT    | Input,         | Xtal connecting pins for high-frequency clock.                                          |

| XIN, XOUT   | Output         | For inputting external clock, XIN is used and XOUT is opened.                           |

| DECET       | 1/0            | Reset signal input or watchdog timer output / address-trap-reset output / system-clock- |

| RESET       | 1/0            | reset output.                                                                           |

| TEST        | Input          | Test pin for out-going test. Be tied to low.                                            |

| VDD, VSS    | Power          | + 5 V, 0 V (GND)                                                                        |

| VAREF, VASS | Supply         | Analog reference voltage for A/D converter (High, Low)                                  |

## **Operational Description**

### 1. CPU Core Functions

The CPU core consists of a CPU, a system clock controller, and an interrupt controller. This section provides a description of the CPU core, the program memory, the data memory, the external memory interface, and the reset circuit.

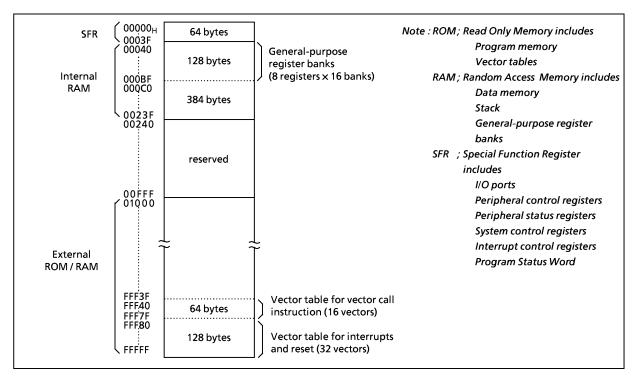

### 1.1 Memory Address Map

The TLCS-870 / X Series is capable of addressing 1M bytes of memory. Figure 1-1 shows the memory address map of the 88C060. The memory of the 88C060 is organized with 3 address spaces such as ROM, RAM SFR (Special Function Register). It uses a memory mapped I/O system, and all I/O registers are mapped in the SFR address space. There are 16 banks of the general-purpose register. The register banks are also assigned to the first 128 bytes of the RAM address space.

Figure 1-1. Memory address map

## 1.2 Program Memory (ROM)

The 88C060 can address up to 1M bytes of external program memory space except the first 4K bytes space (00000<sub>H</sub> to 00FFF<sub>H</sub>).

The 88C060 does not have internal ROM. An external program memory must be connected.

## 1.3 Data Memory (ROM)

The 88C060 can address up to 1M bytes of data memory space. Data memory consists of internal data memory (on-chip RAM) and external data memory (RAM and / or ROM). The 88C060 has 512 bytes of static RAM. The first 128 bytes ( $00040_H$  to  $000BF_H$ ) of the internal RAM are also used as general-purpose register banks.

The data memory contents become unstable when the power supply is turned on; therefore, the data memory should be initialized by an initialization routine.

## **Electrical Characteristics**

Absolute Maximum Rating (V<sub>ss</sub> = 0 V)

| Parameter                        | Symbol            | Conditions                     | Rating                         | Unit |

|----------------------------------|-------------------|--------------------------------|--------------------------------|------|

| Supply Voltage                   | $V_{DD}$          |                                | - 0.3 to 6.5                   |      |

| Input Voltage                    | $V_{IN}$          |                                | - 0.3 to V <sub>DD</sub> + 0.3 | ] ,  |

| Output Voltage                   | V <sub>OUT1</sub> | P21, P22, RESET, Tri-st        | $-0.3$ to $V_{DD} + 0.3$       | ]    |

| Output Voltage                   | V <sub>OUT2</sub> | P20, P23, Sink Open Drain Port | - 0.3 to 5.5                   |      |

|                                  | I <sub>OUT1</sub> | P0, P1, P2, P4, P7 port        | 3.2                            |      |

| Output Current (Per 1 pin)       | I <sub>OUT2</sub> | A19-0, D7-0, RD, WR            | 12                             |      |

|                                  | I <sub>OUT3</sub> | P3                             | 30                             | mA   |

| Contract Command (Tatal)         | $\Sigma I_{OUT1}$ |                                | 80                             |      |

| Output Current (Total)           | $\Sigma I_{OUT2}$ |                                | 120                            |      |

| Power Dissipation (Topr = 70 °C) | PD                |                                | 330                            | mW   |

| Soldering Temperature (time)     | Tsld              |                                | 260 (10 s)                     |      |

| Storage Temperature              | Tstg              |                                | - 55 to 125                    | °C   |

| Operating Temperature            | Topr              |                                | - 40 to 85                     |      |

Note: The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant.

Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

**Recommended Operating Conditions**

$(V_{SS} = 0 \text{ V, Topr} = -40 \text{ to } 85 ^{\circ}\text{C})$

| Parameter          | Symbol           | Pins                            |                          | Conditions                                              | Min                   | Max                    | Unit           |

|--------------------|------------------|---------------------------------|--------------------------|---------------------------------------------------------|-----------------------|------------------------|----------------|

| Supply Voltage     |                  |                                 | fc =                     | NORMAL1, 2 mode                                         | 4.5                   |                        |                |

| lanker, rainings   |                  |                                 | 12.5 MHz                 | IDLE1, 2 mode                                           | 1                     |                        |                |

|                    |                  |                                 | fc =                     | NORMAL1, 2 mode                                         | 1 , -                 | 5.5                    | l <sub>v</sub> |

|                    | $V_{DD}$         |                                 | 4.2 MHz                  | IDLE1, 2 mode                                           | 2.7                   | 3.5                    | V              |

|                    |                  |                                 | fs =                     | SLOW mode                                               |                       |                        |                |

|                    |                  |                                 | 32.768 kHz               |                                                         |                       |                        |                |

|                    |                  |                                 |                          | STOP mode                                               | 2.0                   |                        |                |

| Input High Voltage | V <sub>IH1</sub> | Except hysteresis and TTL input | V <sub>DD</sub> ≧ 4.5 V  |                                                         | $V_{DD} \times 0.70$  |                        |                |

|                    | V <sub>IH2</sub> | Hysteresis input                | 1                        |                                                         | $V_{DD} \times 0.75$  | 1                      |                |

|                    | V <sub>IH3</sub> | Except TLL input                | V <sub>DD</sub> <4.5 V   |                                                         | $V_{DD} \times 0.90$  | V <sub>DD</sub>        | V              |

|                    | .,               | TTL input                       | $V_{DD} = 5 V$           |                                                         | 2.2                   |                        |                |

|                    | $V_{IH4}$        | (Data bus)                      | $V_{DD} = 3 V$           |                                                         | V <sub>DD</sub> - 0.2 |                        |                |

| Input Low Voltage  | V <sub>IL1</sub> | Except hysteresis and TTL input | V <sub>DD</sub> ≧ 4.5 V  |                                                         |                       | V <sub>DD</sub> × 0.30 |                |

|                    | $V_{IL2}$        | Hysteresis input                | 1                        |                                                         |                       | $V_{DD} \times 0.25$   | 1              |

|                    | V <sub>IL3</sub> | Except TTL input                | V <sub>DD</sub> <4.5 V   |                                                         | 1 0                   | $V_{DD} \times 0.10$   | V              |

|                    | .,               | TTL input                       | $V_{DD} = 5 V$           |                                                         | 1                     | 0.8                    | 1              |

|                    | $V_{IL4}$        | (Data bus)                      | V <sub>DD</sub> = 3 V    |                                                         | 1                     | 0.2                    | 1              |

| Clock Frequency    | Took Eroguanay I |                                 | 00                       | V <sub>DD</sub> = 4.5 V to 5.5 V<br>(Normal 1, 2 modes) |                       | 12.5                   | MHz            |

|                    |                  |                                 | $V_{DD} = 2.7 \text{ V}$ | to 5.5 V                                                | 1.0                   | 4.2                    | 1              |

|                    | fs               | XTIN, XTOUT                     |                          |                                                         | 30.0                  | 34.0                   | kHz            |

Note1: The recommended operating conditions for a device are operating conditions under which it can be guaranteed that the device will operate as specified. If the device is used under operating conditions other than the recommended operating conditions (supply voltage, operating temperature range, specified AC/DC values etc.), malfunction may occur. Thus, when designing products which include this device, ensure that the recommended operating conditions for the device are always adhered to.

Note2: fc (Min.) are calculated at using clock Gear as follow: (Minimum value of fc) = (pre-scaled ration)  $\times$  1 [MHz]

DC Characteristics

$(V_{SS} = 0 \text{ V, Topr} = -40 \text{ to } 85 ^{\circ}\text{C})$

| Parameter                          | Symbol                                                  | Pins                                    | Conditions                                                                                                       | Min    | Тур.      | Max      | Unit |

|------------------------------------|---------------------------------------------------------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------|--------|-----------|----------|------|

| Hysteresis Voltage                 | V <sub>HS</sub>                                         | Hysteresis input                        |                                                                                                                  | _      | 0.9       | -        | V    |

| Input Current                      | I <sub>IN1</sub>                                        | TEST, EA                                | V <sub>DD</sub> = 5.5 V<br>V <sub>IN</sub> = 5.5 V / 0 V                                                         | -      | -         | ± 2      | μΑ   |

| Input Resistance                   | I <sub>IN3</sub>                                        | RESET, STOP  RESET  TEST                |                                                                                                                  | 100    | 220<br>70 | 450      | kΩ   |

| Oscillator Feed-back<br>Resistance | R <sub>IN3</sub><br>R <sub>fx</sub><br>R <sub>fxt</sub> | XIN-XTOUT XTIN-XTOUT                    |                                                                                                                  | -<br>- | 1.2       | _<br>    | ΜΩ   |

| Output Leakage<br>Current          | I <sub>LO1</sub>                                        | Sink Open Drain Port Tir-st port        | $V_{DD} = 5.5 \text{ V}, V_{OUT} = 5.5 \text{ V}$<br>$V_{DD} = 5.5 \text{ V}, V_{OUT} = 5.5 \text{ V}/0\text{V}$ | -      | -         | 2<br>± 2 | μΑ   |

| Output High Voltage                | V <sub>OH2</sub>                                        | Tir-st port A19-0, D7-0, RD, WR         | $V_{DD} = 4.5 \text{ V}, V_{OH} = -0.7 \text{ mA}$ $V_{DD} = 4.5 \text{ V}, I_{OH} = -400 \mu\text{s}$           |        | -         | -        | V    |

| Output Low Voltage                 | V <sub>OL3</sub>                                        | A19-0, D7-0, RD, WR                     | $V_{DD} = 4.5 \text{ V}, I_{OL} = 1.6 \text{ mA}$                                                                | -      | _         | 0.45     | V    |

| Output Low Voltage                 | I <sub>OL1</sub>                                        | Except XOUT, P3,<br>A19-0, D7-0, RD, WR | V <sub>DD</sub> = 4.5 V, V <sub>OL</sub> = 0.4 V                                                                 | _      | 1.6       | -        | mA   |

|                                    | I <sub>OL3</sub>                                        | P3                                      | $V_{DD} = 4.5 \text{ V}, V_{OL} = 1.0 \text{ V}$                                                                 | _      | 20        | _        |      |

| Supply Current in NORMAL1, 2 mode  |                                                         |                                         | $V_{DD} = 5.5 \text{ V}$<br>$V_{IN} = 5.3 \text{ V} / 0.2 \text{ V}$                                             | -      | 15        | 20       |      |

| Supply Current in IDLE1, 2 mode    |                                                         |                                         | fc = 12.5 MHz<br>fs = 32.768 kHz                                                                                 | -      | 6         | 8        | mA   |

| Supply Current in SLOW mode        | I <sub>DD</sub>                                         |                                         | V <sub>DD</sub> = 3.0 V<br>V <sub>IN</sub> = 2.8 V / 0.2 V                                                       | -      | 30        | 60       | _    |

| Supply Current in SLEEP mode       |                                                         |                                         | fs = 32.768 kHz                                                                                                  | _      | 15        | 30       | μA   |

| Supply Current in STOP mode        |                                                         |                                         | V <sub>DD</sub> = 5.5 V<br>V <sub>IN</sub> = 5.3 V / 0.2 V                                                       | _      | 0.5       | 10       | μΑ   |

Note 1: Typical values show those at  $T_{opr} = 25 \, ^{\circ}\text{C}$ ,  $V_{DD} = 5 \, V$ . Note 2: Input current  $I_{IN1}$ ,  $I_{IN3}$ : The current through pull-up or pull-down resistor is not included. Note 3: IDD: Except for IREF.

A.C. Characteristics

(1)  $(V_{SS} = 0 \text{ V}, V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Topr} = -40 \text{ to } 85 ^{\circ}\text{C})$

## (1) - ① Clock

| Parameter                    | Symbol           | Conditions                               | Min   | Тур. | Max   | Unit    |

|------------------------------|------------------|------------------------------------------|-------|------|-------|---------|

|                              |                  | In NORMAL1, 2 mode                       | 0.32  |      | 4     |         |

| Mashina Cysla Tima           | +0.4             | In IDLE1, 2 mode                         | 0.32  | 1    |       |         |

| Machine Cycle Time           | tcy              | In SLOW mode                             | 117.6 |      | 122.2 | $\mu$ S |

|                              |                  | In SLEEP mode                            | 117.0 | _    | 133.3 |         |

| High Level Clock Pulse Width | t <sub>WCH</sub> | For external clock operation (XIN input) | 33.75 |      |       | ns      |

| Low Level Clock Pulse Width  | t <sub>WCL</sub> | fc = 12.5 MHz                            | 33.75 | _    | _     | 115     |

| High Level Clock Pulse Width | t <sub>WSH</sub> | For external clock operation (XIN input) | 14.7  |      |       |         |

| Low Level Clock Pulse Width  | t <sub>WSL</sub> | fs = 32.768 kHz                          | 14.7  | -    | _     | μ\$     |

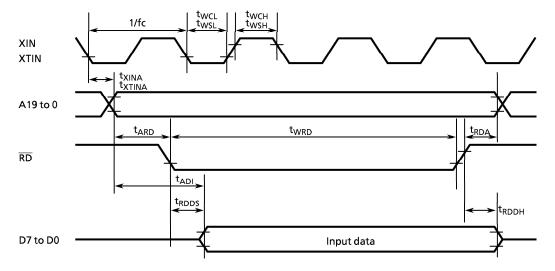

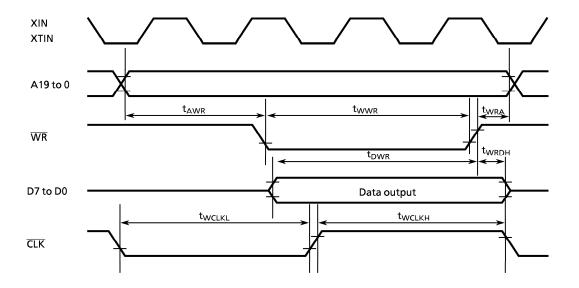

# (1) - ② External Memory Interface

| Donomaton                       | C. mala al         | Vari      | able       | 12.5 | MHz | 11-4:4 |

|---------------------------------|--------------------|-----------|------------|------|-----|--------|

| Parameter                       | Symbol             | Min       | Max        | Min  | Max | Unit   |

| Address Setup to RD             | t <sub>ARD</sub>   | 0.5t - 30 | -          | 10   | -   | ns     |

| Address Setup to WR             | t <sub>AWR</sub>   | 1.5t – 30 | -          | 90   | -   | ns     |

| Address Hold Time After RD / WR | t <sub>RDA</sub>   | 0.5t – 35 |            | 5    | _   | ns     |

| Address Hold Time After KD/WK   | $t_{WRA}$          | 0.51 - 35 | _          | າ    | _   | 115    |

| Address to Valid Data In        | t <sub>ADI</sub>   | =         | 3.5t – 95  | ı    | 185 | ns     |

| RD to Valid Data In             | t <sub>RDDS</sub>  | -         | 3.0t – 100 | -    | 140 | ns     |

| RD Low Pulse Width              | t <sub>WRD</sub>   | 0.3t - 40 | -          | 200  | -   | ns     |

| Input Data Hold After RD        | t <sub>RDDH</sub>  | 0         | -          | 0    | -   | ns     |

| WR Low Pulse Width              | t <sub>WWR</sub>   | 2.0t – 40 | -          | 120  | _   | ns     |

| Data Setup to WR                | t <sub>DWR</sub>   | 2.0t – 40 | -          | 120  | -   | ns     |

| Data Hold After WR              | t <sub>WRDH</sub>  | 0.5t - 35 | -          | 5    | -   | ns     |

| XIN to Address Delay            | t <sub>XINA</sub>  | -         | 140        | - 1  | 140 | ns     |

| XTIN to Address Delay           | t <sub>XTINA</sub> | -         | 340        | _    | 340 | ns     |

Note : t = tcy / 4 (t = 80 ns @ fc = 12.5 MHz)

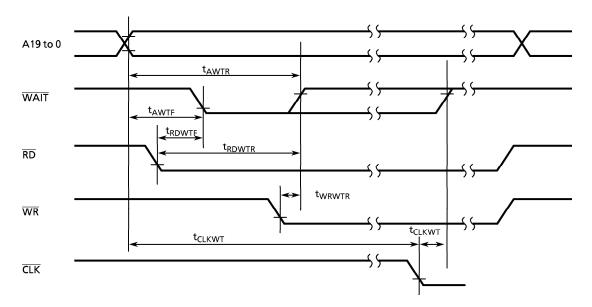

#### (1) - ③ Wait

| Downwater             | C. mala al         | Vari      | able       | 12.5 | MHz  | Unit |

|-----------------------|--------------------|-----------|------------|------|------|------|

| Parameter             | Symbol             | Min       | Max        | Min  | Max  | Unit |

| Address Setup to WAIT | t <sub>AWTF</sub>  | -         | 1.5t – 100 | -    | 20   | ns   |

| Address Setup to WAIT | t <sub>AWTR</sub>  | 1.5t + 20 | 1          | 140  | _    | ns   |

| RD Setup to WAIT      | t <sub>RDWTF</sub> | -         | 1.0t – 100 | -    | - 20 | ns   |

| RD Setup to WAIT      | t <sub>RDWTR</sub> | 1.0t + 20 | -          | 100  | _    | ns   |

| WR Setup to WAIT      | t <sub>WRWTR</sub> | 20        | 1          | 20   | _    | ns   |

| Address Valid to CLK  | t <sub>ACLK</sub>  | -         | 4.0t + 35  | -    | 355  | ns   |

| CLK Pulse Width       | t <sub>WCLKL</sub> | 2.0t – 50 |            | 110  |      |      |

| CLK Pulse Width       | twclkh             | 2.01 – 50 | _          | 110  | _    | ns   |

| CLK Set up to WAIT    | t <sub>CLKWT</sub> | _         | 1.5t – 70  | -    | 50   | ns   |

Note: t = tcy / 4 (t = 80 ns @ fc = 12.5 MHz)

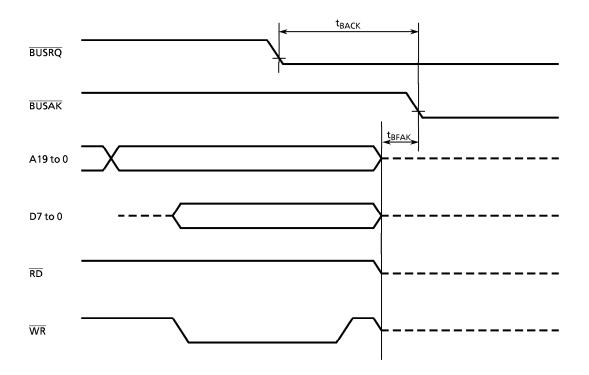

#### (1) - 4 **Bus Arbitration**

| Dovometer                  | C. mala al        | Vari      | able      | 12.5 | MHz | l l m l d |

|----------------------------|-------------------|-----------|-----------|------|-----|-----------|

| Parameter                  | Symbol            | Min       | Max       | Min  | Max | Unit      |

| Bus Floating to BUSAK      | t <sub>BFAK</sub> | 0.5t - 30 | -         | 10   | -   | ns        |

| Period from BUSRQ to BUSAK | t <sub>BACK</sub> | _         | 5.5t + 30 | _    | 470 | ns        |

Note 1: t = tcy / 4 (t = 80 ns @ fc = 12.5 MHz)

Note 2: When the BUSRQ is set to "0" during "Wait Cycle", the Bus will be released after the completion of "Wait Cycle".

Note 3: When the BUSRQ is set to "0" just before interrupt request, the Bus will be released after the completion of current instruction execution and interrupt sequence.

### A.C. Meaurement Condition

High 2.2 V / Low 0.8 V, CL = 100 pF**Output Level** Input level High 2.4 V / Low 0.4 V (D7 to D0)

High 0.7 V<sub>DD</sub> / Low 0.3 V<sub>DD</sub> (WAIT)

High 0.8  $V_{DD}$  / Low 0.2  $V_{DD}$  (Except D7 to D0 and  $\overline{WAIT})$

A.C. Charactiristics

(2)  $(V_{SS} = 0 \text{ V}, V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, \text{ Topr} = -40 \text{ to } 85 ^{\circ}\text{C})$

## (2) - ① Clock

| Parameter                    | Symbol           | Conditions                                | Min   | Тур. | Max   | Unit |

|------------------------------|------------------|-------------------------------------------|-------|------|-------|------|

|                              |                  | In NORMAL1, 2 mode                        | 0.95  |      | 4     |      |

| Machine Cycle Time           | +0.4             | In IDLE1, 2 mode                          | 0.95  | ı    | 4     |      |

| Machine Cycle Time           | tcy              | In SLOW mode                              | 117.6 |      |       | μS   |

|                              |                  | In SLEEP mode                             | 117.6 | _    | 133.3 |      |

| High Level Clock Pulse Width | t <sub>WCH</sub> | For external clock operation (XIN input)  | 110   |      |       |      |

| Low Level Clock Pulse Width  | t <sub>WCL</sub> | fc = 4.2 MHz                              | 110   | 1    | _     | ns   |

| High Level Clock Pulse Width | t <sub>WSH</sub> | For external clock operation (XTIN input) | 14.7  |      |       |      |

| Low Level Clock Pulse Width  | t <sub>WSL</sub> | fs = 32.768 kHz                           | 14.7  | -    | _     | μS   |

## (2) - ② External Memory Interface

| Dansaratas                      | Console al        | Vari       | able       | 4.21 | ИHz | 1114 |

|---------------------------------|-------------------|------------|------------|------|-----|------|

| Parameter                       | Symbol            | Min        | Max        | Min  | Max | Unit |

| Address Setup to RD             | t <sub>ARD</sub>  | 0.5t – 110 | -          | 9    | -   | ns   |

| Address Setup to WD             | t <sub>AWR</sub>  | 1.5t – 120 | ı          | 237  | =   | ns   |

| Address Hold Time After RD / WR | t <sub>RDA</sub>  | 0.5t – 110 |            | 9    |     | ns.  |

| Address Hold Tille After RD7 WK | t <sub>WRA</sub>  | 0.51 - 110 | _          | 9    | _   | ns   |

| Address to Valid Data In        | t <sub>ADI</sub>  | _          | 3.5t – 270 | -    | 563 | ns   |

| RD to Valid Data In             | t <sub>RDDS</sub> | _          | 3.0t – 205 | -    | 509 | ns   |

| RD Low Pulse Width              | t <sub>WRD</sub>  | 3.0t – 40  | -          | 674  | _   | ns   |

| Input Data Hold After RD        | t <sub>RDDH</sub> | 0          | -          | 0    | -   | ns   |

| WR Low Pulse Width              | t <sub>WWR</sub>  | 2.0t - 85  | -          | 391  | -   | ns   |

| Data Setup to WR                | t <sub>DWR</sub>  | 2.0t - 50  | -          | 426  | -   | ns   |

| Data Hold After WR              | t <sub>WRDH</sub> | 0.5t – 110 | _          | 9    | _   | ns   |

Note: t = tcy / 4 (t = 238 ns @ fc = 4.2 MHz)

#### (2) - ③ Wait

| Parameter             | Symbol             | Variable   |            | 4.2 MHz |      | Unit |

|-----------------------|--------------------|------------|------------|---------|------|------|

|                       |                    | Min        | Max        | Min     | Max  | Unit |

| Address Setup to WAIT | t <sub>AWTF</sub>  | -          | 1.5t – 257 | -       | 100  | ns   |

| Address Setup to WAIT | t <sub>AWTR</sub>  | 1.5t + 125 | -          | 482     | -    | ns   |

| RD Setup to WAIT      | t <sub>RDWTF</sub> | -          | 1.0t – 165 | -       | 73   | ns   |

| RD Setup to WAIT      | t <sub>RDWTR</sub> | 1.0t + 125 | -          | 363     | _    | ns   |

| WR Setup to WAIT      | t <sub>WRWTR</sub> | 50         | 1          | 50      | -    | ns   |

| Address Valid to CLK  | t <sub>ACLK</sub>  | -          | 4.0t + 70  | -       | 1022 | ns   |

| CLK Pulse Width       | t <sub>WCLKL</sub> | 2.0t – 118 | -          | 358     | -    | ns   |

|                       | twclkh             |            |            |         |      |      |

| CLK Set up to WAIT    | t <sub>CLKWT</sub> | _          | 1.5t – 170 | -       | 187  | ns   |

Note: t = tcy / 4 (t = 238 ns @ fc = 4.2 MHz)

#### (2) - ④ **Bus Arbitration**

| Parameter                  | Symbol            | Variable   |            | 4.2 MHz |      | Umit |

|----------------------------|-------------------|------------|------------|---------|------|------|

|                            |                   | Min        | Max        | Min     | Max  | Unit |

| Bus Floating to BUSAK      | t <sub>BFAK</sub> | 0.5t - 109 | -          | 10      | _    | ns   |

| Period from BUSRQ to BUSAK | t <sub>BACK</sub> | -          | 5.5t + 109 | -       | 1200 | ns   |

Note 1: t = tcy / 4 (t = 238 ns @ fc = 4.2 MHz) Note 2: When the  $\overline{BUSRQ}$  is set to "0" during "Wait Cycle", the Bus will be released after the completion of "Wait Cycle". Note 3: When the  $\overline{BUSRQ}$  is set to "0" just before interrupt request, the Bus will be released after the completion of current instruction execution and interrupt sequence.

### A.C. Meaurement Condition

Output Level : High  $0.7 V_{DD} / Low 0.3 V_{DD}$ , CL = 100 pF

Input level : High  $0.9 V_{DD} / Low 0.1 V_{DD}$

A / D Conversion Characteristics

$(Topr = -40 \text{ to } 85 ^{\circ}C)$

| Parameter                         | Symbol               | Conditions                                                                                                                                                                                    | Min                   | Тур. | Max               | Unit |

|-----------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------|-------------------|------|

| Analog Reference Voltage          | V <sub>AREF</sub>    |                                                                                                                                                                                               | V <sub>DD</sub> – 1.5 | -    | V <sub>DD</sub>   | V    |

|                                   | V <sub>ASS</sub>     |                                                                                                                                                                                               | V <sub>SS</sub>       | -    | V <sub>SS</sub>   | ]    |

| Analog Reference Voltage<br>Range | $\triangle V_{AREF}$ |                                                                                                                                                                                               | 2.5                   | -    | -                 | V    |

| Analog Input Voltage              | $V_{AIN}$            |                                                                                                                                                                                               | V <sub>ASS</sub>      | -    | V <sub>AREF</sub> | V    |

| Analog Supply Current             | I <sub>REF</sub>     | V <sub>DD</sub> = AVDD = VAREF = 5.5 V<br>VSS = AVSS = VASS = 0.0 V                                                                                                                           | -                     | 0.5  | 1.0               | mA   |

| Non-Linearity Error               |                      | $V_{DD} = 5.0 \text{ to } 5.5 \text{ V}, V_{SS} = 0.0 \text{ V}$ AVDD = VAREF = 5.000 V AVSS = VASS = 0.000 V low Speed Conversion (58.9 $\mu$ s, @ 12.5 MHz)                                 | _                     | -    | ± 2               | LSB  |

| Zero Point Error                  |                      |                                                                                                                                                                                               | _                     | -    | ± 2               |      |

| Full Scale Error                  |                      |                                                                                                                                                                                               | _                     | -    | ± 2               |      |

| Total Error                       |                      |                                                                                                                                                                                               | _                     | -    | ± 4               |      |

| Non-Linearity Error               |                      | $V_{DD} = 2.7 \text{ to } 5.5 \text{ V}, V_{SS} = 0.0 \text{ V}$ $AVDD = VAREF = 2.700 \text{ V}$ $AVSS = VASS = 0.000 \text{ V}$ $Hing speed conversion (43.7 \ \mu s, \ @ 4.2 \text{ MHz})$ | -                     | -    | ± 2               | LSB  |

| Zero Point Error                  |                      |                                                                                                                                                                                               | _                     | _    | ± 2               |      |

| Full Scale Error                  |                      |                                                                                                                                                                                               | -                     | _    | ± 2               |      |

| Total Error                       |                      |                                                                                                                                                                                               | _                     | -    | ± 4               |      |

Note:  $\triangle V_{AREF} = V_{AREF} - V_{ASS}$

# Timing Chart

# (1) Read Cycle

# (2) Write Cycle

# (3) Wait Timing

## (4) Bus Arbitation