#### CMOS 8-Bit Microcontroller

# TMP86CH21U/F

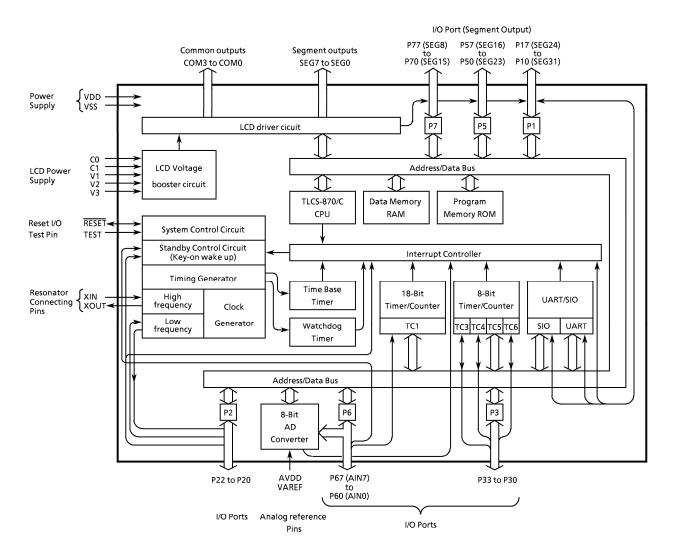

The TMP86CH21 is the high-speed and high-performance 8-bit microcomputer, including ROM, RAM, LCD driver, multi-function timer/counter, serial interface (UART/SIO), a 8-bit AD converter and two clock generators on chip.

| Γ | Product No.  | ROM                  | RAM          | Package                                  | OTP MCU        |

|---|--------------|----------------------|--------------|------------------------------------------|----------------|

| ſ | TMP86CH21U/F | 16 K $\times$ 8 bits | 512 × 8 bits | P-LQFP64-1010-0.50<br>P-QFP64-1414-0.80A | TMP86PM29AU/AF |

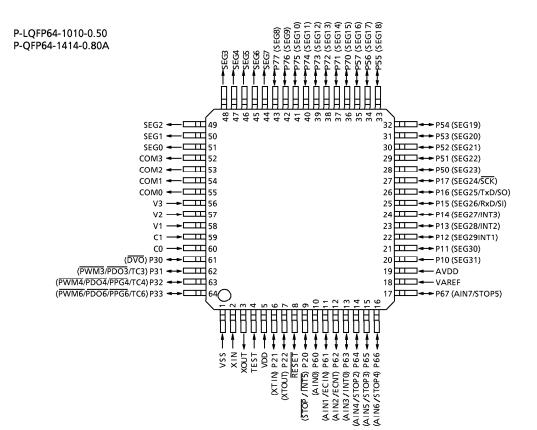

P-LQFP64-1010-0.50

P-QFP64-1414-0.80A

TMP86CH21U

#### **Features**

- ◆ 8-bit single chip microcomputer TLCS-870/C series

- Instruction execution time: 0.25 μs (at 16 MHz) 122 µs (at 32.768 kHz)

- 132 types and 731 basic instructions

- 19 interrupt sources (External: 5, Internal: 14)

- Input/Output ports (39 pins) (Out of which 24 pins are also used as SEG pins)

- 18-bit timer counter: 1 ch

- Timer, Event counter, Pulse width measurement, **Frequencymeasurement modes**

- ◆ 8-bit timer counter: 4 ch

- Timer, Event counter, PWM output, Programmable divider output, PPG output modes

- Time Base Timer

- Divider output function

000707EBP1

TMP86CH21F

ullet For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled

Quality and Reliability Assurance / Handling Precautions. TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc... The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, nervonal equipment office equipment measuring equipment inductrial robotics applications (computer, Toshi personal equipment, office equipment, measuring equipment, industrial robotics, domestic applications (computer, TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of software the universe of the product of the product of the universe of the univers safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others. The information contained herein is subject to change without notice.

# TOSHIBA

- ♦ Watchdog timer

- Interrupt source/reset output (programmable)

- Serial interface

- 8-bit UART/SIO: 1ch

- 8-bit successive approximation type AD converter

- Analog input: 8 ch

- Four key-on wake-up: 4 ch

- ◆ LCD driver/controller

- Built-in voltage booster for LCD driver

- With displaymemory

- LCD direct drive capability (Max  $32 \text{ seg} \times 4 \text{ com}$ )

- 1/4, 1/3, 1/2duties or static drive are programmably selectable

- Dual clock operation

- Single/Dual-clock mode

- Nine power saving operating modes

- STOP mode: Oscillation stops. Battery/Capacitor back-up. Port output hold/High-impedance.

- SLOW 1 mode: Low power consumption operation using low-frequency clock. (High-frequency Stop)

- SLOW 2 mode: Low power consumption operation using low-frequency clock. (High-frequency Oscillation)

- IDLE 0 mode: CPU stops, and peripherals operate using high-frequency clock of Time-Base-Timer. Release by falling edge of TBTCR<TBTCK> setting.

- IDLE 1 mode: CPU stops, and peripherals operate using high-frequency clock. Release by interruputs.

- IDLE 2 mode: CPU stops, and peripherals operate using high and low frequency clock. Release by interruputs.

- SLEEP 0 mode: CPU stops, and peripherals operate using low-frequency clock of Time-Base-Timer. Release by falling edge of TBTCR<TBTCK> setting.

- SLEEP 1 mode: CPU stops, and peripherals operate using low-frequency clock. Release by interrupts.

- SLEEP 2 mode: CPU stops, and peripherals operate using high and low frequency clock. Release by interrupts.

- Wide operating voltage: 1.8 to 5.5 V at 4.2 MHz/32.768 kHz,

2.7 to 5.5 V at 8 MHz/32.768 kHz, 4.5 to 5.5 V at 16 MHz/32.768 kHz

#### Pin Assignments (Top View)

# TOSHIBA

### **Block Diagram**

## **Pin Function**

| Pin Name                       | Input/Output               |                                                                                                                   | Function                                             |                               |  |  |

|--------------------------------|----------------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------|--|--|

| P17 (SEG24, SCK)               | I/O (I/O)                  |                                                                                                                   | Serial clock input/output                            |                               |  |  |

| P16 (SEG25, TxD, SO)           | l/O (Output)               | 8-bit input/output port with latch.                                                                               | UART data output<br>Serial data output               |                               |  |  |

| P15 (SEG26, RxD, SI)           | I/O (I/O)                  | When used as input port, an external interrupt input, serial interface input/output and UART data input/          | UART data input<br>Serial data input                 | LCD segment                   |  |  |

| P14 (SEG27, INT3)              | I/O (I/O)                  | output, the P1LCR must be set to "0"                                                                              | External interrupt 3 input                           | outputs.                      |  |  |

| P13 (SEG28, INT2)              | I/O (I/O)                  | after setting output latch to "1".<br>When used as a LCD segment output,                                          | External interrupt 2 input                           |                               |  |  |

| P12 (SEG29, INT1)              | I/O (I/O)                  | the P1LCR must be set to "1".                                                                                     | External interrupt 1 input                           |                               |  |  |

| P11 (SEG30)                    | l/O (Output)               |                                                                                                                   |                                                      |                               |  |  |

| P10 (SEG31)                    | l/O (Output)               |                                                                                                                   |                                                      |                               |  |  |

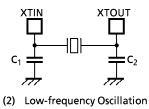

| P22 (XTOUT)                    | I/O (Output)               |                                                                                                                   | Resonator connecting pins (32.7                      |                               |  |  |

| P21 (XTIN)                     | l/O (Input)                | 3-bit input/output port with latch.<br>When used as an input port, the                                            | For inputting external clock, XT<br>XTOUT is opened. |                               |  |  |

| P20 (INT5, STOP)               | l/O (Input)                | output latch must be set to "1".                                                                                  | External interrupt input 5 or ST<br>signal input     | OP mode release               |  |  |

| P33 (PWM6, PDO6,<br>PPG6, TC6) | I/O(I/O)                   | 4-bit programmable input/output<br>port (Nch high current output).                                                | Timer counter 6 input/output                         |                               |  |  |

| P32 (PWM4, PDO4,<br>PPG4, TC4) | I/O(I/O)                   | When used as a timer/counter output<br>or divider output, the output latch<br>must be set to "1". When used as an | Timer counter 4 input/output                         |                               |  |  |

| P31 (PWM3, PDO3,<br>TC3)       | I/O(I/O)                   | input port or timer/counter input, the<br>P3OUTCR must be set to "0" after                                        | Timer counter 3 input/output                         |                               |  |  |

| P30 (DVO)                      | l/O(Output)                | P3DR is set to "1".                                                                                               | Divider output                                       |                               |  |  |

| P57 (SEG16) to<br>P50 (SEG23)  | I/O (Output)               | 8-bit input/output port with latch.<br>When used as a LCD segment output,<br>the P5LCR must be set to "1".        | LCD segment outputs                                  |                               |  |  |

| P67 (AIN7, STOP5)              | I/O (Input)                | 8-bit programmable input/output<br>port (tri-state). Each bit of this port                                        | STOP 5 input                                         |                               |  |  |

| P66 (AIN6, STOP4)              | l/O (Input)                | can be individually configured as an                                                                              | STOP 4 input                                         |                               |  |  |

| P65 (AIN5, STOP3)              | l/O (Input)                | input or an output under software control. When used as an analog                                                 | STOP 3 input                                         |                               |  |  |

| P64 (AIN4, STOP2)              | l/O (Input)                | input, the P6CR must be set to "0"                                                                                | STOP 2 input                                         | AD converter<br>analog inputs |  |  |

| P63 (AIN3, INTO)               | l/O (Input)                | after setting output latch to "0".                                                                                | External interrupt 0 input                           | analog mpats                  |  |  |

| P62 (AIN2, ECNT)               | l/O (Input)                | When used as an input port, a key on wake up input, an external interrupt                                         | Timer/counter 1 input                                |                               |  |  |

| P61 (AIN1, ECIN)               | l/O (Input)                | input and timer/counter input, the                                                                                |                                                      |                               |  |  |

| P60 (AIN0)                     | l/O (Input)                | P6CR must be set to "0" after setting output latch to "1".                                                        |                                                      |                               |  |  |

| P77 (SEG8) to<br>P70 (SEG15)   | I/O (Output)               | 8-bit input/output port with latch.<br>When used as a LCD segment output,<br>the P7LCR must be set to "1".        | LCD segment outputs                                  |                               |  |  |

| SEG7 to SEG0<br>COM3 to COM0   | Output                     | LCD segment outputs<br>LCD common outputs                                                                         |                                                      |                               |  |  |

| V 3 to V 1                     |                            | •                                                                                                                 |                                                      |                               |  |  |

| C1 to C0                       | LCD voltage<br>booster pin | LCD voltage booster pin. Capacitors a pin and GND.                                                                | re required between CU and C1                        | pin and v1/v2/v3              |  |  |

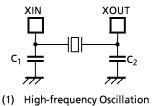

| XIN, XOUT                      | Input Output               | Resonator connecting pins for high-fre<br>used and XOUT is opened.                                                | quency clock. For inputting exte                     | ernal clock, XIN is           |  |  |

| RESET                          | I/O                        | Reset signal input or watchdog timer ou                                                                           | utput/address-trap-reset output                      |                               |  |  |

| TEST                           | Input                      | Test pin for out-going test. Be fixed to l                                                                        | ow.                                                  |                               |  |  |

| VDD, VSS                       |                            | + 5 V, 0 (GND)                                                                                                    |                                                      |                               |  |  |

| VAREF                          | Power Supply               | Analog reference voltage inputs (High)                                                                            |                                                      |                               |  |  |

| AVDD                           |                            | AD circuit power supply                                                                                           |                                                      |                               |  |  |

## **Operational Description**

#### 1. CPU Core Functions

The CPU core consists of a CPU, a system clock controller, and an interrupt controller.

This section provides a description of the CPU core, the program memory, the data memory, the external memory interface, and the reset circuit.

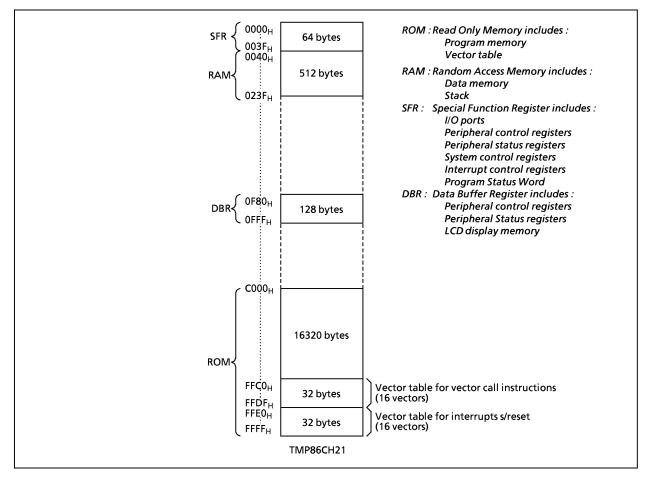

#### 1.1 Memory Address Map

The TMP86CH21 memory consist of 4 blocks: ROM, RAM, DBR (Data Buffer Register) and SFR (Special Function Register). They are all mapped in 64-Kbyte address space. Figure 1-1 shows the TMP86CH21 memory address map. The general-purpose registers are not assigned to the RAM address space.

Figure 1-1. Memory Address Map

#### 1.2 Program Memory (ROM)

The TMP86CH21 has a 16 K×8 bits (address  $C000_H$  to FFFF<sub>H</sub>) of program memory (mask programmed ROM). However, placing program memory on the internal RAM is deregulated if a certain procedure is executed (See 2.4.5 Address trap).

Unit

V

mΑ

mW

- 1.8

3.2

30

60

80

350

260 (10 s)

#### **Electrical Characteristics**

Output Current (Per 1 pin)

**Output Current (Total)**

Power Dissipation [T<sub>opr</sub> = 85°C]

Soldering Temperature (time)

| Absolute Maximum Rat | tings (V <sub>SS</sub> | = 0 V) |                                |

|----------------------|------------------------|--------|--------------------------------|

| Parameter            | Symbol                 | Pins   | Rating                         |

| Supply Voltage       | V <sub>DD</sub>        |        | – 0.3 to 6.5                   |

| Input Voltage        | V <sub>IN</sub>        |        | – 0.3 to V <sub>DD</sub> + 0.3 |

| Output Voltage       | V <sub>OUT1</sub>      |        | – 0.3 to V <sub>DD</sub> + 0.3 |

P3, P6 Port

P3 Port

P3 Port

P1, P2, P5, P6, P7 Port

P1, P2, P5, P6, P7 Port

I<sub>OUT1</sub>

I<sub>OUT2</sub>

I<sub>OUT3</sub>

$\Sigma I_{OUT1}$

ΣΙ<sub>Ουτ2</sub>

PD

Tsld

| Storage Temperature                                            | Tstg                             |                                                                                                                                                                                                  | – 55 to 125                                        |              |

|----------------------------------------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------|

| Operating Temperature                                          | Topr                             |                                                                                                                                                                                                  | – 40 to 85                                         |              |

| Any one of the ratings must no<br>or its performance may be de | ot be exceeded<br>graded, causir | lues which must not be exceeded during ope<br>d. If any absolute maximum rating is exceeded<br>ng it to catch fire or explode resulting in inju<br>, ensure that no absolute maximum rating valu | d, a device may break o<br>ry to the user. Thus, w | down<br>when |

| Parameter                                                          | Symbol           | Pins                                     | c                                           | ondition                          | Min                                                                                                                                                                                                                                                                                                                                                   | Max                  | Unit |     |

|--------------------------------------------------------------------|------------------|------------------------------------------|---------------------------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|------|-----|

|                                                                    |                  |                                          |                                             | NORMAL1, 2 mode                   | 4 5                                                                                                                                                                                                                                                                                                                                                   |                      |      |     |

|                                                                    |                  |                                          | fc = 16 MHz                                 | IDLE0, 1, 2 mode                  | 2 mode $4.5$ $5.5$ 2 mode $2.7$ $5.5$ 2 mode $2.7$ $5.5$ 2 mode $5.5$ $5.5$ mode $1.8$ $5.5$ mode $V_{DD} \times 0.70$ $V_{DD}$ $V_{DD} \times 0.70$ $V_{DD}$ $V_{DD}$ $V_{DD} \times 0.70$ $V_{DD} \times 0.30$ $V_{DD} \times 0.30$ $V_{DD} \times 0.90$ $V_{DD} \times 0.25$ $V_{DD} \times 0.10$ $V_{DD} \times 0.10$ $4.2$ $4.2$ $1.0$ $8.0$ $M$ |                      |      |     |

| Parameter<br>Supply Voltage<br>Input high Level<br>Input low Level |                  |                                          |                                             | NORMAL1, 2 mode                   | 2.7                                                                                                                                                                                                                                                                                                                                                   |                      |      |     |

|                                                                    | V <sub>DD</sub>  |                                          | fc = 8 MHz                                  | IDLE0, 1, 2 mode                  | 2.7                                                                                                                                                                                                                                                                                                                                                   |                      |      |     |

|                                                                    |                  |                                          |                                             | NORMAL1, 2 mode                   |                                                                                                                                                                                                                                                                                                                                                       | 5.5                  |      |     |

|                                                                    |                  |                                          | fc = 4.2 MHz                                | IDLE0, 1, 2 mode                  | 1.8                                                                                                                                                                                                                                                                                                                                                   |                      | v    |     |

|                                                                    |                  |                                          | fs =                                        | SLOW1, 2 mode                     |                                                                                                                                                                                                                                                                                                                                                       |                      |      |     |

|                                                                    |                  |                                          | 32.768 kHz                                  | SLEEP0, 1, 2 mode                 |                                                                                                                                                                                                                                                                                                                                                       |                      |      |     |

|                                                                    |                  |                                          |                                             | STOP mode                         |                                                                                                                                                                                                                                                                                                                                                       |                      |      |     |

| Input high Level                                                   | V <sub>IH1</sub> | Except Hysteresis input                  | N N                                         | > 4 5 1/                          | $V_{DD} \times 0.70$                                                                                                                                                                                                                                                                                                                                  |                      | ]    |     |

|                                                                    | V <sub>IH2</sub> | Hysteresis input                         | $V_{DD} \ge 4.5 V$ $V_{DD} < 4.5 V$         |                                   | $V_{DD} \times 0.75$                                                                                                                                                                                                                                                                                                                                  | V <sub>DD</sub>      |      |     |

|                                                                    | V <sub>IH3</sub> |                                          |                                             |                                   | $V_{DD} \times 0.90$                                                                                                                                                                                                                                                                                                                                  |                      |      |     |

|                                                                    | V <sub>IL1</sub> | Except Hysteresis input                  | N N                                         | <sub>D</sub> ≧ 4.5 V              |                                                                                                                                                                                                                                                                                                                                                       | $V_{DD} \times 0.30$ |      |     |

| Supply Voltage                                                     | V <sub>IL2</sub> | Hysteresis input                         | V D                                         | bD ≌ 4.5 V                        | 0                                                                                                                                                                                                                                                                                                                                                     | $V_{DD} \times 0.25$ |      |     |

|                                                                    | V <sub>IL3</sub> |                                          | V <sub>D</sub>                              | <sub>D</sub> < 4.5 V              |                                                                                                                                                                                                                                                                                                                                                       | $V_{DD} \times 0.10$ |      |     |

|                                                                    |                  |                                          | V <sub>DD</sub> =                           | = 1.8 to 5.5 V                    |                                                                                                                                                                                                                                                                                                                                                       | 4.2                  |      |     |

|                                                                    | fc               | XIN, XOUT V <sub>DD</sub> = 2.7 to 5.5 V | fc XIN, XOUT V <sub>DD</sub> = 2.7 to 5.5 V | UT V <sub>DD</sub> = 2.7 to 5.5 V | (IN, XOUT V <sub>DD</sub> = 2.7 to 5.5 V                                                                                                                                                                                                                                                                                                              | 1.0                  | 8.0  | MHz |

| clock nequency                                                     |                  |                                          | V <sub>DD</sub> =                           | = 4.5 to 5.5 V                    |                                                                                                                                                                                                                                                                                                                                                       | 16.0                 |      |     |

| lock Frequency                                                     | fs               | XTIN, XTOUT                              |                                             |                                   | 30.0                                                                                                                                                                                                                                                                                                                                                  | 34.0                 | kHz  |     |

Note: The recommended operating conditions for a device are operating conditions under which it can be guaranteed that the device will operate as specified. If the device is used under operating conditions other than the recommended operating conditions (supply voltage, operating temperature range, specified AC/DC values etc.), malfunction may occur. Thus, when designing products which include this device, ensure that the recommended operating conditions for the device are always adhered to.

| DC Charact                          | eristics         | (V <sub>SS</sub> = 0 V, Topr                                  | = - 40 to 85°C)                                          |     |      |     |      |

|-------------------------------------|------------------|---------------------------------------------------------------|----------------------------------------------------------|-----|------|-----|------|

| Parameter                           | Symbol           | Pins                                                          | Condition                                                | Min | Тур. | Max | Unit |

| Hysteresis Voltage                  | V <sub>HS</sub>  | Hysteresis input                                              |                                                          | -   | 0.9  | -   | V    |

|                                     | I <sub>IN1</sub> | TEST                                                          |                                                          |     |      |     |      |

| Input Current                       | I <sub>IN2</sub> | Sink Open Drain, Tri-state                                    | $V_{DD} = 5.5 V, V_{IN} = 5.5 V/0 V$                     | -   | -    | ± 2 | μA   |

|                                     | I <sub>IN3</sub> | RESET, STOP                                                   |                                                          |     |      |     |      |

| Input Resistance                    | R <sub>IN1</sub> | TEST Pull-Down                                                |                                                          | -   | 70   | -   | kΩ   |

| input Resistance                    | R <sub>IN2</sub> | RESET Pull-Up                                                 |                                                          | 100 | 220  | 450 | K32  |

| Output Leakage<br>Current           | I <sub>LO</sub>  | Sink Open Drain, Tri-state                                    | $V_{DD}$ = 5.5 V, $V_{OUT}$ = 5.5 V/0 V                  | -   | -    | ± 2 | μΑ   |

| Output High Voltage                 | V <sub>OH2</sub> | C-MOS, Tri-st Port                                            | $V_{DD} = 4.5 \text{ V}, I_{OH} = -0.7 \text{ mA}$       | 4.1 | -    | -   | v    |

| Output Low Voltage                  | V <sub>OL</sub>  | Except XOUT and P3 Port                                       | $V_{DD} = 4.5 V, I_{OL} = 1.6 mA$                        | -   | -    | 0.4 | V    |

| Output Low Current                  | I <sub>OL</sub>  | High Current Port (P3 Port)                                   | $V_{DD}$ = 4.5 V, $V_{OL}$ = 1.0 V                       | -   | 20   | -   |      |

| Supply Current in NORMAL 1, 2 mode  |                  |                                                               | V <sub>DD</sub> = 5.5 V<br>V <sub>IN</sub> = 5.3/0.2 V   | -   | 7.5  | 9   | mA   |

| Supply Current in IDLE 0, 1, 2 mode |                  |                                                               | fc = 16 MHz<br>fs = 32.768 kHz                           | -   | 5.5  | 6.5 |      |

| Supply Current in<br>SLOW 1 mode    |                  |                                                               |                                                          | -   | 18   | 42  |      |

| Supply Current in                   |                  | $V_{DD} = 3.0 V$<br>$V_{IN} = 2.8 V/0.2 V$<br>fs = 32.768 kHz | -                                                        | 16  | 25   | Αμ  |      |

|                                     |                  | LCD driver is not enable.                                     | _                                                        | 12  | 20   |     |      |

| Supply Current in<br>STOP mode      |                  |                                                               | V <sub>DD</sub> = 5.5 V<br>V <sub>IN</sub> = 5.3 V/0.2 V | -   | 0.5  | 10  |      |

| DC Characteristics (\ | ′ss = 0 | V, To |

|-----------------------|---------|-------|

|-----------------------|---------|-------|

Note 1: Typical values show those at Topr =  $25^{\circ}$ C,  $V_{DD} = 5 V$

Note 2: Input current (I<sub>IN1</sub>, I<sub>IN2</sub>); The current through pull-up or pull-down resistor is not included.

Note 3: IDD does not include IREF current.

Note 4: The supply currents of SLOW 2 and SLEEP 2 modes are equivalent to IDLE 0, 1, 2.

#### **AD Conversion Characteristics**

$(V_{SS} = 0.0 \text{ V}, 4.5 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{Topr} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                                           | Symbol            | Condition                                              | Min                    | Тур.            | Max               | Unit |

|-----------------------------------------------------|-------------------|--------------------------------------------------------|------------------------|-----------------|-------------------|------|

| Analog Reference Voltage                            | V <sub>AREF</sub> |                                                        | A <sub>VDD</sub> – 1.5 | -               | A <sub>VDD</sub>  |      |

| Power Supply Voltage of<br>Analog Control Circuit   | A <sub>VDD</sub>  |                                                        |                        | V <sub>DD</sub> |                   |      |

| Analog Reference Voltage Range (Note 4)             | $\Delta v_{aref}$ |                                                        | 3.0                    | -               | -                 |      |

| Analog Input Voltage                                | V <sub>AIN</sub>  |                                                        | V <sub>SS</sub>        | -               | V <sub>AREF</sub> |      |

| Power Supply Current of<br>Analog Reference Voltage | I <sub>REF</sub>  | $V_{DD} = A_{VDD} = V_{AREF} = 5.5 V$ $V_{SS} = 0.0 V$ | -                      | 0.6             | 1.0               | mA   |

| Non linearity Error                                 |                   |                                                        | -                      | -               | ± 1               |      |

| Zero Point Error                                    |                   | $V_{DD} = A_{VDD} = 5.0 V,$                            | -                      | -               | ± 1               | LSB  |

| Full Scale Error                                    |                   | $V_{SS} = 0.0 V$<br>$V_{ARFF} = 5.0 V$                 | -                      | -               | ±1                |      |

| Total Error                                         |                   |                                                        | -                      | -               | ± 2               | 1    |

#### $(V_{SS} = 0.0 \text{ V}, 2.7 \text{ V} \le V_{DD} < 4.5 \text{ V}, \text{Topr} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                                           | Symbol            | Condition                                              | Min                    | Тур.            | Max              | Unit  |

|-----------------------------------------------------|-------------------|--------------------------------------------------------|------------------------|-----------------|------------------|-------|

| Analog Reference Voltage                            | V <sub>AREF</sub> |                                                        | A <sub>VDD</sub> – 1.5 | -               | A <sub>VDD</sub> |       |

| Power Supply Voltage of<br>Analog Control Circuit   | A <sub>VDD</sub>  |                                                        |                        | V <sub>DD</sub> |                  |       |

| Analog Reference Voltage Range (Note 4)             | $\Delta v_{AREF}$ |                                                        | 2.5                    | -               | -                | ]     |

| Analog Input Voltage                                | V <sub>AIN</sub>  |                                                        | V <sub>SS</sub>        | -               | VAREF            |       |

| Power Supply Current of<br>Analog Reference Voltage | I <sub>REF</sub>  | $V_{DD} = A_{VDD} = V_{AREF} = 4.5 V$ $V_{SS} = 0.0 V$ | -                      | 0.5             | 0.8              | mA    |

| Non linearity Error                                 |                   |                                                        | -                      | -               | ± 1              |       |

| Zero Point Error                                    |                   | $V_{DD} = A_{VDD} = 2.7 V,$                            | -                      | -               | ± 1              | LSB   |

| Full Scale Error                                    |                   | $V_{SS} = 0.0 V$<br>$V_{ARFF} = 2.7 V$                 | -                      | -               | ± 1              | 1 L2B |

| Total Error                                         |                   |                                                        | -                      | -               | ±2               | 1     |

# $(V_{SS}$ = 0.0 V, 2.0 V $\leq V_{DD}$ <2.7 V, Topr = - 40 to 85°C) Note 5 (V\_{SS} = 0.0 V, 1.8 V $\leq V_{DD}$ <2.0 V, Topr = - 10 to 85°C) Note 5

| Parameter                                           | Symbol               | Condition                                                 | Min                    | Тур.            | Max              | Unit |

|-----------------------------------------------------|----------------------|-----------------------------------------------------------|------------------------|-----------------|------------------|------|

| Analog Reference Voltage                            | V <sub>AREF</sub>    |                                                           | A <sub>VDD</sub> - 0.9 | -               | A <sub>VDD</sub> |      |

| Power Supply Voltage of<br>Analog Control Circuit   | A <sub>VDD</sub>     |                                                           |                        | V <sub>DD</sub> |                  |      |

| Analog Reference Voltage Range (Note 4)             | $\triangle v_{AREF}$ | $1.8 \text{ V} \leq \text{V}_{\text{DD}} < 2.0 \text{ V}$ | 1.8                    | -               | -                | ] V  |

|                                                     |                      | $2.0V \leqq V_{DD} < 2.7V$                                | 2.0                    | -               | -                |      |

| Analog Input Voltage                                | V <sub>AIN</sub>     |                                                           | V <sub>SS</sub>        | -               | VAREF            |      |

| Power Supply Current of<br>Analog Reference Voltage | I <sub>REF</sub>     | $V_{DD} = A_{VDD} = V_{AREF} = 2.7 V$ $V_{SS} = 0.0 V$    | -                      | 0.3             | 0.5              | mA   |

| Non linearity Error                                 |                      |                                                           | -                      | -               | ± 2              |      |

| Zero Point Error                                    |                      | $V_{DD} = A_{VDD} = 1.8 V,$                               | -                      | -               | ± 2              | LSB  |

| Full Scale Error                                    |                      | $V_{SS} = 0.0 V$<br>$V_{AREF} = 1.8 V$                    | -                      | -               | ±2               |      |

| Total Error                                         |                      |                                                           | -                      | -               | ±4               |      |

Note 1: The total error includes all errors except a quantization error, and is defined as a maximum deviation from the ideal conversion line.

Note 2: Conversion time is different in recommended value by power supply voltage.

About conversion time, please refer to "2.10.2 Register Configuration".

Note 3: Please use input voltage to AIN input Pin in limit of V<sub>AREF</sub> - V<sub>SS</sub>. When voltage of range outside is input, conversion value becomes unsettled and gives affect to other channel conversion value.

Note 4: Analog Reference Voltage Range:  $\triangle V_{AREF} = V_{AREF} - V_{SS}$ Note 5: When AD is used with  $V_{DD} < 2.7 V$ , the guaranteed temperature range varies with the operating voltage.

**AC** Characteristics

$(V_{SS} = 0 V, V_{DD} = 4.5 \text{ to } 5.5 V, \text{Topr} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                    | Symbol | Condition                                 | Min   | Тур.  | Max   | Unit |

|------------------------------|--------|-------------------------------------------|-------|-------|-------|------|

| Machine Cycle Time           |        | NORMAL 1, 2 mode                          |       | -     |       |      |

|                              | tcy    | IDLE 1, 2 mode                            | 0.25  |       | 4     |      |

|                              |        | SLOW 1, 2 mode                            | 447.0 | -     | 133.3 | μs   |

|                              |        | SLEEP 1, 2 mode                           | 117.6 |       |       |      |

| High Level Clock Pulse Width | twcH   | For external clock operation (XIN input)  |       | 31.25 | -     | ns   |

| Low Level Clock Pulse Width  | twcL   | fc = 16 MHz                               | -     |       |       | 115  |

| High Level Clock Pulse Width | twcH   | For external clock operation (XTIN input) |       | 15.26 | _     |      |

| Low Level Clock Pulse Width  | twcL   | fs = 32.768 kHz                           | _     |       |       | μs   |

#### $(V_{SS} = 0 V, V_{DD} = 2.7 \text{ to } 4.5 V, \text{Topr} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                    | Symbol | Condition                                 | Min   | Тур.  | Max   | Unit |

|------------------------------|--------|-------------------------------------------|-------|-------|-------|------|

| Machine Cycle Time           |        | NORMAL 1, 2 mode                          |       | -     | 4     |      |

|                              | tov    | IDLE 1, 2 mode                            | 0.5   |       |       | μs   |

|                              | tcy    | SLOW 1, 2 mode                            | 117 C |       | 133.3 |      |

|                              |        | SLEEP 1, 2 mode                           | 117.6 | -     |       |      |

| High Level Clock Pulse Width | twcH   | For external clock operation (XIN input)  | -     | 62.5  | -     | ns   |

| Low Level Clock Pulse Width  | twcL   | fc = 8 MHz                                |       |       |       |      |

| High Level Clock Pulse Width | twcH   | For external clock operation (XTIN input) |       | 15.26 | -     |      |

| Low Level Clock Pulse Width  | twcL   | fs = 32.768 kHz                           | -     |       |       | μS   |

## $(V_{SS} = 0 V, V_{DD} = 1.8 \text{ to } 2.7 V, \text{Topr} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                    | Symbol | Condition                                 | Min   | Тур.   | Max   | Unit |

|------------------------------|--------|-------------------------------------------|-------|--------|-------|------|

| Machine Cycle Time           |        | NORMAL 1, 2 mode                          |       |        | 4     |      |

|                              | tav    | IDLE 1, 2 mode                            | 0.95  | -      |       | μs   |

|                              | icy    | tcy SLOW 1, 2 mode                        |       |        | 133.3 |      |

|                              |        | SLEEP 1, 2 mode                           | 117.6 | -      |       |      |

| High Level Clock Pulse Width | twcH   | For external clock operation (XIN input)  | -     | 119.05 | -     | ns   |

| Low Level Clock Pulse Width  | twcL   | fc = 4.2 MHz                              |       |        |       |      |

| High Level Clock Pulse Width | twcH   | For external clock operation (XTIN input) |       | 15.26  | -     |      |

| Low Level Clock Pulse Width  | twcL   | fs = 32.768 kHz                           | -     |        |       | μS   |

Timer Counter 1 input (ECIN) Characteristics (V<sub>SS</sub> = 0 V, Topr = -40 to 85°C)

| Parameter              | Symbol           | Condition                                          | Min               | Тур. | Max | Unit |     |

|------------------------|------------------|----------------------------------------------------|-------------------|------|-----|------|-----|

|                        |                  | Frequency measurement mode                         | Single edge count | -    | -   | 16   | MHz |

|                        |                  | $V_{DD} = 4.5 \text{ to } 5.5 \text{ V}$           | Both edge count   | -    | -   |      |     |

|                        | +                | Frequency measurement mode $V_{DD} = 2.7$ to 4.5 V | Single edge count | -    | -   | - 8  |     |

| TC1 input (ECIN input) | t <sub>TC1</sub> |                                                    | Both edge count   | -    | -   |      |     |

|                        |                  | Frequency measurement mode $V_{DD} = 1.8$ to 2.7 V | Single edge count | -    | -   | 4.2  |     |

|                        |                  |                                                    | Both edge count   | -    | -   |      |     |

| Recommended Oscillating Conditions - 1 $(V_{SS} = 0 V, V_{DD} = 4.5 V \text{ to } 5.5 V, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$ |                   |                        |                                            |                      |             |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------------|--------------------------------------------|----------------------|-------------|--|

|                                                                                                                                              |                   | Oscillation            | December ded Oscillator                    | Recommended Constant |             |  |

| Parameter Oscillator                                                                                                                         | Frequency         | Recommended Oscillator | C <sub>1</sub>                             | C <sub>2</sub>       |             |  |

| High-frequency<br>Oscillation                                                                                                                | Ceramic Resonator | 16 MHz                 | MURATA CSALS16M0X55-B0<br>CSACV16.00MXJ040 | 7 pF<br>7pF          | 7 pF<br>7pF |  |

Recommended Oscillating Conditions - 2 ( $V_{SS} = 0 V$ ,  $V_{DD} = 2.7 V$  to 5.5 V, Topr = -40 to 85°C)

|                               |                      | Oscillation<br>Frequency |                                    | Recommended Constant |                                      |

|-------------------------------|----------------------|--------------------------|------------------------------------|----------------------|--------------------------------------|

| Parameter                     | Parameter Oscillator |                          | Recommended Oscillator             | C <sub>1</sub>       | C <sub>2</sub>                       |

| High-frequency<br>Oscillation | Ceramic Resonator    | 8 MHz                    | MURATA CSTS0800MG03<br>CSTCC8.00MG |                      | 15 pF (built-in)<br>15 pF (built-in) |

| Recommended Oscillating Conditions - 3 $(V_{SS} = 0 V, V_{DD} = 2.0 V \text{ to } 5.5 V, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$ |                   |                          |                                        |                             |                                      |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------|----------------------------------------|-----------------------------|--------------------------------------|--|--|

| Parameter                                                                                                                                    | Oscillator        | Oscillation<br>Frequency | Recommended Oscillator                 | Recommend<br>C <sub>1</sub> | ed Constant<br>C <sub>2</sub>        |  |  |

| High-frequency<br>Oscillation                                                                                                                | Ceramic Resonator | 4.19 MHz                 | MURATA CSTS0419MG06<br>CSTCR4M19G55-R0 |                             | 47 pF (built-in)<br>39 pF (built-in) |  |  |

| Recommended (                 | Oscillating Conditi | ons - 4 (V <sub>SS</sub> = | $0 \text{ V}, \text{ V}_{\text{DD}} = 1.8 \text{ V} \text{ to } 5.5 \text{ V}, \text{ Topr} = -40$ | to 85°C)             |       |

|-------------------------------|---------------------|----------------------------|----------------------------------------------------------------------------------------------------|----------------------|-------|

|                               |                     | Oscillation                | Recommended Oscillator                                                                             | Recommended Constant |       |

| Parameter Oscillator          | Frequency           | C <sub>1</sub>             |                                                                                                    | C <sub>2</sub>       |       |

| High-frequency<br>Oscillation | Ceramic Resonator   | 4.19 MHz                   | MURATA CSA4.19MG-951                                                                               | 30 pF                | 30 pF |

Note 1: An electrical shield by metal shield plate on the surface of IC package is recommended in order to protect the device from the high electric field stress applied from CRT (Cathodic Ray Tube) for continuous reliable operation.

Note 2: The product numbers and specifications of the resonators by Murata Manufacturing Co., Ltd. are subject to change. For up-to-date information, please refer to the following URL; http://www.murata.co.jp/search/index.html