# VOLTAGE REGULATOR FOR CMOS MICROPROCESSOR BASED SYSTEMS

- OUTPUT CURRENT: 100 mA

- ON-CHIP CURRENT LIMIT AND THERMAL PROTECTION

- RESET GENERATOR WITH EXTERNALLY AD-JUSTABLE DELAY

- REGULATOR INPUT VOLTAGE LEVEL DE-TECTION SYSTEM (level adjusted externally)

- WATCH DOG TIMER

- INPUT VOLTAGE FAILURE DETECTION SYS-TEM DELIVERS A STORE SIGNAL IN CASE OF INPUT VOLTAGE DISCONTINUITY

- REGULATOR ON/OFF CONTROL SIGNAL AL-SO SETS THE OUTPUT TO HIGH IMPEDANCE STATE

#### DESCRIPTION

The TEA7105 is a voltage regulator especially suited to all microprocessor-based digital systems. Upon initial power on, the circuit delivers a RESET signal with programmable delay. This signal is disabled under three conditions:

- When supply voltage falls below a certain threshold level adjusted externally

- When output voltage falls below a preset level

- In the absence of trigger pulses on WATCH DOG input

The regulator features a WATCH DOG function with timing requirements met by a wide range of frequencies. The device detects the occurance of input voltage DROP and delivers a STORE signal whitebeing powered by the energy stored in the input capacitor.

An ON/OFF function is provided enabling the circuit to be put in standby mode and also to set the regulated output to high impedance state. In this mode, the power consumption is extremely low.

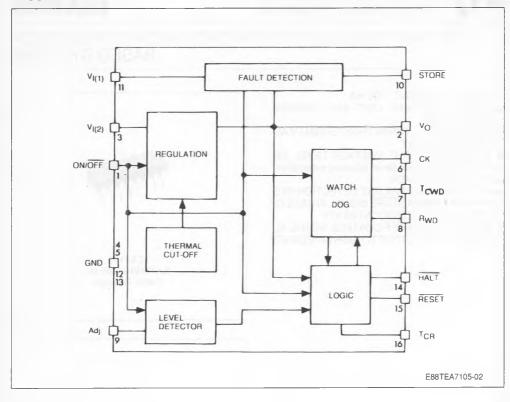

#### **BLOCK DIAGRAM**

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol                                | Parameter                           | Value                      | Unit |

|---------------------------------------|-------------------------------------|----------------------------|------|

| V <sub>I(1)</sub> . V <sub>I(2)</sub> | Supply Voltage                      | + 40                       | V    |

|                                       | CK Input Voltage                    | - 0.3 to V <sub>O</sub>    | V    |

|                                       | ON/OFF Input Voltage                | - 0.3 to V <sub>I(2)</sub> | V    |

|                                       | Adj. Pin Input Voltage              | - 0.3 to V <sub>I(2)</sub> | V    |

| Ptot                                  | Power Dissipation                   | Internally Limited         | _    |

| Toper                                 | Operating Ambient Temperature Range | - 40 to + 85               | °C   |

| T <sub>sta</sub>                      | Storage Temperature Range           | - 65 to + 150              | °C   |

#### THERMAL DATA

| R <sub>th (i-a)</sub> | Maximum Junction-ambient Thermal Resistance | 45 | °C/W |

|-----------------------|---------------------------------------------|----|------|

| R <sub>th (j-c)</sub> | Maximum Junction-case Thermal Resistance    | 11 | °C/W |

R<sub>th(j-a)</sub> is measured on packages soldered on a printed circuit board with a copper area of 20 cm<sup>2</sup>.

Unit

mA

Max.

Typ.

200

Min.

# **ELECTRICAL CHARACTERISTICS** $T_{amb} = +25$ °C, $V_{I(1)} = V_{I(2)} = +12$ V (unless otherwise specified)

Short-circuit Current ( $V_1 = + 10 \text{ V}, 0 \le V_0 \le + 5 \text{ V}$ )

**Parameter**

| ٧ | OLTAGE | REGULATOR                                                                                         |      |    |      |    |

|---|--------|---------------------------------------------------------------------------------------------------|------|----|------|----|

|   | Vo     | Output Voltage (+ 7 V $\leq$ V <sub>I</sub> $\leq$ + 36 V, 1 $\leq$ I <sub>O</sub> $\leq$ 100 mA) | 4.85 | _  | 5.15 | V  |

|   | Kvi    | Line Regulation (+ 7 V $\leq$ V <sub>I</sub> $\leq$ + 36 V, I <sub>O</sub> = 50 mA)               | _    | 30 | 100  | mV |

|   | Kvo    | Load Regulation (V <sub>I</sub> = + 10 V, 5 mA < I <sub>O</sub> < 100 mA)                         | _    | 10 | 75   | mV |

#### RESET FUNCTION

Symbol

Isc

|                       | Minimum Output Voltage to Activate RESET             | 4.5                | _   | 4.8 | V  |

|-----------------------|------------------------------------------------------|--------------------|-----|-----|----|

|                       | Output Voltage Hysteresis to Disable RESET           | -                  | 50  | _   | mV |

| V <sub>(ref)</sub>    | Internal Reference for the Adj. Detection            | -                  | 2.5 | _   | V  |

| l(adj)                | Maximum Adj. Pin Current (V <sub>(adj)</sub> = 0 V)  | -                  | -   | 1   | μА |

| V <sub>L(reset)</sub> | Low Level RESET Output (Io = 2 mA)                   | -                  | -   | 0.4 | V  |

| V <sub>H(reset)</sub> | High Level RESET Output (I <sub>OH</sub> = - 100 μA) | V <sub>0</sub> - 1 | -   | Vo  | V  |

### CK AND ON/OFF INPUTS

| ſ | V <sub>IL</sub> | Maximum Low Level Input Voltage                              | _     | _    | 0.8 | V  |

|---|-----------------|--------------------------------------------------------------|-------|------|-----|----|

|   | I <sub>IL</sub> | Maximum Low Level Input Current (V <sub>IL</sub> = 0 V)      | - 120 | - 60 | _   | μА |

|   | V <sub>IH</sub> | Minimum High Level Input Voltage                             | 2.4   | _    | -   | V  |

|   | LiH             | Maximum High Level Input Current (V <sub>IH</sub> = + 2.4 V) | _     | -    | 100 | μА |

### ALARM /STORE FUNCTION

| V <sub>H(min)</sub>   | Minimum Input Voltage to Activate STORE Signal       | 5                  | 5.7 | 6.4 | V |

|-----------------------|------------------------------------------------------|--------------------|-----|-----|---|

| V <sub>L(store)</sub> | Low Level STORE Output (I <sub>0</sub> = 2 mA)       | _                  | _   | 0.4 | V |

| VH(store)             | High Level STORE Output (I <sub>OH</sub> = - 100 μA) | V <sub>0</sub> - 1 | _   | Vo  | V |

## ON/OFF FUNCTION

| 1 <sub>(Sb)</sub>   | Standby Current                                                                        |   |     |   | mA |

|---------------------|----------------------------------------------------------------------------------------|---|-----|---|----|

|                     | $V_{(ON/OFF)} = 2.4 \text{ V}$                                                         | - | 4   | 8 |    |

|                     | V <sub>(ON/OFF)</sub> = 0 V                                                            | _ | 0.5 | - |    |

| I <sub>O(dis)</sub> | V <sub>O</sub> Pin Discharge Current (V <sub>ON/OFF</sub> = 0, V <sub>O</sub> = + 5 V) | _ | _   | 2 | μА |

#### **ELECTRICAL CHARACTERISTICS**(continued)

|  | Symbol | Parameter | Min. | Тур. | Max. | Unit |

|--|--------|-----------|------|------|------|------|

|--|--------|-----------|------|------|------|------|

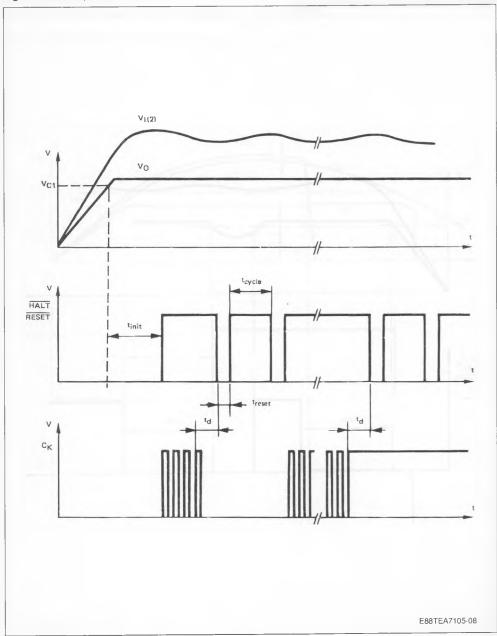

### TIMING (see timing diagrams)

|                    | CWD                                                              | _  | _  | 33             | nF |

|--------------------|------------------------------------------------------------------|----|----|----------------|----|

|                    | CR                                                               | _  | _  | 220            | nF |

| t <sub>init</sub>  | t <sub>init</sub> (C <sub>R</sub> = 100 nF) Note 1               | -  | 30 | -              | ms |

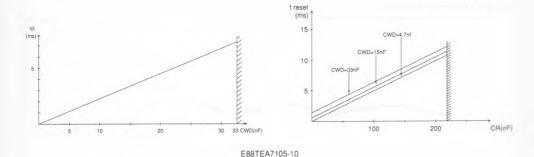

| t <sub>d</sub>     | t <sub>d</sub> (CWD = 33 nF) Note 2                              | _  | 7  | _              | ms |

| treset             | t <sub>reset</sub> (CWD = 33 nF, C <sub>R</sub> = 100 nF) Note 3 | _  | 6  | _              | ms |

| t <sub>cycle</sub> | t <sub>cycle</sub> (CWD = 33 nF, C <sub>R</sub> = 100 nF) Note 4 |    | 13 | _              | ms |

| T <sub>CK</sub>    | Pulse Width at Input CK                                          | 20 | _  | t <sub>d</sub> | μs |

Notes: 1. This is the period at the end of which RESET signal appears after Vour rises up and when switch S1 has been closed, this is given by the following relationship.

$t_{nit} = 0.3$  CR  $\cdot$  10<sup>6</sup> 2. This is the maximal clock period determined by the value of CWD

$t_d = \frac{2.7}{11.6} \cdot \text{CWD} \cdot 10^6$

This is the time required for micorcomputer reinitialisation.

$$t_{\text{reset}} = \frac{1}{116} \text{ CWD } 10^6 + \frac{5}{125} \text{ CR} \cdot 10^6$$

This is the time required by the microcomputer during a restart to generate at least one clock pulse

toppe = t<sub>0</sub> + t<sub>lessel</sub>.

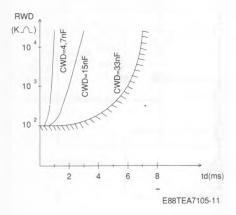

Remark: For more important clock period see specific application figure 10

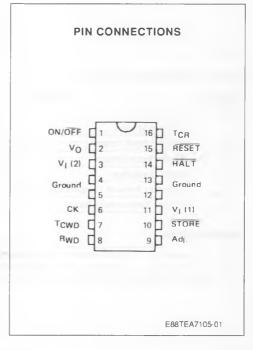

#### **PIN DESCRIPTION**

V<sub>I(1)</sub>

Input connected directly to power supply to detect any supply failure.

V<sub>I(2)</sub>

Regulator's power input. This input is separated from power supply through a diode.

A decoupling capacitor is connected to this input.

An inadequate supply voltage level is detected at this input.

Adj

In order to detect the level of  $V_{I(2)}$  a resistance inserted between Adj pin and  $V_{I(2)}$  and another between Adj pin and GND are necessary.

ON/OFF

Logic input. A logic 1 applied to this input will cause the TEA7105 to become fully operational; whereas a logic O will set the circuit to standby mode.

Vo

Power cutput to microprocessor and digital systems.

Two different output voltage levels are detected according to whether the transition is from low voltage

to high voltage or the inverse (Refer to timing diagram - figure 4).

High impedance output when the circuit is in standby mode.

TCR

Combination of a grounded capacitor and the internal current generator will implement the RESET signal delay upon the initial power on.

T<sub>CWD</sub>

A relaxation oscillator is implemented by combining a grounded capacitor and the internal current generator

RwD

A resistance inserted between this pin and ground will cause the flow of additional charging current to capacitor CwD thereby modifying the slope of the local oscillator and improving the choice of CwD values.

Ск

This is the WATCH DOG function input. The clock signal resets the ramp of the relaxation oscillator. The circuit is triggerred on rising edge of the clock.

#### RESET

During the initialization, TEA7105 detects at the output Vo a voltage level Vc1 and generates a RESET signal (see timing diagrams - figure 5).

The following three conditions cause RESET signal to be forced to zero level :

- If the output voltage level falls below V<sub>C1</sub> by a hysteresis of ΔV<sub>C1</sub> (see timing diagrams - fiqure 5).

- If no signal arrives at input CK for a minimal period to 20 µs and maximal period equal to td (see timing diagrams - figure 6).

If the input voltage falls below the adjustable threshold level (see timing diagrams - figure 4).

#### HALT

Fonction and electrical characteristics are the same as the RESET pin.

#### STORE

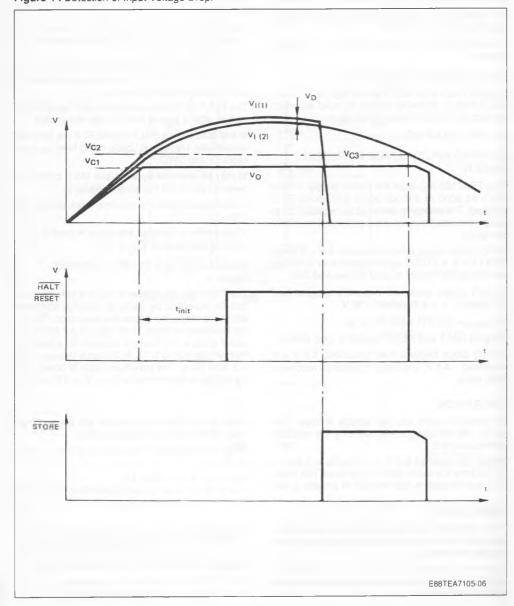

If input voltage  $V_{I(1)}$  falls below  $V_{C2}$  level, TEA7105 will use the energy stored in the input capacitor to generate the STORE signal for the microprocessor data protection (see timing diagrams - figure 4).

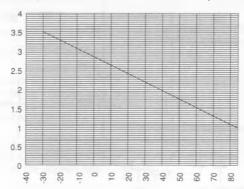

Figure 1: Maximum Power Dissipation Versus Junction-ambient Temperature.

E88TEA7105-03

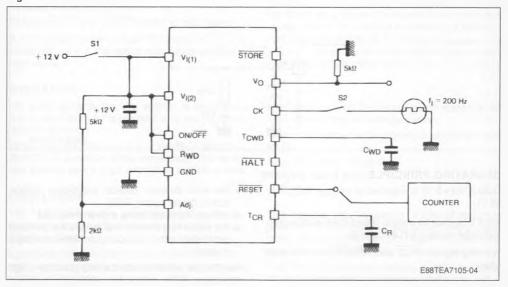

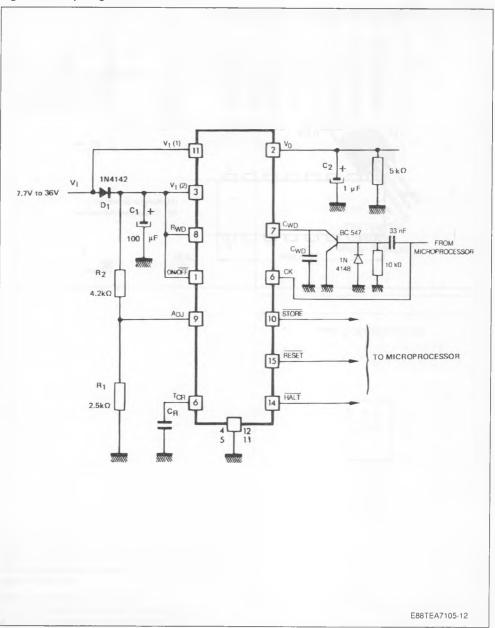

Figure 2: Test Circuit.

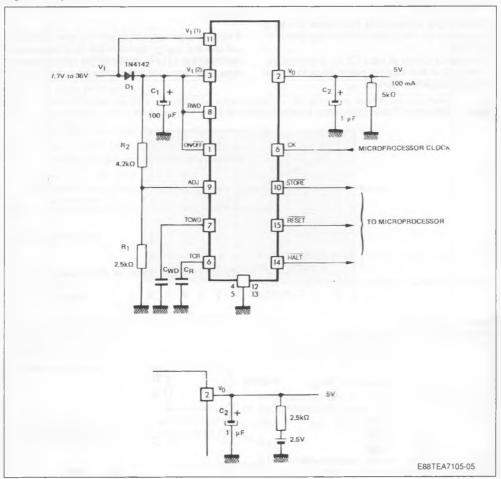

#### TYPICAL APPLICATION

A minimum current of 1 mA should be delivered by the TEA7105 for effective voltage control. This is why a 5  $K\Omega$  resistor (or an equivalent load if a

backup battery is used) shall be connected between  $V_O$  and the ground.

Figure 3: Typical Application.

### **OPERATING PRINCIPLE** (see block diagram)

Output  $V_O(+\ 5\ V)$  is supplied by voltage  $V_I(2)$  (7 to 36 V).

Input  $V_I(1)$  may be used to detect input voltage drop and to generate a STORE signal.

Warning signals  $\overline{\text{HALT}}$  and  $\overline{\text{RESET}}$  are generated when :

• the circuit is being powered, for a time tinit,

- the level detector detects insufficient voltage across power supply V<sub>1</sub>(2),

- voltage Vo drops below a given threshold,

- the watch dog detects that pulses are no more generated by the microcomputer when running a program.

The thermal protection device may produce a high impedance at the voltage regulator output.

The impedance of the complete circuit becomes high when  $V_1(2)$  drops below a fixed threshold, 4.5 V < V threshold < 4.8 V or by acting on the ON/OFF input.

External capacitors allow inputs town and ton to define the t<sub>Init</sub>, t<sub>reset</sub>, t<sub>cycle</sub>, td times (figures 5 and 7) which are characteristic of the HALT and RESET signals.

It's possible to inhibit the watch dog function by grounding the pin 7 (CWD).

If store function is not used the diode D1 is not accessary.

#### WHEN POWERING (figures 4,5,6)

Outputs HALT and RESET are (at logic level O) during a time t<sub>int</sub> following voltage V<sub>O</sub> build up, which is used for microcomputer initialization.

$t_{init}$  (ms) = 0.3 CR (nF).

# WHEN NO INPUT VOLTAGE IS PRESENT (figure 4)

The TEA7105 regulates the power supply voltage  $V_I(1)$ . As soon as it drops below  $V_I(2)$  diode D1 is blocked. The energy is delivered by capacitor C1 to supply the internal logics of the circuit and the microcomputer.

If  $V_1(1)$  drops below a fixed threshold, 5 V < V threshold < 6.4 V, a STORE signal is generated to indicate to the supplied system to save the required data.

If  $V_1(2)$  drops below an externally programmed threshold (7 V < V threshold < 36 V).

$V_{threshold} = (2.5 (R1 + R2)/R1) + V_d.$

Outputs HALT and RESET switch to logic state 0.

If  $V_1(2)$  drops below a fixed threshold, 4.5 V < V threshold < 4.8 V, the circuit impedance reaches a high value.

#### **OPERATION**

For small currents the  $V_{BE}$  voltage is lower than 0.6 V; the transistor is blocked, only the regulator delivers current.

When  $V_{BE}$  reaches 0.6 V (I =  $V_{BE}/R_b$  = 0.6/33 = 20 mA) the transistor starts conduction. The transistor current gain is high enough to provide a very

# WHEN THE OUTPUT VOLTAGE DROPS (figure 4)

When voltage  $V_O$  drops below a <u>fixed threshold</u>, 4.5 V < V threshold < 4.8 V outputs HALT and RESET switch to logic state 0.

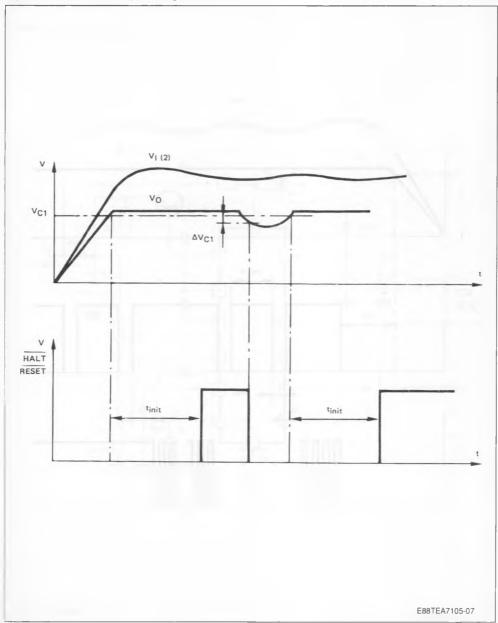

# WHEN NO CLOCK SIGNAL IS PRESENT (figure 6)

The microcomputer when in operation will generate a clock signal whose period t will be between t min =  $20 \mu s$  and t max = td

When this signal is not generated, or if the clock period is larger than td, this means that the microcomputer does not operate correctly.

The TEA7105 thus generates the HALT and RESET signals after a time to from the last rising edge.

In this case signals HALT and RESET are activated periodically, t reset and t cycle being fixed by capacitors Cr and CWD.

td may be adjusted by a resistor RWD connected between pin 8 and the ground (figure 9).

In normal condition the maximal clock period is to  $7\ \mathrm{ms}.$

It's possible to increase this value in adding some external components (figure 10).

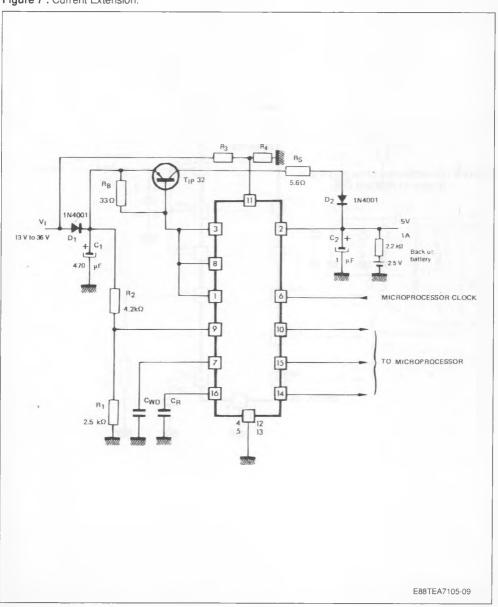

# INCREASE OF THE OUTPUT CURRENT (figure 7)

The TEA7105 can deliver a 100 mA current which can be increased by using an external transistor, which maintains the circuit characteristics. The setup illustrated in figure 10 an used in our laboratory circuit gives a 7 mV output variation for a load current varying from 0 to 1A. In this case  $V_{threshold} \approx V_S + 3 V_D + R_S.I_S$ . The maximum value of power supply voltage is determined by  $V_{min} \approx V_S + 3 V_D + R_S.I_S$ .

small current drift of the controller with respect to the load, which improves voltage control.

When short-circuited the current is limited by resistor Rs.

$I_{SC} = (V_I - 2.V_d - V_{Sat}) R_S$

#### CONCLUSION

The TEA7105 is a new generation voltage regulator giving a simple answer to microcomputer power supply problems.

It prevents untimely interruption of microcomputers and makes it possible to return to current program without any trouble. This regulator may be used in its original version to power a microcomputer or any system with a maximum current requirement of 100 mA. A current extension is available for more powerful systems.

The TEA7105 provides a simple, reliable, economical and high performance power supply.

When  $V_I$  (1) becom<u>es lowe</u>r than a fixed threshold 5V < VC3 < 6.4 the <u>STORE</u> output switches to logic state 1. This threshold may be modified by using an external potential divider.

When V<sub>I</sub> (2) becomes lower than an externally ad-

justable threshold signals  $\overline{HALT}$  and  $\overline{RESET}$  switch to logic state O (V<sub>C</sub>2 = 2.5 (R1 + R2) / R1).

When  $V_{\rm I}$  (2) becomes lower than a fixed threshold 4.5 V < V threshold < 5.5 V the circuit impedance becomes high.

Figure 4: Detection of Input Voltage Drop.

When the output voltage becomes lower than V threshold (4.5 < threshold < 4.8 V) the warning signals HALT and RESET switch to logic state O.

These signals become active as soon as  $V_O$  reaches the threshold to reinitialize and block the microcomputer during  $t_{\rm init}$ .

Figure 5: Detection of Output Voltage Drop.

Signals  $\overline{\text{HALT}}$  and  $\overline{\text{RESET}}$  become active after a time  $t_d$  from the last clock signal rising edge.

$t_{d}$  and  $t_{reset}$  depend on capacitors  $C_{WD}$  and  $C_{R},\,preset$  curves are given in figure 8.

Figure 6: Interruption of Clock Pulses.

This application is used to deliver a 1 A current with excellent voltage control. The D2 diode avoids the discharge of the back up battery in the TEA7105 when it's in hight impedance output in stand by mode.

The value of  $V_{I(1)}$  activing  $\overline{STORE}$  signal is determined by  $(V_{I(1)}$  store = (5.7 (R3 + R4)/R4).

Figure 7: Current Extension.

We see that  $C_r$  and  $C_{WD}$  actions are not fully independent. It is possible to adjust td more finely by

using an external resistor connected between pin RwD and the ground (figure 9).

Figure 8: Determination of t<sub>d</sub> and t<sub>reset</sub> in relation to C<sub>WD</sub> and C<sub>R</sub>.

Figure 9 : Determination of tok max = t<sub>d</sub> in relation to Rwp and Cwp.

For applications using very long clock period it's possible to use an external transistor. In this case the maximal clock period, in relation to Cwp, may be

longer than 500 ms. The relationship to define  $t_{init}$ ,  $t_d$ ,  $t_{reset}$  are same that in typical application.

Figure 10: Very Long Clock Period.

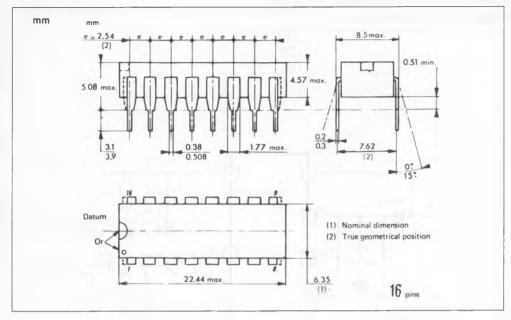

#### PACKAGE MECHANICAL DATA

16 PINS - PLASTIC DIP