## HIGH RANGE SPEECH CIRCUIT WITH SQUELCH FUNCTION

#### 2/4 WIRES INTERFACE WITH

- DOUBLE ANTISIDETONE NETWORK

- MICROPHONE NOISE THRESHOLD (squelch)

- RX GAIN AND AC IMPEDANCE EXTER-NALLY PROGRAMMABLE

- DTMF INTERFACE

- PULSE DIAL INTERFACE

- 3.25 VOLTS SUPPLY FOR MICROPROCES-SOR OR DIALER

- RESET TO MICROPROCESSOR

- CURRENT SUPPLY FOR LOUDSPEAKER

- HANDS-FREE INTERFACE

- DC CHARACTERISTIC AND ON/OFF HOOK FOR FRANCE

- CONTROL AGAINST HIGH VOLTAGE TRAN-SIENTS

#### DESCRIPTION

The TEA7050 is expressely designed to meet the french specification for telephone set in high range equipments.

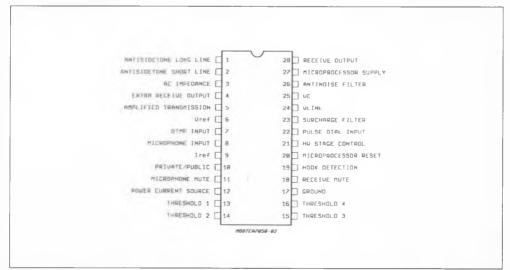

#### **PIN CONNECTION** (top view)

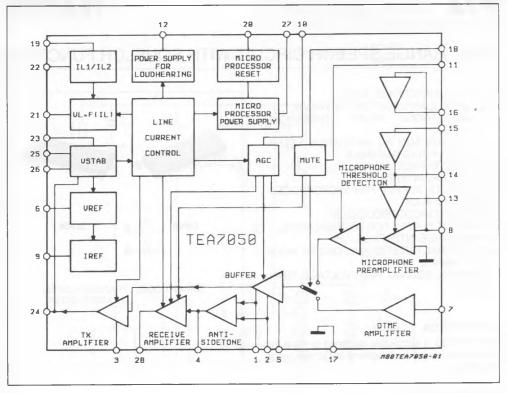

#### **BLOCK DIAGRAM**

## ELECTRICAL CHARACTERISTICS

| Symbol                     | Parameter                                                                          | Test Conditions                                                 | Min.                 | Тур.             | Max.       | Unit.             |

|----------------------------|------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------|------------------|------------|-------------------|

| Vc                         | Stabilized Voltage (pin 25)                                                        | II = 27mA                                                       | 2.6                  | 2.8              | 2.95       | V                 |

| Idem                       | Charging Current (pin 25)                                                          | II = 27mA                                                       |                      | 2.6              |            | mA                |

| lr<br>Ir/II                | Line Current Regulation for HV<br>Control (pin 21)                                 | Pin 19 = Pin 25 = GND<br>II = 150mA<br>II = 100mA               | 150                  |                  | 5          | μА                |

|                            |                                                                                    | Pin 19 ON ; Pin 25 = GND<br>II = 75mA                           | 150                  |                  |            | μA                |

|                            |                                                                                    | Pins 19 and 25 ON<br>II = 60mA<br>II = 16mA<br>27mA < II < 50mA | 150<br>0.8           | 0.9              | 100<br>1.0 | μΑ<br>nA<br>μΑ/mA |

| lint                       | Internal Bias Current (pin 25)                                                     | II = 27mA ;<br>R9 = 26.7 Kohms ;<br>(V24 = R6°lint + Vc)        | 410                  | 460              | 510        | μА                |

| Vref                       | Reference Voltage                                                                  | II = 27mA                                                       | 1.32                 | 1.38             | 1.47       | V                 |

| Iref                       | Current at Vref                                                                    |                                                                 | - 10                 |                  | 100        | μА                |

| Vmp                        | Stabilized Supply at Pin 27                                                        |                                                                 | 3.1                  | 3.3              | 3.5        | V                 |

| lcmp                       | Charging Current at Pin 27                                                         | Pin 19 = Pin 25 = GND<br>IL1 = II - Idem                        | 0.7 x<br>x IL1       |                  |            | mA                |

| lspm                       | Static Current at Pin 27                                                           | II = 6mA<br>II > 25mA                                           | 0.5<br>2.5           | 2.8              |            | mA                |

| limp                       | Internal Consumption                                                               |                                                                 | 90                   | 120              | 160        | μA                |

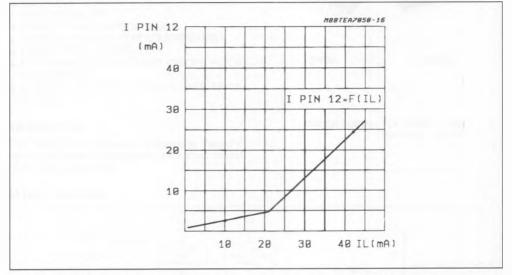

| lea                        | Supply Current for Parallel<br>Circuits (pin 12)                                   | R9 = 26.7Kohm<br>II = 10mA<br>II = 27mA<br>II = 42mA            | 8<br>21              | 3<br>9.5<br>23.5 | 11<br>26   | mA<br>mA<br>mA    |

| Vrh<br>Vrb<br>Vrsh<br>Vrsb | Microprocessor Reset<br>High Treshold<br>Low Treshold<br>Output High<br>Output Low | Reset = 1<br>Reset = 0                                          | 0.845<br>0.76<br>0.9 | 0.89<br>0.8      | 0.84       | Vmp<br>(pin 27)   |

## **ELECTRICAL CHARACTERISTICS**

| Symbol     | Parameter                               | Test Conditions                               | Min.         | Тур.         | Max.         | Unit.  |

|------------|-----------------------------------------|-----------------------------------------------|--------------|--------------|--------------|--------|

| Vmh<br>Vmb | Mute Microphone (pin 11)                | ON<br>OFF                                     | 1.6          |              | 0.8          | V<br>V |

| Vmh<br>Vmb | Mute Earphone (pin 18)                  | ON<br>OFF                                     | 2.7          |              | 2.1          | V<br>V |

| Gel<br>Gec | Tx Gain Long Line<br>Tx Gain Short Line | = 27mA<br>   = 42mA                           | 48.5<br>41.5 | 49.5<br>43.5 | 50.5<br>45.5 | dB     |

| DGe        | Squelch Attenuation                     |                                               |              | - 9          |              | dB     |

| Vse        | Squelch Switch-off Level on the Line    | II = 27mA                                     | - 44         | - 39         | - 34         | dBm    |

| Gmf        | DTMF Gain                               | II = 27mA<br>Pin 11 > 1.6V                    | 33.5         | 34.5         | 35.5         | dB     |

| De         | Tx Distortion                           | II = 27 to 42mA<br>VI = 0dBm<br>VI = 3dBm     |              |              | 3<br>10      | %      |

| Ze         | Microphone Impedance                    |                                               | 9.6          | 12           | 14.5         | Kohm   |

| Вер        | Tx Noise<br>(psophometric)              | II > 27mA<br>2K at Pins 6-8                   |              | - 71         |              | dBmp   |

| Re         | Tx Attenuation in Mute Mode             | II = 27mA<br>Pin 11 > 1.6V                    | 60           |              |              | dB     |

| Grl<br>Grc | Rx Gain Long Line<br>Rx Gain Short Line | II = 27mA<br>II = 42mA                        | 29<br>22     | 30<br>24     | 31<br>26     | dB     |

| Dr         | Rx Distortion                           | II = 27 to 42mA<br>Vec = 500mV<br>Vec = 700mV |              |              | 3<br>10      | %      |

| Brp        | Rx Noise                                | 11 > 27mA                                     |              | - 74         |              | dBmp   |

| Rc         | Rx Attenuation in Mute Mode             | II = 27mA<br>Pin 18 > 2.7V                    | 60           |              |              | dB     |

| Gal        | Antisidetone                            | II = 27 to 42mA                               | - 22         |              |              | dB     |

| Zac        | AC Impedance                            | ll > 27mA                                     | 500          | 650          | 800          | ohm    |

| Grs        | Confidence Level<br>Vrec/Vmf            | Pin 11 > 1.6V ;<br>Pin 14 > 2.7V              | 28           | 31           | 34           | dB     |

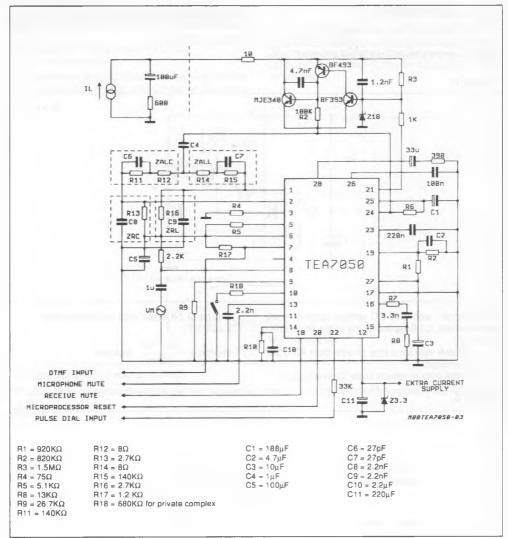

#### **TEST CIRCUIT**

## **CIRCUIT DESCRIPTION**

#### 1. DC-CHARACTERISTICS

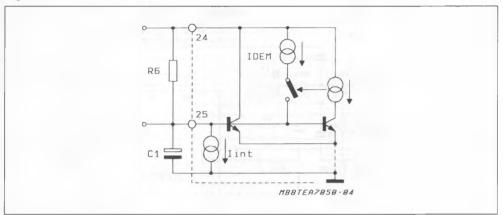

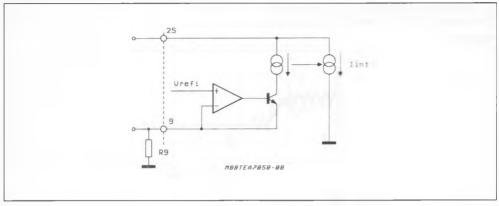

1.1. VC (PIN 25). The stabilized voltage Vc is connected to Vline (pin 24) through an internal shunt regulator which presents to the line a high AC impe-

#### Figure 1.

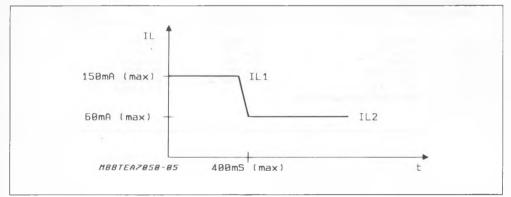

At "Off-hook", with only DC voltage applied to the line terminals, C1 fixes the timing of the line current profile at :

- 150mA max for a time shorter than 400msec (T-charge)

- 60mA max in steady state (conversation)

T-charge of 240msec (typ) is obtained with C1 = 220  $\mu\text{F}.$

dance at frequencies higher than 200Hz. At this purpose the value of C1 (at pin 25) must be not lower

than 47 microFarad.

T-charge =  $\frac{Vc \times C1}{Idem}$  typically.

#### Figure 2.

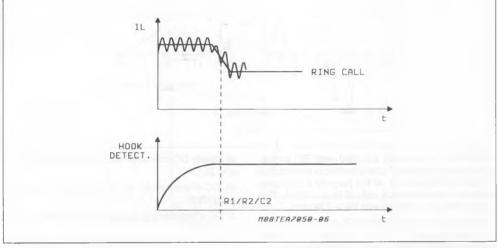

1.2. HOOK DETECTION (in ring mode) (pin 19). The DC-characteristic requested to allow off-hook detection by the exchange during ring call may be accomplished :

a) through an analog control (R-C) or b) by a microprocessor.

a) Application with standard dialer (analog control) The components R1, R2 and C2 define the timing

#### Figure 3.

of the DC characteristic and also limit at 75mA-peak the line current during decadic dialing.

Optimum values are : - R1 x C2 = 1.8sec; R2 x C2 = 0.8sec.

To reduce the minimum time between a "on-hook / off-hook" sequence, R2 may be replaced by a switch to ground.

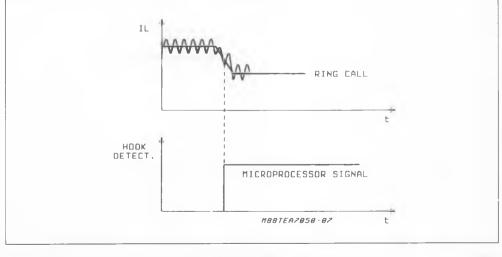

b) Application with a microprocessor

Pin 19 may be controlled directly by the micro-controller, through a resistor R1b which replaces R1, R2 and C2.

#### Figure 4.

1.3. VLINE (PIN 24). The line voltage (pin 24) is determined by the value of the external resistor R6 and by the internal current, lint, flowing between Vc (pin 25) and Ground (see also paragr. 1.1.) : Vline = Vc + R6 x lint. Vc is fixed by design at about 2.8 volts.

lint is reversely related to R9 (lint = 12V / R9 at lline = 27mA).

Vline must be externally adjusted (with R6) to guarantee both DC and AC characteristic in accordance to the french standards. At this purpose it is suggested that Vline equals 5.6 volts at lline = 16mA. This typical value is obtained with R6 = 7.5Kohm.

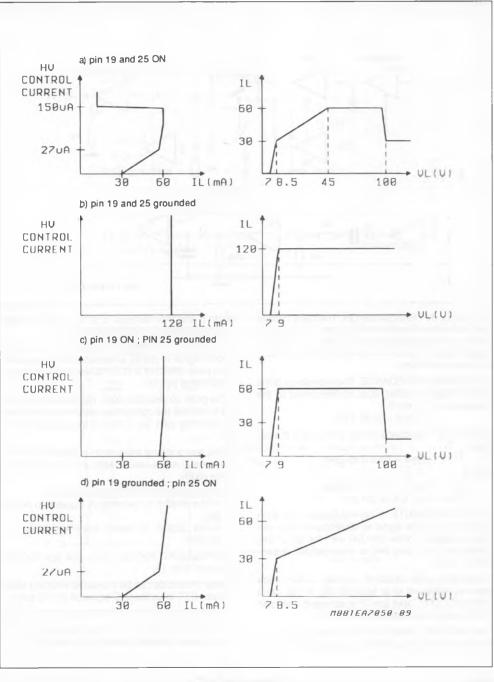

1.4. HIGH VOLTAGE CONTROL STAGE (PIN 21). The behaviour of "HV control" is determined by several conditions, both internal (lline sensor) and external (pins 19 and 25) with the purpose to accomplish the different DC characteristics and transitory conditions imposed by the French specification : a) steady DC-characteristic and lightnings (pins 19 and 25 ON)

b) DC-characteristic at off-hook (pin 19 and 25 grounded)

c) DC-characteristic during decadic dialing (pin 25 grounded)

d) DC-characteristic after off-hook in ringing (pin 19 grounded)

To do that, HV control pin regulates the current injected into the external high voltage transistor stage, requested by the French specification.

## Figure 6.

SGS-THOMSON MICROELECTROMICS

#### 2. TRANSMISSION CHAIN

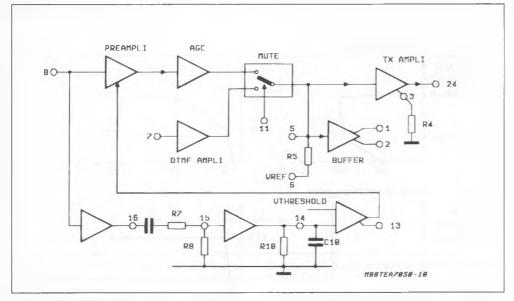

Figure 7.

2.1. A.G.C. IN TRANSMISSION. The transmission gain between Microphone Input (pin 8) and Vline (pin 24) is internally decreased of 6dB when the line current varies from 27mA to 42mA with a constant AC load of 600ohms.

2.2. SENDING IMPEDANCE. The impedance of the Output Stage Amplifier, Zout, is determined by the impedance Z4 at pin 3.

#### Zout = 10.65 x Z4.

The total AC impedance shown to the line is the parallel

Zpar = Zout//Zint//Zext

where :

- Zint = 10kohm // 8.5nF (internal)

- Zext = R6 // C4 (at pin 24)

2.3. SENDING MUTE. In normal speech operation (Vmute 0.8V), the signal at Microphone Input (pin 8) is amplified to Vline (pin 24) with the gains Gec (short line), Gel (long line) or intermediate, depending on lline.

In sending mute condition (Vmute 1.6V) these gains are reduced of at least 60 dB. In the same condition DTMF input (pin 7) is activated, with gain Gmf to the line independent from lline.

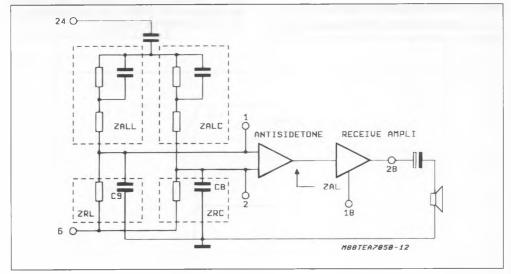

2.4. ANTISIDETONE BUFFER. The signal coming from the sending preamplifier is internally presented

at pin 5 and than buffered to pins 1 and 2 for sidetone cancellation (see paragraph 3.2.).

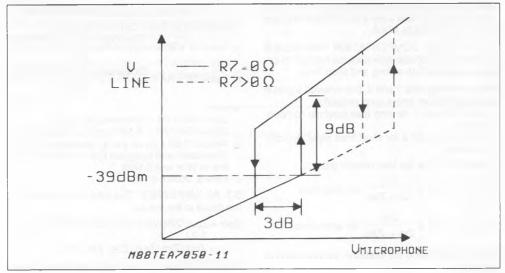

2.5. NOISE THRESHOLD (SQUELCH). The microphone signal is highly amplified (46dB) at pin 16, then peak detected and compared with an internal threshold at pin 14.

If the peak so detected does not exceed the internal threshold, the comparator reduces of about 9dB the sending gain Ge, acting at the preamplifier level.

In this way a strong attenuation is obtained, both of the speech noise (about 4dB) and of the ambient noise (9dB).

The equivalent thresholds on the line are :

- minus 39dBm to switch from squelch to normal gain,

- minus 32dBm to switch from normal gain to squelch,

with R8=150K $\Omega$  from pin 15 to gnd and C=3.3nF from pin 16 to 15.

These thresholds can be increased inserting also a resistor (R7) in series to C between pin 16 and 15.

The variation is given by the formula : (R8 + R7)/R8.

A hysteresis of about 3dB is defined to avoid continuous switch between squelch and normal gain.

## Figure 8.

#### 3. RECEIVE CHAIN

## Figure 9.

3.1. A.G.C. IN RECEIVE. As described for the transmission chain, also the receiving gains Gr, from pins 1 and 2 to pin 28, have a reduction of 6dB when Iline moves from 27mA to 42mA.

3.2. SIDETONE COMPENSATION. The circuit is provided with a double anti-sidetone network to optimize sidetone both at long and short lines.

Before entering pins 1 and 2, the received signal is attenuated by two attenuating networks :

- Zall / Zrl to pin 1 for long lines sidetone compensation,

- Zalc / Zrc to pin 2 for short lines sidetone compensation.

Zrl and Zrc define the total receive gains :

- a)  $\frac{V28}{V24} = Grl \times \frac{Zrl}{Zrl + Zall}$  for long lines

- b)  $\frac{V28}{V24} = \text{Grc} \times \frac{\text{Zrc}}{\text{Zrc} + \text{Zalc}}$  for short lines

Zall and Zalc define the sidetone compensation of the circuit.

The equivalent balancing impedance is given by the formula :

$Zal = K \times Zalc + (1 K) \times Zall$

where K = 0 at lline = 27mA or lower (long line)

K varies from 0 to 1 with Iline between 27mA

and 42mA,

K=1 at lline=42mA or higher (short line).

Calculations to define Zall and Zalc are :

a) Zall = 70 x R5 x Zline(long) // Zext // Zint // Zout

where :

- \_ Zext = R6 // C4 // (Zelectret) (at pin 24)

- Zint = 10Kohms // 8.5nF (internal impedance)

- Zout = 10.65 x Z4 (at pin 3 ; see paragr. 2.2.)

- Zline(short) and (long) are the impedances of the line at 0Km and 3.5Km.

- $R5 = 5.1 Kohm \pm 1\%$

3.3. AC IMPEDANCE. The total AC impedance of the circuit to the line is :

- Zpar = Zout//Zint//Zext//Zalc//Zall (see par. 2.2. and 3.2.)

- = Zout//Zint//Zext (Zalc, Zall Zpar)

3.4. RECEIVE MUTE (and confidence level). When the receive channel is muted (Vpin 18 2.7V) the receive gain is reduced of 60dB minimum.

In this condition an internal connection is activated from DTMF input (pin 7) to Receive Output (pin 28) with a gain Gmf = 31dB to provide acoustic feedback of the DTMF transmission.

#### 4. MICROPROCESSOR INTERFACE

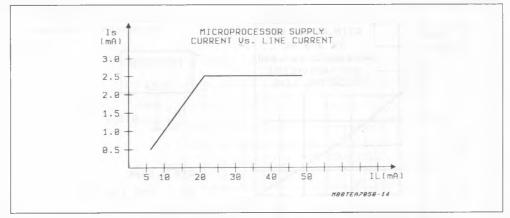

4.1. MICROPROCESSOR SUPPLY (PIN 27). At "offhook" the first priority of the circuit is to make some current available at the Microprocessor Supply (pin 27) to charge quickly the external capacitor C3.

This charging current is :  $lcpm = 0.7 \times (lline - ldem)$ , where ldem = 2.6mA is the current charging C1.

Vmp = 3.3V in normal operation and current increases linearly from 0.5mA min, at lline = 6mA, to 2.5mA min, at lline = 27mA, remaining stable for higher values of lline.

#### Figure 10.

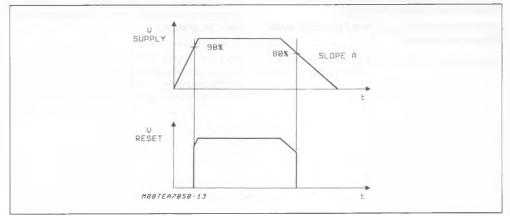

4.2. MICROPROCESSOR RESET (pin 20). The Microprocessor Reset becomes active when Vmp overcomes 85% of its nominal level. It becomes low when Vmp undergoes 84%.

Slope A is related to C3, limp (internal consumption) and to the external load (microprocessor or dialer).

Figure 11.

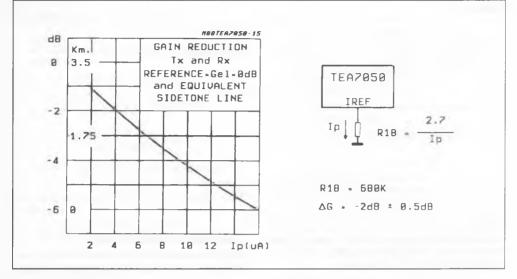

#### 5. PUBLIC / PRIVATE

5.1. A.G.C. OFF (PIN 10). An external resistor, R18, applied between pin 10 and ground disconnects the AGC control.

Sending, receiving gain and sidetone compensation

are now independent of the line length and the value of the current lp, flowing through R18, defines the length of the line for which sidetone is optimized (lp = 2.7V / R18).

#### Figure 12.

5.2. SECRET FUNCTION FOR PRIVATE (PINS 11 & 18). The two separate Mute pins allow "Secret Function" (only microphone muted).

As the two controls have different threshold levels, they can be operated :

a) separately through two different control logic,

b) connected in short circuit with a three levels logic  $(Vm = 0V \text{ speech mode}; Vm = 1.8V \text{ microph mute}; Vm = 3V all mute}).$

#### 6. POWER MANAGEMEN AND HANDS-FREE INTERFACE

6.1. POWER MANAGEMENT (PIN 12). Most of the DC current available from the line will be delivered by the speech circuit at the output Isource (pin 12) through an internal current generator.

Typical values of this current, lea, are :

- lea = (0.3 x lline) for lline < 22mA

- lea = (0.9 x Iline 13mA) for Iline > 22mA

- (ex : lline=16mA then lea=4.8mA lline=30mA then lea=14.0mA lline=60mA then lea=41.0m)

The voltage level at pin 12 must be defined by an external regulator (i.e. : zener) and, if necessary, filtered with a capacitor (47 to 220  $\mu$ F).

In case Vline (at pin 24) approaches V at pin 12, then the internal current source switches off and its DC current is shunt to ground through an internal complementary generator, thus avoiding any negative effect on the Ac and DC impedances of the telephone set application.

6.2. EXTRA RECEIVE OUTPUT (PIN 4). The Extra Receive Signal is active also in Receive Mute condition, so allowing the transit of the receive signal from the speech circuit to the Hands-Free system even when the earpiece is muted. The gain at this pin is 30dB lower than standard Receive Output (pin 28).