# **Signetics**

# TDA8400 FLL Tuning Circuit With Prescaler

**Product Specification**

#### **Linear Products**

### DESCRIPTION

The TDA8400 provides closed-loop digital tuning of TV receivers, with or without AFC, as required. It comprises a 1.1GHz prescaler, with the divide-by-64 ratio, which drives a tuning interface providing a tuning voltage of 33V (maximum) via an external output transistor. The TDA8400 can also drive external PNP transistors to provide 4 high-current outputs for tuner band selection.

The IC can be used in conjunction with a microcomputer from the MAB8400 family and is controlled via a two-wire, bidirectional I<sup>2</sup>C bus.

#### **FEATURES**

- Combined analog and digital circultry minimizes the number of additional interfacing components required

- Frequency measurement with resolution of 50kHz

- On-chip prescaler

- Tuning voltage amplifier

- 4 high-current outputs for direct band selection

- Tuning with control of speed

- Tuning with or without AFC

- Single-pin, 4MHz, on-chip oscillator

- I<sup>2</sup>C bus slave transceiver

### **APPLICATIONS**

- TV receivers

- Satellite receivers

- CATV converters

#### ORDERING INFORMATION

| DESCRIPTION                   | TEMPERATURE RANGE | ORDER CODE |

|-------------------------------|-------------------|------------|

| 18-Pin DIP (SOT - 102 HE, KE) | 0 to 70°C         | TDA8400N   |

# **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL                               | PARAMETER                               | RATING      | UNIT   |

|--------------------------------------|-----------------------------------------|-------------|--------|

| V <sub>CCS</sub><br>V <sub>CCP</sub> | Supply voltage:<br>(Pin 10)<br>(Pin 15) | 6<br>6      | V<br>V |

| V <sub>N</sub>                       | Input/output voltage (each pin)         | 6           | ٧      |

| P <sub>TOT</sub>                     | Total power dissipation                 | 350         | mW     |

| T <sub>STG</sub>                     | Storage temperature range               | -65 to +150 | °C     |

| TA                                   | Operating ambient temperature range     | -10 to +80  | °C     |

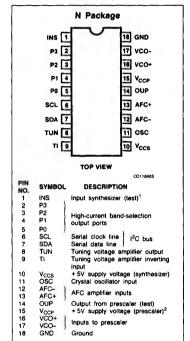

#### PIN CONFIGURATION

#### NOTES:

1. Connected to ground for application.

2. Left open-circuit for application.

**TDA8400**

# **BLOCK DIAGRAM**

**TDA8400**

# DC ELECTRICAL CHARACTERISTICS $T_A = 25$ °C; $V_{CCS}$ , $V_{CCP}$ at typical voltages, unless otherwise specified.

| OVMOOL                               | DADAMSTED                                                              |            | LIMITS    |                      |                |

|--------------------------------------|------------------------------------------------------------------------|------------|-----------|----------------------|----------------|

| SYMBOL                               | PARAMETER                                                              | Min        | Тур       | Max                  | UNIT           |

| V <sub>CCS</sub><br>V <sub>CCP</sub> | Supply voltage Synthesizer (Pin 10) Prescaler (Pin 15)                 | 4.5<br>4.5 | 5<br>5    | 5.5<br>5.5           | V<br>V         |

| Iccs<br>Iccp                         | Supply current Synthesizer (Pin 10) Prescaler (Pin 15)                 |            | 12<br>43  |                      | mA<br>mA       |

| Ртот                                 | Total power dissipation                                                |            | 275       |                      | mW             |

| T <sub>A</sub>                       | Operating ambient temperature range                                    | 0          |           | +70                  | °C             |

| T <sub>STG</sub>                     | Operating storage temperature range                                    | -10        |           | +85                  | °C             |

| I <sup>2</sup> C bus in              | puts/outputs Inputs: SDA (Pin 7); SCL (Pin 6)                          |            |           |                      |                |

| V <sub>IH</sub>                      | Input voltage HIGH                                                     | 3.1        |           | 5.5                  | ٧              |

| V <sub>IL</sub>                      | Input voltage LOW                                                      | -0.3       |           | 1.6                  | ٧              |

| I <sub>IH</sub>                      | Input current HIGH                                                     |            |           | 10                   | μΑ             |

| IIL                                  | Input current LOW                                                      |            |           | 10                   | μΑ             |

|                                      | SDA output (Pin 7, open-collector)                                     |            |           |                      |                |

| V <sub>OL</sub>                      | Output voltage LOW at I <sub>OL</sub> = 3mA                            |            |           | 0.4                  | V              |

| loL                                  | Output sink current                                                    |            |           | 5                    | mA             |

| Tuning vo                            | Itage amplifier Input TI, output TUN (Pins 9, 8)                       |            |           | 1                    |                |

| I <sub>TI</sub>                      | Input bias current                                                     | -5         |           | +5                   | nA             |

| -I <sub>TUNL</sub>                   | Output current LOW at V <sub>TUN</sub> = 0.4V                          | 20         |           |                      | μΑ             |

| CH₀<br>CH₁                           | Minimum charge IT to tuning amplifier  TUHN = 0  TUHN = 1              |            | 5<br>125  |                      | μΑ•μs<br>μΑ•μs |

| I <sub>TO</sub>                      | Maximum current I into tuning amplifier TUHN = 0 TUHN = 1              |            | 18<br>440 |                      | μΑ<br>μΑ       |

| AFC ampli                            | fler (Inputs AFC+, AFC- Pins 13, 12)                                   |            |           |                      |                |

| V <sub>DIF</sub>                     | Differential input voltage                                             |            |           | 1                    | ٧              |

| 91                                   | Transconductance at AFCS = 1                                           | 5          | 10        | 15                   | μA/V           |

| 90                                   | Transconductance at AFCS = 0                                           | 30         | 50        | 70                   | μA/V           |

| V <sub>CM</sub>                      | Common mode input voltage                                              | 2.5        |           | V <sub>CC1</sub> - 1 | V              |

| CMRR                                 | Common mode rejection ratio                                            |            | 50        |                      | dB             |

| PSRR                                 | Power supply (V <sub>CC1</sub> ) rejection ratio                       |            | 50        |                      | dB             |

| կ                                    | Input current                                                          |            |           | 1                    | μΑ             |

| Main band                            | I-selection output ports P0, P1, P2, P3 (Pins 5 to 2, open-collection) | ctor)      |           |                      |                |

| IBSL1                                | Output sink current<br>LOW impedance<br>HIGH impedance                 | 0.8        | 1         | 1.2<br>10            | mA<br>μA       |

**TDA8400**

## DC ELECTRICAL CHARACTERISTICS (Continued) TA = 25°C; VCCS, VCCP at typical voltages, unless otherwise specified.

|                     |                                                                             | LIMITS                 |     |                        |      |

|---------------------|-----------------------------------------------------------------------------|------------------------|-----|------------------------|------|

| SYMBOL              | PARAMETER Min Typ                                                           |                        | Тур | Max                    | UNIT |

| Prescaler I         | inputs (VCO+ Pin 16; VCO- Pin 17)                                           | ·!                     |     | <del></del>            | -    |

|                     | Input differential voltage (RMS value)                                      |                        |     |                        |      |

| V <sub>I(RMS)</sub> | at f = 70MHz                                                                | 17.5                   |     | 200                    | mV   |

| VI(RMS)             | at f = 150MHz                                                               | 10                     |     | 200                    | m۷   |

| V <sub>I(RMS)</sub> | at f = 300MHz                                                               | 10                     |     | 200                    | mV   |

| V <sub>I(RMS)</sub> | at f = 500MHz                                                               | 10                     |     | 200                    | mV   |

| VI(RMS)             | at f = 900MHz                                                               | 10                     |     | 200                    | mV   |

| VI(RMS)             | at f = 1.1GHz                                                               | 25                     |     | 200                    | mV   |

| f <sub>I</sub>      | Input frequency                                                             | 0.07                   |     | 1.1                    | GHz  |

| OSC Input           | (Pin 11)                                                                    |                        | -   | •                      |      |

| R <sub>XTAL</sub>   | Crystal resistance at resonance (4MHz)                                      |                        |     | 150                    | Ω    |

| Power-dow           | n reset                                                                     |                        |     | •                      |      |

| V <sub>PD</sub>     | Maximum supply voltage V <sub>CC1</sub> at which power-down reset is active |                        |     | 4                      | ٧    |

| Voltage le          | vei for valid module address                                                |                        |     | •                      |      |

| -                   | Voltage level P0 (Pin 5) for valid module address as a function of MA1, MA0 |                        |     |                        |      |

|                     | MA1 MA0                                                                     |                        |     | 1                      |      |

|                     | 0 0 pin used as an output                                                   |                        |     |                        |      |

| V <sub>VA01</sub>   | 0 1                                                                         | -0.3                   |     | 0.8                    | V    |

| V <sub>VA10</sub>   | 1 0                                                                         | 2.4                    |     | V <sub>CCS</sub> - 1.6 | v    |

| V <sub>VA11</sub>   |                                                                             | V <sub>CCS</sub> - 0.3 |     | Vccs                   | v    |

#### **FUNCTIONAL DESCRIPTION**

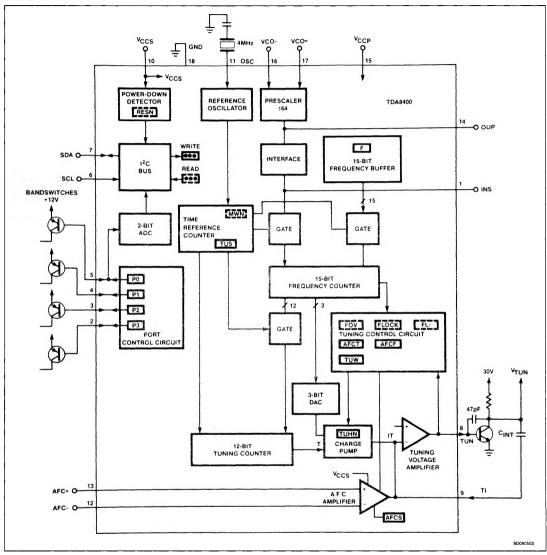

#### Prescaler

The integrated prescaler has a divide-by-64 ratio with a maximum input frequency of 1.1GHz. It will oscillate in the absence of an input signal within the frequency range of 800MHz to 1.1GHz.

### Tuning

This is performed using frequency-locked loop digital control. Data corresponding to the required tuner frequency is stored in the 15-bit frequency buffer. The actual tuner frequency (1.1GHz maximum) is applied to the circuit on the two complementary inputs VCO+ and VCO- which drive the integrated prescaler. The resulting frequency (FDIV) is measured over a period controlled by a time reference counter and fed via a gate to a 15-bit frequency counter where it is compared to the contents of the frequency buffer. The result of the comparison is used to control the tuning voltage so that the tuner frequency equals the contents of the frequency buffer multiplied by 50kHz within a programmable tuning window (TUW).

The system cycles over a period of 2.56ms, controlled by the time reference counter which is clocked by an on-chip 4MHz reference oscillator. Regulation of the tuning voltage is performed by a charge pump frequency-

locked loop system. The charge IT flowing into the tuning voltage amplifier (external capacitance  $C_{\rm INT}=0.5\mu{\rm F}$ ) is controlled by the tuning counter, 3-bit DAC, and the charge pump circuit. The charge IT is linear with the frequency deviation  $\Delta f$  in steps of 50kHz. For loop gain control, the relationship  $\Delta IT/\Delta f$  is programmable. In the normal mode (control bit TUHN = logic 1; see Table 2) the minimum charge IT at  $\Delta f=50{\rm kHz}$  equals  $125\mu{\rm A}\cdot\mu{\rm s}$  (typ.).

By programming the tuning sensitivity bits (TUS; see Table 3) the charge IT can be doubled up to 6 times. From this, the maximum charge IT at  $\Delta f = 50 \mathrm{kHz}$  equals  $2^6 \times 125 \mu A \mu s$  (typ.). The maximum tuning current I is  $440 \mu A$ , while T is limited to the duration of the tuning cycle (2.56ms).

In the tuning-hold mode (TUHN = logic 0) the tuning current I is reduced, and, as a consequence, the charge into the tuning amplifier is also reduced. An in-lock situation can be detected by reading FLOCK. The TDA8400 can be programmed to tune in the digital mode or the AFC mode by setting AFCF. In the digital mode (AFCF = logic 0), the tuning window is programmable through the TUW flag. When the tuner oscillator frequency is within the programmable tuning window (TUW), FLOCK is set to logic 1.

In the AFC mode, FLOCK will remain at logic 1 provided the tuner frequency is within a £ 900kHz hold range. Switching from digital mode to AFC mode is determined by the microcontroller (AFCF flag). Switching from AFC mode to digital mode can be determined by the microcontroller, but if the frequency of the tuning oscillator does not remain within the hold range, the system automatically reverts to digital tuning. Switching back to the AFC mode will then have to be effected externally again. The tuning mode can be checked by reading the AFCT flag.

The occurence of positive and negative transitions in the FLOCK signal can be read by FL/ 1N and FL/0N. The AFC amplifier has programmable transconductance to 2 predefined values.

#### Control

For tuner band selection there are four output ports, P0 to P3, which are capable of driving external PNP transistors (open collector) as current sources. Output port P0 can also be used as valid address input with an active level determined by module address bits MA0 and MA1.

### Reset

The TDA8400 goes into the power-down reset mode when V<sub>CC1</sub> is below 3V (typ.). In this mode all registers are set to a defined state.

TDA8400

### **OPERATION**

#### Write

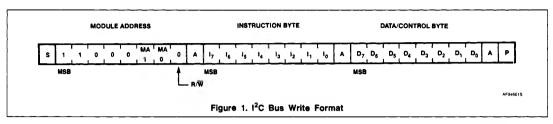

The TDA8400 is controlled via a bidirectional two-wire I<sup>2</sup>C bus; additional information on the I<sup>2</sup>C bus is available on request.

For programming, a module address,  $R/\overline{W}$  bit (logic 0), an instruction byte, and a data/control byte are written into the device in the format shown in Figure 1.

The module address bits MA1, MA0 are used to give a 2-bit module address as a function of the voltage at port input P0 as shown in Table 1.

Table 1. Valid Module Addresses

| P0                   | MA1 | MAO |

|----------------------|-----|-----|

| Don't care           | 0   | 0   |

| GND                  | 0   | 1   |

| 1/2 V <sub>CCS</sub> | 1   | 0   |

| V <sub>CCS</sub>     | 1   | 1   |

Acknowledge (A) is generated by the TDA8400 only when a valid address is received and the device is not in the power-down reset mode.

## **Tuning**

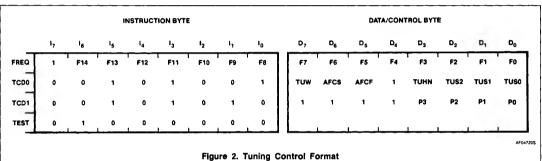

Tuning is controlled by the instruction and data/control bytes as shown in Figure 2.

## Frequency

Frequency is set when Bit I<sub>7</sub> of the instruction byte is set to logic 1; the remaining bits of this byte are processed as being data. Instruction bytes are fully decoded. All frequency bits are set to logic 1 and control bits to logic 0 at reset. The test instruction byte cannot be used for any other purpose.

Table 2. Tuning Current Control

| TUHN | TYP. I <sub>MAX</sub> (μA) | TYP. IT <sub>MIN</sub> (μΑ/μs) |

|------|----------------------------|--------------------------------|

| 0    | 18 <sup>1</sup>            | 5 <sup>1</sup>                 |

| 1    | 440                        | 125                            |

#### NOTE:

1. Values after reset.

#### **Tuning Hold**

The TUHN bit is used to decrease the maximum tuning current (I) and, as a consequence, the minimum charge IT (at  $\Delta f = 50 \text{kHz}$ ) into the tuning amplifier.

### **Tuning Sensitivity**

To be able to program an optimum loop gain, the charge IT can be programmed by changing T using tuning sensitivity (TUS). Table 3 shows the minimum charge IT obtained by programming the TUS bits at  $\Delta f = 50 \text{kHz}$ ; TUHN = logic 1.

Table 3. Minimum Charge IT as a Function of TUS

| TUS2 | TUS1 | TUS0 | TYP.<br>IT <sub>MIN</sub><br>(mA·µs) |

|------|------|------|--------------------------------------|

| 0    | 0    | 0    | 0.125                                |

| 0    | 0    | 1    | 0.25                                 |

| 0    | 1    | 0    | 0.5                                  |

| 0    | 1    | 1    | 1                                    |

| 1    | 0    | 0    | 2                                    |

| 1    | 0    | 1    | 4                                    |

| 1    | 1    | 0    | 8                                    |

#### NOTE:

The minimum tuning pulse is  $2\mu$ s.

**Tuning Mode**

AFCF determines whether the TDA8400 has to tune in the digital mode or the AFC mode as shown in Table 4.

Table 4. Selection of Tuning

Mode as a Function of

AFCF

| AFCF | TUNING MODE |  |

|------|-------------|--|

| 0    | Digital     |  |

| 1    | AFC         |  |

If the tuner oscillator frequency comes out of the hold range when in the AFC mode, the device will automatically switch to digital tuning and AFCF is reset to logic 0.

#### **Tuning Window**

In the digital tuning mode TUW determines the tuning window (see Table 5) and the device is said to be in the "in-lock" situation.

Table 5. Tuning Window Programming

|     | •                   |

|-----|---------------------|

| TUW | TUNING WINDOW (kHz) |

| 0   | 0                   |

| 1   | ± 200               |

**TDA8400**

#### Transconductance

The transconductance (g) of the AFC amplifier is programmed via the AFC sensitivity bit AFCS as shown in Table 6.

Table 6. Transconductance Programming

| AFCS | TYP. TRANSCONDUCTANCE (μΑ/V) |

|------|------------------------------|

| 1 0  | 10<br>50                     |

# **Band Selection Control Ports** (PX)

For band selection control, there are four output ports, PO to P3, which are capable of driving external PNP transistors (open collector) as current sources. If a logic 1 is programmed on any of the PX bits PO to P3, the

PNP transistor will conduct and the relevant output goes LOW. All outputs are HIGH after reset.

#### Read

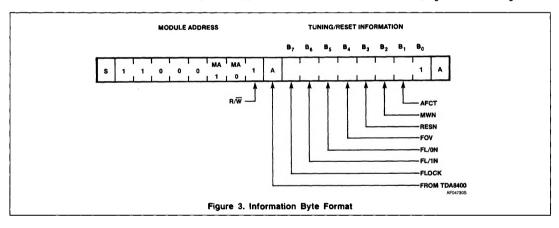

Information is read from the TDA8400 when the  $R/\overline{W}$  bit is set to logic 1. Only one information byte is sent from the device. No acknowledge is required from the master after transmitting. The format of the information byte is shown in Figure 3.

#### Tuning/Reset Information Bits

FLOCK — Set to logic 1 when the tuning oscillator frequency is within the programmed tuning window (TUW) in the digital tuning mode, or within the ± 800kHz AFC hold range in the AFC mode.

FL/1N — Set to logic 0 (Active-LOW) when FLOCK changes from 0 to 1 and is reset to logic 1 automatically after tuning information has been read.

FL/0N — Same as for FL/1N but it is set to logic 0 when FLOCK changes from 1 to 0.

FOV — Indicates frequency overflow. When the tuner oscillator frequency is too high with respect to the programmed frequency, FOV is at logic 1, and, when too low, FOV is at logic 0

RESN — Set to logic 0 (active Low) by a power-down reset. It is reset to logic 1 automatically after tuning/reset information has been read.

MWN — MWN (frequency measuring window, Active-LOW) is at logic 1 for a period of 1.28ms, during which time the results of frequency measurement are processed. During the remaining time, MWN is at logic 0 and the received frequency is measured.

AFCT — AFCT (tuning mode flag) is set to logic 1 when the TDA8400 is in AFC mode and reset to logic 0 when in the digital mode.