INTEGRATED CIRCUITS

Preliminary specification File under Integrated Circuits, IC02 September 1994

**Philips Semiconductors**

## **TDA8315T**

### FEATURES

- CVBS or Y/C input

- Integrated chrominance trap and bandpass filters (automatically calibrated)

- Integrated luminance delay line

- Alignment-free NTSC colour decoder

- Horizontal PLL with an alignment-free horizontal oscillator

- Vertical count-down circuit

- Low dissipation (320 mW)

- Small amount of peripheral components compared with competition ICs.

### **GENERAL DESCRIPTION**

The TDA8315T is an alignment-free NTSC decoder/sync processor. The device can be used for normal television applications and for Picture-in-Picture (PIP) applications.

The input signal can be either CVBS or Y/C and at the outputs the following signals are available:

- Luminance signal

- Colour difference signals (U and V)

- Horizontal and vertical synchronization pulses

- Back porch clamping pulse (burst-key pulse).

The supply voltage for the IC is 8 V. It is available in a 24-pin SO package.

### QUICK REFERENCE DATA

| SYMBOL               | PARAMETER                                       | MIN. | TYP. | MAX. | UNIT |

|----------------------|-------------------------------------------------|------|------|------|------|

| VP                   | supply voltage (pins 11 and 12)                 | 7.2  | 8.0  | 8.8  | V    |

| l <sub>P</sub>       | supply current                                  | -    | 40   | -    | mA   |

| Input voltages       |                                                 | 1    |      |      |      |

| V <sub>13(p-p)</sub> | CVBS/Y input voltage (peak-to-peak value)       | -    | 1    | -    | V    |

| V <sub>15(p-p)</sub> | chrominance input voltage (peak-to-peak value)  | -    | 0.3  | -    | V    |

| Output signals       |                                                 |      |      | •    |      |

| V <sub>O(b-w)</sub>  | luminance output voltage (blank-to-white value) | -    | 1.65 | _    | V    |

| V <sub>21(p-p)</sub> | -U output voltage (peak-to-peak value)          | -    | 1.5  | -    | V    |

| V <sub>20(p-p)</sub> | -V output voltage (peak-to-peak value)          | -    | 1.5  | -    | V    |

| V <sub>2</sub>       | horizontal sync pulse                           | -    | 4    | -    | V    |

| V <sub>7</sub>       | vertical sync pulse                             | -    | 4    | -    | V    |

| V <sub>10</sub>      | back porch clamping pulse                       | -    | 4    | -    | V    |

| Control voltages     |                                                 |      |      |      |      |

| V <sub>control</sub> | control voltages for Saturation and Hue         | 0    | _    | 5    | V    |

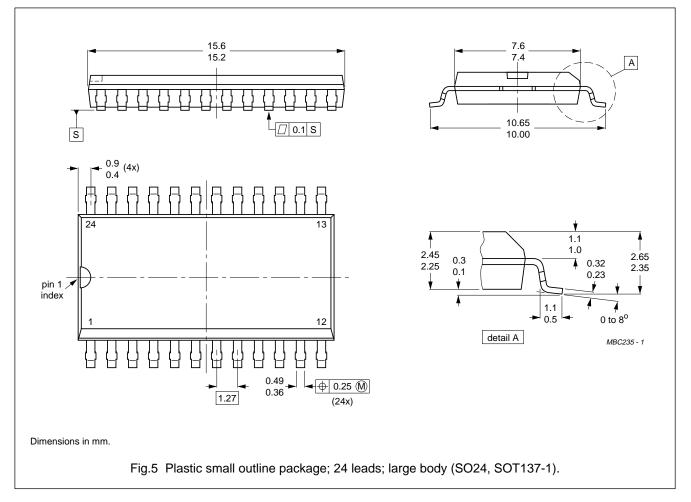

### ORDERING INFORMATION

|          | NAME | DESCRIPTION                                                     | VERSION |  |

|----------|------|-----------------------------------------------------------------|---------|--|

| TDA8315T | SO24 | plastic small outline package; 24 leads; body width 7.5 mm SOT1 |         |  |

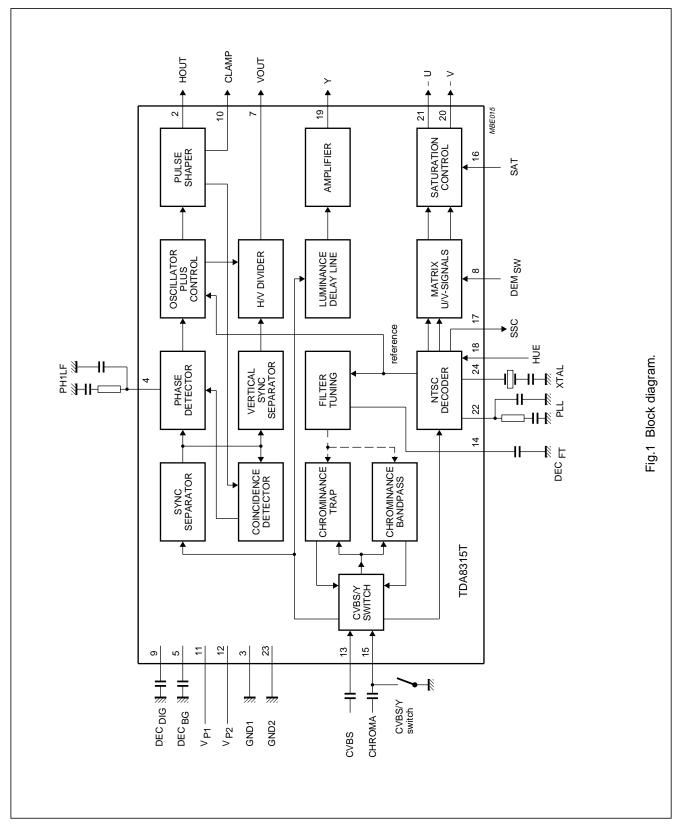

#### **BLOCK DIAGRAM**

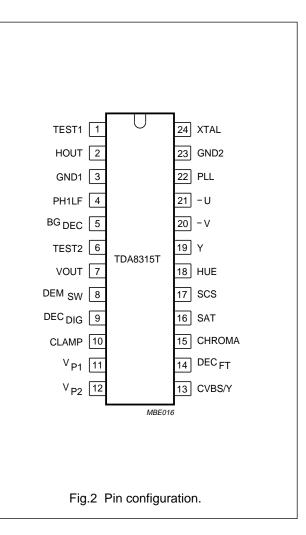

### PINNING

| SYMBOL               | PIN | DESCRIPTION                  |

|----------------------|-----|------------------------------|

| TEST1 <sup>(1)</sup> | 1   | test pin 1                   |

| HOUT                 | 2   | horizontal output pulse      |

| GND1                 | 3   | ground 1 (0 V)               |

| PH1LF                | 4   | phase 1 loop filter          |

| DEC <sub>BG</sub>    | 5   | bandgap decoupling           |

| TEST2 <sup>(1)</sup> | 6   | test pin 2                   |

| VOUT                 | 7   | vertical output pulse        |

| DEM <sub>SW</sub>    | 8   | demodulation angle switch    |

| DEC <sub>DIG</sub>   | 9   | decoupling digital supply    |

| CLAMP                | 10  | back porch clamping pulse    |

| V <sub>P1</sub>      | 11  | supply voltage 1 (+8 V)      |

| V <sub>P2</sub>      | 12  | supply voltage 2 (+8 V)      |

| CVBS/Y               | 13  | CVBS/Y input                 |

| DEC <sub>FT</sub>    | 14  | decoupling filter tuning     |

| CHROMA               | 15  | chrominance and switch input |

| SAT                  | 16  | saturation control input     |

| SCS                  | 17  | sub-carrier signal output    |

| HUE                  | 18  | hue control input            |

| Y                    | 19  | Y output                     |

| -V                   | 20  | -V output                    |

| _U                   | 21  | –U output                    |

| PLL                  | 22  | PLL colour filter            |

| GND2                 | 23  | ground 2 (0 V)               |

| XTAL                 | 24  | 3.58 MHz crystal connection  |

#### Note

1. In the application the test pins must be connected to ground.

### CVBS or Y/C input

The TDA8315T has a video input which can be switched to CVBS (with internal chrominance bandpass and trap filters) and to Y/C (without chrominance bandpass and trap filters). The switching between CVBS and Y/C is achieved by the DC level of the CHROMA input (pin 15).

### Integrated video filters

The circuit contains a chrominance bandpass and trap circuit. The filters are realised by gyrator circuits that are automatically tuned by comparing the tuning frequency with the crystal frequency of the decoder. The chrominance trap can be switched off by the DC level of the CHROMA input.

The luminance delay line is also realised by gyrator circuits.

### Colour decoder

The colour decoder contains an alignment-free crystal oscillator, a colour killer circuit and colour difference demodulators. The gain of the two colour difference signal demodulators is identical and the phase angle of the reference carrier signals is 90°. This phase shift is achieved internally. It is possible to switch the demodulator angle to 110° by an internal matrix circuit. The switching is obtained externally via pin 8.

#### Synchronization circuit

The sync separator is preceded by a voltage controlled amplifier which adjusts the sync pulse amplitude to a fixed level. The sync pulses are then fed to the slicing stage (separator) which operates at 50% of the amplitude.

The separated sync pulses are fed to the first phase detector and to the coincidence detector. The coincidence detector is used to detect whether the line oscillator is synchronized. The PLL has a very high static steepness, this ensures that the phase of the picture is independent of the line frequency. The line oscillator operates at twice the line frequency.

The oscillator network is internal. Because of the spread of internal components an automatic adjustment circuit has been added to the IC.

The circuit compares the oscillator frequency with that of the crystal oscillator in the colour decoder. This results in a free-running frequency which deviates less than 2% from the typical value.

The horizontal output pulse is derived from the horizontal oscillator via a pulse shaper. The pulse width of the output pulse is 5.4  $\mu$ s, the front edge of this pulse coincides with the front edge of the sync pulse at the input.

The vertical output pulse is generated by a count-down circuit. The pulse width is approximately  $380 \ \mu s$ . Both the horizontal and vertical pulses will always be available at the outputs even when no input signal is available.

## TDA8315T

## LIMITING VALUES

In accordance with the Absolute Maximum Rating System (IEC134).

| SYMBOL           | PARAMETER                              | MIN. | MAX. | UNIT |

|------------------|----------------------------------------|------|------|------|

| V <sub>P</sub>   | supply voltage                         | -    | 9.0  | V    |

| T <sub>stg</sub> | storage temperature                    | -25  | +150 | °C   |

| T <sub>amb</sub> | operating ambient temperature          | -25  | +70  | °C   |

| T <sub>sld</sub> | soldering temperature for 5 s          | -    | 260  | °C   |

| Tj               | maximum operating junction temperature | _    | 125  | °C   |

## THERMAL CHARACTERISTICS

| SYMBOL              | PARAMETER                                               | VALUE | UNIT |

|---------------------|---------------------------------------------------------|-------|------|

| R <sub>th j-a</sub> | thermal resistance from junction to ambient in free air | ≤65   | K/W  |

## CHARACTERISTICS

$V_P$  = 8 V;  $T_{amb}$  = 25 °C; unless otherwise specified.

| SYMBOL               | PARAMETER                                                          | CONDITIONS    | MIN. | TYP. | MAX. | UNIT |

|----------------------|--------------------------------------------------------------------|---------------|------|------|------|------|

| Supplies             |                                                                    | •             | •    | -    |      |      |

| VP                   | supply voltage (pins 11 and 12)                                    |               | 7.2  | 8.0  | 8.8  | V    |

| I <sub>P</sub>       | supply current (pins 11 and 12)                                    |               | -    | 40   | -    | mA   |

| P <sub>tot</sub>     | total power dissipation                                            |               | _    | 320  | _    | mW   |

| CVBS or Y/           | C input                                                            |               |      |      |      |      |

| CVBS/Y INP           | ut (pin 13)                                                        |               |      |      |      |      |

| V <sub>13(p-p)</sub> | CVBS/Y input voltage (peak-to-peak value)                          | notes 1 and 2 | -    | 1    | 1.4  | V    |

| I <sub>13</sub>      | CVBS/Y input current                                               |               | -    | 4    | -    | μA   |

| COMBINED C           | HROMINANCE AND SWITCH INPUT (PIN 15)                               | •             |      |      |      |      |

| V <sub>15(p-p)</sub> | chrominance input voltage<br>(peak-to-peak value)                  | notes 2 and 3 | _    | 0.3  | -    | V    |

| V <sub>15(p-p)</sub> | input signal amplitude before clipping occurs (peak-to-peak value) | note 2        | 1    | -    | -    | V    |

| RI                   | chrominance input resistance                                       |               | _    | 15   | -    | kΩ   |

| CI                   | chrominance input capacitance                                      | note 4        | -    | _    | 5    | pF   |

| V <sub>15</sub>      | DC input voltage for Y/C operation                                 |               | 3    | 4    | 5    | V    |

| V <sub>15</sub>      | DC input voltage for CVBS operation                                |               | -    | -    | 1    | V    |

| Chrominan            | ce filters and luminance delay line                                |               |      |      |      |      |

| CHROMINANC           | CE TRAP CIRCUIT                                                    |               |      |      |      |      |

| f <sub>trap</sub>    | trap frequency                                                     |               | -    | 3.58 | -    | MHz  |

| В                    | luminance signal bandwidth                                         | note 2        | -    | 2.7  | _    | MHz  |

| SR                   | colour subcarrier rejection                                        |               | 20   | _    | -    | dB   |

| SYMBOL                  | PARAMETER                                                            | CONDITIONS                          | MIN. | TYP. | MAX. | UNI  |

|-------------------------|----------------------------------------------------------------------|-------------------------------------|------|------|------|------|

| CHROMINAN               | CE BANDPASS CIRCUIT                                                  |                                     | -!   | -1   | -1   | -1   |

| f <sub>c</sub>          | centre frequency                                                     |                                     | _    | 3.58 | _    | MHz  |

| QBP                     | bandpass quality factor                                              |                                     | _    | 3    | _    |      |

| Y DELAY LINE            | · · · · · · · · · · · · · · · · · · ·                                |                                     |      |      |      |      |

| t <sub>d</sub>          | delay time                                                           | note 2                              | _    | 390  | _    | ns   |

| В                       | bandwidth of internal delay line                                     | note 2                              | 8    | _    | _    | MHz  |

| Y OUTPUT SI             | GNAL (PIN19)                                                         | -                                   | 1    | -1   | -1   |      |

| V <sub>19(p-p)</sub>    | output signal amplitude<br>(peak-to-peak value)                      | note 1                              | -    | 2.27 | -    | V    |

| Z <sub>O</sub>          | output impedance                                                     |                                     | _    | 350  | _    | Ω    |

| V <sub>19</sub>         | top sync level                                                       |                                     | -    | 2.85 | -    | V    |

| S/N                     | signal-to-noise ratio                                                | notes 2 and 5                       | -    | 56   | -    | dB   |

| Colour dec              | oder                                                                 |                                     |      | ł    | 1    |      |

| CHROMINAN               | CE AMPLIFIER                                                         |                                     |      |      |      |      |

| ACC <sub>cr</sub>       | ACC control range                                                    | note 6                              | 24   | _    | _    | dB   |

| ΔV                      | change in amplitude of the output signals over the ACC range         |                                     | -    | -    | 2    | dB   |

| THR <sub>on</sub>       | threshold colour killer ON                                           |                                     | tbf  | -31  | tbf  | dB   |

| HYSoff                  | hysteresis colour killer OFF                                         | note 2                              |      |      |      |      |

|                         | strong input signal                                                  | $S/N \ge 40 \text{ dB}$             | -    | +3   | _    | dB   |

|                         | noisy input signal                                                   |                                     | -    | +1   | -    | dB   |

| ACL CIRCUIT             | r                                                                    |                                     |      |      |      |      |

|                         | chrominance burst ratio at which the ACL starts to operate           |                                     | 2.3  | -    | 2.7  |      |

| REFERENCE               | PART                                                                 |                                     |      |      |      |      |

| Phase-locke             | ed loop; note 7 (filter connected to pin 22)                         |                                     |      |      |      |      |

| f <sub>CR</sub>         | catching range                                                       |                                     | 300  | 500  | -    | Hz   |

| Δφ                      | phase shift for a $\pm$ 400 Hz deviation of the oscillator frequency | note 7                              | -    | -    | 2    | deg  |

| Oscillator (p           | in 24)                                                               | -                                   | 1    | -1   | -1   |      |

| TC <sub>osc</sub>       | temperature coefficient of fosc                                      | note 2                              | -    | 2.0  | 2.5  | Hz/K |

| $\Delta f_{\text{osc}}$ | $f_{\text{osc}}$ deviation with respect to $V_{\text{P}}$            | note 2;<br>V <sub>P</sub> = 8 V±10% | -    | -    | 250  | Hz   |

| RI                      | input resistance                                                     | note 4                              | -    | 1.5  | -    | kΩ   |

| CI                      | input capacitance                                                    | note 4                              | -    | _    | 10   | pF   |

| HUE CONTRO              | dl input (pin 18)                                                    |                                     |      |      |      |      |

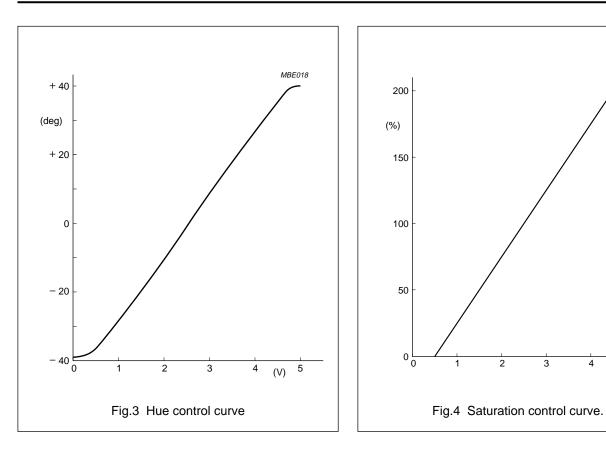

| HUE <sub>cr</sub>       | hue control range                                                    | see also Fig.3                      | ±35  | ±45  | -    | deg  |

| SATURATION              | CONTROL INPUT (PIN 16)                                               |                                     | •    | - •  |      |      |

| SAT <sub>cr</sub>       | saturation control range                                             | see also Fig.4                      | 52   | _    | _    | dB   |

|                         | -                                                                    | -                                   |      | -    |      | -    |

| SYMBOL                        | PARAMETER                                                             | CONDITIONS                          | MIN.               | TYP.      | MAX.      | UNIT       |

|-------------------------------|-----------------------------------------------------------------------|-------------------------------------|--------------------|-----------|-----------|------------|

| DEMODULATO                    | DR OUTPUTS (PINS 20 AND 21)                                           |                                     | 1                  | -         | -1        | -1         |

| В                             | bandwidth of demodulators                                             | –3 dB; note 8                       | _                  | 650       | -         | kHz        |

| $\Delta V_O / \Delta T$       | change of output signal amplitude with temperature                    | note 2                              | -                  | 0.1       | -         | %/K        |

| $\Delta V_{O} / \Delta V_{P}$ | change of output signal amplitude with supply voltage                 | note 2                              | -                  | -         | ±0.1      | dB         |

| G                             | gain ratio of demodulator G(–U)/G(–V)                                 |                                     | 0.9                | 1.0       | 1.1       |            |

|                               | demodulator angle<br>pin 8 LOW<br>pin 8 HIGH                          |                                     | 85<br>105          | 90<br>110 | 95<br>115 | deg<br>deg |

| V <sub>21(p-p)</sub>          | –U output signal amplitude at nominal saturation (peak-to-peak value) | note 9                              | -                  | 1.5       | -         | V          |

| V <sub>20(p-p)</sub>          | -V output signal amplitude at nominal saturation (peak-to-peak value) | note 9                              | -                  | 1.5       | -         | V          |

| Z <sub>O</sub>                | output impedance (–U)/(–V) output                                     |                                     | _                  | -         | 500       | Ω          |

| Vo                            | DC output voltage                                                     |                                     | _                  | 3         | -         | V          |

| Demodulati                    | ON ANGLE SWITCH INPUT (PIN 8)                                         | •                                   |                    | ŀ         |           | 1          |

| V <sub>8</sub>                | input voltage for 90° angle                                           |                                     | -                  | -         | 1         | V          |

| V <sub>8</sub>                | input voltage for 110° angle                                          |                                     | V <sub>P</sub> – 1 | -         | -         | V          |

| SUBCARRIER                    | OUTPUT SIGNAL (PIN 17)                                                |                                     | -                  |           |           | -          |

| V <sub>17(p-p)</sub>          | output signal amplitude<br>(peak-to-peak value)                       |                                     | -                  | 300       | -         | mV         |

| Z <sub>O</sub>                | output impedance                                                      |                                     | _                  | 250       | -         | Ω          |

| Vo                            | DC output voltage                                                     |                                     | _                  | 1.6       | -         | V          |

| Horizontal a                  | and vertical synchronization circuits                                 |                                     |                    |           |           |            |

| SYNC VIDEO                    | INPUT (PIN 13)                                                        |                                     |                    |           |           |            |

| V <sub>13</sub>               | sync pulse amplitude                                                  | note 4                              | 50                 | 300       | _         | mV         |

| SL                            | slicing level                                                         | note 10                             | _                  | 50        | _         | %          |

| VERTICAL SY                   | ÍNC                                                                   |                                     |                    |           |           |            |

| t <sub>W</sub>                | width of the vertical sync pulse without sync instability             | note 11                             | 22                 | -         | -         | μs         |

| HORIZONTAL                    | OSCILLATOR                                                            | 1                                   | 1                  | -1        | -1        | -1         |

| f <sub>fr</sub>               | free-running frequency                                                |                                     | _                  | 15734     | -         | Hz         |

| $\Delta f_{fr}$               | spread on free running frequency                                      |                                     | _                  | _         | ±2        | %          |

| $\Delta f_{osc} / \Delta V_P$ | frequency variation with respect to the supply voltage                | V <sub>P</sub> = 8 V±10%;<br>note 2 | -                  | 0.2       | 0.5       | %          |

| $\Delta f_{osc} / \Delta T$   | frequency variation with temperature                                  | note 2                              | _                  | _         | tbf       | Hz/K       |

| SYMBOL                 | PARAMETER                                                                                                                 | CONDITIONS            | MIN. | TYP. | MAX. | UNIT |

|------------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------|------|------|------|------|

| HORIZONTAL             | PLL; NOTE 12 (FILTER CONNECTED TO PIN 4)                                                                                  | 1                     | ļ    | ļ    | -1   | ļ    |

| f <sub>HR</sub>        | holding range PLL                                                                                                         |                       | -    | ±0.9 | ±1.2 | kHz  |

| f <sub>CR</sub>        | catching range PLL                                                                                                        | note 2                | ±0.6 | ±0.9 | _    | kHz  |

| S/N                    | signal-to-noise ratio of the video input<br>signal at which the time constant is<br>switched                              |                       | -    | 20   | -    | dB   |

| HYS                    | hysteresis at the switching point                                                                                         |                       | _    | 3    | _    | dB   |

| HORIZONTAL             | OUTPUT (PIN 2)                                                                                                            |                       |      |      |      |      |

| V <sub>OH</sub>        | HIGH level output voltage                                                                                                 | I <sub>O</sub> = 2 mA | 2.4  | 4.0  | _    | V    |

| V <sub>OL</sub>        | LOW level output voltage                                                                                                  | I <sub>O</sub> = 2 mA | _    | 0.3  | 0.6  | V    |

| I <sub>O(sink)</sub>   | output sink current                                                                                                       |                       | -    | -    | 2    | mA   |

| I <sub>O(source)</sub> | output source current                                                                                                     |                       | _    | -    | 2    | mA   |

| t <sub>W</sub>         | pulse width                                                                                                               | note 13               | -    | 5.4  | -    | μs   |

| t <sub>d</sub>         | delay time between positive edge of the<br>horizontal output pulse and start of the<br>horizontal sync pulse at the input |                       | -    | 0    | -    | μs   |

| BACK PORCH             | i clamping output (pin 10)                                                                                                |                       |      |      |      |      |

| V <sub>OH</sub>        | HIGH level output voltage                                                                                                 | I <sub>O</sub> = 2 mA | 2.4  | 4.0  | -    | V    |

| V <sub>OL</sub>        | LOW level output voltage                                                                                                  | I <sub>O</sub> = 2 mA | _    | 0.3  | 0.6  | V    |

| I <sub>O(sink)</sub>   | output sink current                                                                                                       |                       | -    | -    | 2    | mA   |

| I <sub>O(source)</sub> | output source current                                                                                                     |                       | -    | -    | 2    | mA   |

| t <sub>W</sub>         | pulse width                                                                                                               |                       | 3.2  | 3.4  | 3.6  | μs   |

| t <sub>d</sub>         | delay time between start of clamping pulse<br>and start of the start sync pulse                                           |                       | 5.2  | 5.4  | 5.6  | μs   |

| VERTICAL OU            | JTPUT (PIN 7); NOTE 14                                                                                                    | •                     |      | ·    |      |      |

| f <sub>fr</sub>        | free-running frequency                                                                                                    |                       | _    | 60   | _    | Hz   |

| f <sub>lock</sub>      | locking range                                                                                                             |                       | 54.6 | -    | 64.5 | Hz   |

|                        | divider value not locked                                                                                                  |                       | _    | 525  | _    |      |

|                        | locking range (lines/frame)                                                                                               |                       | 488  | _    | 576  |      |

| V <sub>OH</sub>        | HIGH level output voltage                                                                                                 | I <sub>O</sub> = 2 mA | 2.4  | 4.0  | -    | V    |

| V <sub>OL</sub>        | LOW level output voltage                                                                                                  | I <sub>O</sub> = 2 mA | -    | 0.3  | 0.6  | V    |

| I <sub>O(sink)</sub>   | output sink current                                                                                                       |                       | -    | -    | 2    | mA   |

| I <sub>O(source)</sub> | output source current                                                                                                     |                       |      | _    | 2    | mA   |

| t <sub>W</sub>         | pulse width (6 line periods)                                                                                              |                       | -    | 380  | _    | μs   |

| t <sub>d</sub>         | delay time between start of the vertical sync<br>pulse at the input and the positive edge of<br>the output pulse          |                       | -    | 37.5 | -    | μs   |

## TDA8315T

#### Notes to the characteristics

- 1. Signal with negative-going sync. Amplitude includes sync pulse amplitude.

- 2. This parameter is not tested during production and is guaranteed by the design and qualified by matrix batches which are made in the pilot production period.

- 3. Burst amplitude; for a colour bar with 75% saturation the chrominance signal amplitude is 660 mV (p-p).

- 4. This parameter is not tested during production and is just given as application information for the designer of the television receiver.

- 5. The signal-to-noise ratio is specified as a peak-to-peak signal with respect to RMS noise (bandwidth 5 MHz).

- 6. At a chrominance input voltage of 660 mV (p-p) (colour bar with 75% saturation i.e. burst signal amplitude 300 mV (p-p)) the dynamic range of the ACC is +6 and -18 dB.

- All frequency variations are referenced to 3.58 MHz carrier frequency. All oscillator specifications are measured with the Philips crystal series 9922 520. If the spurious response of the crystal is lower than –3 dB with respect to the fundamental frequency for a damping resistance of 1.5 kΩ, oscillation at the fundamental frequency is guaranteed.

The catching and detuning range are measured for nominal crystal parameters. These are:

- a) load resonance frequency  $f_0$  (C<sub>L</sub> = 20 pF) = 3.579545 MHz

- b) motional capacitance  $C_M = 14.5 \text{ fF}$

- c) parallel capacitance  $C_0 = 4.5 \text{ pF}$ .

The actual load capacitance in the application should be  $C_L = 18 \text{ pF}$  to account for parasitic capacitances on and off chip.

The free-running frequency of the oscillator can be checked by pulling the saturation control pin to the positive supply rail. In that condition the colour killer is not active so that the frequency offset is visible on the screen.

- 8. This value indicates the bandwidth of the complete chrominance circuit including the chrominance bandpass filter. The bandwidth of the demodulator low-pass filter is approximately 1 MHz.

- Output signal amplitude for a standard colour bar signal with 75% saturation and a demodulation angle of 90°. For a

demodulation angle of 110° the –V signal amplitude will decrease to 1.2 V (p-p) and the –U signal amplitude remains

unchanged. The nominal saturation is specified as maximum –6 dB.

- 10. Slicing level independent of sync pulse amplitude. The slicing level of the vertical sync separator is 70% (slicing level in direction of black level) during strong signal reception (no noise detected in the incoming signal) and 30% during weak signal reception.

- 11. The horizontal and vertical sync are stable while processing Copy Guard signals and signals with phase shifted sync pulses (stretched tapes). Trick mode conditions of the VCR will also not disturb the synchronization. The value given is the delay caused by the vertical sync pulse integrator. The integrator has been designed such that the vertical sync is not disturbed for special anti-copy tapes with vertical sync pulses with an on/off time of 10/22 μs.

- 12. To obtain a good performance for both weak signal and VCR playback the time constant of the first control loop is switched depending on the input signal condition. Therefore the circuit contains a noise detector and the time constant is switched to 'slow' when excessive noise is present in the signal. In the 'fast' mode during the vertical retrace time the phase detector current is increased 50% so that phase errors due to head-switching of the VCR are corrected as soon as possible.

To prevent the horizontal synchronization being disturbed by anti-copy guard signals such as Macrovision the phase detector is gated during the vertical retrace period so that pulses during scan have no effect on the output voltage. The width of the gate pulse is approximately 12  $\mu$ s. during weak signal conditions (noise detector active) the gating is active during the complete scan period and the width of the gate pulse is reduced to 5.7  $\mu$ s so that the effect of the noise is reduced to a minimum.

The output current of the phase detector in the two modes is shown in Table 1.

TDA8315T

- 13. The horizontal output pulses are obtained from the horizontal oscillator by a pulse shaper. The width of the output pulse is approximately 5.4 μs and the rising edge of the pulse symmetrically coincides with the start of the sync pulse at the input.

- 14. The vertical output pulses are generated by a divider circuit. The vertical output pulse has a delay of 37.5 μs with respect to the start of the vertical sync pulse at the input. This is caused by the clock frequency of the divider being twice the horizontal frequency.

This divider circuit has 2 modes of operation:

Search mode (large window).

This mode is switched on when the circuit is not synchronized or, when a non-standard signal is received (the number of lines per frame outside the range is between 261 and 264). In the search mode the divider can be triggered between line 244 and line 288 (approximately 54 to 64.5 Hz).

Standard mode (narrow window).

This mode is switched on when more than 15 successive vertical sync pulses are detected in the narrow window. When the circuit is in the standard mode and a vertical sync pulse is missing the output pulse is generated at the end of the window. Consequently, the disturbance of the picture is very small. The circuit will switch back to the search window when, for 6 successive vertical periods, no sync pulses are found within the window. When no input signal is available the divider generates output pulses with a timing of 262.5 lines (standard 60 Hz signal).

Table 1

Output current of phase detector.

| CURRENT PHASE DETECTOR DURING  | <b>SCAN (μA)</b> | VERTICAL RETRACE (µA) | GATED YES/NO               |

|--------------------------------|------------------|-----------------------|----------------------------|

| Weak signal and synchronized   | 30               | 30                    | YES (5.7 μs)               |

| Strong signal and synchronized | 180              | 270                   | YES (12 μs) <sup>(1)</sup> |

| Not synchronized               | 180              | 270                   | NO                         |

#### Note

1. Vertical retrace.

## QUALITY SPECIFICATION

Quality level in accordance with SNW-FQ-611-part E.

| SYMBOL | PARAMETER                                 | RANGE A <sup>(2)</sup> | RANGE B <sup>(3)</sup> | UNIT |

|--------|-------------------------------------------|------------------------|------------------------|------|

| ESD    | protection circuit specification (note 1) | >2000                  | >200                   | V    |

|        |                                           | 100                    | 200                    | pF   |

|        |                                           | 1500                   | 0                      | Ω    |

#### Notes

- 1. All pins are protected against ESD by means of internal clamping diodes.

- 2. Range A is for Human body model.

- 3. Range B is for machine model.

## Latch up

All pins meet the specification:

$I_{trigger} \geq 100 \text{ mA or} \geq 1.5 \text{ V}_{DDmax}$

$I_{trigger} \leq -100 \text{ mA or} \leq -0.5 \text{ V}_{DDmax}.$

## TDA8315T

MBE017

5

(V)

## TDA8315T

## PACKAGE OUTLINE

### SOLDERING

#### Plastic small-outline packages

BY WAVE

During placement and before soldering, the component must be fixed with a droplet of adhesive. After curing the adhesive, the component can be soldered. The adhesive can be applied by screen printing, pin transfer or syringe dispensing.

Maximum permissible solder temperature is 260  $^{\circ}$ C, and maximum duration of package immersion in solder bath is 10 s, if allowed to cool to less than 150  $^{\circ}$ C within 6 s. Typical dwell time is 4 s at 250  $^{\circ}$ C.

A modified wave soldering technique is recommended using two solder waves (dual-wave), in which a turbulent wave with high upward pressure is followed by a smooth laminar wave. Using a mildly-activated flux eliminates the need for removal of corrosive residues in most applications.

#### BY SOLDER PASTE REFLOW

Reflow soldering requires the solder paste (a suspension of fine solder particles, flux and binding agent) to be applied to the substrate by screen printing, stencilling or pressure-syringe dispensing before device placement.

Several techniques exist for reflowing; for example, thermal conduction by heated belt, infrared, and vapour-phase reflow. Dwell times vary between 50 and 300 s according to method. Typical reflow temperatures range from 215 to 250 °C.

Preheating is necessary to dry the paste and evaporate the binding agent. Preheating duration: 45 min at 45 °C.

REPAIRING SOLDERED JOINTS (BY HAND-HELD SOLDERING IRON OR PULSE-HEATED SOLDER TOOL)

Fix the component by first soldering two, diagonally opposite, end pins. Apply the heating tool to the flat part of the pin only. Contact time must be limited to 10 s at up to  $300 \,^{\circ}$ C. When using proper tools, all other pins can be soldered in one operation within 2 to 5 s at between 270 and 320  $^{\circ}$ C. (Pulse-heated soldering is not recommended for SO packages.)

For pulse-heated solder tool (resistance) soldering of VSO packages, solder is applied to the substrate by dipping or by an extra thick tin/lead plating before package placement.

## TDA8315T

### DEFINITIONS

| Data sheet status                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                       |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|

| Objective specification                                                                                                                                                                                                                                                                                                                                                                                                                                   | This data sheet contains target or goal specifications for product development.       |  |  |  |  |

| Preliminary specification                                                                                                                                                                                                                                                                                                                                                                                                                                 | This data sheet contains preliminary data; supplementary data may be published later. |  |  |  |  |

| Product specification This data sheet contains final product specifications.                                                                                                                                                                                                                                                                                                                                                                              |                                                                                       |  |  |  |  |

| Limiting values                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                       |  |  |  |  |

| Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability. |                                                                                       |  |  |  |  |

| Application information                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                       |  |  |  |  |

Where application information is given, it is advisory and does not form part of the specification.

### LIFE SUPPORT APPLICATIONS

These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips for any damages resulting from such improper use or sale.