#### **FEATURES**

- Customer programmable LSI

- 330 to 1100 gate complexity

- Mature silicon gate technology with local oxidation

- Library of 60 pre-designed, fully characterized macrocells available

- Full CAD, including auto-place and auto-route, for quick error-free design

- Very low power consumption (e.g. standby power for SCC 0700 is 0.25mW)

- Excellent noise immunity

- Power supply range 3 to 15V

- Over 80% utilization typical

- Fully programmable I/O pins, each having a wide range of functions

- Input protection by series resistor and diode clamp to  $V_{\mbox{\scriptsize SS}}$

- TTL outputs (buffers) drive up to four LSTTL loads

- -55°C to + 125°C operating temperature

- Plastic and ceramic DIP, ceramic leadless chip carriers, and plastic leaded chip carriers available

### **PRODUCT DESCRIPTION**

The SCCXXXX gate array family offers the circuit designer the facility to create a semi-custom circuit with a unique set of CAD (Computer-Aided Design) tools in a well-established CMOS process.

Signetics M-Series CMOS Gate Arrays are single chip programmable devices that allow customization of user logic. Only metalization and contact are programmed in these mature CMOS devices. Thus, fast turnaround from logic to completed silicon is achieved.

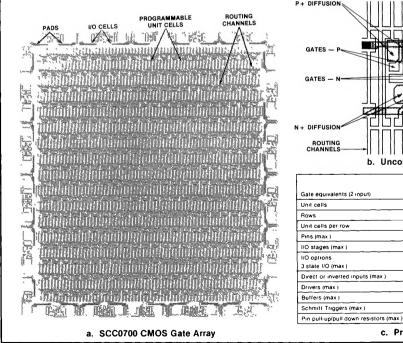

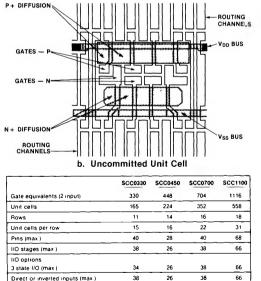

Each device in this family of low power gate arrays contains numerous identical, uncommitted unit cells (Figure 1) which are interconnected by two custom masks (metal and contact). Each unit cell contains four pairs of N and P transistors. Access to the transistors is from both the top and bottom of the cells and, additionally, there are two poly feed-throughs at each side of the cell. This homogenous cell design allows for excellent routing flexibility, and many designs result in better than 80% utilization of the gates available.

The M-Series Gate Arrays are built on a mature, state-of-theart 4-micron Si-gate CMOS process incorporating an episubstrate, which significantly reduces the potential for latch as compared with other bulk CMOS processes.

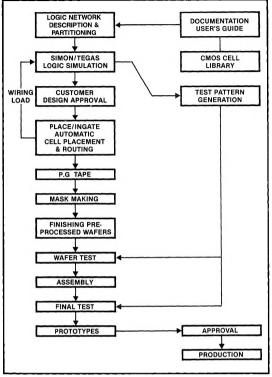

Computer Aided Design (CAD) is used throughout the design process to ensure accurate implementation of customer logic (see Figure 14 for typical process flow).

#### **ORDERING INFORMATION**

Contact Local Sales Representative

38

34

34

34

c. Product Matrix

14

12

8

26

22

16

10

34

66

66

66

66

Figure 1. Internal Configuration and Functional Characteristics of M-Series CMOS Gate Arrays

### ABSOLUTE MAXIMUM RATINGS Limiting values in accordance with the Absolute Maximum System (IEC 134)

| Supply voltage range                                                                                                                                                                        | V <sub>DD</sub>                      | – 0.5 to + 18V                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------------------------------|

| Voltage on any input when pin pull up/down resistors are:<br>Used<br>Not used                                                                                                               | v,<br>v,                             | – 0.5 to V <sub>DD</sub> + 0.5V<br>– 0.5 to + 18V |

| DC current into any input or output                                                                                                                                                         | ±1                                   | Max. 10mA                                         |

| Power dissipation per output                                                                                                                                                                | Ρ                                    | Max. 100mW                                        |

| Power dissipation per package<br>For standard temperature range: -40°C to +85°C (plastic and ceramic DIP)<br>For T <sub>amb</sub> = -40°C to +60°C<br>For T <sub>amb</sub> = +60°C to +85°C | P <sub>tot</sub><br>P <sub>tot</sub> | Max 400mW<br>Derate linearly by 8mW/K to 200mW    |

| For extended temperature range: $-55$ °C to $+125$ °C (ceramic DIP)<br>For T <sub>amb</sub> = $-55$ °C to $+100$ °C<br>For T <sub>amb</sub> = $+100$ °C to $+125$ °C                        | P <sub>tot</sub><br>P <sub>tot</sub> | Max. 400mW<br>Derate linearly by 8mW/K to 200mW   |

| Storage temperature range                                                                                                                                                                   | T <sub>sta</sub>                     | - 65 °C to + 150 °C                               |

### DC ELECTRICAL CHARACTERISTICS $V_{SS} = 0V$ , for all devices unless otherwise specified

|                 |                        |                                                    | TEMPERATURE RANGE <sup>1</sup> |                                                                      |                    |      |                    |        |                         |      |                  |

|-----------------|------------------------|----------------------------------------------------|--------------------------------|----------------------------------------------------------------------|--------------------|------|--------------------|--------|-------------------------|------|------------------|

| A N             | SYMBOL<br>D PARAMETER  | OPERATING<br>TEMP (T <sub>amb</sub> ) <sup>1</sup> | SUPPLY                         | TEST<br>CONDITIONS                                                   | T <sub>amb</sub> = | LOW  | T <sub>amb</sub> = | = 25°C | T <sub>amb</sub> = HIGH |      |                  |

| AND PARAMETER   |                        | (lamb)                                             | VOLIAGE                        | CONDITIONS                                                           | MIN                | MAX  | MIN                | MAX    | MIN                     | MAX  |                  |

|                 |                        |                                                    | 5                              |                                                                      | _                  | 50   | _                  | 50     | -                       | 375  |                  |

|                 |                        | Standard                                           | 10                             |                                                                      | —                  | 100  | —                  | 100    | -                       | 750  |                  |

| I <sub>DD</sub> | Quiescent              |                                                    | 15                             | All valid input                                                      | _                  | 200  | -                  | 200    | _                       | 1500 |                  |

|                 | device current         |                                                    | 5                              | combinations,<br>V <sub>1</sub> = V <sub>SS</sub> or V <sub>DD</sub> | —                  | 15   | -                  | 15     | —                       | 375  | μΑ               |

|                 |                        | Extended                                           | 10                             | 1 33 00                                                              | -                  | 25   | 1                  | 25     | —                       | 750  |                  |

|                 |                        |                                                    | 15                             |                                                                      | _                  | 50   |                    | 50     | -                       | 1500 |                  |

|                 |                        |                                                    | 5                              |                                                                      | —                  | 0 05 | -                  | 0 05   | —                       | 0 05 |                  |

| VOL             | Output<br>voltage Low  |                                                    | 10                             |                                                                      | -                  | 0 05 | —                  | 0 05   | -                       | 0 05 |                  |

|                 | vollage Low            | Both standard<br>and extended<br>ranges            | 15                             | $V_1 = V_{SS} \text{ or } V_{DD},$<br>$I_0 < 1.0 \mu A$              | -                  | 0 05 | _                  | 0 05   | —                       | 0 05 |                  |

|                 |                        |                                                    | 5                              |                                                                      | 4 95               | -    | 4 95               | —      | 4 95                    | —    |                  |

| V <sub>он</sub> | Output<br>voltage High |                                                    | 10                             |                                                                      | 9 95               | 1    | 9 95               | _      | 9 95                    | -    |                  |

|                 | voltage High           |                                                    | 15                             |                                                                      | 14 95              | -    | 14 95              | —      | 14 95                   | -    |                  |

| VII             | Input                  |                                                    | 5                              | V <sub>O</sub> =0.5V or 4.5V;                                        | -                  | 15   | -                  | 15     | —                       | 15   | ]                |

| ۹IL             | voltage Low            |                                                    | 10                             | $I_0 < 10 \mu A$                                                     |                    | 30   | -                  | 3.0    | -                       | 30   |                  |

|                 | INPI/INPB              | Both standard<br>and extended                      | 15                             | V <sub>O</sub> = 1 0V or 9 0V,                                       | -                  | 4.0  | —                  | 40     |                         | 4 0  | ] v              |

| VIH             | Input                  | ranges                                             | 5                              | Ι <sub>Ο</sub> < 10μΑ                                                | 35                 | -    | 35                 | -      | 35                      | -    |                  |

| . 14            | voltage High:          |                                                    | 10                             | V <sub>O</sub> = 1 5V or 13.5V,                                      | 70                 | -    | 70                 | —      | 70                      | 1    | ]                |

|                 | INPI/INPB              |                                                    | 15                             | Ι <sub>Ο</sub> < 1.0μΑ                                               | 11 0               | -    | 11 0               | —      | 11 0                    | -    |                  |

| V <sub>11</sub> | Input                  |                                                    | 5                              | V <sub>O</sub> = 0 5V or 4 5V,                                       | —                  | 10   | -                  | 10     | -                       | 10   |                  |

|                 | voltage Low            |                                                    | 10                             | Ι <sub>Ο</sub> < 1.0 μΑ                                              |                    | 20   | —                  | 2 0    | -                       | 20   | $\left. \right $ |

| _               | INPA, INPD, INPS       | Both standard<br>and extended                      | 15                             | V <sub>O</sub> = 1 0V or 9.0V,                                       | _                  | 2.5  | —                  | 2 5    | -                       | 2 5  |                  |

| ViH             | Input voltage          | ranges                                             | 5                              | l <sub>0</sub> < 10μA                                                | 4.0                | —    | 40                 | —      | 40                      | -    |                  |

| 1               | High: INPA,            |                                                    | 10                             | V <sub>O</sub> = 1 5V or 13 5V;                                      | 80                 | -    | 80                 | -      | 80                      | _    |                  |

|                 | INPD, INPS             |                                                    | 15                             | l <sub>O</sub> < 1 0μA                                               | 12 5               | Ű.   | 12 5               | -      | 12.5                    | -    |                  |

### DC ELECTRICAL CHARACTERISTICS (Continued) V<sub>SS</sub> = 0V; for all devices unless otherwise specified.

|                   | SYMBOL                        | OPERATING SUPPLY TEST                 |         |                                             | TEMPERATURE RANGE <sup>1</sup> |     |                    |                   |                    |        |      |

|-------------------|-------------------------------|---------------------------------------|---------|---------------------------------------------|--------------------------------|-----|--------------------|-------------------|--------------------|--------|------|

| AN                | D PARAMETER                   | TEMP (T <sub>amb</sub> ) <sup>1</sup> | VOLTAGE | CONDITIONS                                  | T <sub>amb</sub> =             | LOW | T <sub>amb</sub> = | =25°C             | T <sub>amb</sub> = | = HIGH |      |

|                   |                               |                                       |         |                                             | MIN                            | MAX | MIN                | MAX               | MIN                | MAX    |      |

|                   |                               |                                       | 5       |                                             | 1.1                            | -   | 0.9                | —                 | 0.7                | -      |      |

|                   |                               | Standard                              | 10      |                                             | 4.0                            | - 1 | 3.3                | -                 | 2.6                | -      | ]    |

|                   | Output (sink)                 |                                       | 15      |                                             | 12.0                           | _   | 10.0               | -                 | 8.0                | _      | 1    |

|                   | current Low<br>driver outputs |                                       | 5       | $V_1 = 0V$ or 5V;                           | 1.2                            | -   | 0.9                | _                 | 0.6                | -      | 1    |

|                   | •                             | Extended                              | 10      | $V_0 = 0.4V$                                | 4.2                            | -   | 3.3                | -                 | 2.2                | -      | 1    |

|                   |                               |                                       | 15      | V <sub>1</sub> = 0V or 10V;                 | 13.0                           | -   | 10.0               | _                 | 6.7                | _      |      |

| -                 |                               |                                       | 5       | V <sub>O</sub> = 0.5V                       | 2.2                            | -   | 1.8                | —                 | 1.4                | -      | ]    |

|                   |                               | Standard                              | 10      | V <sub>I</sub> = 0V or 15V;                 | 8.0                            | -   | 6.6                | -                 | 5.6                | -      | ]    |

|                   | Output (sink)                 |                                       | 15      | V <sub>O</sub> = 1.5V                       | 24.0                           | _   | 20.0               | _                 | 16.0               | _      | ]    |

|                   | current Low<br>buffer outputs |                                       | 5       |                                             | 2.4                            | -   | 1.8                | -                 | 1.2                | _      | mA   |

|                   |                               | Extended                              | 10      |                                             | 8.4                            | -   | 6.6                | -                 | 4.4                | -      | ]    |

|                   |                               |                                       | 15      |                                             | 26.0                           | -   | 20.0               | —                 | 13.4               | -      | 1    |

|                   |                               |                                       | 5       | $V_i = 0V \text{ or } 5V;$                  | 1.1                            | -   | 0.9                | _                 | 0.7                | -      |      |

|                   |                               | Standard                              | 10      | $V_0 = 4.6V$<br>$V_1 = 0V \text{ or } 10V;$ | 3.1                            | _   | 2.6                | _                 | 2.0                | _      |      |

| –I <sub>ОН</sub>  | Output                        |                                       | 15      |                                             | 12.0                           | -   | 10.0               | _                 | 8.0                | -      |      |

|                   | (source)<br>current High      | Extended                              | 5       | V <sub>O</sub> = 9.5V                       | 1.2                            | -   | 0.9                | _                 | 0.6                | _      |      |

|                   | ourion riigh                  |                                       | 10      | V <sub>1</sub> =0V or 15V;                  | 3.5                            |     | 2.6                |                   | 1.7                |        |      |

|                   |                               |                                       | 15      | V <sub>O</sub> = 13.5V                      | 13.0                           | -   | 10.0               | —                 | 6.7                | _      |      |

|                   |                               | Standard                              | 10      | V <sub>I</sub> = 0V or 10V                  | _                              | 0.3 | _                  | 0.3               | _                  | 1.0    |      |

| ±μΝ               | Input                         |                                       | 15      |                                             | _                              | 0.3 | -                  | 0.3               | -                  | 1.0    |      |

|                   | leakage<br>current            | Extended                              | 10      | V <sub>1</sub> =0V or 15V                   | _                              | 0.1 | —                  | 0.1               | —                  | 1.0    |      |

|                   |                               | Externada                             | 15      | vi=0v 0i 15v                                | _                              | 0.1 | -                  | 0.1               | —                  | 1.0    |      |

| I <sub>OZH</sub>  | Three-state                   | Standard                              | 10      |                                             | _                              | 1.6 | 1                  | 1.6               | -                  | 12.0   |      |

|                   | output and<br>open N-channel  | Standard                              | 15      | Output returned                             | _                              | 1.6 | 1                  | 1.6               | —                  | 12.0   | ]    |

|                   | output leakage                |                                       | 10      | to V <sub>DD</sub>                          | —                              | 0.4 | -                  | 0.4               | —                  | 5.0    | - µA |

|                   | current High                  | Extended                              | 15      |                                             | —                              | 0.4 | -                  | 0.4               | —                  | 5.0    |      |

| -l <sub>ozl</sub> |                               | Standard                              | 10      |                                             | _                              | 1.6 | -                  | 1.6               | —                  | 12.0   |      |

|                   | output and<br>open P-channel  | Standard                              | 15      | Output returned                             | _                              | 1.6 | -                  | 1.6               | _                  | 12.0   |      |

|                   | output leakage                | Extended                              | 10      | to V <sub>SS</sub>                          | _                              | 0.4 | _                  | 0.4               | —                  | 5.0    |      |

|                   | current Low                   | Extended                              | 15      |                                             | -                              | 0.4 | -                  | 0.4               | —                  | 5.0    |      |

| V <sub>TH</sub>   | Upper                         |                                       | 5       |                                             |                                | -   | 3.4                |                   |                    | _      |      |

|                   | threshold                     |                                       | 10      |                                             | _                              | -   |                    | Typical<br>values | _                  | —      |      |

|                   | voltage                       | Standard                              | 15      | Internal Schmitt                            | _                              | -   | 10.2               |                   | —                  | —      |      |

| VTL               | V <sub>TL</sub> Lower         | Giangang                              | 5       | trigger                                     | _                              | -   | 2.2                |                   | _                  | -      |      |

|                   | threshold                     |                                       | 10      |                                             | -                              | -   |                    | Typical<br>values | _                  | —      | ] v  |

|                   | voltage                       |                                       | 15      |                                             | _                              | -   | 3.8                |                   | _                  | —      |      |

| V <sub>H</sub>    | Hysteresis                    |                                       | 5       |                                             | _                              | -   | 0.2                |                   | -                  | -      | ]    |

| ·H                | voltage                       | -                                     | 10      | -                                           | _                              | -   |                    | Typical<br>values | _                  | -      | 1    |

|                   | input: INPS                   |                                       | 15      |                                             | -                              | -   | 0.8)               |                   | _                  | _      | 1    |

NOTES.

1

Tamb Low - 40°C for standard temperature range

Tamb High + 85°C for standard temperature range

-55°C for extended temperature range

+ 125°C for extended temperature range

2. Pin-connected pull-up and pull-down resistors are typically 7 to 78 K-ohms - see PERIPHERY

3. When pull-up or pull-down resistors are used, current limits for IpD must be extrapolated

#### **DC CHARACTERISTICS (Continued)**

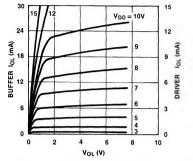

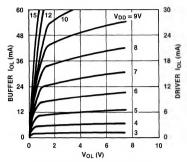

Figure 2. Minimum Output Current LOW as a Function of the Output Voltage LOW; Buffer and Driver Outputs

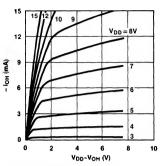

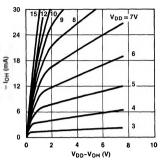

Figure 3. Minimum Output Current HIGH as a Function of the Supply Voltage Minus the Output Voltage HIGH

| AC ELECTRICAL | CHARACTERISTICS | $V_{SS} = 0V; T_{amb} = 25^{\circ}C$ |

|---------------|-----------------|--------------------------------------|

|               |                 |                                      |

|                  | SYMBOL AND<br>PARAMETER                           | PWR<br>SUP (V <sub>DD</sub> ) | MIN     | ТҮР      | мах       | UNIT       |                  | SYMBOL AND PARAMETER                   | PWR<br>SUP (V <sub>DD</sub> )          | MiN          | ТҮР                | MAX | UNIT |

|------------------|---------------------------------------------------|-------------------------------|---------|----------|-----------|------------|------------------|----------------------------------------|----------------------------------------|--------------|--------------------|-----|------|

| f <sub>max</sub> | Maximum toggle frequency<br>flip-flop GT00        | 5<br>10                       | 6<br>12 | 12<br>24 | -         | MHz<br>MHz | OUTF<br>Inpu     | PUT STAGE TRANSI<br>transition ≤ 20ns, | TION TIMES<br>C <sub>L</sub> = 50pF; V | ;<br>55 = 0' | V, T <sub>am</sub> |     | C    |

|                  | (no set/reset)                                    | 15                            | 15      | 30       | -         | MHz        |                  |                                        | 5                                      |              | 60                 | 120 | ns   |

|                  |                                                   |                               |         |          |           |            | t <sub>THL</sub> | Driver outputs                         | 10                                     |              | 30                 | 60  | ns   |

| f <sub>s</sub>   | Maximum system frequency<br>(may depend on number | 5<br>10                       | 3       | 6<br>12  | 4         | MHz<br>MHz |                  | High-to-Low                            | 15                                     |              | 20                 | 40  | ns   |

|                  | of gates in sequence)                             | 15                            | 9       | 18       | -         | MHz        |                  | Buffer outputs                         | 5                                      |              | 30                 | 60  | ns   |

|                  |                                                   |                               |         | <u> </u> |           |            | t <sub>THL</sub> | High-to-Low                            | 10                                     |              | 15                 | 30  | ns   |

| tp               | Propagation delays<br>for 2-input NAND gate       | 5<br>10                       | 1       | 8        | 16<br>6.4 | ns<br>ns   | _                | High-to-Low                            | 15                                     |              | 10                 | 20  | ns   |

|                  | with fanout of 2                                  | 15                            | -       | 2        | 4         | ns         |                  | Buffer outputs                         | 5                                      |              | 40                 | 80  | ns   |

|                  |                                                   |                               |         |          |           |            |                  | Low-to-High                            | 10                                     |              | 18                 | 36  | ns   |

|                  |                                                   |                               |         |          |           |            |                  | Low-to-riigh                           | 15                                     |              | 12                 | 24  | ns   |

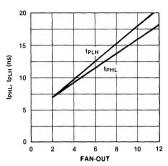

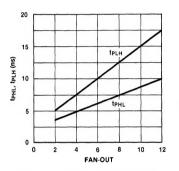

### GATE DELAYS

#### **Nominal Propagation Delay**

In Figures 6 through 12, examples are given of the nominal propagation delay times of several library cells, these being calculated from the delay figures given in the individual macro descriptions. These graphs are intended to provide quick-reference data to enable the designer to make an esti-

mate of critical a.c. path without having built or simulated a network.

Accurate delay figures can only be obtained after incorporating the wiring length load automatically calculated by INGATE (i.e., the result of the automatic routing program). A maximum delay is obtained by multiplying the nominal value by 2.2.

# SCC0330-M, SCC0450-M SCC0700-M, SCC1100-M

### **GATE DELAYS (Continued)**

Figure 4. Typical Output Current LOW as a Function of the Output Voltage LOW; **Buffer and Driver Outputs**

Figure 5. Typical Output Current HIGH as a Function of the Supply Voltage Minus the Output Voltage HIGH

20

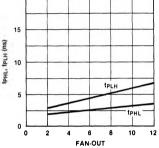

Figure 6. Nominal Propagation Delay as a Function of the Fan-Out; GIN1 (Single Inverter)

Figure 7. Nominal Propagation Delay as a Function of the Fan-Out: GNAND2 (2-Input NAND Gate)

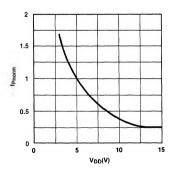

Figure 10. Normalized Propagation Delay (t<sub>Pnom</sub>) as a Function of the Supply Voltage

Figure 8. Nominal Propagation Delay as a Function of the Fan-Out: GIN4 (Quadruple Inverter)

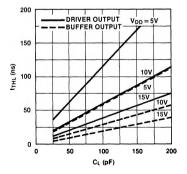

Figure 11. Output Transition Time (HIGHto-LOW) as a Function of the Load Capacitance

2 tPnorm 05 ٥ 50 100 150 - 50 Tamb(°C)

Figure 9. Normalized Propagation Delay (tPnorm) as a Function of the Ambient Temperature

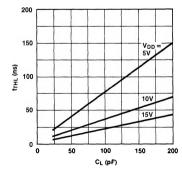

Figure 12. Output Transition Time (LOWto HIGH) as a Function of the Load **Capacitance for Driver and Buffer Outputs**

#### PERIPHERY

To provide a versatile interface, M-Series CMOS arrays have numerous I/O pads—see Figure 1a. These peripheral elements can be configured to match the input or output requirements of a wide variety of logic families. Accordingly, a bonding pad may have one of the following functions assigned to it:

- INPUT STAGE which includes an input protection circuit (series resistor and single diode clamp to V<sub>SS</sub>). The recommended maximum load is 260 array gates, or 100 array gates for optimum speed performance. Because the input voltage is not clamped to V<sub>DD</sub>, input voltages greater than the supply voltage is possible, thus allowing voltage level shifting.

- SCHMITT TRIGGER input stage for noise reduction, pulse shaping, or suppression of oscillation spikes associated with slow input clock transitions. The recommended maximum load is 10 array gates, or 5 for optimum speed performance.

- TRANSCEIVER input/output stage

- THREE-STATE output with driver or buffer performance capability for bussing applications

- COMPLEMENTARY OUTPUT with driver or buffer performance capability.

- OPEN DRAIN N- or P-transistor output

- PULL-UP/PULL-DOWN resistors (see Figure 2 for availability) may be added at various I/O stages. The values available are 5, 10, 15, 30, 60, 65, 70 and 75 Kohms.

|               | TCD<br>TCD<br>TPXI<br>TND<br>TPXI<br>TND<br>TPXI<br>TND<br>TPXI<br>TND<br>TPXI<br>TND<br>TPXI<br>TND<br>TPXI<br>TPXI<br>TPXI<br>TPXI<br>TPXI<br>TPXI<br>TPXI<br>TPXI |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TRANSOCIVI    |                                                                                                                                                                      |  |  |  |  |

| 1. 1. 19. 19. |                                                                                                                                                                      |  |  |  |  |

| TCDI          | complementary driver output                                                                                                                                          |  |  |  |  |

| TCBI          | complementary buffer output                                                                                                                                          |  |  |  |  |

| TPXI<br>TNDI  | open drain p-channel driver output<br>open drain n-channel driver output                                                                                             |  |  |  |  |

| TNBI          | open drain n-channel buffer output                                                                                                                                   |  |  |  |  |

|               |                                                                                                                                                                      |  |  |  |  |

| TRANSCEIV     | er with schmitt trigger input                                                                                                                                        |  |  |  |  |

| TCDS          | complementary driver output                                                                                                                                          |  |  |  |  |

| TPXS          | open drain p-channel driver output                                                                                                                                   |  |  |  |  |

| TNDS          | open drain n-channel driver output                                                                                                                                   |  |  |  |  |

| INPUTS        |                                                                                                                                                                      |  |  |  |  |

| INPA          | direct access to array                                                                                                                                               |  |  |  |  |

| INPI          | inverter                                                                                                                                                             |  |  |  |  |

| INPD          | driver                                                                                                                                                               |  |  |  |  |

| INPB          | buffer                                                                                                                                                               |  |  |  |  |

| INPS          | Schmitt trigger                                                                                                                                                      |  |  |  |  |

| OUTPUTS       | FANOUT: DRIVER = 4 LSTTL LOADS @ 4.5V<br>BUFFER = 6 LSTTL LOADS @ 4.5V                                                                                               |  |  |  |  |

| OCDR          | complementary driver                                                                                                                                                 |  |  |  |  |

| OCBU          | complementary buffer                                                                                                                                                 |  |  |  |  |

| OTDR          | 3-state driver                                                                                                                                                       |  |  |  |  |

| OTBU          | 3-state buffer                                                                                                                                                       |  |  |  |  |

| OPDB          | open drain p-channel driver                                                                                                                                          |  |  |  |  |

| ONDR          | open drain n-channel driver                                                                                                                                          |  |  |  |  |

| ONBU          | open drain n-channel buffer                                                                                                                                          |  |  |  |  |

| OSCILLATO     | RS                                                                                                                                                                   |  |  |  |  |

| XTOD          | crystal oscillator with driver stage                                                                                                                                 |  |  |  |  |

| хтов          | crystal oscillator with buffer stage                                                                                                                                 |  |  |  |  |

| RCOD          | RC oscillator with driver stage                                                                                                                                      |  |  |  |  |

| RCOB          | RC oscillator with buffer stage                                                                                                                                      |  |  |  |  |

| RESISTORS     |                                                                                                                                                                      |  |  |  |  |

| RD            | pull-down resistors                                                                                                                                                  |  |  |  |  |

| RU            | pull-up resistors                                                                                                                                                    |  |  |  |  |

|               |                                                                                                                                                                      |  |  |  |  |

Figure 13. The SCCXXXX I/O Cell Library

### Table 1. THE SCCXXXX GATE ARRAY CELL LIBRARY

| LIBRARY<br>IDENT.<br>CODE | LOGIC ELEMENT                         | FUNCTION                      | NUMBER<br>OF<br>UNITS                       | NUMBER<br>OF EQUIV.<br>GATES | REMARKS            |

|---------------------------|---------------------------------------|-------------------------------|---------------------------------------------|------------------------------|--------------------|

| Inverters/buffe           | ers                                   |                               | •                                           |                              |                    |

| GIN1                      | Inverter                              | A                             | 1/4                                         | 1/2                          | Max. 2 in one unit |

| GIN2                      | Array driver inverting                | A                             | 1/2                                         | 1                            | 2 times GIN1       |

| GIN3                      | Array driver inverting                | A .                           | 3/4                                         | 1+1/2                        | 3 times GIN1       |

| GIN4                      | Array driver inverting                | A .                           | 1                                           | 2                            | 4 times GIN1       |

| GIN6                      | Array driver inverting                | A                             | 1 + 1/2                                     | 3                            | 6 times GIN1       |

| GIN8                      | Array driver inverting                | A                             | 2                                           | 4                            | 8 times GIN1       |

| GIN12                     | Array driver inverting                | A                             | 3                                           | 6                            | 12 times GIN1      |

| GB12                      | Array buffer non-inverting            | A                             | 1                                           | 2                            | 2 times GIN1       |

| GB13                      | Array buffer non-inverting            | A                             | 1                                           | 2                            | 3 times GIN1       |

| NAND/AND ga               | ites                                  |                               | l                                           |                              |                    |

| GNAND2                    | 2-input NAND                          | A1•A2                         | 1/2                                         | 1                            |                    |

| GNAND3                    | 3-input NAND                          | A1•A2•A3                      | 3⁄4                                         | 1+1/2                        |                    |

| GNAND4                    | 4-input NAND                          | A1+A2+A3+A4                   | 1                                           | 2                            |                    |

| GAND2                     | 2-input AND                           | A1•A2                         | 1                                           | 2                            | Output GIN2        |

| GAND3                     | 3-input AND                           | A1•A2•A3                      | 1                                           | 2                            | ·                  |

| OR/NOR gates              | lk                                    | L                             | L                                           | 1                            |                    |

| GNOR2                     | 2-input NOR                           | $\overline{A1 + A2}$          | 1/2                                         | 1                            |                    |

| GNOR3                     | 3-input NOR                           | A1 + A2 + A3                  | 3/4                                         | 1+1/2                        |                    |

| GNOR4                     | 4-input NOR                           | A1 + A2 + A3 + A4             | 1                                           | 2                            |                    |

| GOR2                      | 2-input OR                            | A1 + A2                       | 1 1                                         | 2                            | Output GIN2        |

| GOR3                      | 3-input OR                            | A1 + A2 + A3                  | 1                                           | 2                            |                    |

| Complex logic             | functions                             |                               | L                                           | 1                            |                    |

| GF01 )                    |                                       | A1+B1•B2                      | 1                                           | 2                            |                    |

| GF02                      |                                       | A1 + B1•B1•B3                 | 1                                           | 2                            |                    |

| GF03                      |                                       | A1•A2+ B1•B2                  | 1                                           | 2                            |                    |

| GF06                      |                                       | A1 + A2 + B1•B2               | 1                                           | 2                            |                    |

| GF15                      |                                       | $A1 + B1 \cdot (C1 + C2)$     | 1 1                                         | 2                            |                    |

| GF51                      | Complex function                      | A1•(B1 + B2)                  | l i                                         | 2                            |                    |

| GF52                      |                                       | $A1 \bullet (B1 + B2 + B3)$   | 1                                           | 2                            |                    |

| GF53                      |                                       | $(A1 + A2) \bullet (B1 + B2)$ | 1                                           | 2                            |                    |

| GF56                      |                                       | A1•A2•(B1 + B2)               | 1                                           | 2                            |                    |

| GF65                      |                                       | A1•(B1+C1•C2)                 | 1                                           | 2                            |                    |

| GXOR1                     | EXCLUSIVE-OR                          | A+B+A+B                       | 1                                           | 2                            | Unbuffered         |

| GXNOR1                    | EXCLUSIVE-NOR                         | A•B+Ā•B                       | 1                                           | 2                            | Unbuffered         |

| GXOR2                     | EXCLUSIVE-OR                          | A+B+A+B                       | 1                                           | 2                            | Buffered           |

| GXNOR2                    | EXCLUSIVE-NOR                         | A•B+Ā•B                       | 1                                           | 2                            | Buffered           |

| GXOR3                     | EXCLUSIVE-OR                          | A+B+A+B                       | 2                                           | 4                            |                    |

| Transmission              | gate latches                          |                               | <u>ــــــــــــــــــــــــــــــــــــ</u> | <u> </u>                     |                    |

| GTL0                      | Strobed D-LATCH without SET           |                               |                                             |                              |                    |

|                           | and RESET                             |                               | 1                                           | 2                            | D                  |

| GTLRP                     | Strobed D-LATCH with RESET            |                               | 1 + 1/2                                     | 3                            | Positive triggered |

| GTLRN                     | Strobed D-LATCH with RESET            |                               | 1 + 1/2                                     | 3                            | Negative triggere  |

| GTLSP                     | Strobed D-LATCH with SET              | 1                             | 1 + 1/2                                     | 3                            | Positive triggered |

| GTLSN                     | Strobed D-LATCH with SET              | 1                             | 1 + 1/2                                     | 3                            | Negative triggered |

| GTL2                      | Strobed D-LATCH with SET and<br>RESET |                               | 1 + 1/2                                     | 3                            |                    |

| LIBRARY<br>IDENT.<br>CODE |                                         | FUNCTION | NUMBER<br>OF<br>UNITS | NUMBER<br>OF EQUIV.<br>GATES | REMARKS            |

|---------------------------|-----------------------------------------|----------|-----------------------|------------------------------|--------------------|

| Compound I                | atches                                  |          |                       |                              |                    |

| GGM0                      | MASTER module without SET and<br>RESET  |          | 2                     | 4                            |                    |

| GGMR                      | MASTER module with RESET                |          | 2                     | 4                            | All positive       |

| GGMS                      | MASTER module with SET                  |          | 2                     | 4                            | triggered          |

| GGM2                      | MASTER module with SET and<br>RESET     |          | 2                     | 4                            |                    |

| GGS0                      | SLAVE module without SET and<br>RESET   |          | 2                     | 4                            |                    |

| GGSR                      | SLAVE module with RESET                 |          | 2                     | 4                            | All negative       |

| GGSS                      | SLAVE module with SET                   |          | 2                     | 4                            | triggered          |

| GGS2                      | SLAVE module with SET and RESET         |          | 2                     | 4 ]                          |                    |

| Transmission              | n gate master-slave flip-flop (MD-D-FF) |          |                       | L                            | L                  |

| GT00                      | MS-D-FF without SET and RESET           |          | 2                     | 4                            |                    |

| GTR0P                     | MS-D-FF with RESET on MASTER            |          | $2 + \frac{1}{2}$     | 5                            | Positive triggered |

| GTRON                     | MS-D-FF with RESET on MASTER            |          | 2 + 1/2               | 5                            | Negative triggered |

| GTRRP                     | MS-D-FF with RESET on MASTER            |          |                       | 1                            |                    |

|                           | and SLAVE                               |          | 3                     | 6                            | Positive triggered |

| GTRRN                     | MS-D-FF with RESET on MASTER            |          |                       |                              |                    |

|                           | and SLAVE                               |          | 3                     | 6                            | Negative triggered |

| GTSSP                     | MS-D-FF with SET on MASTER              |          |                       | 1                            |                    |

|                           | and SLAVE                               |          | 3                     | 6                            | Positive triggered |

| GTSSN                     | MS-D-FF with SET on MASTER              |          |                       |                              |                    |

|                           | and SLAVE                               |          | 3                     | 6                            | Negative triggered |

| GT22                      | MS-D-FF with SET and RESET on           |          |                       |                              |                    |

|                           | MASTER and SLAVE                        |          | 3                     | 6                            |                    |

#### Table 1. THE SCCXXXX GATE ARRAY CELL LIBRARY (Continued)

#### DESIGNING A GATE ARRAY CHIP

The design of a gate array chip can be subdivided into several steps, which logically succeed each other, but can sometimes be performed in parallel. (See Figure 14.)

#### Logic Network Description

This transfers the user specification into a logic network description, using the gate array cells from the cell library.

The cell library contains several logic functions, ranging from simple logic gates (AND, NAND, etc.) to more complex flip-flop functions. For each cell, the logic function and timing are known. A macro-facility is available for user convenience.

#### SIMON — Logic Simulation

This step checks the logical behavior of the described network against the user specification. The well-proven logic simulator, SIMON, is used to simulate the response of the network on the user-supplied input stimuli. SIMON is an event-driven logic simulator with variable gate delay and uses five logic values (HIGH, LOW, UNKNOWN, etc.).

If the response of the simulated network does not comply with the user specification, the network has to be corrected and simulated again.

#### **INGATE, Cell Placement and Routing**

The INGATE step takes care of cell placement and automatic routing in accordance with the logic network description. The gate array cells used in the network have to be placed on the chip area in rows. The special construction of the cells results in very efficient use of the available chip area. The INGATE program calculates the wiring for the entire chip using only two mask steps (contacts and aluminum). User interaction is possible and useful for extremely dense circuits.

When large signal tracks occur on a chip, the capacitance of these can increase the fan-out driven by a gate output. This extra fan-out is computed in the INGATE program and can be fed back for use in the SIMON program to calculate the extra delay values that are necessary.

#### Mask-Making

The INGATE program interfaces directly with the CIRCUIT MASK program, which produces the control tapes for the mask generators for the two masks.

#### Testing

The logic simulator enables the fault coverage and efficiency of the user-supplied test sequences to be determined. The program interfaces with a test generation program that adds the d.c. parametric test and generates the control tapes to enable testing on any of the equipment used in the CAD program.

This equipment includes the following:

Sentry VII

Sentry 21

Figure 14. Development Flow

### **DESIGN PROCEDURE**

#### Gate Count

The following step-by-step procedure is intended to guide the designer in determining the correct gate count.

- · Simplify the logic circuit.

- Prepare a detailed logic drawing using only library cells provided in this data sheet.

- Expand all MSI functions to the level of gates and flip-flops (see e.g. the logic diagrams HE4000B family).

- Eliminate all unused functions and simplify the complex functions. Standard off-the-shelf products e.g. up/down counters, programmable counters and latches are often devices for considerable simplification.

- Partition the logic into several sections based on the pattern of interconnecting wiring. Circuits with numerous interconnections should be grouped together and interconnections between groups should be kept to a minimum.

- Examine the logic to see if complex functions can be used to reduce the gate count. Reduction can be achieved by using GF. functions and eliminating unnecessary inversions.

- Rearrange the logic into the library cells. When fan-out is more than 10 to 15, add or use buffers to minimize delays.

- One "equivalent gate" is a 2-input device.

- A rough estimate count can quickly be made by using HE4000B family gate count table.

- Sequential logic is more desirable as extensive, random interconnection yields a lower utilization factor. In addition, regular LSI functions, such as memories, may lead to inefficient use of a gate array.

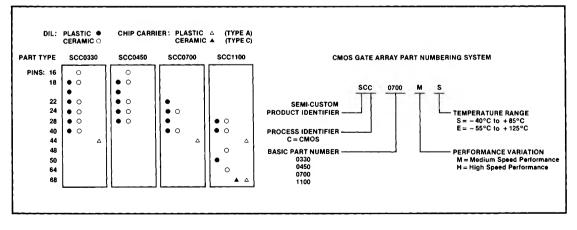

### PACKAGING INFORMATION AND PART NUMBERING SYSTEM

# SCC0330-M, SCC0450-M SCC0700-M, SCC1100-M

### GATE COUNT FOR HE400B FAMILY

A gate count is given below of 98 different devices that are described in the HE4000B CMOS Family Databook.

Only the gates to be implemented in the array area are given.

The connections to the 'outside world' are via the inputs or outputs located in the periphery area (among the bonding pads).

| TYPE<br>NUMBER       | NUMBER<br>OF EQUIV.<br>GATES | TYPE<br>NUMBER         | NUMBER<br>OF EQUIV.<br>GATES |

|----------------------|------------------------------|------------------------|------------------------------|

| HEF4000B             | 4                            | HEF4502B               | 6                            |

| HEF4001UB            | 4                            | HEF4508B               | 12                           |

| HEF4002B             | 4                            | HEF4510B               | 82                           |

| HEF4006B             | 76                           | HEF4511B               | 49                           |

| HEF4007B             | ▲                            | HEF4512B               | 26                           |

| HEF4008B             | 45                           | HEF4514B               | 60                           |

| HEF4011UB            | 4                            | HEF4515B               | 60                           |

| HEF4012B             | 4                            | HEF4516B               | 82                           |

| HEF4013B             | 14                           | HEF4517B               | 552                          |

| HEF4014B             | 57                           | HEF4518B               | 58                           |

| HEF4015B             | 41                           | HEF4519B               | 27                           |

| HEF4017B             | 38                           | HEF4520B               | 54                           |

| HEF4018B             | 57                           | HEF4521B*              | 128                          |

| HEF4019B             | 8                            | HEF4522B               | 62                           |

| HEF4020B             | 70                           | HEF4526B               | 62                           |

| HEF4021B             | 73                           | HEF4527B               | 60                           |

| HEF4022B             | 31                           | HEF4528B               | -                            |

| HEF4023B             | 6                            | HEF4531B               | 36                           |

| HEF4024B             | 35                           | HEF4532B               | 24                           |

| HEF4025B             | 6                            | HEF4534B               | -                            |

| HEF4027B             | 22                           | HEF4539B               | 24                           |

| HEF4028B             | 23                           | HEF4541B**             | 100                          |

| HEF4029B             | 75                           | HEF4543B               | 65                           |

| HEF4030B             | 12                           | HEF4555B               | 16                           |

| HEF4031B             | 277                          | HEF4556B               | 16                           |

| HEF4035B             | 46                           | HEF4557B               | 360                          |

| HEF4040B             | 61                           | HEF4585B               | 40                           |

| HEF4041B             | ▲                            | HEF4724B               | 52                           |

| HEF4042B             | 11                           | HEF4731B; V            | 1064                         |

| HEF4043B             | 8                            | HEF4737B; V            | —                            |

| HEF4044B             | 8                            | HEF40097B              | ▲                            |

| HEF4047B             | -                            | HEF40098B              | <b>A</b>                     |

| HEF4049B             | <b>A</b>                     | HEF40106B              | <b>A</b>                     |

| HEF4050B             |                              | HEF40160B              | 54                           |

| HEF4068B             | 6                            | HEF40161B              | 54                           |

| HEF4069UB            |                              | HEF40162B              | 52                           |

| HEF4070B             | 12                           | HEF40163B              | 52                           |

| HEF4071B             | 8                            | HEF40174B              | 34                           |

| HEF4072B             | 6                            | HEF40175B              | 24<br>68                     |

| HEF4073B             | 6                            | HEF40192B              |                              |

| HEF4075B             | 6                            | HEF40193B              | 68<br>64                     |

| HEF4076B             | 30                           | HEF40194B              | 64<br>40                     |

| HEF4077B             | 12                           | HEF40195B<br>HEF40240B | 40                           |

| HEF4078B<br>HEF4081B | 6<br>8                       | HEF40240B<br>HEF40244B |                              |

| _                    |                              |                        |                              |

| HEF4082B<br>HEF4085B | 4                            | HEF40245B<br>HEF40373B | ▲<br>16                      |

| HEF4085B             | 8                            | HEF40373B<br>HEF40374B | 32                           |

| HEF4000B             | ×                            | 1121 403/4D            | 52                           |

| HEF4093B<br>HEF4094B | 54                           |                        |                              |

| 1121 40340           | <u> </u>                     | l                      |                              |

Preliminary list (use for indication only)

•Excluding V'DD and V'SS •Excluding power-on reset

▲Located in the periphery