# **Signetics**

#### **Linear Products**

### DESCRIPTION

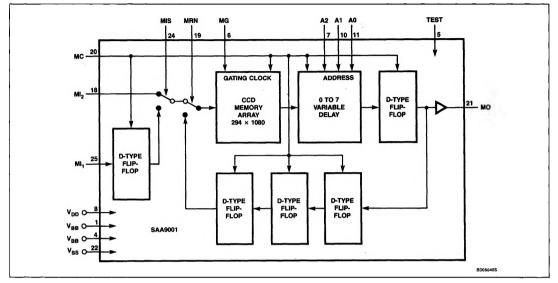

The SAA9001 is a 1-bit wide, 317,520-bit long, charge-coupled shift register, organized in 294 blocks of 1080 bits each. It is intended for use in a TV field memory at a maximum frequency of 21.3MHz.

Control is performed by two external signals, memory clock (MC), and memory gating (MG). The circuit has two data inputs (MI<sub>1</sub> and MI<sub>2</sub>) and the data may be internally recirculated. An adjustable delay of 0 to 7 bits is incorporated at the output to increment the total delay on a bit-by-bit basis, as programmed by the inputs AO, A1, and A2. All inputs, outputs, and controls are TTL-compatible.

### ORDERING INFORMATION

| DESCRIPTION                  | TEMPERATURE RANGE | ORDER CODE |

|------------------------------|-------------------|------------|

| 28-Pin Plastic DIP (SOT-117) | 0 to +60°C        | SAA9001N   |

#### **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL                          | PARAMETER                                                                                           | RATING      | UNIT |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------|-------------|------|--|

| v <sub>i</sub> , v <sub>o</sub> | Voltage on any pin, except V <sub>BB</sub> (Pin 4) and MO (Pin 21), with respect to V <sub>SS</sub> | 7           |      |  |

| V <sub>BB</sub>                 | Back-bias voltage                                                                                   | min7        | V    |  |

| 10                              | DC output current (sink or source)                                                                  | 10 mA       |      |  |

| T <sub>A</sub>                  | Operating ambient temperature range<br>(under DC operating conditions)                              | 0 to 60     | °C   |  |

| T <sub>STG</sub>                | Storage temperature range                                                                           | -65 to +150 | °C   |  |

| Ртот                            | Total power dissipation per package                                                                 | 1 W         |      |  |

# SAA9001 317k Bit CCD Memory

**Product Specification**

### FEATURES

- $\bullet$  317k bits (294 imes 1080)

- 21.3MHz toggle frequency

- TTL-compatible

- 28-pin DIP package

### APPLICATIONS

- TV field memory

- Digitizing images

### PIN CONFIGURATION

|          | VBB I      | 28 NC                                                                         |  |  |

|----------|------------|-------------------------------------------------------------------------------|--|--|

|          | NC 2       | 27] NC                                                                        |  |  |

|          | NC 3       | 26 NC                                                                         |  |  |

|          | Vee 4      | 25] MI,                                                                       |  |  |

|          | TEST 5     | 24 MIS                                                                        |  |  |

|          | MG 6       | 23 NC                                                                         |  |  |

|          |            |                                                                               |  |  |

|          | A2 7       | 22 V <sub>ss</sub>                                                            |  |  |

|          | V00 8      | 21] MO                                                                        |  |  |

|          | NC 9       | 20 MC                                                                         |  |  |

|          | A1 10      | 19 MRN                                                                        |  |  |

|          | A0 11      | 18 MI2                                                                        |  |  |

|          | NC 12      | 17 NC                                                                         |  |  |

|          | NC 13      | 16 NC                                                                         |  |  |

|          | NC 14      | 15 NC                                                                         |  |  |

|          |            |                                                                               |  |  |

|          |            | TOP VIEW                                                                      |  |  |

| PIN NO.  | SYMBOL     | DESCRIPTION                                                                   |  |  |

| 1        | VBB        | Back-bias supply voltage (to be<br>connected to Pin 4)                        |  |  |

| 4        | VBB        | Back-bias supply voltage (to be                                               |  |  |

| 5        | TEST       | connected to Pin 1)<br>Control input for testing                              |  |  |

|          |            | purposes only. It is internally connected to V <sub>SS</sub> via a $1k\Omega$ |  |  |

|          |            | (approx.) resistor and needs no                                               |  |  |

| 6        | MG         | external connection<br>Memory gating input                                    |  |  |

| 7        | A2         | Control input for additional                                                  |  |  |

| 8        | VDD        | internal delay<br>Positive supply voltage                                     |  |  |

| 10       | AI         | Control input for additional                                                  |  |  |

| 11       | AO         | internal delay<br>Control input for additional                                |  |  |

|          |            | internal delay                                                                |  |  |

| 18<br>19 | MI2<br>MBN | Memory input 2                                                                |  |  |

| 19       |            | Memory recirculate control.<br>Recirculation is activated when<br>MRN is Low  |  |  |

| 20       | мс         | Memory clock input                                                            |  |  |

| 21       | MO         | Memory output                                                                 |  |  |

| 22       | VSS        | Negative supply voltage                                                       |  |  |

| 24       | MIS        | (ground)<br>Memory input select; selects                                      |  |  |

|          |            | MI <sub>1</sub> or MI <sub>2</sub>                                            |  |  |

| 25       | MI1        | Memory input 1                                                                |  |  |

|          |            |                                                                               |  |  |

# SAA9001

### **BLOCK DIAGRAM**

## CAPACITANCE

| SYMBOL          | PARAMETER                                            | MAX | UNIT |  |

|-----------------|------------------------------------------------------|-----|------|--|

| CI              | Data inputs MI1, MI2 (Pins 25 and 18)                | 9   | рF   |  |

| C <sub>C</sub>  | Clock input MC (Pin 20)                              | 9   | pF   |  |

| CG              | Gating input MG (Pin 6)                              | 9   | рF   |  |

| Co              | Data output MO (Pin 21)                              | 9   | pF   |  |

| C <sub>RN</sub> | Recirculation control MRN (Pin 19) 9                 |     |      |  |

| CIS             | Input select control MIS (Pin 24)                    | 9   | рF   |  |

| CA              | Delay program inputs A0, A1, A2 (Pins 11, 10, and 7) | 9   | рF   |  |

# SAA9001

## DC OPERATING CONDITIONS

| SYMBOL          |                        | LIMITS |     |       |      |

|-----------------|------------------------|--------|-----|-------|------|

|                 | PARAMETER              | Min    | Тур | Max   | UNIT |

| V <sub>DD</sub> | Supply voltage range   | 4.75   |     | 5.25  | v    |

| V <sub>BB</sub> | Back-bias supply range | -3.65  |     | -3.35 | v    |

| VIL             | Input voltage Low      | -1.0   |     | + 0.8 | v    |

| VIH             | Input voltage High     | 2.0    |     | 6.0   | v    |

# DC ELECTRICAL CHARACTERISTICS $T_A = 0$ to $+ 60^{\circ}$ C; $V_{DD} = 4.75$ to 5.25V; $V_{BB} = -3.5 \pm 0.15$ V; output not loaded, unless otherwise specified.

| SYMBOL |                                                                                                                        | LIMITS      |      |     |    |

|--------|------------------------------------------------------------------------------------------------------------------------|-------------|------|-----|----|

|        | PARAMETER                                                                                                              | Min Typ Max | UNIT |     |    |

| ILI    | Input leakage current at $V_1$ = GND to $V_{DD}$ :<br>MI <sub>1</sub> ; MI <sub>2</sub> ; MC; MG; A0; A1; A2; MRN; MIS |             |      | 10  | μΑ |

| IDD    | Power supply current from V <sub>DD</sub> at f = 21.3MHz                                                               |             |      | 70  | mA |

| VOL    | Output voltage Low at I <sub>OL</sub> = 4mA                                                                            |             |      | 0.4 | v  |

| VOH    | Output voltage High at I <sub>OH</sub> = -1mA                                                                          | 2.4         |      |     | v  |

### AC TEST CONDITIONS

| PARAMETER                                                                                               | LIMIT        | UNIT |

|---------------------------------------------------------------------------------------------------------|--------------|------|

| Input pulse levels                                                                                      | 0.6 and 2.4  | V    |

| Rise and fall times between 0.8 and 2.0V (t <sub>R</sub> , t <sub>F</sub> ) clock input MC              | ≤3           | ns   |

| data inputs MI <sub>1</sub> , MI <sub>2</sub> ; gating input MG;<br>control inputs A0, A1, A2, MIS, MRN | ≥3           | ns   |

| Timing reference levels                                                                                 |              |      |

| clock input MC                                                                                          | 1.5          | V    |

| data inputs MI <sub>1</sub> , MI <sub>2</sub> ; gating input MG                                         | 0.8 or 2.0   | V    |

| data output MO                                                                                          | 0.8 or 2.0   | V    |

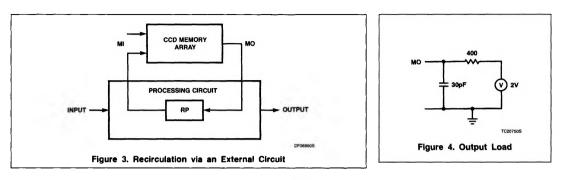

| Output load                                                                                             | see Figure 4 |      |

# SAA9001

| AC ELECTRICAL CHARACTERISTICS $T_A = 0$ to $+60^{\circ}$ C; $V_{DD} = 4.75$ to 5.2 | 25V; V <sub>BB</sub> = -3.5 ± 0.15V. |

|------------------------------------------------------------------------------------|--------------------------------------|

|------------------------------------------------------------------------------------|--------------------------------------|

| SYMBOL             |                                                  |     | LIMITS |                       |      |

|--------------------|--------------------------------------------------|-----|--------|-----------------------|------|

|                    | PARAMETER                                        | Min | Тур    | Max                   | UNIT |

| f <sub>CL</sub>    | Clock frequency <sup>1</sup>                     |     |        | 21.3                  | MHz  |

| t <sub>CL</sub>    | Clock Low time                                   | 18  |        |                       | ns   |

| t <sub>CH</sub>    | Clock High time                                  | 18  |        |                       | ns   |

| t <sub>R</sub>     | Recirculation time <sup>1</sup>                  |     |        | 27                    | ms   |

| t <sub>GW</sub>    | Waiting time (gating Low/High time) <sup>2</sup> |     |        | 1100                  | μs   |

| t <sub>GC</sub>    | Gating setup time                                | 7.5 |        |                       | ns   |

| t <sub>CG</sub>    | Gating hold time                                 | 0.5 |        |                       | ns   |

| t <sub>IC</sub>    | Data setup time                                  | 7.5 |        |                       | ns   |

| t <sub>CI</sub>    | Data hold time                                   | 0.5 |        |                       | ns   |

| t <sub>OH</sub>    | Output hold time                                 | 5.0 |        |                       | ns   |

| top                | Output delay time                                |     |        | 23.5                  | ns   |

| t <sub>AH</sub>    | Output invalid after address change              | 0   |        |                       | μs   |

| t <sub>AD</sub>    | Address valid after address change <sup>3</sup>  |     |        | 7 clock<br>pulses + 1 | μs   |

| t <sub>MRNSU</sub> | Recirculation setup time <sup>4</sup>            | 0   |        | 1                     | μs   |

| t <sub>MISSU</sub> | Input select setup time5                         | 0   |        | 1 clock<br>pulse + 1  | μs   |

NOTES:

1. The maximum recirculation time must never be exceeded by any combination of low frequency gating and/or waiting time.

2. Every 1300µs, at least three blocks of 1080 bits must be transferred to the output. This means that immediately after a wait of 1100µs, three blocks must be shifted out.

A change in delay will cause invalid data at the output for the time t<sub>AD</sub>.

After a change of MRN, the signal recirculation path is not switched before t<sub>MRNSU</sub>.

5. After a change of MIS, data at the input is invalid for t<sub>MISSU</sub>

SAA9001

# 317k Bit CCD Memory

### FUNCTIONAL DESCRIPTION

#### Operation

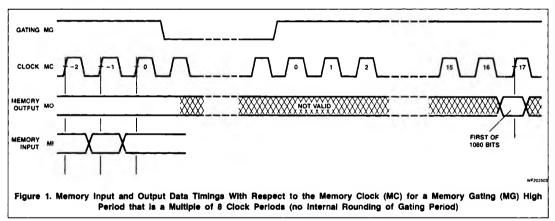

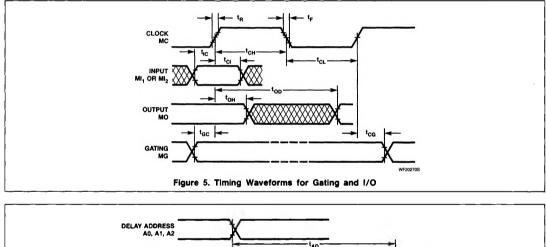

The memory array is organized to handle data in blocks of 1080 bits and has a capacity of 294 data blocks. The structure of the memory array provides fast, serial data input and output, with parallel transfer of data blocks through the memory. Memory input and output are controlled by the memory gating (MG); the serial output is initiated by the rising edge of MG, and the storage of the data present in the memory's input register Is performed on the falling edge of MG. In normal operation, one cycle of MG is an uninterrupted High level of at least 1080 clock periods (-4 or +3 clock periods) followed by a Low level of at least 32 clock periods. Input, output, and gating signals are all referred to the rising edge of the memory clock (MC).

The internal recirculation facility is activated when the control input MRN is Low.

#### Memory output

Output is enabled when MG is High and data is clocked serially from the memory. Referring to Figure 1, the first rising clock edge after the positive transition of MG is defined as clock pulse "0". If the delay control address is A2 = A1 = A0 = 0, then the first bit of the output is valid at clock pulse "17" (the delay of 17 clock periods is due to internal multiplexing of the data in the memory).

The output delay can be increased by the values shown in Table 1 using the internal delay line controlled by A0, A1, and A2.

#### Table 1. Additional Delay Control

|    | DELAY<br>ADDRESS |            |                 |

|----|------------------|------------|-----------------|

| A2 | A1               | <b>A</b> 0 | (CLOCK PERIODS) |

| 0  | 0                | 0          | 0               |

| 0  | 0                | 1          | 1               |

| 0  | 1                | 0          | 2               |

| 0  | 1                | 1          | 3               |

| 1  | 0                | 0          | 4               |

| 1  | 0                | 1          | 5               |

| 1  | 1                | 0          | 6               |

| 1  | 1                | 1          | 7               |

#### **Data input**

Data to be stored is directed to the memory from either  $M_1$  or  $M_2$  as selected by the control input MIS (see Table 2). The  $M_1$  input is delayed by one clock period.

#### **Table 2. Input Selection**

| CONTROL INPUT | MEMORY INPUT    |

|---------------|-----------------|

| MIS = 0       | MI <sub>1</sub> |

| MIS = 1       | MI <sub>2</sub> |

Input data is clocked serially into the input register of the CCD memory. When the negative transition of MG occurs, the 1080 bits of data present in the input register are entered into the memory array. If the interval of MG = High is not an exact multiple of eight clock periods, the timing of the negative transition of MG is internally rounded to be an exact multiple of eight clock periods. Note that the data path from input MI<sub>1</sub> has a delay of one clock period and the path from MI<sub>2</sub> is direct.

## SAA9001

# 317k Bit CCD Memory

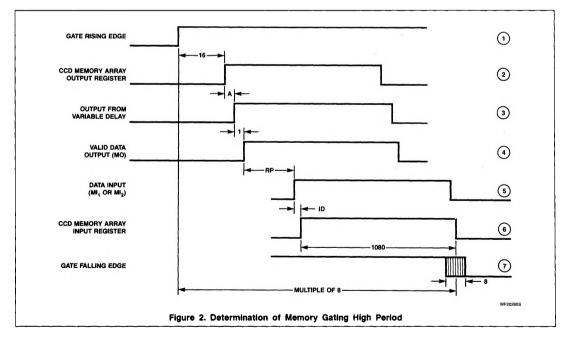

The length of the MG = High interval required for internal and external recirculation of data is determined as shown in Figure 2. The positive transition of MG (waveform 1) initiates the serial transfer of data from the output register. Due to multiplexing in the memory, valid data is available after 16 clock periods (waveform 2). After a delay of "A" clock periods, determined by A0, A1, and A2 (waveform 3), and a one-clock period delay via a Dtype flip-flop, the valid data is available at the output pin MO (waveform 4).

Incoming data can be delayed by two amounts: RP (waveform 5), a phase shift introduced when the data is recirculated through an external processing circuit, and ID (waveform 6), a one-clock period delay when input MI<sub>1</sub> is selected. The negative transition of MG, internally rounded to a multiple of eight clock periods (waveform 7), initiates storage of the last 1080 bits presented at the memory input (waveform 6). Therefore, the MG = High interval is 16 + A + 1 + RP + ID + 1080 clock periods, and this figure is rounded to a multiple of eight. From this, (A + 1 + RP + ID) modulo 8 = 0.

During internal recirculation of the data (MRN = Low), the three D-type flip-flops in the recirculation path give RP a value of three clock periods and ID will be zero. Consequently, the variable delay should be programmed for a delay of A = 4 for proper data retention, i.e., (4 + 1 + 3 + 0) modulo 8 = 0.

In conclusion, to store 1080 bits of valid data and to retrieve at the output 1080 valid data bits, the MG = High interval must be at least 1076 clock periods followed by an MG = Low interval of at least 32 clock periods. The MG = Low interval can be reduced to a minimum of 24 clock periods when MG = High is a multiple of eight clock periods.

#### **Fast Gating**

Fast gating is a method of accelerating the internal transfer of data through the memory at the expense of valid data, and is therefore useful for skipping unwanted data blocks. The MG = High interval for fast gating is less than 1076 clock periods to a minimum of 360 clock

periods. If the MG = High interval is a multiple of eight clock periods during fast gating, the MG = Low interval can be reduced to 24 clock periods (min.); otherwise, the MG = Low interval must be at least 32 clock periods. The output data is not valid during fast gating and during the first two data blocks at the output after fast gating has ceased. No valid data is clocked into the input register of the CCD memory during fast gating.

#### **Slow Gating**

The transfer of data can be decelerated by using slow gating. For this, the MG = High or MG = Low interval is extended to the maximum waiting time  $(t_{GW})$ .

#### HANDLING

Inputs and outputs are protected against electrostatic charge in normal handling. However, to be totally safe, it is desirable to take normal precautions appropriate to handling MOS devices.

# SAA9001

-tAH->

Figure 6. Timing Waveforms for Address Setup and Hold

WF202805

OUTPUT MO