# INTEGRATED CIRCUITS

Objective specification File under Integrated Circuits, IC01 1997 Aug 12

HILIP

### **Objective specification**

### ATAPI CD-R block decoder

### CONTENTS

| 1      | FEATURES                                     |

|--------|----------------------------------------------|

| 2      | GENERAL DESCRIPTION                          |

| 2.1    | Memory mapped control registers              |

| 2.2    | Error correction features                    |

| 2.3    | Host interface features                      |

| 2.4    | Buffer memory organisation                   |

| 2.5    | Subcode handling features                    |

| 2.5    | Multimedia output audio control features     |

| -      |                                              |

| 3      | QUICK REFERENCE DATA                         |

| 4      | ORDERING INFORMATION                         |

| 5      | BLOCK DIAGRAM                                |

| 6      | PINNING                                      |

| 6.1    | Detailed description of pin functions        |

| 7      | FUNCTIONAL DESCRIPTION                       |

| 7.1    | Memory field description                     |

| 7.1.1  | DVD-ROM memory field information             |

| 7.2    | CD input control registers                   |

| 7.2.1  | Registers associated with data in process    |

| 7.3    | Multimedia output interface                  |

| 7.3.1  | Subcode input block                          |

| 7.3.2  | Subcode mode transmit control register       |

| 7.3.3  | General description of the multimedia output |

|        | interface                                    |

| 7.3.4  | IEC 958/EBU output                           |

| 7.3.5  | Memory-to-memory block copy function         |

| 7.4    | Interrupt registers                          |

| 7.4.1  | Interrupt 1                                  |

| 7.4.2  | Interrupt 2                                  |

| 7.4.3  | UART interrupt                               |

| 7.5    | Host interface                               |

| 7.5.1  | Introduction                                 |

| 7.5.2  | Description of the host interface block      |

| 7.5.3  | Description of the host interface registers  |

| 7.5.4  | Transfer counter                             |

| 7.5.5  | Packet size store                            |

| 7.5.6  | Sequencer status                             |

| 7.5.7  | Host interface DMA special bits              |

| 7.5.8  | Automatic block pointer reload programming   |

| 7.5.9  | DMA transfer programming of the host         |

|        | interface                                    |

| 7.5.10 | Generic interface operation                  |

| 7.5.11 | DMA transfers in generic mode                |

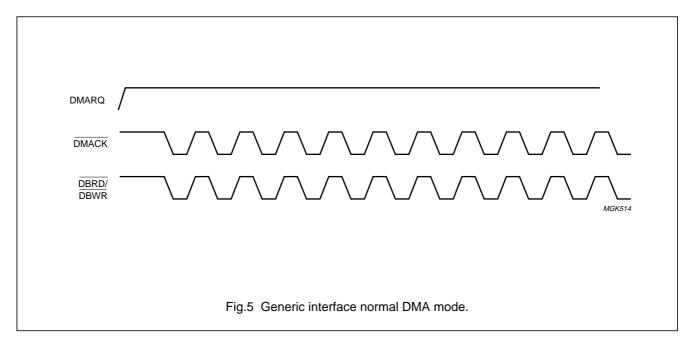

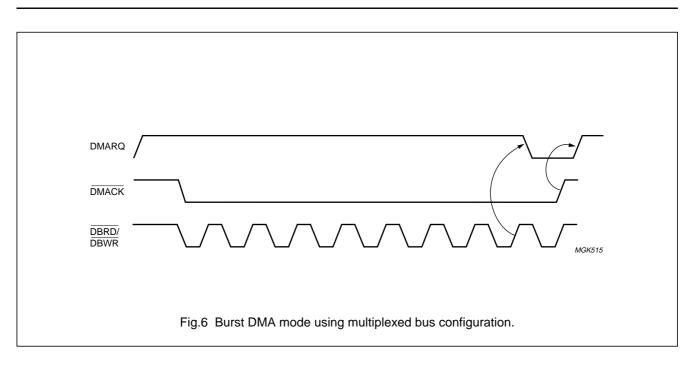

| 7.5.12<br>7.5.13        | Normal DMA mode<br>Burst DMA mode using multiplexed bus                               |

|-------------------------|---------------------------------------------------------------------------------------|

| 7.6<br>7.6.1            | configuration<br>Microcontroller interface<br>Kernel based firmware                   |

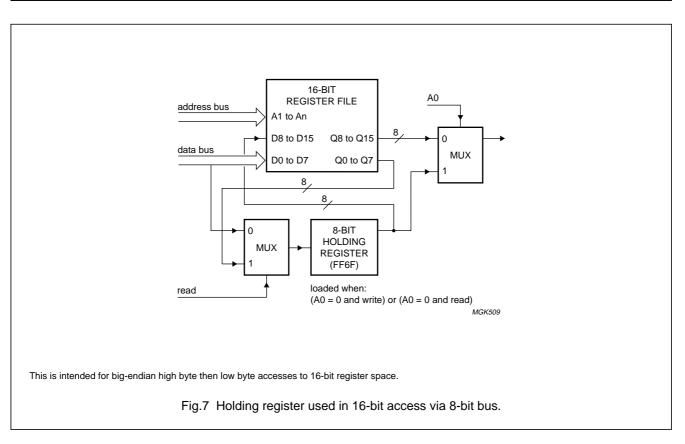

| 7.6.2<br>7.7            | 16-bit registers automatic read and write<br>8051 CPU and memory management functions |

| 7.7.1<br>7.7.2<br>7.7.3 | Sub-CPU bus access timing<br>Buffer memory organisation<br>Subpage                    |

| 7.8<br>7.8              | External memory interface<br>DRAM interface configuration register                    |

| 7.9<br>7.9<br>7.9.1     | UART for communication with CD engine<br>UART basic engine interface                  |

| 7.10<br>7.10.1          | Clock generation control<br>Crystal oscillator                                        |

| 7.10.2<br>7.10.3        | Sub-CPU clock control register<br>SAA7381 system clock control registers              |

| 8                       | LIMITING VALUES                                                                       |

| 9                       | THERMAL CHARACTERISTICS                                                               |

| 10                      | CHARACTERISTICS                                                                       |

| 11                      | TIMING CHARACTERISTICS                                                                |

| 11.1<br>11.2            | External memory interface timing<br>Host interface timing                             |

| 11.2.1<br>11.2.2        | Host interface ATAPI PIO and DMA timing ATA bus timing                                |

| 11.2.3                  | Ultra DMA operation and timing                                                        |

| 11.2.4                  | Ultra DMA read/write timing                                                           |

| 11.3<br>11.4            | Sub-CPU interface timing UART timing                                                  |

| 12                      | APPENDIX A                                                                            |

| 13                      | APPLICATION INFORMATION                                                               |

| 14                      | PACKAGE OUTLINE                                                                       |

| 15                      | SOLDERING                                                                             |

| 15.1                    | Introduction                                                                          |

| 15.2                    | Reflow soldering                                                                      |

| 15.3<br>15.4            | Wave soldering<br>Repairing soldered joints                                           |

| 16                      | DEFINITIONS                                                                           |

| 17                      | LIFE SUPPORT APPLICATIONS                                                             |

|                         |                                                                                       |

### SAA7381

### **1 FEATURES**

- Supports real time error detection and correction in hardware. Error correction to n = 27, error detect to n = 30 and raw data transfer to n = 32.

- DVD-ROM supported in combination with the SAA7335

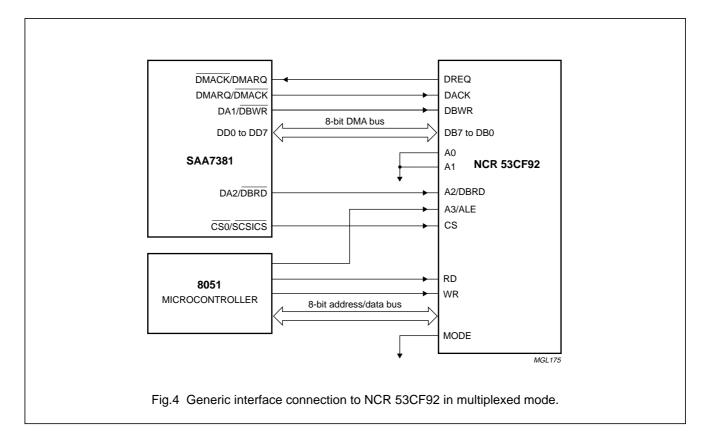

- Direct generic interface to external Small Computer Systems Interface (SCSI) controller devices

- Operates with up to 16 Mbytes DRAM

- Hyper-page DRAM up to 33 Mbytes words/s burst

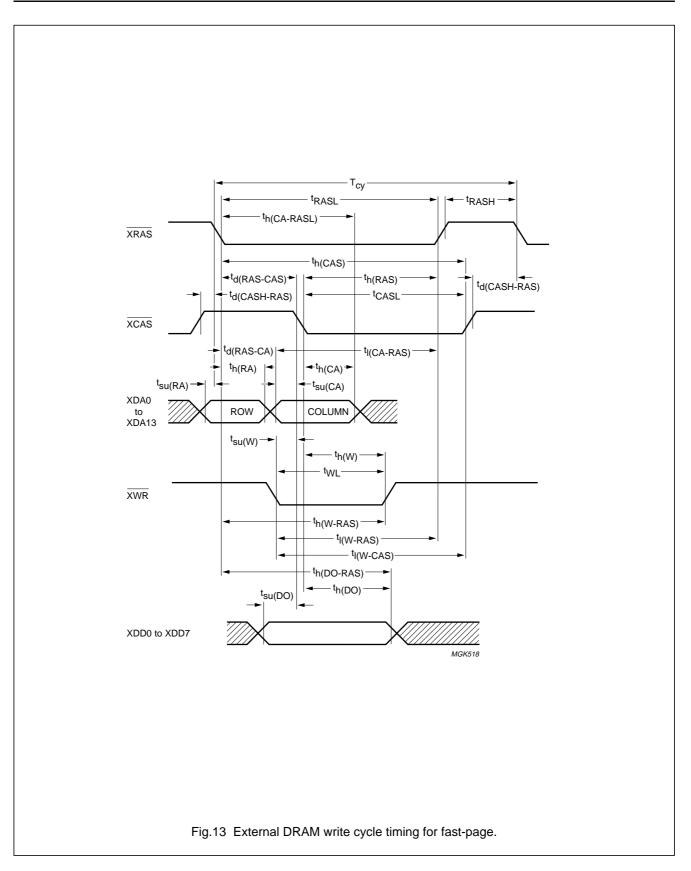

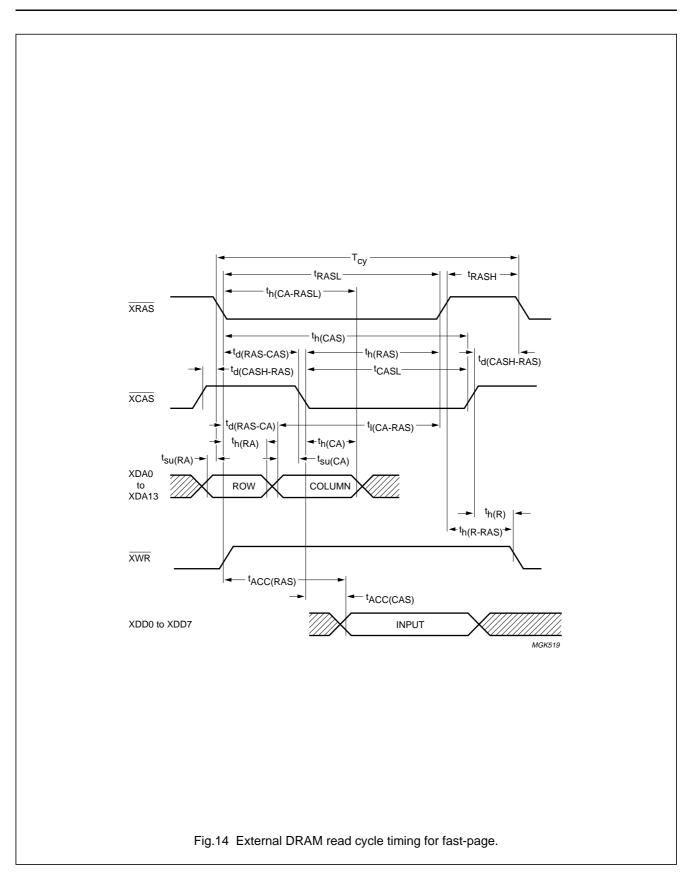

- Fast-page DRAM at up to 17.5 Mbytes words/s burst

- Has fixed n = 1 or n = 2 rate (44.1 or 88.2 kHz) I<sup>2</sup>S-bus multimedia output for simple audio/video output; features for CAV/quasi-CLV support

- Supports Philips multimedia audio CODEC

- Provides 'SHOARMA' Red Book audio buffer

- IEC 958 (SPDIF, AES/EBU and DOBM) output with Q-W subcode and programmable category code, output at n = 1 rate

- Device registers are memory mapped for faster direct access to the chip

- Provides direct access from sub-CPU to buffer RAM to support scratchpad accesses. This eliminates the need for extra RAM chips in the system

- Automatic sequencing of ATAPI packet command protocol, including command termination

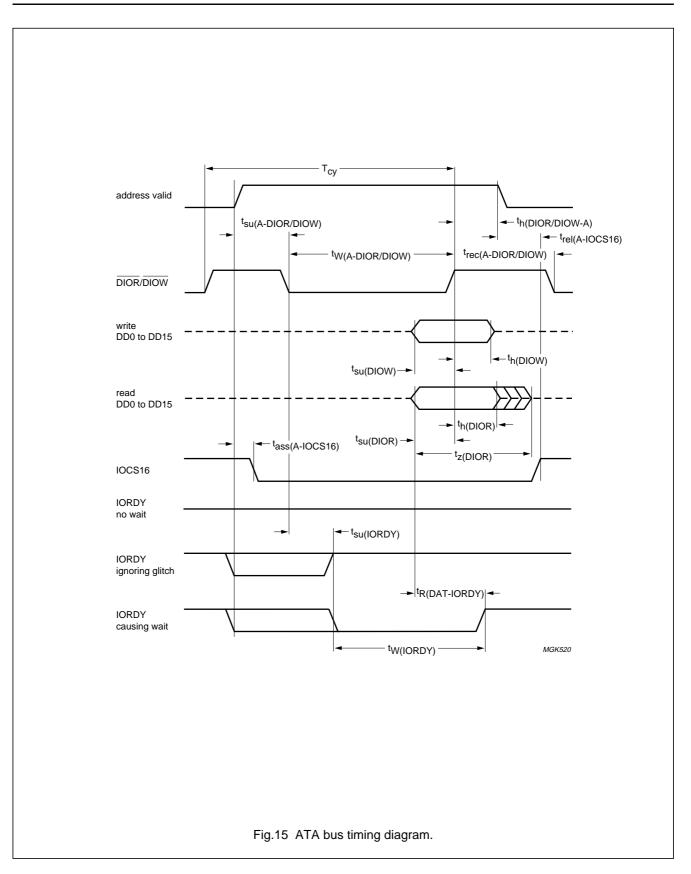

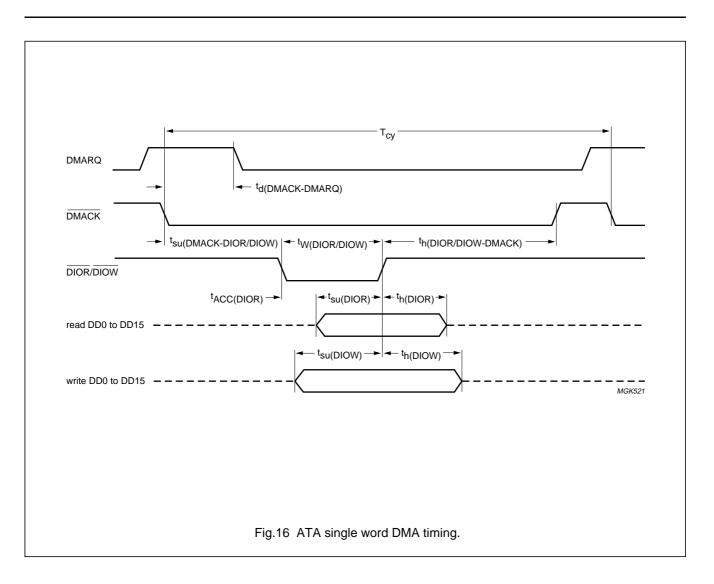

- Automated data transfers to and from the host using PIO, DMA and ultra DMA.

### 2 GENERAL DESCRIPTION

The SAA7381 is a block decoder/encoder and buffer manager for high-speed CD-ROM/CD-R functions, that integrates real time error correction and detection and bidirectional ATAPI transfer functions into a single chip.

### 2.1 Memory mapped control registers

The SAA7381 device has a large number of memory mapped registers. These are arranged so that high-level languages see the registers as external byte or 16-bit integer quantities. The block addressing of the SAA7381 facilitates the use of pairs of 16-bit quantities to represent addresses. The reading and writing of 16-bit registers within the device can be performed by two separate 8-bit reads, where the second byte data is latched at the same time as the first byte is read.

### 2.2 Error correction features

The SAA7381 has an on-chip 36 kbits memory that is used as a buffer memory for error and erasure correction processing. This buffer memory reduces the number of external RAM accesses that are needed for error correction and thus allows for an increased rate of data throughput.

The error corrector is switchable between two-pass, single-pass [both with Error Detection/Correction (EDC/ECC)] and EDC only modes to further improve throughput. The presence of the full error corrector removes the need for firmware based control of the error corrector's operation.

### 2.3 Host interface features

The SAA7381 has an ATAPI host interface that may be directly connected to the ATAPI bus thereby reducing the need for external support devices. It supports PIO Mode 4 transfer and Mode 0 ultra DMA. This interface can also be configured as a generic DMA interface for use with external host interface devices (e.g. SCSI controller). The DMA interface has the following features:

- ATAPI command packets are automatically loaded into the command FIFO

- Data transfer to the host is automatically sequenced to reduce inter-block latencies and improve host CPU utilisation

- Host data transfer rate is independent of error corrector operation and the data input path

- The host interface features automatic determination of block length for Mode 2, Form 1 and Form 2 sectors. The block length transferred is programmable.

- The host interface can transfer up to 3 sub-blocks per sector, with each sub-block being transferred dependent on the Form bit. Automatic reload of sub-block pointers and unconditional transfer are supported.

## SAA7381

### 2.4 Buffer memory organisation

Memory is mapped as a 16-bit block number and 12-bit offset into that block. The block oriented memory structure permits the use of 16-bit pointers in software thereby minimising the overhead of accessing memory. The address can be found from the following equation: address = block number  $\times$  2560 + offset.

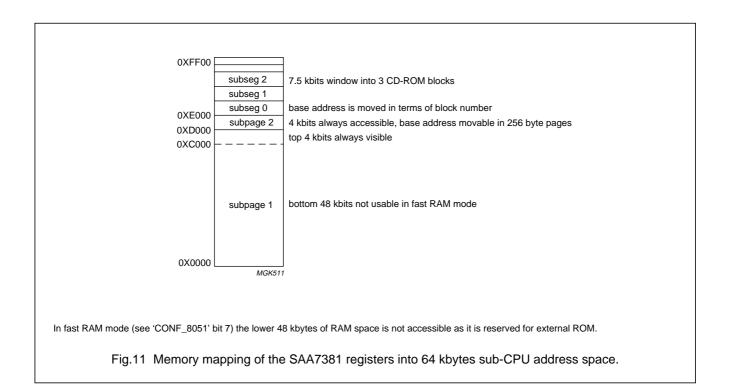

The microcontroller sees the SAA7381 as a memory mapped peripheral, with control and status registers appearing in the upper address space.

The lowest 52 kbytes (48 kbytes + 4 kbytes) of the 8051 microcontroller external address space is mapped as a window into the memory on a user-specified 1 kbyte boundary within the buffer RAM. This can be used as a scratchpad memory.

The next 4 kbytes is separately mapped as a window into the memory on a user-specified 1 kbyte boundary within the RAM.

The next 7.5 kbytes of the external data space consists of three independently addressed memory segments for accessing block data, subcode information and block headers.

The registers of the SAA7381 are mapped into the top 256 bytes of external data space.

### 2.5 Subcode handling features

The writing of data into the buffer RAM is aligned to the absolute time sync marker with the following features:

- Subcodes are written into memory together with their associated sector data. This eases the provision of specialist features, for example CD + G or Karaoke CD applications.

- All channels of subcode are de-interleaved

- The Q channel is also Cyclic Redundancy Checked (CRC) for increased reliability

- When operating in 3-wire subcode mode, it is possible to control or read the P bit in the P-W subcode stream.

### 2.6 Multimedia output audio control features

The I<sup>2</sup>S-bus input may be processed before feeding to the multimedia audio output in several simple ways:

- As audio is transferred via the buffer memory, it is not necessary to have the CD-DSP I<sup>2</sup>S-bus input at exactly the audio n = 1 or video n = 2 rate. Any faster speed will work because the buffer RAM is used as a FIFO.

- Both channels may be independently controlled. The left channel output may be sourced from zero (digital silence), left or right input; this also applies for the right channel output. This permits basic audio switching and channel swapping.

- IEC 958 (SPDIF, AES/EBU and DOBM) output with Q-W subcode and programmable category code, can be output from the same CD-DSP I<sup>2</sup>S-bus data source.

| SYMBOL                 | PARAMETER                         | MIN.                   | TYP.                                  | MAX. | UNIT |

|------------------------|-----------------------------------|------------------------|---------------------------------------|------|------|

| V <sub>DDD(core)</sub> | digital core supply voltage       | 3.0                    | 3.3                                   | 3.6  | V    |

| V <sub>DDD(pad)</sub>  | digital peripheral supply voltage | V <sub>DDD(core)</sub> | 5.0 or 3.3                            | 5.0  | V    |

| I <sub>DDD</sub>       | supply current                    | tbf                    | 60                                    | tbf  | mA   |

| f <sub>xtal</sub>      | crystal frequency                 | 8                      | 8.4672, 11.289,<br>16.9344 or 33.8688 | 35   | MHz  |

| T <sub>amb</sub>       | operating ambient temperature     | 0                      | -                                     | 70   | °C   |

| T <sub>stg</sub>       | storage temperature               | -55                    | -                                     | +125 | °C   |

### **3 QUICK REFERENCE DATA**

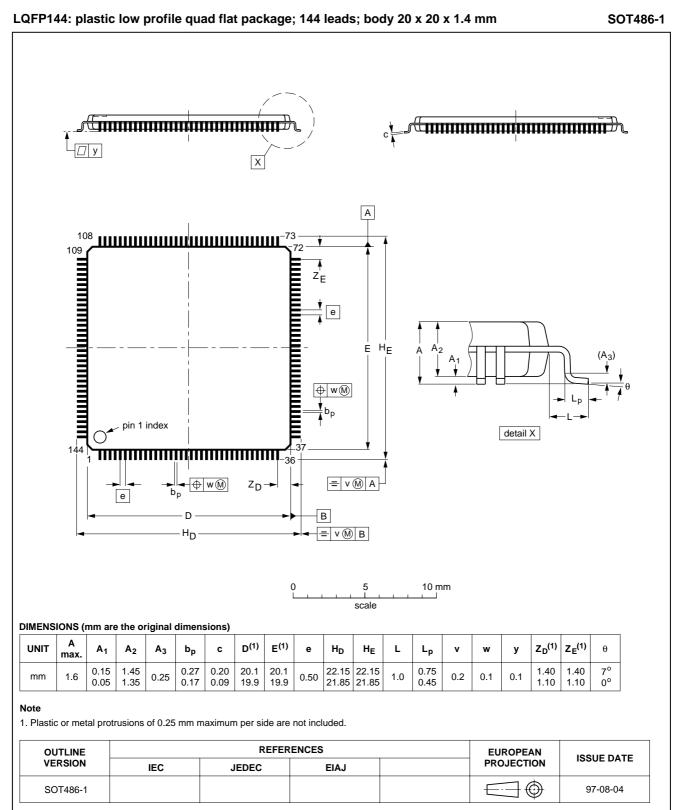

### 4 ORDERING INFORMATION

| TYPE    |         |                                                                                     |          |  |  |  |

|---------|---------|-------------------------------------------------------------------------------------|----------|--|--|--|

| NUMBER  | NAME    | NAME DESCRIPTION VERSION                                                            |          |  |  |  |

| SAA7381 | LQFP144 | plastic low profile quad flat package; 144 leads; body $20 \times 20 \times 1.4$ mm | SOT486-1 |  |  |  |

## SAA7381

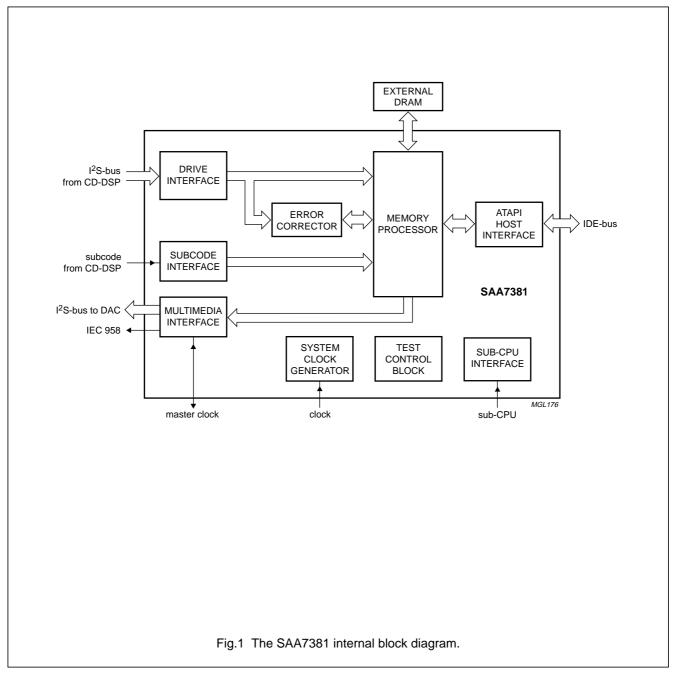

### 5 BLOCK DIAGRAM

# SAA7381

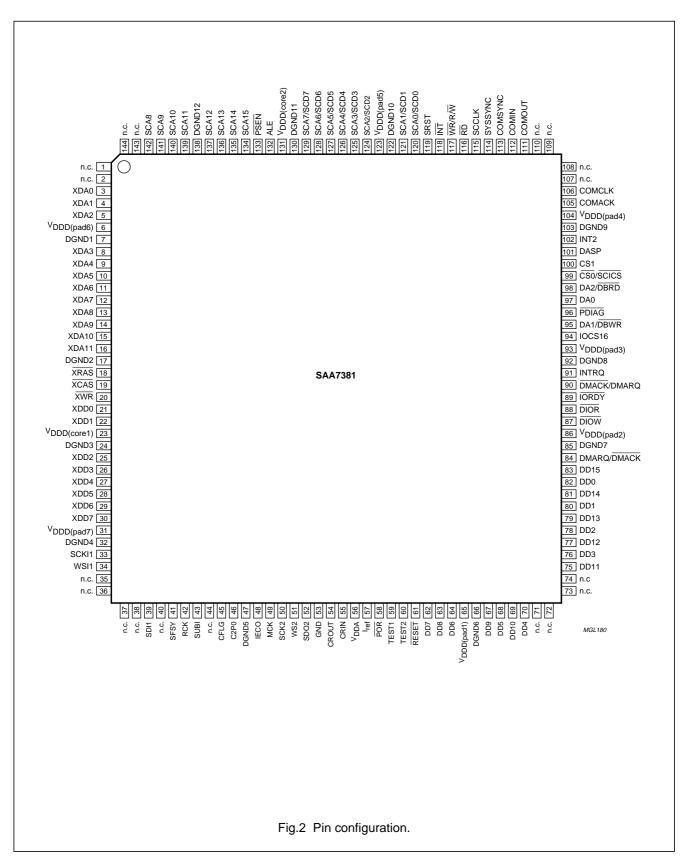

### 6 PINNING

| SYMBOL                  | PIN | TYPE | DRIVE/<br>THRESHOLD | GROUPING                 | DESCRIPTION                                   |

|-------------------------|-----|------|---------------------|--------------------------|-----------------------------------------------|

| n.c.                    | 1   | -    | -                   | _                        | not connected                                 |

| n.c.                    | 2   | -    | -                   | _                        | not connected                                 |

| XDA0                    | 3   | 0    | М                   | RAM                      | output address lines                          |

| XDA1                    | 4   | 0    | М                   |                          |                                               |

| XDA2                    | 5   | 0    | М                   |                          |                                               |

| V <sub>DDD(pad6)</sub>  | 6   | -    | -                   | _                        | digital peripheral supply voltage 6           |

| DGND1                   | 7   | -    | -                   | _                        | digital ground 1                              |

| XDA3                    | 8   | 0    | М                   | RAM                      | output address lines                          |

| XDA4                    | 9   | 0    | М                   |                          |                                               |

| XDA5                    | 10  | 0    | М                   |                          |                                               |

| XDA6                    | 11  | 0    | М                   |                          |                                               |

| XDA7                    | 12  | 0    | М                   |                          |                                               |

| XDA8                    | 13  | 0    | М                   |                          |                                               |

| XDA9                    | 14  | 0    | М                   |                          |                                               |

| XDA10                   | 15  | 0    | М                   |                          |                                               |

| XDA11                   | 16  | 0    | М                   |                          |                                               |

| DGND2                   | 17  | _    | _                   | _                        | digital ground 2                              |

| XRAS                    | 18  | 0    | Н                   | RAM                      | row address strobe output (active LOW)        |

| XCAS                    | 19  | 0    | Н                   |                          | column address strobe output (active LOW)     |

| XWR                     | 20  | 0    | Н                   |                          | write enable output (active LOW)              |

| XDD0                    | 21  | I/O  | M/T                 | RAM                      | data bus input/output                         |

| XDD1                    | 22  | I/O  | M/T                 |                          |                                               |

| V <sub>DDD(core1)</sub> | 23  | -    | _                   | _                        | digital core supply voltage 1                 |

| DGND3                   | 24  | -    | _                   | _                        | digital ground 3                              |

| XDD2                    | 25  | I/O  | M/T                 | RAM                      | data bus input/output                         |

| XDD3                    | 26  | I/O  | M/T                 |                          |                                               |

| XDD4                    | 27  | I/O  | M/T                 |                          |                                               |

| XDD5                    | 28  | I/O  | M/T                 |                          |                                               |

| XDD6                    | 29  | I/O  | M/T                 |                          |                                               |

| XDD7                    | 30  | I/O  | M/T                 |                          |                                               |

| V <sub>DDD(pad7)</sub>  | 31  | _    | _                   | _                        | digital peripheral supply voltage 7           |

| DGND4                   | 32  | _    | _                   | _                        | digital ground 4                              |

| SCKI1                   | 33  | I    | С                   | I <sup>2</sup> S-bus I/O | I <sup>2</sup> S-bus bit clock input          |

| WSI1                    | 34  | I    | С                   |                          | I <sup>2</sup> S-bus word select strobe input |

| SYMBOL                 | PIN      | TYPE   | DRIVE/<br>THRESHOLD | GROUPING                   | DESCRIPTION                                                                                                               |

|------------------------|----------|--------|---------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------|

| n.c.                   | 35 to 38 | -      | _                   | _                          | not connected                                                                                                             |

| SDI1                   | 39       | I      | С                   | I <sup>2</sup> S-bus I/O   | data input from CD engine                                                                                                 |

| n.c.                   | 40       | 0      | М                   |                            | not connected                                                                                                             |

| SFSY                   | 41       | I/O    | L/C                 | subcode I/O                | 3-wire subcode sync input/output                                                                                          |

| RCK                    | 42       | I/O    | L/C                 |                            | 3-wire subcode clock input/output                                                                                         |

| SUBI                   | 43       | I      | С                   |                            | Q and R-W subcode input                                                                                                   |

| n.c.                   | 44       | 0      | L                   |                            | not connected                                                                                                             |

| CFLG                   | 45       | I      | С                   | I <sup>2</sup> S-bus input | CD error corrector flags and absolute time sync                                                                           |

| C2P0                   | 46       | I      | С                   |                            | CD C2 error correction flag input for ERCO                                                                                |

| DGND5                  | 47       | -      | _                   | _                          | digital ground 5                                                                                                          |

| IECO                   | 48       | 0      | М                   | multimedia                 | IEC 958 output                                                                                                            |

| MCK                    | 49       | I/O    | M/C                 | multimedia<br>output       | 256f <sub>s</sub> or 384f <sub>s</sub> clock for multimedia master clock/IEC 958 clock or divided system clock for CD-DSP |

| SCK2                   | 50       | I/O    | L/C                 | multimedia                 | I <sup>2</sup> S-bus bit clock input/output                                                                               |

| WS2                    | 51       | I/O    | L/C                 |                            | I <sup>2</sup> S-bus word select strobe input/output                                                                      |

| SDO2                   | 52       | 0      | М                   |                            | I <sup>2</sup> S-bus data output to DAC/video decoder                                                                     |

| GND                    | 53       | -      | _                   | _                          | ground                                                                                                                    |

| CROUT                  | 54       | 0      | crystal pad         | crystal oscillator         | crystal oscillator output                                                                                                 |

| CRIN                   | 55       | I      | crystal pad         |                            | crystal oscillator/clock input                                                                                            |

| V <sub>DDA</sub>       | 56       | -      | _                   | _                          | analog supply voltage                                                                                                     |

| I <sub>ref</sub>       | 57       | analog | current input       | clock generator            | VCO reference current                                                                                                     |

| POR                    | 58       | I      | Schmitt trigger     | system                     | power-on reset (active LOW)                                                                                               |

| TEST1                  | 59       | I      | С                   | test                       | mode control input test pins                                                                                              |

| TEST2                  | 60       | I      | С                   |                            |                                                                                                                           |

| RESET                  | 61       | I      | Schmitt trigger     | host                       | ATAPI bus reset input from host (active LOW)                                                                              |

| DD7                    | 62       | I/O    | AL/T                | host                       | data bus input/output                                                                                                     |

| DD8                    | 63       | I/O    | AL/T                |                            |                                                                                                                           |

| DD6                    | 64       | I/O    | AL/T                |                            |                                                                                                                           |

| V <sub>DDD(pad1)</sub> | 65       | -      | _                   | _                          | digital peripheral supply voltage 1                                                                                       |

| DGND6                  | 66       | -      | _                   | _                          | digital ground 6                                                                                                          |

| DD9                    | 67       | I/O    | AL/T                | host                       | data bus pin order of ATAPI interface matches                                                                             |

| DD5                    | 68       | I/O    | AL/T                |                            | the pinning of the 40-way IDE connector (slew rate limiting by control of drive capability into                           |

| DD10                   | 69       | I/O    | AL/T                |                            | capacitive load of ATA bus)                                                                                               |

| DD4                    | 70       | I/O    | AL/T                |                            |                                                                                                                           |

| SYMBOL                 | PIN      | ТҮРЕ | DRIVE/<br>THRESHOLD | GROUPING | DESCRIPTION                                                                                     |

|------------------------|----------|------|---------------------|----------|-------------------------------------------------------------------------------------------------|

| n.c.                   | 71 to 74 | _    | _                   | _        | not connected                                                                                   |

| DD11                   | 75       | I/O  | AL/T                | host     | data bus; pin order of ATAPI interface matches                                                  |

| DD3                    | 76       | I/O  | AL/T                |          | the pinning of the 40-way IDE connector (slew rate limiting by control of drive capability into |

| DD12                   | 77       | I/O  | AL/T                |          | capacitive load of ATA bus)                                                                     |

| DD2                    | 78       | I/O  | AL/T                |          |                                                                                                 |

| DD13                   | 79       | I/O  | AL/T                |          |                                                                                                 |

| DD1                    | 80       | I/O  | AL/T                |          |                                                                                                 |

| DD14                   | 81       | I/O  | AL/T                |          |                                                                                                 |

| DD0                    | 82       | I/O  | AL/T                |          |                                                                                                 |

| DD15                   | 83       | I/O  | AL/T                |          |                                                                                                 |

| DMARQ/<br>DMACK        | 84       | 0    | AL                  | host     | DMA request/SCSI DMA acknowledge output (active LOW)                                            |

| DGND7                  | 85       | _    | -                   | _        | digital ground 7                                                                                |

| V <sub>DDD(pad2)</sub> | 86       | _    | -                   | _        | digital peripheral supply voltage 2                                                             |

| DIOW                   | 87       | I    | L/T                 | host     | write cycle write enable/control register write input (active LOW)                              |

| DIOR                   | 88       | I    | L/T                 | host     | read cycle read enable/control register read input (active LOW)                                 |

| IORDY                  | 89       | 0    | AH                  | host     | device is ready to transfer data output<br>(active LOW)                                         |

| DMACK/<br>DMARQ        | 90       | I    | Т                   | host     | DMA acknowledge (active LOW)/SCSI DMA request input                                             |

| INTRQ                  | 91       |      | A                   | host     | host interrupt request (NB 3-state output)                                                      |

| DGND8                  | 92       | _    | -                   | _        | digital ground 8                                                                                |

| V <sub>DDD(pad3)</sub> | 93       | _    | -                   | _        | digital peripheral supply voltage 3                                                             |

| IOCS16                 | 94       | 0    | AH                  | host     | I/O port is 16-bit output (active LOW)                                                          |

| DA1/DBWR               | 95       | I/O  | L/T                 | host     | address wire 1/DMA from generic interface is output from the SAA7381 (active LOW)               |

| PDIAG                  | 96       | I/O  | AL/T                | host     | ATAPI passed diagnostics input/output (active LOW)                                              |

| DA0                    | 97       | I/O  | L/T                 | host     | address wire 0 input/output                                                                     |

| DA2/DBRD               | 98       | I/O  | L/T                 | host     | address wire 2/DMA from generic interface is input to the SAA7381 (active LOW)                  |

| CS0/<br>SCSICS         | 99       | I/O  | L/T                 | host     | chip select 1FX/generic interface chip select (active LOW)                                      |

| CS1                    | 100      | I/O  | L/T                 | host     | chip select 3FX input/output (active LOW)                                                       |

| DASP                   | 101      | I/O  | AH/T                | host     | device active slave present input/output (active LOW)                                           |

| INT2                   | 102      | 0    | L                   | sub-CPU  | sub-CPU interrupt output from the SAA7381<br>drive block and UART                               |

| SYMBOL                  | PIN        | TYPE | DRIVE/<br>THRESHOLD | GROUPING | DESCRIPTION                                                       |

|-------------------------|------------|------|---------------------|----------|-------------------------------------------------------------------|

| DGND9                   | 103        | _    | _                   | _        | digital ground 9                                                  |

| V <sub>DDD(pad4)</sub>  | 104        | _    | _                   | _        | digital peripheral supply voltage 4                               |

| COMACK                  | 105        | Ι    | С                   | UART     | command acknowledge/transmit flow control input                   |

| COMCLK                  | 106        | 0    | L                   | UART     | serial data clock for synchronous mode output                     |

| n.c.                    | 107 to 110 | -    | -                   | _        | not connected                                                     |

| COMOUT                  | 111        | 0    | L                   | UART     | transmit data output                                              |

| COMIN                   | 112        | Ι    | С                   | UART     | receive data input                                                |

| COMSYNC                 | 113        | I    | С                   | UART     | basic engine synchronization input                                |

| SYSSYNC                 | 114        | Ι    | С                   | UART     | basic engine synchronization input                                |

| SCCLK                   | 115        | 0    | М                   | sub-CPU  | sub-CPU clock output                                              |

| RD                      | 116        | I    | Т                   | sub-CPU  | sub-CPU read enable (active LOW)                                  |

| WR/R/W                  | 117        | I    | т                   | sub-CPU  | sub-CPU write enable/and read/write control input (active LOW)    |

| INT                     | 118        | 0    | L                   | sub-CPU  | sub-CPU interrupt request output from host interface (active LOW) |

| SRST                    | 119        | 0    | L                   | sub-CPU  | sub-CPU reset output                                              |

| SCA0/SCD0               | 120        | I/O  | L/T                 | sub-CPU  | multiplexed address/data lines                                    |

| SCA1/SCD1               | 121        | I/O  | L/T                 |          |                                                                   |

| DGND10                  | 122        | -    | -                   | _        | digital ground 10                                                 |

| V <sub>DDD(pad5)</sub>  | 123        | -    | -                   | _        | digital peripheral supply voltage 6                               |

| SCA2/SCD2               | 124        | I/O  | L/T                 | sub-CPU  | multiplexed address/data lines                                    |

| SCA3/SCD3               | 125        | I/O  | L/T                 |          |                                                                   |

| SCA4/SCD4               | 126        | I/O  | L/T                 |          |                                                                   |

| SCA5/SCD5               | 127        | I/O  | L/T                 |          |                                                                   |

| SCA6/SCD6               | 128        | I/O  | L/T                 |          |                                                                   |

| SCA7/SCD7               | 129        | I/O  | L/T                 |          |                                                                   |

| DGND11                  | 130        | _    | -                   | _        | digital ground 11                                                 |

| V <sub>DDD(core2)</sub> | 131        | _    | _                   | _        | digital core supply voltage 2                                     |

| ALE                     | 132        | Ι    | Т                   | sub-CPU  | demultiplex enable input for lower address lines                  |

| PSEN                    | 133        | I    | Т                   | sub-CPU  | program store enable (active LOW)                                 |

| SCA15                   | 134        | Ι    | Т                   | sub-CPU  | upper address lines input                                         |

| SCA14                   | 135        | I    | Т                   |          |                                                                   |

| SCA13                   | 136        | Ι    | Т                   |          |                                                                   |

| SCA12                   | 137        | I    | Т                   |          |                                                                   |

| DGND12                  | 138        | _    | _                   | _        | digital ground 12                                                 |

| SYMBOL | PIN | TYPE | DRIVE/<br>THRESHOLD | GROUPING | DESCRIPTION               |

|--------|-----|------|---------------------|----------|---------------------------|

| SCA11  | 139 | I    | Т                   | sub-CPU  | upper address lines input |

| SCA10  | 140 | I    | Т                   |          |                           |

| SCA9   | 141 | I    | Т                   |          |                           |

| SCA8   | 142 | I    | Т                   |          |                           |

| n.c.   | 143 | _    | _                   | _        | not connected             |

| n.c.   | 144 | _    | _                   | _        | not connected             |

SAA7381

### 6.1 Detailed description of pin functions

Table 1

Q and R-W input/output subcode connections (4 pins)

| SYMBOL | DESCRIPTION             | COMMENT                                                                                                                      |

|--------|-------------------------|------------------------------------------------------------------------------------------------------------------------------|

| SFSY   | 3-wire subcode sync     | input subcode frame sync for receiving 3-wire subcode; output subcode frame sync for transmitting 3-wire subcode             |

| RCK    | 3-wire subcode clock    | output bit clock for receiving 3-wire subcode; input bit clock for transmitting 3-wire subcode                               |

| SUBI   | Q and R-W subcode input | configurable for 3-wire or Philips V4 subcode mode; can use either RCK or WSI1 as clock references with appropriate dividers |

Table 2

I<sup>2</sup>S-bus multimedia audio output (5 pins)

| SYMBOL | DESCRIPTION                                                                                                                           | COMMENT                                                                                                                                                                                                                                                                 |

|--------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

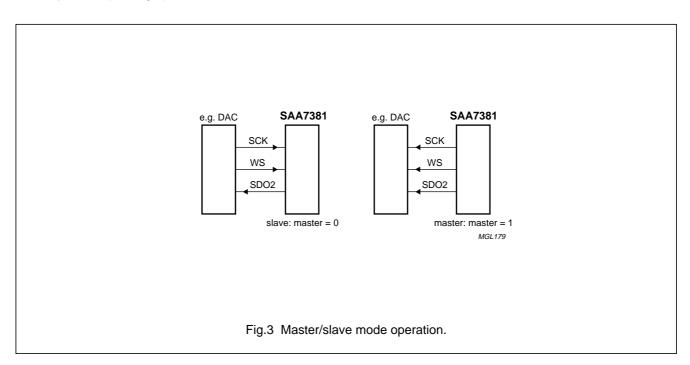

| МСК    | 256f <sub>s</sub> or 384f <sub>s</sub> clock for<br>multimedia master<br>clock/IEC 958 clock or<br>divided system clock for<br>CD-DSP | Clock reference input pin when interface is in a master mode; a<br>programmable divider is provided. This pin is also configurable as a<br>programmable clock output intended as a clock reference for a<br>CD-DSP. Should be pulled up if not in use.                  |

| SCK2   | I <sup>2</sup> S-bus bit clock                                                                                                        | This is used for master and slave I <sup>2</sup> S-bus application as both modes are needed. For instance, the Philips multimedia CODEC is an I <sup>2</sup> S-bus slave, hence this must be a master interface. When driving some DACs, this interface can be a slave. |

| WS2    | I <sup>2</sup> S-bus left/right strobe                                                                                                | word select strobe either master or slave                                                                                                                                                                                                                               |

| SDO2   | I <sup>2</sup> S-bus data to DAC/video decoder                                                                                        | I <sup>2</sup> S-bus multimedia data                                                                                                                                                                                                                                    |

| IECO   | IEC 958 output                                                                                                                        | the IEC 958 output combines multimedia data and Q-W subcode                                                                                                                                                                                                             |

Table 3

I<sup>2</sup>S-bus connections to CD engine (6 pins)

| SYMBOL | DESCRIPTION                                     | COMMENT                                                                                                                                                                                                                     |

|--------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCKI1  | I <sup>2</sup> S-bus bit clock                  | this is a separate clock to the multimedia bit clock as this rate is derived from the disc linear velocity                                                                                                                  |

| WSI1   | I <sup>2</sup> S-bus left/right strobe          |                                                                                                                                                                                                                             |

| SDI1   | I <sup>2</sup> S-bus data from CD-DSP           |                                                                                                                                                                                                                             |

| C2P0   | CD C2 error corrector flag<br>from ERCO         | these flags are used to indicate errors from second layer correction to the ERCO                                                                                                                                            |

| CFLG   | CD error corrector flags and absolute time sync | The absolute time sync is used in the CD input process for playing 'Red Book' discs; the error corrector status is also read in from this signal, to provide an indication of C1 and C2 performance for CD-RW applications. |

| Table 4 ATAPI targe | et mode interface |

|---------------------|-------------------|

|---------------------|-------------------|

| ATAPI<br>NAME | ATAPI MEANING                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET         | ATAPI reset signal: the SAA7381 will not recognize a signal assertion shorter than 20 ns as a valid reset signal.                                                                                                                                                                                                                                                                                                 |

| DD0 to DD7    | ATAPI D0 to D7.                                                                                                                                                                                                                                                                                                                                                                                                   |

| DD8 to DD15   | ATAPI D8 to D15: these data bits are only used in accesses to the 16-bit data port.                                                                                                                                                                                                                                                                                                                               |

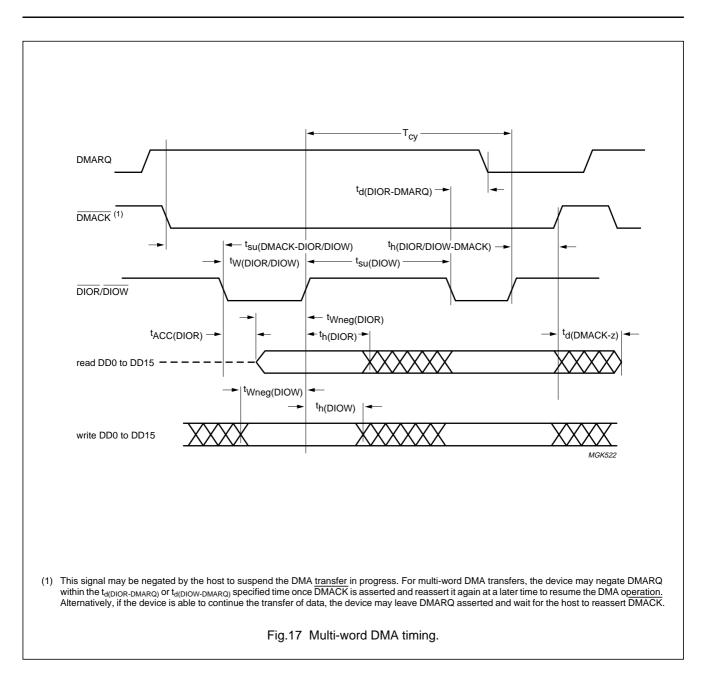

| DMARQ         | DMA request: this signal, used for DMA data transfers between host and device, is asserted by the SAA7381 when it is ready to transfer data to or from the host. The direction of data transfer is controlled by DIOR and DIOW.                                                                                                                                                                                   |

| DMACK         | DMA acknowledge: this signal is used by the host in response to DMARQ to initiate DMA transfers.<br>This signal may be temporarily negated by the host to suspend the DMA transfer in process.                                                                                                                                                                                                                    |

| IOCS16        | ATAPI I/O port is a 16-bit open-drain output: during PIO transfer Modes 0, 1 or 2, IOCS16 indicates to the host system that the 16-bit data port has been addressed and that the device is prepared to send or receive a 16-bit data word.                                                                                                                                                                        |

| IORDY         | ATAPI I/O ready open-drain output: this signal is negated to extend the host transfer cycle of any host register access (read or write) when the SAA7381 is not ready to respond to a data transfer request. This signal is only enabled during DIOR/DIOW cycles to the SAA7381. When IORDY is not active, it is in the high-impedance (undriven) state.                                                          |

| DA0 to DA2    | Address bus (device address).                                                                                                                                                                                                                                                                                                                                                                                     |

| DIOW          | ATAPI write strobe: the rising edge of $\overline{\text{DIOW}}$ latches data from the signals, DD0 to DD7 or DD0 to DD15 into a register or the data port of the SAA7381. The SAA7381 will not act on the data until it is latched.                                                                                                                                                                               |

| DIOR          | ATAPI read strobe: the falling edge of $\overline{\text{DIOR}}$ enables data from a register or data port of the SAA7381 onto the signals, DD0 to DD7 or DD0 to DD15. The rising edge of $\overline{\text{DIOR}}$ latches data at the host and the host will not act on the data until it is latched.                                                                                                             |

| CS0           | ATAPI chip select 0 input: this is the chip select signal from the host used to select the ATA command block registers. This signal is also known as CS1FX.                                                                                                                                                                                                                                                       |

| CS1           | ATAPI chip select 1 input: this is the chip select signal from the host used to select the ATA control block registers. This signal is also known as CS3FX.                                                                                                                                                                                                                                                       |

| INTRQ         | ATAPI interrupt output: this signal is used to interrupt the host system. INTRQ is asserted only when the device has a pending interrupt, the device is selected, and the host has cleared the 'nien' bit in the device control register. If the 'nien' bit is equal to 1, or the device is not selected, this output is in a high-impedance state, regardless of the presence or absence of a pending interrupt. |

| PDIAG         | ATAPI passed diagnostics: this signal shall be asserted by device 1 to indicate to device 0 that it has completed diagnostics.                                                                                                                                                                                                                                                                                    |

| DASP          | ATAPI DASP (device active, device 1 present): this is a time-multiplexed signal which indicates that a device is active, or that device 1 is present. This signal is an open-drain output.                                                                                                                                                                                                                        |

SAA7381

### Table 5 Generic host controller interface

| ATAPI<br>NAME | GENERIC<br>INTERFACE<br>NAME | GENERIC HOST CONTROLLER INTERFACE MEANING                      |  |  |  |

|---------------|------------------------------|----------------------------------------------------------------|--|--|--|

| RESET         | RESET                        | controller reset output                                        |  |  |  |

| DD0 to DD7    | D0 to D7                     | controller DMA path/controller data and control bus (optional) |  |  |  |

| DD8 to DD15   | D8 to D15                    | controller upper DMA path (optional)                           |  |  |  |

| DMARQ         | DMACK                        | DMA acknowledge to controller                                  |  |  |  |

| DMACK         | DMARQ                        | DMA request from controller                                    |  |  |  |

| DA1           | DBWR                         | DMA bus write to controller                                    |  |  |  |

| DA2           | DBRD                         | DMA bus read from controller                                   |  |  |  |

| CS0           | SCSICS                       | controller chip select output for sub-CPU read/write cycles    |  |  |  |

### Table 6Miscellaneous pins

| SYMBOL           | DESCRIPTION                    | COMMENT              |

|------------------|--------------------------------|----------------------|

| CRIN             | crystal oscillator/clock input | -                    |

| CROUT            | crystal oscillator output      | -                    |

| I <sub>ref</sub> | VCO reference current          | clock PLL multiplier |

| POR              | power-on reset pin             | -                    |

| TEST1 and TEST2  | mode control test pins         | -                    |

### Table 7 Sub-CPU interface pins

| SYMBOL                        | DESCRIPTION                                                          | COMMENT                                                                                                                                                                                         |

|-------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRST                          | sub-CPU reset                                                        | active HIGH reset if XDD7 is pulled LOW during power-on reset;<br>active LOW reset if XDD7 is pulled HIGH during power-on reset                                                                 |

| INT                           | sub-CPU interrupt request<br>output from host interface              | open-drain sub-processor interrupt from host interface                                                                                                                                          |

| INT2                          | sub-CPU interrupt output<br>from the SAA7381 drive<br>block and UART | open-drain sub-processor interrupt from drive and UART                                                                                                                                          |

| SCCLK                         | sub-CPU clock out                                                    | -                                                                                                                                                                                               |

| RD                            | sub-CPU read enable                                                  | sub-CPU read enable strobe; if grounded permanently, the $\overline{\rm WR}$ signal will act as read/write control input                                                                        |

| WR/R/W                        | sub-CPU write enable/<br>read/write control                          | write enable; alternative usage is read/write if $\overline{RD}$ is held LOW at all times; $\overline{WR}$ has priority over $\overline{RD}$ at all times                                       |

| ALE                           | demultiplex enable input for lower address lines                     | while HIGH, the lower address bits are latched from<br>SCD0 to SCD7; should be used with a Schmitt trigger input to<br>avoid false latching due to ground bounce on the<br>8051 microcontroller |

| PSEN                          | program store enable                                                 | this pin should be tied high using a 10 k $\Omega$ resistor                                                                                                                                     |

| SCD0 to SCD7/<br>SCA0 to SCA7 | sub-CPU data bus<br>multiplexed/low address bus                      | -                                                                                                                                                                                               |

| SCA8 to SCA15                 | sub-CPU address high bits                                            | -                                                                                                                                                                                               |

### SAA7381

### **Table 8**RAM interface pins

| SYMBOL        | DESCRIPTION                            | COMMENT                             |

|---------------|----------------------------------------|-------------------------------------|

| XDA0 to XDA11 | RAM address bits, multiplexed for DRAM | up to 16 Mbytes DRAM only supported |

| XRAS          | DRAM row address strobe                |                                     |

| XCAS          | DRAM column address strobe             |                                     |

| XWR           | RAM write enable                       |                                     |

| XDD0 to XDD7  | RAM data bus                           |                                     |

#### Table 9 Basic engine interface

| SYMBOL  | DESCRIPTION                               | COMMENT                                                      |  |  |

|---------|-------------------------------------------|--------------------------------------------------------------|--|--|

| SYSSYNC | basic engine synchronization input        | generate interrupts on rising and/or falling edges           |  |  |

| COMSYNC | basic engine synchronization input        | generate interrupts on rising and/or falling edges           |  |  |

| COMIN   | receive data                              | -                                                            |  |  |

| COMOUT  | transmit data                             | -                                                            |  |  |

| COMCLK  | serial data clock for synchronous mode    | -                                                            |  |  |

| COMACK  | command acknowledge/transmit flow control | must be HIGH for synchronous mode to transmit next data byte |  |  |

### 7 FUNCTIONAL DESCRIPTION

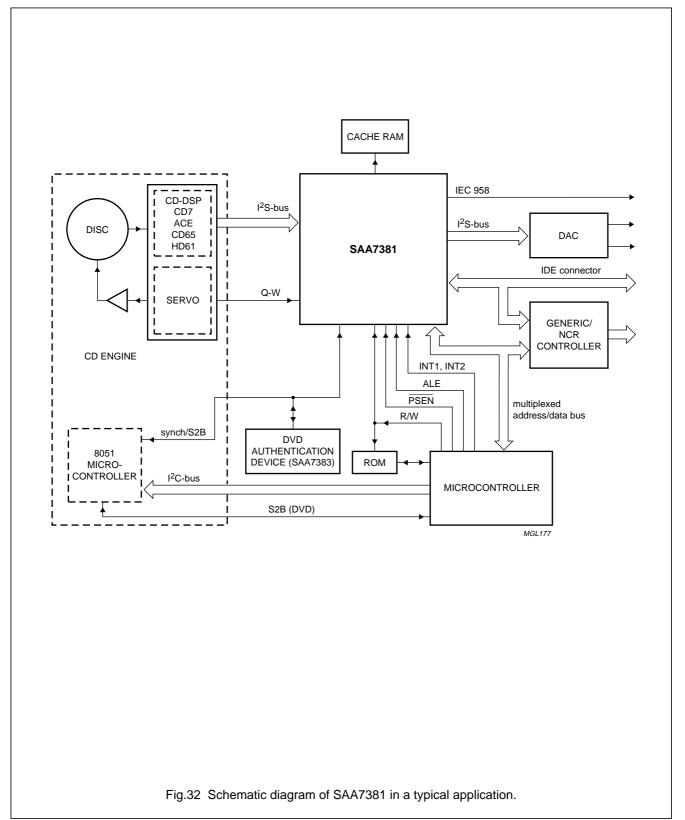

The SAA7381 device consists of a number of main functional units; a CD engine interface, a multimedia block, a microcontroller interface, an error detection and correction block, a host interface and a memory manager. There are also several smaller blocks including a clock control block and a UART for communication with the CD engine. Each block is independently controlled by a dedicated register set. These registers are memory mapped to the sub-CPU to allow for faster access. The external RAM can also be accessed directly from the microcontroller to support scratchpad accesses and thus eliminate the need for further memory devices in the system.

### 7.1 Memory field description

The CD input function of the SAA7381 buffer manager receives the main data stream in  $I^2$ S-bus format from the CD-DSP, performs sync detection and partitions the data into blocks.

It then writes the blocks to the buffer memory and onboard ERCO RAM. Any detected errors are then corrected and over written into the buffer memory.

Memory is segmented and addressable by segment pointers. The segment pointers consist of a block number, offset pointer and byte number within the block. The data within each segment is organised in the same manner (see Table 10).

The arrangement of data within each segment in memory differs from other Philips devices, because of the different error correction processing possibilities within the SAA7381.

Addresses 0 to 2355 are written to memory by the drive processor when enabled.

## SAA7381

Table 10

The memory map of a block in the buffer RAM for standard density mode (see Table 11)

| ADDRESS (OFFSET) | TYPE OF DATA                                                  |

|------------------|---------------------------------------------------------------|

| 0 to 3           | header field                                                  |

| 4 to 2339        | block data field                                              |

| 2340 to 2351     | sync field                                                    |

| 2352             | copy of STAT0                                                 |

| 2353             | copy of STAT1                                                 |

| 2354             | copy of STAT2                                                 |

| 2355             | number of C2 flags in sector (compressed format)              |

| 2356 to 2451     | 96-byte de-interleaved R-W data field                         |

| 2452 to 2463     | 12-byte Q-subcode field                                       |

| 2464 to 2465     | copy of STAT4 field; only valid if ERCO did run on this block |

| 2466 to 2559     | user work space                                               |

### Table 11 Description of Table 10

| DATA             | DESCRIPTION                                                                                                                                                     |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Header field     | The 4-byte header data consists of a 3-byte block address of absolute time (minutes, seconds and frame, bytes 0 to 3). The fourth byte is for the mode of data: |  |  |  |  |

|                  | Mode 0 = zero mode                                                                                                                                              |  |  |  |  |

|                  | Mode 1 = data storage with EDC and ECC                                                                                                                          |  |  |  |  |

|                  | Mode 2 = data storage                                                                                                                                           |  |  |  |  |

| Block data field | in the CD-ROM mode the block data consists of 2048 bytes of user data and 288 bytes of auxiliary data                                                           |  |  |  |  |

|                  | User data:                                                                                                                                                      |  |  |  |  |

|                  | Mode 0= all 2048 bytes in user data are zero                                                                                                                    |  |  |  |  |

|                  | Mode 1= all 2048 bytes are available to the user                                                                                                                |  |  |  |  |

|                  | Mode 2= all 2048 bytes are available to the user                                                                                                                |  |  |  |  |

|                  | Auxiliary data:                                                                                                                                                 |  |  |  |  |

|                  | Mode 0= all 288 bytes in Aux data are zero                                                                                                                      |  |  |  |  |

|                  | Mode 1= the Aux field is in accordance with the EDC and ECC specification                                                                                       |  |  |  |  |

|                  | Mode 2= all 288 bytes are available to the user                                                                                                                 |  |  |  |  |

| Sync field       | The 12-byte sync field is the next segment in memory. All bytes in the sync field are FFH, except the first and last bytes which are \$00.                      |  |  |  |  |

SAA7381

| DATA                                             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Number of C2 flags in sector (compressed format) | While storage of C2 flag positions is not possible as a consequence of the architecture of the SAA7381, a count of the number of flags seen per block is made in a single-byte counter. This counter packs the possibly 12-bit count into a single byte in the following way, at the expense of resolution in the count values for large counts.                                                                                    |  |  |

|                                                  | C2count_val = count (5 down to 0) $\times$ [4 ^ count (7 down to 6)], the resolution of the count is therefore:                                                                                                                                                                                                                                                                                                                     |  |  |

|                                                  | C2count_val 0 to 63: counter resolution = 1                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|                                                  | C2count_val 64 to 255: counter resolution = 4                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|                                                  | C2count_val 256 to 1023: counter resolution = 16                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|                                                  | C2count_val 1024 to 4095: counter resolution = 64                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 96-byte de-interleaved<br>R-W data field         | Written to memory by the automatic Q-channel copy process (copy2 channel). If the copy process is not enabled, these fields are not written (see Section 7.3.5). These bytes may either be R-W de-interleaved or presented as raw Q-W subcode bytes. If the copy2 interleaving mode is set to <b>raw</b> , interleaved copying is still required as the subcode temporary holding buffer has Q bytes interspersed with the raw R-W. |  |  |

| 12-byte Q-subcode field                          | As above: these will not be separated out if the copy2 interleaving option is set to <b>raw</b> .                                                                                                                                                                                                                                                                                                                                   |  |  |

| 2 copies of STAT4 field                          | Address 2465 and 2466 are copies of the STAT4 register written by the ERCO when<br>enabled. This allows the user to determine if the STAT4 register has been written to by the<br>ERCO. If seg2465 = seg2466 then STAT4 definitely has not been written by the ERCO.<br>If seg2465 $\neq$ seg2466 then STAT4 probably has not been written by the ERCO.                                                                             |  |  |

|                                                  | Via direct access to buffer memory, the sub-CPU will be able to look at all of the blocks so far corrected, to check their status, in a background task.                                                                                                                                                                                                                                                                            |  |  |

|                                                  | ERCO failures do not have to be dealt with immediately, as the status of every block loaded in to RAM is stored with that block, and it is not overwritten until the RAM block is filled with new data from CD input.                                                                                                                                                                                                               |  |  |

|                                                  | The error corrector will be controlled additionally to permit the use of single pass P-Q or only EDC operation to allow for greater than $n = 14$ operation of the ERCO.                                                                                                                                                                                                                                                            |  |  |

|                                                  | The ERCO status will be copied into the RAM along with the data. This is possible because the RAM now has spare capacity to store the information, as part of the change from linear to segment/offset addressing.                                                                                                                                                                                                                  |  |  |

|                                                  | It is possible to program transfers into RAM of more than one block without processor intervention. It is also possible to continually loop on the same buffer area of RAM, by not altering the reload register values when the reload interrupt occurs.                                                                                                                                                                            |  |  |

### 7.1.1 DVD-ROM MEMORY FIELD INFORMATION

The buffer arrangement for DVD usage is basically the same (data followed by flags) but the size of the block data differs, and the ERCO flags are at a different offset, and as the ERCO is not in use, the flags relating to ERCO performance will not be valid.

SAA7381

### 7.2 CD input control registers

The CD input process is intended to be as automated as possible. Data is read in from the front end, descrambled if in CD-ROM mode and then written to RAM. The registers that control the address of where the data is written to are in the memory processor block.

The input data is synchronized, decoded and written to the buffer RAM. The input data format is software programmable.

The synchronization is performed by using a sync detector and a sync interpolator. The sync detector can detect CD-ROM syncs and syncs from the CFLG pin, for use with Red Book, audio and for DVD. When no sync is found, it is optionally interpolated.

After decoding, each full sector of data (2352 bytes) comprising sync, header and sub-header is written to the buffer RAM. The R-W and Q subcode is added by a software-initiated automatic block copy process.

7.2.1 REGISTERS ASSOCIATED WITH DATA IN PROCESS

Table 12 IFCONFIG (write only; address FF10H) (see Table 13)

| BIT 7    | BIT 6  | BIT 5  | BIT 4  | BIT 3    | BIT 2    | BIT 1       | BIT 0       |

|----------|--------|--------|--------|----------|----------|-------------|-------------|

| ipconfig | ckdiv1 | ckdiv0 | subsel | modulo 1 | modulo 0 | config swap | config wclk |

### Table 13 Description of the IFCONFIG register bits

| BIT     | NAME         | VALUE | MEANING                                                             |  |

|---------|--------------|-------|---------------------------------------------------------------------|--|

| 7       | ipconfig     | 0     | I <sup>2</sup> S-bus mode                                           |  |

|         |              | 1     | EIAJ serial interface mode                                          |  |

| 6 and 5 | ckdiv1 and   | 00    | oversample, bit clock division ratio = 2                            |  |

|         | ckdiv0       | 01    | oversample, bit clock division ratio = 4                            |  |

|         |              | 10    | oversample, bit clock division ratio = 8                            |  |

|         |              | 11    | bit clock division ratio = 1 (no division)                          |  |

| 4       | subsel       | 0     | both copies of sub-header contribute to STAT1/sh0err to sh3err      |  |

|         |              | 1     | first copy only of sub-header contributes to STAT1/sh0err to sh3err |  |

| 3 and 2 | modulo 1 and | 00    | modulo count 2352                                                   |  |

|         | modulo 0     | 01    |                                                                     |  |

|         |              | 10    | modulo count 2064                                                   |  |

|         |              | 11    | modulo count 2064, but do not count bytes with flag = 1             |  |

| 1       | config swap  | 0     | the received data from the CD-DSP or drive FIFO is not swapped      |  |

|         |              | 1     | the received data from the CD-DSP or drive FIFO is swapped          |  |

| 0       | config wclk  | 0     | the internal 'irclk' is not inverted                                |  |

|         |              | 1     | the internal 'irclk' is inverted                                    |  |

SAA7381

| ADDRESS | NAME           | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|---------|----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| FF21H   | DRIVECURSEG-L  | s7    | s6    | s5    | s4    | s3    | s2    | s1    | s0    |

| FF20H   | DRIVECURSEG-H  | incen | wren  | _     | s12   | s11   | s10   | s9    | s8    |

| FF60H   | DRIVECURCOUNT  | c7    | c6    | c5    | c4    | c3    | c2    | c1    | c0    |

| FF27H   | DRIVENEXTSEG-L | s7    | s6    | s5    | s4    | s3    | s2    | s1    | s0    |

| FF26H   | DRIVENEXTSEG-H | incen | wren  | _     | s12   | s11   | s10   | s9    | s8    |

| FF61H   | DRIVENEXTCOUNT | c7    | c6    | c5    | c4    | c3    | c2    | c1    | c0    |

| FF23H   | DRIVEPREVSEG-L | s7    | s6    | s5    | s4    | s3    | s2    | s1    | s0    |

| FF22H   | DRIVEPREVSEG-H | incen | wren  | -     | s12   | s11   | s10   | s9    | s8    |

| FF24H   | DRIVEOFFSET-H  | s7    | s6    | s5    | s4    | s3    | s2    | s1    | s0    |

| FF25H   | DRIVEOFFSET-L  | s7    | s6    | s5    | s4    | s3    | s2    | s1    | s0    |

Table 14 CD input control registers (see Table 15)

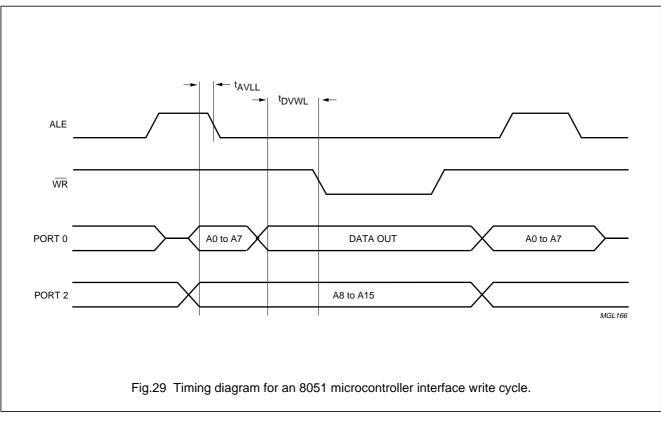

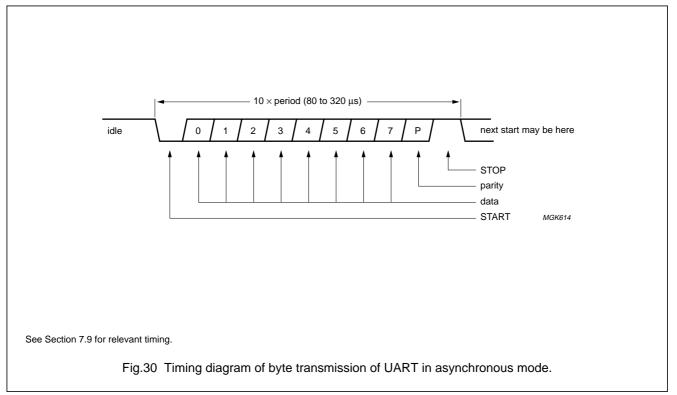

There are two sets of address registers, one giving the current (DRIVECURSEG) number of the segment being filled and a segment/block counter. The other set contains the values (DRIVENEXTSEG) to use on completion of the current group of blocks being filled or emptied (in CD-R). The DRIVEPREVSEG register is loaded with the value of the DRIVECURSEG register at the end of each CD-ROM block.