## **Signetics**

#### **Linear Products**

#### DESCRIPTION

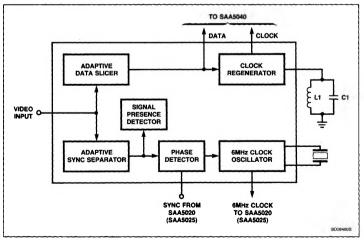

The SAA5030 is a monolithic bipolar integrated circuit used for teletext video processing. It is one of a package of four circuits to be used in teletext TV data systems. The SAA5030 extracts data and data clock information from the television composite video signal and feeds this to the Acquisition and Control Circuit SAA5040. A 6MHz crystal-controlled, phase-locked oscillator is incorporated which drives the Timing Chain Circuit SAA5020. An adaptive sync separator is also provided which derives line and field sync pulses from the input video in order to synchronize the timing chain.

## SAA5030 Teletext Video Processor

Product Specification

#### FEATURES

- Slices digital data embedded in the composite video signal

- Generates a synchronized clock for the sliced data

- Generates a system display clock, locked with the incoming video signal

- On-chip signal quality detector

- On-chip adaptive sync separator

#### APPLICATIONS

- Teletext

- Data slicer

- Phase-locking with incoming video (when used with SAA5025D)

- Telecaptioning

#### ORDERING INFORMATION

| DESCRIPTION        | TEMPERATURE RANGE | ORDER CODE |

|--------------------|-------------------|------------|

| 24-Pin Plastic DIP | -20°C to +70°C    | SAA5030N   |

#### BLOCK DIAGRAM

#### PIN CONFIGURATION

| N Package    |            |                                                            |  |  |  |

|--------------|------------|------------------------------------------------------------|--|--|--|

| т            |            | 24 C2S                                                     |  |  |  |

|              | CLR 2      | 23 C15                                                     |  |  |  |

| FLR 3        |            | 22 CCLK                                                    |  |  |  |

| GND 4        |            |                                                            |  |  |  |

|              |            | 21 LCLK                                                    |  |  |  |

| PL/C         | BB 5       | 20 CA                                                      |  |  |  |

|              | F6 6       | 19 DATA                                                    |  |  |  |

| т            | CPD 7      | 18 F7                                                      |  |  |  |

|              | F61 8      | 17 Vcc                                                     |  |  |  |

| F6Q 9 16 VI  |            |                                                            |  |  |  |

| PO 10 15 CSS |            |                                                            |  |  |  |

| 1            | AHS 11     | 14 FSST                                                    |  |  |  |

| SI           | NQ 12      | 13 FS                                                      |  |  |  |

|              | -L         |                                                            |  |  |  |

|              |            | CD123205                                                   |  |  |  |

|              | SYMBOL     | DESCRIPTION                                                |  |  |  |

| 1            | TCSP       | To signal presence time<br>constant components             |  |  |  |

| 2            | TCLR       | Line reset time constant                                   |  |  |  |

| 3            | FLR<br>GND | Fast line reset output<br>Ground (0V)                      |  |  |  |

| 5            | PL/CBB     | Sandcastle input                                           |  |  |  |

| 6            | F6         | 6MHz output                                                |  |  |  |

| 7            | TCPD       | To phase detector time<br>constant components              |  |  |  |

| 8            | F6I        | 6MHz crystal oscillator input                              |  |  |  |

| 9            | F6Q        | 6MHz crystal oscillator output                             |  |  |  |

| 10<br>11     | PO         | Picture-on input<br>After-hours sync input                 |  |  |  |

| 12           | SYNQ       | Sync output to TV                                          |  |  |  |

| 13           | FS         | Field sync output                                          |  |  |  |

| 14           | FSST       | Field sync separator timing                                |  |  |  |

| 15<br>16     | CSS<br>VI  | To sync separator capacitor<br>Composite video input       |  |  |  |

| 17           | Vcc        | + 12V supply                                               |  |  |  |

| 18           | F7         | Clock output                                               |  |  |  |

| 19           | DATA       | Data output                                                |  |  |  |

| 20<br>21     | CA<br>LCLK | Clock phase capacitor                                      |  |  |  |

| 21           | CCLK       | Clock regenerating coil<br>To clock pulse timing           |  |  |  |

|              |            | capacitor                                                  |  |  |  |

| 23<br>24     | C1S<br>C2S | Peak detector capacitor pin<br>Peak detector capacitor pin |  |  |  |

|              |            |                                                            |  |  |  |

## SAA5030

#### ABSOLUTE MAXIMUM RATINGS

| SYMBOL           | PARAMETER                                                                 | RATING                      | UNIT        |  |

|------------------|---------------------------------------------------------------------------|-----------------------------|-------------|--|

| V <sub>CC</sub>  | Supply voltage V17-4                                                      | 13.2                        | v           |  |

| Vi<br>Vi<br>Vi   | Input voltages V <sub>5-4</sub><br>V <sub>10-4</sub><br>V <sub>11-4</sub> | 9<br>V <sub>CC</sub><br>7.5 | V<br>V<br>V |  |

| T <sub>STG</sub> | Storage temperature range                                                 | -55 to +150                 | °C          |  |

| T <sub>A</sub>   | Operating ambient temperature range                                       | -20 to +70                  | °C          |  |

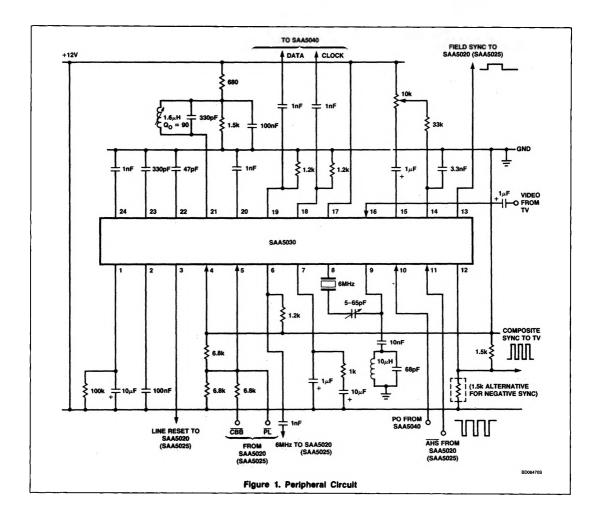

# DC AND AC ELECTRICAL CHARACTERISTICS At $T_A = 25^{\circ}$ C, $V_{CC} = 12V$ , and with external components as shown in Figure 3, unless otherwise stated.

| SYMBOL              | PARAMETER                                                                                                                                                   | LIMITS |      |      |        |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|--------|

|                     |                                                                                                                                                             | Min    | Тур  | Max  | UNIT   |

| V <sub>CC</sub>     | Supply voltage                                                                                                                                              | 10.8   | 12.0 | 13.2 | v      |

| lcc                 | Supply current (V <sub>CC</sub> = 12.0V)                                                                                                                    |        | 110  |      | mA     |

| Video input         | and sync separator                                                                                                                                          |        |      |      |        |

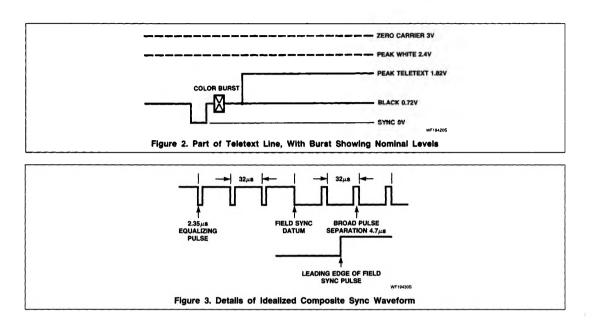

| V16VIDEO(P-P)       | Video input amplitude (sync to white); see Figure 2                                                                                                         | 2.0    | 1.4  | 3.0  | V      |

| Z <sub>S</sub>      | Source impedance, f = 100kHz                                                                                                                                |        |      | 250  | Ω      |

| V16SYNC(P-P)        | Sync amplitude                                                                                                                                              | 0.07   | 0.7  | 1.0  | V      |

| to                  | Delay through sync separator                                                                                                                                |        | 0.5  |      | μs     |

| t <sub>D</sub>      | Delay between field sync datum at Pin 12 and the leading edge<br>of separated field sync at Pin 13 <sup>1</sup> (see Figure 2)                              | 32     | 48   | 62   | μs     |

| Field sync o        | utput                                                                                                                                                       |        |      | •    |        |

| V <sub>OL</sub>     | V <sub>O</sub> (Low) (I <sub>13</sub> = 20μA)                                                                                                               |        |      | 0.5  | V      |

| V <sub>OH</sub>     | V <sub>O</sub> (High) (-I <sub>13</sub> = 100μA)                                                                                                            | 2.4    |      |      | v      |

| f <sub>F6</sub>     | Frequency                                                                                                                                                   |        | 6.0  |      | MHz    |

|                     | Holding range                                                                                                                                               | 1.5    | 3.0  |      | kHz    |

|                     | Catching range                                                                                                                                              | 1.5    | 3.0  |      | kHz    |

|                     | Control sensitivity of phase detector measured as voltage at Pin<br>7 with respect to phase difference between separated syncs<br>and phase-locked pulse PL |        | 0.3  |      | mV/ns  |

|                     | Control sensitivity of oscillator measured as change in 6MHz<br>phase shift from Pin 8 to Pin 9 with respect to voltage at<br>Pin 7                         |        | 2    |      | deg/mV |

|                     | Gain of sustaining amplifier, $V_{9-8}$ measured with input voltage of 100mV_{P,P} and phase detector immobilized                                           | 2.5    |      |      | V/V    |

|                     | Output voltage of 6MHz signal at Pin 6, measured into 20pF load capacitance; peak-to-peak value                                                             |        | 5.5  |      | v      |

| t <sub>R</sub> , t⊨ | Output rise and fall times at Pin 6 into 20pF load                                                                                                          |        |      | 30   | ns     |

## SAA5030

# DC AND AC ELECTRICAL CHARACTERISTICS (Continued) At T<sub>A</sub> = 25°C, V<sub>CC</sub> = 12V, and with external components as shown in Figure 3, unless otherwise stated.

| 0/01001                         |                                                                                                                                                      | LIMITS   |            |          | 1                |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------|----------|------------------|

| SYMBOL                          | PARAMETER                                                                                                                                            |          | Тур        | Max      | UNIT             |

| Data slicer                     | and clock regenerator                                                                                                                                |          |            |          |                  |

|                                 | Teletext data input amplitude, Pin 16 (see Figure 2);<br>peak-to-peak value <sup>2</sup>                                                             |          | 1.1        |          | v                |

|                                 | Data input amplitude at Pin 16 required to enable amplitude gate flip-flop; peak-to-peak value                                                       |          | 0.46       |          | v                |

|                                 | Attack rate, measured at Pins 23 and 24 with a step to Pin 16<br>(positive)<br>(negative)                                                            |          | 15<br>9    |          | V/μs<br>V/μs     |

|                                 | Decay rate, measured at Pins 23 and 24 with a step input to Pin 16                                                                                   | 48       | 100        | 144      | mV/µs            |

|                                 | Width of clock coil drive pulses from Pin 21 when clock<br>amplitude is not being controlled <sup>3</sup>                                            |          | 40         |          | ns               |

|                                 | Clock hangover measured at Pin 18 as the time the clock coil continues ringing after the end of data <sup>4</sup>                                    | 20       |            |          | Clock<br>Periods |

|                                 | Clock and data output voltages at Pins 18 and 19 measured<br>with 20pF load capacitance; peak-to-peak value                                          |          | 5.5        |          | v                |

| t <sub>R</sub> , t <sub>F</sub> | Output rise and fall times at Pins 18 and 19 into 20pF loads                                                                                         |          |            | 30       | ns               |

| Sandcastle                      | Input                                                                                                                                                |          |            |          |                  |

|                                 | Sandcastle detector thresholds, Pin 5<br>phase-locked pulse (PL) on<br>phase-locked pulse off<br>blanking pulse (CBB) on<br>blanking pulse off       | 2<br>4.5 |            | 3<br>5.5 |                  |

| Dual polarit                    | y sync buffer                                                                                                                                        |          |            |          |                  |

|                                 | After-hours sync (AHS) pulse input Pin 11<br>threshold for AHS active<br>threshold for AHS off                                                       | 1.0      |            | 2.0      | v<br>v           |

|                                 | Picture-on (PO) input, Pin 10<br>threshold for PO active<br>threshold for PO off                                                                     | 1.0      |            | 2.0      | v<br>v           |

|                                 | Sync output, Pin 12<br>AHS output with Pin $10 < 1V^5$ ; peak-to-peak value<br>composite sync output with Pin $10 > 2V^5$ , 6, peak-to-peak<br>value |          | 0.7<br>0.7 | 1        | v<br>v           |

|                                 | output current                                                                                                                                       |          |            | 3        | mA               |

### SAA5030

## DC AND AC ELECTRICAL CHARACTERISTICS (Continued) At T<sub>A</sub> = 25°C, V<sub>CC</sub> = 12V, and with external components as shown in Figure 3, unless otherwise stated.

| 0/4/00/      | PARAMETER                                                                                           | LIMITS |      |     |      |

|--------------|-----------------------------------------------------------------------------------------------------|--------|------|-----|------|

| SYMBOL       |                                                                                                     | Min    | Тур  | Max | UNIT |

| Line reset a | nd signal presence detectors                                                                        |        |      |     |      |

|              | Schmitt trigger threshold on Pin 2 to inhibit line reset output at Pin 3 (syncs coincident)         |        | 6.2  |     | v    |

|              | Schmitt trigger threshold on Pin 2 to permit line reset output at Pin 3 (syncs non coincident)      |        | 7.8  |     | v    |

|              | Line reset output $V_{OL}$ (I <sub>3</sub> = 20 $\mu$ A)                                            |        |      | 0.5 | v    |

|              | Line reset output V <sub>OH</sub> (-I <sub>3</sub> = 100µA)                                         | 2.4    |      |     | V    |

|              | Signal presence Schmitt trigger threshold on Pin 2 below which the circuit accepts the input signal |        | 6.0  |     | v    |

|              | Signal presence Schmitt trigger threshold on Pin 2 above which the input signal is rejected         |        | 6.3  |     | v    |

| Crystal-cont | rolled, phase-locked oscillator                                                                     |        |      |     |      |

|              | C <sub>1</sub>                                                                                      |        | 27.5 |     | pF   |

|              | C <sub>0</sub>                                                                                      |        | 6.8  |     | pF   |

|              | CL                                                                                                  |        | 20   |     | pF   |

|              | Trimability (CL increased to 30pF)                                                                  | 750    |      |     | Hz   |

|              | Fundamental ESR                                                                                     |        |      | 50  | Ω    |

NOTES:

1. This is measured with the dual polarity buffer external resistor connected to give negative-going syncs. The measurement is made after adjustment of the potential divider at Pin 14 for optimum delay.

2. The teletext data input contains binary elements as a two-level NRZ signal shaped by a raised cosine filter. The bit rate is 6.9375Mbit/s. The use of odd parity for the 8-bit bytes ensures that there are never more than 14-bit periods between each data transition.

3. This is measured by replacing the clock coil with a small value resistor.

4. This must be measured with the clock coil tuned and using a clock-cracker signal into Pin 16. The clock-cracker is a teletext waveform consisting of only one data transition in each byte.

5. With the external resistor connected to the ground rail, syncs are positive-going centered on +2.3V. With the resistor connected to the supply rail, syncs are negative-going centered on +9.7V.

6. When the composite sync is being delivered, the level is substantially the same as that at the video input.

### SAA5030

#### APPLICATION DATA

The function is quoted against the corresponding pin number

- Signal Presence Time Constant A capacitor and a resistor connected in parallel between this pin and supply determine the delay in operation of the signal presence detector.

- 2 Line Reset Time Constant A capacitor between this pin and supply integrates current pulses from the coincidence detector; the resultant level is used to determine whether to allow FLR pulses (see Pin 3).

- 3 Fast Line Reset Output (FLR) Positivegoing sync pulses are produced at this output if the coincidence detector shows no coincidence between the syncs separated from the incoming video and the CBB waveform from the timing chain circuit SAA5020. These pulses are sent to the timing chain circuit and are used to reset its counters, so as to effect rapid lock-up of the phase-locked loop.

#### 4 Ground (0V)

5 Sandcastle Input (PL and CBB) — This input accepts a sandcastle waveform which is formed from PL and CBB from the timing chain SAA5020. PL is obtained by slicing the waveform at 2.5V, and this, together with separated sync, are inputs to the phase detector which forms part of the phase-locked loop. When the loop has locked up, the edges of PL are nominally 2µs before and 2µs after the leading edge of separated line syncs.

CBB is obtained by slicing the waveform at 5V, and is used to prevent the data slicer from being offset by the color burst.

6 6MHz Output (F6) — This is the output of the crystal oscillator (see Pins 8 and 9), and is taken to the timing chain circuit SAA5020 via a series capacitor.

- 7 Phase Detector Time Constant The integrating components for the phase detector of the phase-locked loop are connected between this pin and supply.

- 8,9 6MHz Crystal A 6MHz crystal in series with a trimmer capacitor is connected between these pins. It forms part of an oscillator whose frequency is controlled by the voltage on Pin 7, which forms part of the phase-locked loop.

- 10 Picture On Input (PO) The PO signal, from the acquisition and control circuits SAA5040 series, is fed to this input and is used to determine whether the input video (Pin 16) or the AHS waveform (Pin 11) appears at Pin 12.

- 11 After Hours Sync (AHS) A composite sync waveform AHS is generated in the timing chain circuit SAA5020 and is used to synchronize the TV (see Pin 10).

- 12 Sync Output to TV The input video of AHS is available at this output dependent on whether the PO signal is High or Low. In addition, either signal may be positivegoing or negative-going, dependent on whether the load resistor at this output is connected to ground or supply.

- 13 Field Sync Output (FS) A pulse, derived from the input video by the field sync separator, which is used to reset the line counter in the timing chain circuit SAA5020.

- 14 Field Sync Separator Timing A capacitor and adjusting network is connected to this pin and forms the integrator of the field sync separator.

- 15 Sync Separator Capacitor A capacitor connected to this pin forms part of the adaptive sync separator.

- 16 Composite Video Input (VI) The composite video is fed to this input via a coupling capacitor.

- 17 Supply Voltage (+12V)

- 18 Clock Output The regenerated clock, after extraction from the teletext data, is fed out to the acquisition and control circuits SAA5040 series via a series capacitor.

- 19 Data Output The teletext data is sliced off the video waveform, squared up, and latched within the SAA5030. The latched output is fed to the acquisition and control circuits SAA5040 series via a series capacitor.

- 20 Clock Decoupling A 1nF capacitor between Pin 20 and ground is required for clock decoupling.

- 21 Clock Regenerator Coil A high-Q parallel tuned circuit is connected between this pin and an external potential divider. The coil is part of the clock regeneration circuit (see Pin 22).

- 22 Clock Pulse Timing Capacitor Short pulses are derived from both edges of data with the aid of a capacitor connected to this pin. The resulting pulses are fed, as a current, into the clock coil connected to Pin 21. Resulting oscillations are limited and taken to the acquisition and control circuits SAA5040 series via Pin 18.

- 23, 24 Peak Detector Capacitors The teletext data is sliced with an automatic data slicer, having a slicing level at the mid-point of two peak detectors working on the video signal. Storage capacitors are connected to these pins for the negative and positive peak detectors.

### SAA5030

### SAA5030