#### FEATURES

2

- 45ns cycle time (typ)

- Easy expansion to multiple of 2 bits

- 11 general purpose registers

- Full function accumulator

- Useful functions include: 2's complement arithmetic Logical AND, OR, NOT, exclusive-NOR Increment, decrement Shift left/shift right Bit testing and zero detection Carry look-ahead generation

- Masking via K-bus Conditioned clocking allowing nondestructive testing of data in accumulator and scratchpad

- 3 input buses

- 2 output buses

- Control bus

### DESCRIPTION

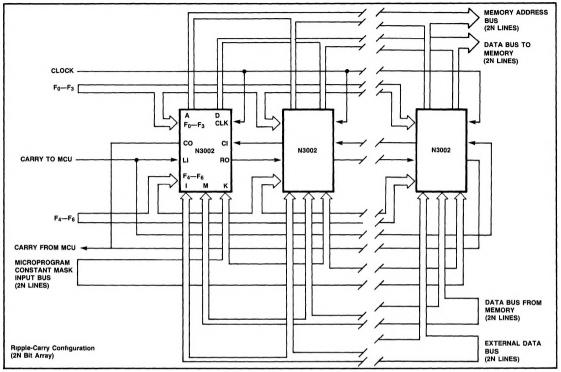

The N3002 Central Processing Element (CPE) is one part of a bipolar microcomputer set. The N3002 is organized as a 2-bit slice and performs the logical and arithmetic functions required by microInstructions. A system with any number of bits in a data word can be implemented by using multiple N3002s, the N3001 microcomputer control unit, the N74S182 carry look-ahead unit and ROM or PROM memory

#### FUNCTION F<sub>6</sub> GROUP F<sub>5</sub> F4 0 0 0 0 1 0 0 1 2 0 1 0 3 0 1 1 4 n 0 1 5 1 0 1 6 1 1 0 7 1 1 1

FUNCTION TRUTH TABLE

| REGISTER<br>GROUP | REGISTER       | F3 | F <sub>2</sub> | F1 | Fo |

|-------------------|----------------|----|----------------|----|----|

|                   | R <sub>0</sub> | 0  | 0              | 0  | 0  |

|                   | R,             | 0  | 0              | 0  | 1  |

|                   | R <sub>2</sub> | 0  | 0              | 1  | 0  |

|                   | R <sub>3</sub> | 0  | 0              | 1  | 1  |

|                   | R₄             | 0  | 1              | 0  | 0  |

|                   | R₅             | 0  | 1              | 0  | 1  |

|                   | R <sub>6</sub> | 0  | 1              | 1  | 0  |

|                   | R <sub>7</sub> | 0  | 1              | 1  | 1  |

|                   | Re             | 1  | 0              | 0  | 0  |

|                   | R <sub>9</sub> | 1  | 0              | 0  | 1  |

|                   | Т              | 1  | 1              | 0  | 0  |

|                   | AC             | 1  | 1              | 0  | 1  |

|                   | т              | 1  | 0              | 1  | 0  |

|                   | AC             | 1  | 0              | 1  | 1  |

|                   | т              | 1  | 1              | 1  | 0  |

| ш                 | AC             | 1  | 1              | 1  | 1  |

### PIN CONFIGURATION

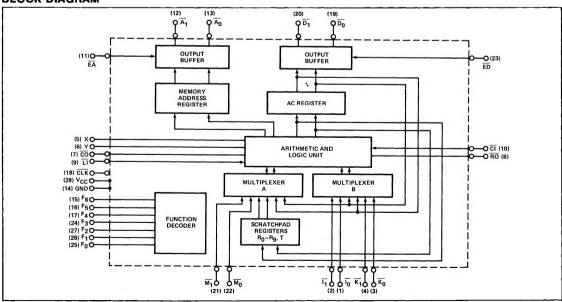

#### **BLOCK DIAGRAM**

# S/N3002

#### **PIN DESCRIPTION**

| PIN            | SYMBOL                          | NAME AND FUNCTION                                                                                                                                                                                       | TYPE                      |

|----------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 1, 2           | 1 <sub>0</sub> -1 <sub>1</sub>  | External Bus Input<br>The external bus inputs provide a separate input port for external input devices.                                                                                                 | Active low                |

| 3, 4           | K <sub>0</sub> – K <sub>1</sub> | Mask Bus Inputs<br>The mask bus inputs provide a separate input port from the microprogram memory, to<br>allow mask or constant entry                                                                   | Active low                |

| 5, 6           | Х, Ү                            | Standard Carry Look-Ahead Cascade Outputs<br>The cascade outputs allow high speed arithmetic operations to be performed when they<br>are used in conjunction with the 74S182 Look-Ahead Carry Generator | Active high               |

| 7              | co                              | Ripple Carry Out                                                                                                                                                                                        | Active low                |

|                |                                 | The ripple carry output is only disabled during shift right operations.                                                                                                                                 | Three-state               |

| 8              | RO                              | Shift Right Output<br>The shift right output is only enabled during shift right operations.                                                                                                             | Active low<br>Three-state |

| 9              | U 1                             | Shift Right Input                                                                                                                                                                                       | Active low                |

| 10             | CI                              | Carry Input                                                                                                                                                                                             | Active low                |

| 11             | EA                              | Memory Address Enable Input<br>When in the low state, the memory address enable input enables the memory address<br>outputs $(A_0 - A_1)$ .                                                             | Active low                |

| 12-13          | A <sub>0</sub> – A <sub>1</sub> | Memory Address Bus Outputs<br>The memory address bus outputs are the buffered outputs of the memory address<br>register (MAR).                                                                          | Active low<br>Three-state |

| 14             | GND                             | Ground                                                                                                                                                                                                  |                           |

| 14-17<br>24-27 | $F_0 - F_6$                     | Micro-Function Bus Inputs<br>The micro-function bus inputs control ALU function and register selection.                                                                                                 | Active high               |

| 18             | CLK                             | Clock Input                                                                                                                                                                                             |                           |

| 19-20          | $D_0 - D_1$                     | Memory Data Bus Outputs                                                                                                                                                                                 | Active low                |

|                |                                 | The memory data bus outputs are the buffered outputs of the full function accumulator register (AC).                                                                                                    | Three-state               |

| 21-22          | M <sub>0</sub> – M <sub>1</sub> | Memory Data Bus Inputs<br>The memory data bus inputs provide a separate input port for memory data.                                                                                                     | Active low                |

| 23             | ED                              | Memory Data Enable Input When in the low state, the memory data enable input enables the memory data outputs $(D_0 - D_1)$ .                                                                            | Active low                |

| 28             | V <sub>cc</sub>                 | + 5 Volt Supply                                                                                                                                                                                         | 1                         |

#### SYSTEM DESCRIPTION **Microfunction Decoder and K-Bus**

Basic microfunctions are controlled by a 7-bit bus (F<sub>0</sub>-F<sub>6</sub>) which is organized into 2 groups. The higher 3 bits ( $F_4$ - $F_6$ ) are designated as F-Group and the lower 4 bits ( $F_0$ - $F_3$ ) are designated as the R-Group The F-Group specifies the type of operation to be performed and the R-Group specifies the registers involved.

The F-Bus instructs the microfunction decoder to:

- Select ALU functions to be performed

- Generate scratchpad register address ٠

- Control A and B multiplexer ٠

The resulting microfunction action can be:

- Data transfer

- Shift operations

- Increment and decrement ٠

- Initialize stack

- Test for zero conditions 2's complement addition and subtraction •

- ٠

- Bit masking

- · Maintain program counter

### A and B Multiplexers

A and B multiplexers select the proper 2 operands to the ALU.

- A multiplexer selects inputs from one of the following:

- M-bus (data from main memory)

- . Scratchpad registers

- Accumulator ٠

B multiplexer selects inputs from one of the following:

- I-bus (data from external I/O devices)

- Accumulator

- K-bus (literal or masking information from • micro-program memory)

#### Scratchpad Registers

- Contains 11 registers (R<sub>0</sub>-R<sub>9</sub>, T) Scratchpad register outputs are multi-. plexed to the ALU via the A multiplexer

- Used to store intermediate results from

- arithmetic/logic operations

- · Can be used as program counter

### Arithmetic/Logic Unit (ALU)

The ALU performs the arithmetic and logic operations of the CPE.

- Arithmetic operations are:

- · 2's complement addition

- Incrementing

- Decrementing

- · Shift left Shift right

Logical operations are:

- Transfer

- AND

- Inclusive-OR

- Exclusive-NOR •

- Logic complement

ALU operation results are then stored in the accumulator and/or scratchpad registers. For easy expansion to larger arrays carry lookahead outputs (X and Y) and cascading shift inputs (LI, RO) are provided.

#### Accumulator

- Stores results from ALU operations

- The output of accumulator is multiplexed into ALU via the A and B multiplexer as one of the operands

### **Input Buses**

M-bus: Data bus from main memory

- Accepts 2 bits of data from main memory into CPE

- Is multiplexed into the ALU via the A multiplexer

I-bus: Data bus from input/output devices Accepts 2 bits of data from external input/output devices into CPE

- Is multiplexed into the ALU via the B multiplexer

- K-bus: A special feature of the N3002 CPE

- During arithmetic operations, the K-bus can be used to mask portions of the field being operated on

- Select or remove accumulator from operation by placing K-bus in all "1" or all "0" state respectively

- During non-arithmetic operation, the carry circuit can be used in conjunction with the K-bus for word-wise-OR operation for bit testing

- Supply literal or constant data to CPE

#### **Output Buses**

A-bus and Memory Address Register

- Main memory address is stored in the memory address register (MAR)

- · Main memory is addressed via the A-bus

- MAR and A-bus may also be used to generate device address when executing I/O instructions

- A-bus has Tri-State outputs

D-bus: Data bus from CPE to main memory or to I/O devices

- Sends buffered accumulator outputs to main memory or the external I/O devices

- D-bus has Tri-State outputs

| F<br>GROUP | R<br>GROUP | K<br>BUS | NAME | EQUATION                                                                                                                                                                                                                                                | DESCRIPTION                                                                                                                                                                                            |

|------------|------------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0          | 1 *        | XX       | -    | R <sub>n</sub> + (AC K) + CI→R <sub>n</sub> , AC                                                                                                                                                                                                        | Logically AND AC with K-bus. Add the result to $R_{\rm n}$ and carry input (CI). Deposit the sum in AC and $R_{\rm n}.$                                                                                |

|            |            | 00       | ILR  | R <sub>n</sub> + CI→R, AC                                                                                                                                                                                                                               | Conditionally increment $R_n$ and load the result in AC. Used to load AC from $R_n$ or to increment $R_n$ and load a copy of the results in AC.                                                        |

|            |            | 11       | ALR  | AC + R <sub>n</sub> + CI→R <sub>n</sub> , AC                                                                                                                                                                                                            | Add AC and CI to ${\rm R}_n$ and load the result in AC. Used to add AC to a register. If ${\rm R}_n$ is AC, then AC is shifted left one bit position.                                                  |

| 0          | "          | xx       | -    | M + (AC K) + CI→AT                                                                                                                                                                                                                                      | Logically AND AC with the K-bus. Add the result to CI and the M-bus.<br>Deposit the sum in AC or T.                                                                                                    |

|            |            | 00       | ACM  | M + CI→AT                                                                                                                                                                                                                                               | Add CI to M-bus. Load the result in AC or T, as specified. Used to load<br>memory data in the specified register, or to load incremented memory data<br>in the specified register.                     |

|            |            | 11       | АМА  | M + AM + CI→AT                                                                                                                                                                                                                                          | Add the M-bus to AC and CI, and load the result in AC or T, as specified.<br>Used to add memory data or incremented memory data to AC and store<br>the sum in the specified register.                  |

| 0          | III        | xx       | Ì    | $\begin{array}{l} AT_{L} \lor (\overline{I_{L} \land K_{L}}) \rightarrow RO \\ LI \lor [(I_{H} \land K_{H}) \land AT_{H}] \rightarrow AT_{H} \\ [AT_{L} \land (I_{L} \land K_{L})] \\ [AT_{H} \lor (I_{H} \land K_{H})] \rightarrow AT_{L} \end{array}$ | None                                                                                                                                                                                                   |

|            |            | 00       | SRA  | AT <sub>L</sub> →RO<br>AT <sub>H</sub> →AT <sub>L</sub><br>L <sub>I</sub> →AT <sub>H</sub>                                                                                                                                                              | Shift AC or T, as specified, right one bit position. Place the previous<br>low order bit value on RO and fill the high order bit from the data on LI<br>Used to shift or rotate AC or T right one bit. |

| 1          | I          | XX       | -    | K∨R <sub>n</sub> →MAR<br>R <sub>n</sub> + K + Cl→R <sub>n</sub>                                                                                                                                                                                         | Logically OR $R_n$ with the K-bus. Deposit the result in MAR. Add the K-bus to $R_n$ and CI. Deposit the result in $R_n.$                                                                              |

|            |            | 00       | LMI  | R <sub>n</sub> →MARm R <sub>n</sub> + Cl→R <sub>n</sub>                                                                                                                                                                                                 | Load MAR from $R_n.$ Conditionally increment $R_n.$ Used to maintain a macro-instruction program counter.                                                                                              |

|            |            | 11       | DSM  | 11→MAR, R <sub>n</sub> – 1 + Cl→R <sub>n</sub>                                                                                                                                                                                                          | Set MAR to all ones. Conditionally decrement $R_n$ by one. Used to force MAR to its highest address and to decrement $R_n$ .                                                                           |

| 1          | "          | XX       | _    | KVM→MAR<br>M + K + CI→AT                                                                                                                                                                                                                                | Logically OR the M-bus with the K-bus. Deposit the result in MAR. Add the K-bus to the M-bus and CI. Deposit the sum in AC or T.                                                                       |

|            |            | 00       | LMM  | M→MAR, M + CI→AT                                                                                                                                                                                                                                        | Load MAR from the M-bus. Add CI to the M-bus. Deposit the result in AC<br>or T. Used to load the address register with memory data for macro-<br>instructions using indirect addressing.               |

|            |            | 11       | LDM  | 11→MAR<br>M – 1 + Cl→AT                                                                                                                                                                                                                                 | Set MAR to all ones. Subtract one from the M-bus. Add CI to the difference<br>and deposit the result in AC or T, as specified. Used to load decremented<br>memory data in AC or T.                     |

### FUNCTION DESCRIPTION

### FUNCTION DESCRIPTION (Cont'd)

| F<br>GROUP | R<br>GROUP | K<br>BUS | NAME | EQUATION                                    | DESCRIPTION                                                                                                                                                                                                         |

|------------|------------|----------|------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          |            | XX       | -    | (ĀT∨K) + (AT^K) + CI→AT                     | Logically OR the K-bus with the complement of AC or T, as specified.<br>Add the result to the logical AND of specified register with the K-bus. Add<br>the sum to CI. Deposit the result in the specified register. |

|            |            | 00       | CIA  | AT + CI→AT                                  | Add CI to the complement of AC or T, as specified. Deposit the result in<br>the specified register. Used to form the 1's or 2's complement of AC or T.                                                              |

|            |            | 11       | DCA  | AT – 1 + CI→AT                              | Subtract one from AC or T, as specified. Add CI to the difference and deposit the sum in the specified register. Used to decrement AC or T.                                                                         |

| 2          |            | XX       | -    | (AC^K) – 1 + CI→R <sub>n</sub>              | Logically AND the K-bus with AC. Subtract one from the result and add the difference to CI. Deposit the sum in ${\sf R}_{\sf n}$ .                                                                                  |

|            |            | 00       | CSR  | CI – 1→R <sub>n</sub><br>(See Note 1)       | Subtract one from CI and deposit the difference in $\rm R_n.$ Used to conditionally clear or set $\rm R_n$ to all 0's or 1's, respectively                                                                          |

|            |            | 11       | SDR  | AC – 1 + CI→R <sub>n</sub><br>(See Note 1)  | Subtract one from AC and add the difference to CI. Deposit the sum in $R_n$ . Used to store AC in $R_n$ , or to store the decremented value of AC in $R_n$ .                                                        |

| 2          |            | хх       | -    | (AC ^ K) – 1 + CI-+AT<br>(See Note 1)       | Logically AND the K-bus with AC. Subtract one from the result and<br>add the difference to CI. Deposit the sum in AC or T, as specified.                                                                            |

|            |            | 00       | CSA  | CI – 1→AT<br>(See Note 1)                   | Subtract one from CI and deposit the difference in AC or T. Used to conditionally clear or set AC or T.                                                                                                             |

|            |            | 11       | SDA  | AC – 1 + CI→AT<br>(See Note 1)              | Subtract one from AC and add the difference to Cl. Deposit the sum in AC or T. Used to store AC in T, or decrement AC, or store the decremented value of AC in T.                                                   |

| 2          |            | хх       | 4    | (I ^ K) – 1 + CI→AT<br>(See Note 1)         | Logically AND the data of the K-bus with the data on the I-bus.<br>Subtract one from the result and add the difference to CI. Deposit the sum<br>in AC or T, as specified.                                          |

|            |            | 00       | CSA  | CI – 1→AT                                   | Subtract one from CI and deposit the difference in AC or T $$ Used to conditionally clear or set AC or T $$                                                                                                         |

|            |            | 11       | LDI  | I – 1 + CI→AT                               | Subtract one from the data on the I-bus and add the difference to CI. Deposit the sum in AC or T, as specified Used to load input bus data or decremented input bus data in the specified register.                 |

| 3          | 1          | ХХ       | -    | $R_n + (AC^{\wedge}K) + CI \rightarrow R_n$ | Logically AND AC with the K-bus. Add $\rm R_n$ and CI to the result. Deposit the sum in $\rm R_n.$                                                                                                                  |

|            |            | 00       | INR  | R <sub>n</sub> + Cl→R <sub>n</sub>          | Add CI to $R_n$ and deposit the sum in $R_n$ . Used to increment $R_n$ .                                                                                                                                            |

|            |            | 11       | ADR  | AC + R <sub>n</sub> + CI→R <sub>n</sub>     | Add AC to $R_n$ Add the result to CI and deposit the sum in $R_n$ . Used to add the accumulator to a register or to add the incremented value of the accumulator to a register                                      |

| 3          | H          | XX       | -    | M + (AC∧K) +CI→AT                           | Logically AND AC with the K-bus. Add the result to CI and the M-bus.<br>Deposit the sum in AC or T.                                                                                                                 |

|            |            | 00       | ACM  | M + Cl→AT                                   | Add CI to M-bus Load the result in AC or T, as specified. Used to load<br>memory data in the specified register, or to load incremented memory data<br>in the specified register.                                   |

|            |            | 11       | AMA  | M + AC + CI→AT                              | Add the M-bus to AC and CI, and load the result in AC or T, as specified.<br>Used to add memory data or incremented memory data to AC and store<br>the sum in the specified register                                |

NOTE

1. 2's complement arithmetic adds 111 11 to perform subtraction of 000

01

# FUNCTION DESCRIPTION (Cont'd)

| F<br>GROUP | R<br>GROUP | K<br>BUS | NAME | EQUATION                                                               | DESCRIPTION                                                                                                                                                                                                                                                                          |

|------------|------------|----------|------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3          | 111        | xx       | -    | AT + (I∧K) + CI→AT                                                     | Logically AND the K-bus with the I-bus. Add CI and the contents of AC<br>or T, as specified, to the result. Deposit the sum in the specified register.                                                                                                                               |

|            |            | 00       | INA  | AT + CI→AT                                                             | Conditionally increment AC or T. Used to increment AC or T.                                                                                                                                                                                                                          |

|            |            | 11       | AIA  | I + AT + CI→AT                                                         | Add the I-bus to AC or T. Add CI to the result and deposit the sum in the<br>specified register. Used to add input data or incremented input data to the<br>specified register.                                                                                                      |

| 4          | 1          | XX       | 1    | CI ∨ ( $R_n \land AC \land K$ )→CO<br>$R_n \land (AC \land K$ )→ $R_n$ | <b>Logically AND the K-bus with AC.</b> Logically AND the result with the contents of $R_n$ . Deposit the final result in $R_n$ . Logically OR the value of CI with the word-wise OR of the bits of the final result. Place the value of the carry OR on the carry output (CO) line. |

|            |            | 00       | CLR  | CI→CO, O→R <sub>n</sub>                                                | Clear ${\rm R}_{\rm n}$ to all O's. Force CO to CI. Used to clear a register and force CO to CI.                                                                                                                                                                                     |

|            |            | 11       | ANM  | Cl ∨ (R <sub>n</sub> ^ AC)→CO<br>R <sub>n</sub> ^ AC→R <sub>n</sub>    | Logically AND AC with ${\sf R}_n.$ Deposit the result in ${\sf R}_n.$ Force CO to one if the result is non-zero. Used to AND the accumulator with a register and test for a zero result.                                                                                             |

| 4          | 11         | xx       | 1    | CI ∨ (M ∧ AC ∧ K)→CO<br>M ∧ (AC ∧ K)→AT                                | Logically AND the K-bus with AC. Logically AND the result with The M-bus. Deposit the final result in AC ot T. Logically OR the value of CI with the word-wise OR of the bits of the final result. Place the value of the carry OR on CO.                                            |

|            |            | 00       | CLA  | CI→CO, O→AT                                                            | Clear AC or T, as specified, to all O's. Force CO to Cl. Used to clear the specified register and force CO to Cl.                                                                                                                                                                    |

|            |            | 11       | ANM  | CI∨(M∧AC)→CO<br>M∧AC→AT                                                | Logically AND the M-bus with AC. Deposit the result in AC or T. Force CO to one if the result is non-zero. Used to AND the M-bus data to the accumulator and test for a zero result.                                                                                                 |

| 4          | Ξ          | хх       | 1    | CI∨(AT ^ 1 ^ K)→CO<br>AT ^ (I ^ K)→AT                                  | Logically AND the I-bus with the K-bus. Logically AND the result with AC or T. Deposit the final result in the specified register. Logically OR CI with the word-wise OR of the final result. Place the value of the carry OR on CO.                                                 |

|            |            | 00       | CLA  | CI→CO, O→AT                                                            | Clear AC or T, as specified, to all O's. Force CO to CI. Used to clear the specified register and force CO to CI.                                                                                                                                                                    |

|            |            | 11       | ANI  | Cl ∨ (AT ∧ I)→CO<br>AT ∧ 1→AT                                          | Logically AND the I-bus with AC or T, as specified. Deposit the result<br>in the specified register. Force CO to one if the result is non-zero. Used<br>to AND the I-bus to the accumulator and test for a zero result.                                                              |

| 5          |            | xx       | 1    | CI ∨ (R <sub>n</sub> ∧ K)→CO<br>K ∧ R <sub>n</sub> →R <sub>n</sub>     | Logically AND the K-bus with $R_n$ . Deposit the result in $R_n$ . Logically OR CI with the word-wise OR of the result. Place the value of the carry OR on CO.                                                                                                                       |

|            |            | 00       | CLR  | CI→CO, O→R <sub>n</sub>                                                | Clear $\mathbf{R}_{n}$ to all O's. Force CO to CI. Used to clear a register and force CO to CI.                                                                                                                                                                                      |

|            |            | 11       | TZR  | Cl∨R <sub>n</sub> →CO<br>R <sub>n</sub> →R <sub>n</sub>                | Force CO to one if ${\rm I\!R}_n$ is non-zero. Used to test a register for zero. Also used to AND K-bus data with a register for masking and, optionally, testing for a zero result.                                                                                                 |

| 5          |            | XX       | -    | CI∨(M∧K)→CO<br>K∧M→AT                                                  | Logically AND the K-bus with the M-bus. Deposit the result in AC or T, as specified. Logically OR CI with the work-wise OR of the result. Place the value of the carry OR on CO.                                                                                                     |

|            |            | 00       | CLA  | CI→CO, O→AT                                                            | Clear AC or T, as specified, to all O's. Force CO to CI. Used to clear the specified register and force CO to CI.                                                                                                                                                                    |

|            |            | 11       | LTM  | CI ∨ M→CO<br>M→AT                                                      | Load AC or T, as specified, from the M-bus. Force CO to one if the result<br>is non-zero. Used to load the specified register from memory and test for<br>zero result. Also used to AND the K-bus with the M-bus for masking and,<br>optionally, testing for a zero result.          |

# FUNCTION DESCRIPTION (Cont'd)

| F<br>GROUP | R<br>GROUP | K<br>BUS | NAME | EQUATION                                                                                                  | DESCRIPTION                                                                                                                                                                                                                                                           |

|------------|------------|----------|------|-----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5          | III        | ХХ       | 1    | CI∨(AT∧K)→CO<br>K∧AT→AT                                                                                   | Logically AND the K-bus with AC or T, as specified. Deposit the result<br>in the specified register. Logically OR CI with the word-wise OR of the result.<br>Place the value of the carry OR on CO.                                                                   |

|            |            | 00       | CLA  | CI→CO, O→AT                                                                                               | Clear AC or T, as specified, to all O's. Force CO to CI. Used to clear the specified register and force CO to CI.                                                                                                                                                     |

|            |            | 11       | TZA  | CI∨AT→CO<br>AT→AT                                                                                         | Force CO to one if AC or T, as specified, is non-zero. Used to test the specified register for zero. Also used to AND the K-bus to the specified register for masking and, optionally, testing for a zero result.                                                     |

| 6          | -          | ХХ       | -    | CI∨ (AC ∧ K)→CO<br>R <sub>n</sub> ∨ (AC ∧ K)→R <sub>n</sub>                                               | Logically OR CI with the word-wise OR of the logical AND of AC and the K-bus. Place the result of the carry OR on CO. Logically OR $R_n$ with the logical AND of AC and the K-bus. Deposit the result in $R_n$ .                                                      |

|            |            | 00       | NOP  | CI→CO, R <sub>n</sub> →R <sub>n</sub>                                                                     | Force CO to CI. Used as a null operation or to force CO to CI.                                                                                                                                                                                                        |

|            |            | 11       | ORR  | CI ∨ AC→CO<br>R <sub>n</sub> ∨ AC→R <sub>n</sub>                                                          | Force CO to one if AC is non-zero. Logically OR AC with $R_n$ , Deposit the result in $R_n$ . Used to OR the accumulator to a register and, optionally, test the previous accumulator value for zero.                                                                 |

| 6          | "          | xx       | -    | CI ∨ (AC ^ K)→CO<br>M ∨ (AC ^ K)→AT                                                                       | Logically OR CI with the word-wise OR of the logical AND of AC and<br>the K-bus. Place the carry OR on CO. Logically OR the M-bus, with the<br>logical AND of AC and the K-bus. Deposit the final result in AC or T.                                                  |

|            |            | 00       | LMF  | CI→CO, M→AT                                                                                               | Load AC or T, as specified, from the M-bus. Force CO to CI. Used to load<br>the specified register with memory data and force CO to Ci.                                                                                                                               |

|            |            | 11       | ORM  | CI∨AC→CO<br>M∨AC→AT                                                                                       | Force CO to one if AC is non-zero. Logically OR the M-bus with AC. Deposit the result in AC or T, as specified. Used to OR M-bus with the AC and, optionally, test the previous value of AC for zero.                                                                 |

| 6          | 111        | XX       | Í    | Cl ∨ (I ∧ K)→CO<br>AT ∨ (I ∧ I)→AT                                                                        | Logical OR CI with the word-wise OR of the logical AND of the I-bus<br>and the K-bus. Place the carry OR on CO. Logically AND the K-bus with<br>the I-bus. Logically OR the result with AC or T, as specified. Deposit the<br>final result in the specified register. |

|            |            | 00       | NOP  | CI→CO, AT→AT                                                                                              | Force CO to CI. Used as a null operation or to force CO to CI.                                                                                                                                                                                                        |

|            |            | 11       | ORI  | Cl ∨ I→CO<br>I ∨ AT→                                                                                      | Force CO to one if the data on the I-bus is non-zero. Logically OR the I-bus to AC or T, as specified. Deposit the result in the specified register. Used to OR I-bus data with the specified register and, optionally, test the I-bus data for zero.                 |

| 7          | -          | XX       | -    | $CI \lor (R_n \land AC \land K) \rightarrow CO$ $R_n \ \overline{\bullet} \ (AC \land K) \rightarrow R_n$ | Logically OR CI with the word-wise OR of the logical AND of $R_n$ and AC and the K-bus. Place the carry OR on CO. Logically AND the K-bus with AC. Exclusive-NOR the result with $R_n$ . Deposit the final result in $R_n$ .                                          |

|            |            | 00       | CMR  | CI→CO, R <sub>n</sub> →R <sub>n</sub>                                                                     | Complement the contents of R <sub>n</sub> . Force CO to CI.                                                                                                                                                                                                           |

|            |            | 11       | XNR  | CI (R <sub>n</sub> ∨ AC)→CO<br>R <sub>n</sub>                                                             | Force CO to one if the logical AND of AC and $R_n$ is non-zero. Exclusive-NOR AC with $R_n$ . Deposit the result in $R_n$ . Used to exclusive-NOR the accumulator with a register.                                                                                    |

# FUNCTION DESCRIPTION (Cont'd)

| F<br>GROUP | R<br>GROUP | K<br>BUS | NAME | EQUATION                               | DESCRIPTION                                                                                                                                                                                                                                                                            |

|------------|------------|----------|------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7          | Ш          | xx       | -    | CI∨(M ∧AC ∧K)→CO<br>M ⊕ (AC ∧K)→AT     | Logically OR CI with the word-wise OR of the logical AND of AC<br>and the K-bus and M-bus. Place the carry OR on CO. Logically AND the<br>K-bus with AC. Exclusive NOR the result with the M-bus. Deposit the final<br>result in AC or T.                                              |

|            |            | 00       | LCM  | CI→CO, M→AT                            | Load the complement of the M-bus into AC or T, as specified. Force CO to Cl.                                                                                                                                                                                                           |

|            |            | 11       | XNM  | CI (M ∧ AC)→CO<br>M ≅ AC→AT            | Force CO to one if the logcal AND of AC and the M-bus is non-zero.<br>Exclusive-NOR AC with the M-bus. Deposit the result in AC or T, as<br>specified. Used to exclusive-NOR memory data with the accumulator.                                                                         |

| 7          |            | хх       | -    | Cl ∨ (AT ^ I ^ K)→CO<br>ATē (l ^ K)→AT | Logically OR CI with the word-wise OR of the logical AND of the specified register and the I-bus and K-bus. Place the carry OR on CO. Logically AND the K-bus with the I-bus. Exclusive-NOR the result with AC or T, as specified. Deposit the final result in the specified register. |

|            |            | 00       | СМА  | CI→CO ĀT→AT                            | Complement AC or T, as specified. Force CO to Cl.                                                                                                                                                                                                                                      |

|            |            | 11       | XNI  | Cl∨(AT∧l)→CO<br>I ⊕ AT→AT              | Force CO to one if the logical AND of the specified register and the l-bus<br>is non-zero. Exclusive-NOR AC with the l-bus. Deposit the result in AC or<br>T, as specified. Used to exclusive-NOR input data with the accumulator.                                                     |

### FUNCTION DESCRIPTION KEY

| SYMBOL         | MEANING                                                      |

|----------------|--------------------------------------------------------------|

| I,K,M          | Data on the I, K, and M buses, respectively                  |

| CI,LI          | Data on the carry input and left input, respectively         |

| CO,RO          | Data on the carry output and right output, respectively      |

| R <sub>n</sub> | Contents of register n including<br>T and AC (R-Group I)     |

| AC             | Contents of the accumulator                                  |

| AT             | Contents of AC or T, as specified                            |

| MAR            | Contents of the memory address register                      |

| L,H            | As subscripts, designate low and high ordr bit, respectively |

| +              | 2's complement addition                                      |

| -              | 2's complement subtraction                                   |

| ^              | Logical AND                                                  |

| ~              | Logical OR                                                   |

| Ð              | Exclusive-NOR                                                |

| <b>→</b>       | Deposit into                                                 |

###

|                                          | PARAMETER                                                                                                                                                                         |              | N3002                                    |                            |              |                                          |                             |                            |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------|----------------------------|--------------|------------------------------------------|-----------------------------|----------------------------|

|                                          | FARAMEIER                                                                                                                                                                         | Min          | Тур*                                     | Max                        | Min          | Тур*                                     | Max                         |                            |

| tCY                                      | Clock Cycle Time                                                                                                                                                                  | 70           | 45                                       |                            | 120          | 45                                       |                             | ns                         |

| tWP                                      | Clock Pulse Width                                                                                                                                                                 | 17           | 10                                       |                            | 42           | 10                                       |                             | ns                         |

| tFS                                      | Function Input Set-Up Time (F <sub>0</sub> through F <sub>6</sub> )                                                                                                               | 48           | - 23-→35                                 |                            | 70           | - 23→35                                  |                             | ns                         |

| Data<br>tDS<br>tSS                       | Set-Up Time:<br>I <sub>0</sub> , I <sub>1</sub> , M <sub>0</sub> , M <sub>1</sub> , K <sub>0</sub> , K <sub>1</sub><br>LI, CI                                                     | 40<br>21     | 12→29<br>0→7                             | 1                          | 60<br>30     | 12→29<br>0→7                             |                             | ns<br>ns                   |

| Data<br>tFH<br>tDH<br>tSH                | and Function Hold Time:<br>F <sub>0</sub> through F <sub>6</sub><br>1 <sub>0</sub> , I <sub>1</sub> , M <sub>0</sub> , M <sub>1</sub> , K <sub>0</sub> , K <sub>1</sub><br>Ll, Cl | 4<br>4<br>12 | 0<br>- 28→ - 11<br>- 7→0                 |                            | 5<br>5<br>15 | 0<br>28→11<br>7→0                        |                             | ns<br>ns<br>ns             |

| Propa<br>tXF<br>tXD<br>tXT<br>tXL        | agation Delay to X, Y, RO from:<br>Any Function Input<br>Any Data Input<br>Trailing Edge of CLK<br>Leading Edge of CLK                                                            | 13           | 28<br>16→20<br>33<br>18→40               | 52<br>33<br>48<br>70       | 13           | 28<br>16→20<br>33<br>18→40               | 65<br>65<br>75<br>90        | ns<br>ns<br>ns<br>ns       |

| Propa<br>tCL<br>tCL<br>tCF<br>tCD<br>tCC | agation Delay to CO from:<br>Leading Edge of CLK<br>Trailing Edge of CLK<br>Any Function Input<br>Any Data Input<br>CI (Ripple Carry)                                             | 16           | 24→44<br>30→40<br>25→35<br>17→23<br>9→13 | 70<br>56<br>52<br>55<br>20 |              | 24→44<br>30→40<br>25→35<br>17→23<br>9→13 | 90<br>100<br>75<br>65<br>30 | ns<br>ns<br>ns<br>ns<br>ns |

| Propa<br>tDL<br>tDE                      | agation Delay to A <sub>0</sub> , A <sub>1</sub> , D <sub>0</sub> , D <sub>1</sub> from:<br>Leading Edge of CLK<br>Enable Input ED, EA                                            |              | 17→25<br>10→12                           | 40<br>20                   |              | 17→25<br>10→12                           | 75<br>35                    | ns<br>ns                   |

#### \*NOTE

Typical values are for  $T_A = 25^{\circ}C$  and typical supply voltage.

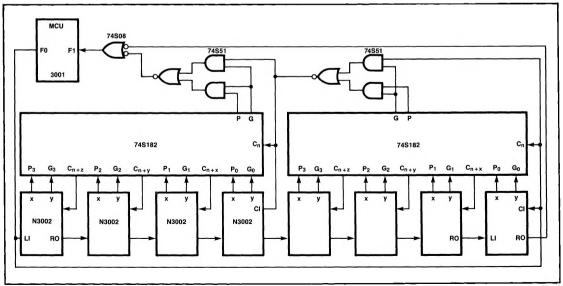

### CARRY LOOK-AHEAD CONFIGURATION

# S/N3002

### TYPICAL CONFIGURATIONS

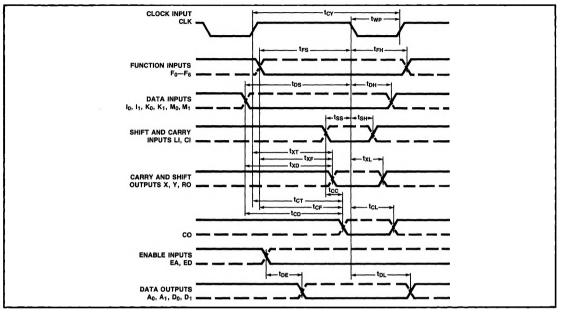

### **VOLTAGE WAVEFORMS**