## **Signetics**

# PNA7509 7-Bit Analog-to-Digital Converter

Preliminary Specification

#### **Linear Products**

#### DESCRIPTION

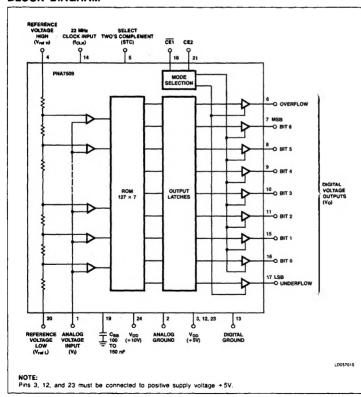

The PNA7509 is a monolithic NMOS 7-bit analog-to-digital converter designed for video applications. The device converts the analog input signal into 7-bit binary coded digital words at a sampling rate of 22MHz.

The circuit comprises 129 comparators, a reference resistor chain, combining logic, transcoder stages, and TTL output buffers which are positive edge-triggered and can be switched into 3-State mode. The digital output is selectable in two's complement or binary coding.

The use of separate outputs for overflow and underflow detection facilitates full-scale driving.

#### **FEATURES**

- 7-bit resolution

- 22MHz clock frequency

- No external sample and hold required

- High input impedance

- Binary or two's complement 3-State TTL outputs

- Overflow and underflow 3-State TTL outputs

- Low reference current (250μA typ.)

- Positive supply voltages (+5V, +10V)

- Low power consumption (400mW typ.)

- Available in SO package

#### **BLOCK DIAGRAM**

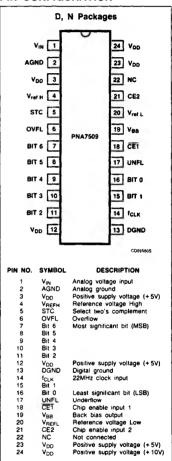

## PIN CONFIGURATION

#### **APPLICATIONS**

- High-speed A/D conversion

- Video signal digitizing

- · Radar pulse analysis

- High energy physics research

- Transient signal analysis

PNA7509

## **ORDERING INFORMATION**

| DESCRIPTION                   | TEMPERATURE RANGE | ORDER CODE |  |  |

|-------------------------------|-------------------|------------|--|--|

| 24-Pin Plastic DIP (SOT-101A) | 0 to +70°C        | PNA7509N   |  |  |

| 24-Pin Plastic SO (SOT-101)   | 0 to +70°C        | PNA7509D   |  |  |

## ABSOLUTE MAXIMUM RATINGS

| SYMBOL           | PARAMETER                             | RATING      | UNIT |  |  |

|------------------|---------------------------------------|-------------|------|--|--|

| V <sub>DD</sub>  | Supply voltage range (Pins 3, 12, 23) | 7           | ٧    |  |  |

| V <sub>DD</sub>  | Supply voltage range (Pin 24)         | 12          | ٧    |  |  |

| V <sub>IN</sub>  | Input voltage range                   | 7           | ٧    |  |  |

| lout             | Output current                        | 5           | mA   |  |  |

| PD               | Power dissipation                     | 1           | W    |  |  |

| T <sub>STG</sub> | Storage temperature range             | -65 to +150 | °C   |  |  |

| TA               | Operating ambient temperature range   | 0 to +70    | °C   |  |  |

DC ELECTRICAL CHARACTERISTICS  $V_{DD} = V_{3, 12, 23-13} = 4.5$  to 5.5V;  $V_{DD} = V_{24-2} = 9.5$  to 10.5V;  $C_{BB} = 100$ nF;  $T_A = 0$  to +70°C, unless otherwise specified.

| CYMPOL                                                | DADAMETED                                                        |                |           |      |          |  |

|-------------------------------------------------------|------------------------------------------------------------------|----------------|-----------|------|----------|--|

| SYMBOL                                                | PARAMETER                                                        | Min            | Тур       | Max  | UNIT     |  |

| Supply                                                |                                                                  |                |           |      |          |  |

| V <sub>DD</sub>                                       | Supply voltage (Pins 3, 12, 23)                                  | 4.5            |           | 5.5  | V        |  |

| V <sub>DD</sub>                                       | Supply voltage (Pin 24)                                          | 9.5            |           | 10.5 | V        |  |

| (DD                                                   | Supply current (Pins 3, 12, 23)                                  | 1              | 51        | 85   | mA       |  |

| IDD                                                   | Supply current (Pin 24)                                          |                | 11        | 18   | mA       |  |

| Reference v                                           | voltages                                                         |                |           |      |          |  |

| VREFL                                                 | Reference voltage Low (Pin 20)                                   | 2.4            | 2.5       | 2.6  | V        |  |

| VREFH                                                 | Reference voltage High (Pin 4)                                   | 5.0            | 5.1       | 5.2  | V        |  |

| IREF                                                  | Reference current                                                | 150            |           | 450  | μΑ       |  |

| Inputs                                                |                                                                  |                |           |      |          |  |

|                                                       | Clock input (Pin 14)                                             |                |           |      |          |  |

| VIL                                                   | Input voltage Low                                                | -0.3           | į         | 0.8  | V        |  |

| VIH                                                   | Input voltage High Digital input levels (Pins 5, 18, 21)*        | 3.0            |           | 5.5  | \ \ \    |  |

| VIL                                                   | Input voltage Low                                                | 0              | ł         | 0.8  | V        |  |

| VIH                                                   | Input voltage High                                               | 2.0            |           | 5.5  | v        |  |

|                                                       | Input current                                                    | <del>-  </del> |           |      |          |  |

| -15                                                   | at $V_5 = 0V$ ; $V_{13} = GND$                                   | 15             |           | 70   | μΑ       |  |

| 118                                                   | at $V_{18} = 5V$ ; $V_{13} = GND$                                | 15             |           | 70   | μΑ       |  |

|                                                       | Input leakage current                                            |                |           |      |          |  |

| -121                                                  | at $V_{21} = 0V$ ; $V_{13} = GND$                                | 25             |           | 120  | μΑ       |  |

| ILI                                                   | Input leakage current (except Pins 5, 18, 21)                    | 1              |           | 10   | μΑ       |  |

|                                                       | Analog Input levels (Pin 1)                                      |                | ļ         | 1    |          |  |

|                                                       | at V <sub>REFL</sub> = 2.5V; V <sub>REFH</sub> = 5.1V            |                | ļ         |      |          |  |

| V <sub>IN P-P</sub>                                   | Input voltage amplitude (peak-to-peak value)                     | 1              | 2.6       |      | V        |  |

| VIN                                                   | input voltage (underflow)                                        | 1              | 2.5       |      | V        |  |

| V <sub>IN</sub><br>V <sub>I</sub> — V <sub>REFL</sub> | Input voltage (overflow)                                         |                | 5.1<br>10 | 1    | 1        |  |

| VI — VREFL<br>VI — VREFH                              | Offset input voltage (underflow) Offset input voltage (overflow) |                | -10       |      | mV<br>mV |  |

| C <sub>1, 2</sub>                                     | Input capacitance                                                | +              |           | 60   | ρF       |  |

| Outputs                                               | T when contrasts                                                 |                | 1         | 1    |          |  |

|                                                       | Digital voltage outputs                                          |                | 1         |      | 1        |  |

|                                                       | (Pins 6 to 11 and 15 to 17)                                      |                | 1         |      |          |  |

|                                                       | Output voltage Low                                               |                | 1         |      | 1        |  |

| VOL                                                   | at I <sub>O</sub> = 2mA                                          | 0              | 1         | -0.4 | V        |  |

|                                                       | Output voltage High                                              |                | 1         |      | 1        |  |

| V <sub>OH</sub>                                       | at ~I <sub>O</sub> = 0.5mA                                       | 2.4            | 1         | 5.5  | ٧        |  |

When Pin 5 is Low, binary coding is selected.

When Pin 5 is High, two's complement is selected.

If Pins 5, 18 and 21 are open-circuit, Pins 5, 21 are High and Pin 18 is Low.

For output coding, see Table 1; for mode selection, see Table 2.

PNA7509

AC ELECTRICAL CHARACTERISTICS  $V_{DD} = V_{3, 12, 23-13} = 4.5$  to 5.5V;  $V_{DD} = V_{24-2} = 9.5$  to 10.5V;  $V_{REFL} = 2.5V$ ;  $V_{REFL} = 5.1V$ ;  $f_{CLK} = 22MHz$ ;  $C_{BB} = 100nF$ ;  $T_A = 0$  to  $+70^{\circ}C$ , unless otherwise specified.

| CVMDO                                                   | 242445752                                                                                                                     | [             |                |                  |                          |  |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|------------------|--------------------------|--|

| SYMBOL                                                  | PARAMETER                                                                                                                     | Min           | Тур            | Max              | UNIT                     |  |

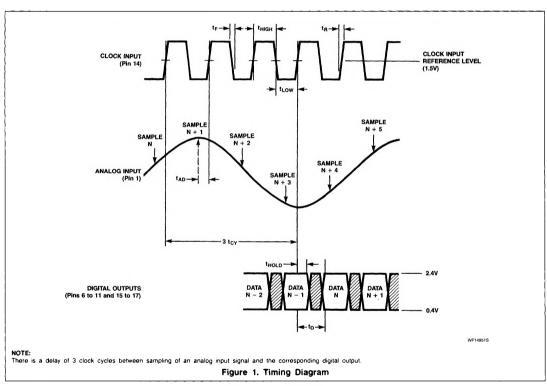

| Timing (see a                                           | Iso Figure 1)                                                                                                                 | •             |                |                  |                          |  |

| f <sub>CLK</sub><br>t <sub>LOW</sub><br>thigh           | Clock input (Pin 14) clock frequency clock cycle time Low clock cycle time High                                               | 1<br>20<br>20 | 25             | 22               | MHz<br>ns<br>ns          |  |

| t <sub>R</sub><br>t <sub>F</sub>                        | Input rise and fall times <sup>1</sup> rise time fall time                                                                    |               |                | 3<br>3           | ns<br>ns                 |  |

| BW<br>dG                                                | Analog input <sup>1</sup> Bandwidth (-3 dB) Differential gain                                                                 | 11            | 20             |                  | MHz                      |  |

| dp                                                      | at f <sub>l</sub> = ≤ 4.5MHz <sup>2</sup> Differential phase                                                                  |               | ± 3            | ± 5              | %                        |  |

| PE                                                      | at f₁ = ≤ 4.5MHz² Phase error                                                                                                 |               | ± 1            | ± 2.5            | deg                      |  |

| S/N                                                     | at f <sub>I</sub> = ≤ 4.5MHz <sup>3</sup> Signal-to-noise ratio (non-harmonic noise) Peak error Harmonics (full-scale)        |               | 10<br>-40      | ± 12<br>-36<br>3 | deg<br>dB<br>LSB         |  |

| f <sub>0</sub><br>f <sub>2, 3</sub><br>f <sub>4-7</sub> | Fundamental 2nd and 3rd harmonics 4th +5th +6th +7th harmonics                                                                |               | -31<br>-39     | 0<br>-28<br>-35  | dB<br>dB<br>dB           |  |

| thold<br>to                                             | Digital outputs <sup>2, 4</sup> Output hold time Output delay time $C_L$ = 15pF Output delay time $C_L$ = 50pF Internal delay | 6             | 3              | 38<br>48         | ns<br>ns<br>ns<br>clocks |  |

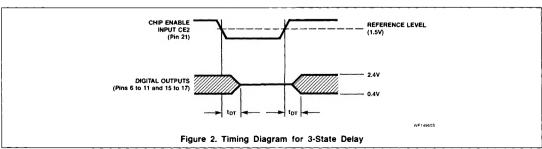

| t <sub>DT</sub><br>C <sub>OL</sub>                      | 3-State delay time (see Figure 2) Capacitive output load Transfer function Non-linearity at f <sub>1</sub> = 1.1kHz           | 0             |                | 25<br>15         | ns<br>pF                 |  |

| INL<br>DNL                                              | integral differential                                                                                                         |               | ± 1/4<br>± 1/3 | ± ½<br>± ½       | LSB<br>LSB               |  |

#### NOTES:

<sup>1.</sup> Clock input rise and fall times are at the maximum clock frequency (10% and 90% levels).

<sup>2.</sup> Low frequency sine wave (peak-to-peak value of the analog input voltage at VIN = 1.8V) amplitude modulated with a sine wave voltage (VIN = 0.7V) at

<sup>3.</sup> Sine wave voltage with increasing amplitude at  $f_1 = 5 MHz$  (minimum amplitude  $V_{1N} = 0.25V$ ; maximum amplitude  $V_{1N} = 2.5V$ ).

4. The timing values of the digital output Pins 6 to 11 and 15 to 17 are measured with the clock input reference level at 1.5V.

## PNA7509

Table 1. Output Coding (V<sub>REFL</sub> = 2.5V; V<sub>REFH</sub> = 5.1V)

|   | STEP      | V <sub>1, 2</sub><br>(Typ) | UNFL OVFL |     |   | BINARY<br>Bit 6 - Bit 0 |   |   |   |   |   | TWO's<br>COMPLEMENT<br>Bit 6 - Bit 0 |   |   |   |   |   |   |

|---|-----------|----------------------------|-----------|-----|---|-------------------------|---|---|---|---|---|--------------------------------------|---|---|---|---|---|---|

| 1 | Underflow | < 2.51                     | 1         | 0   | 0 | 0                       | 0 | 0 | 0 | 0 | 0 | 1                                    | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0         | 2.51                       | 0         | 0   | 0 | 0                       | 0 | 0 | 0 | 0 | 0 | 1                                    | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1         | 2.53                       | 0         | 0   | 0 | 0                       | 0 | 0 | 0 | 0 | 1 | 1                                    | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 |           |                            |           | 11. | • |                         | • | • | • | • |   |                                      | • | ٠ | ٠ | ٠ | • | • |

| 1 |           |                            |           |     | • | ٠                       |   | • | • | ٠ | ٠ |                                      | ٠ | • | ٠ | ٠ | • | ٠ |

| 1 |           |                            |           |     |   | •                       | • | • | • | • |   |                                      |   | • |   | ٠ | • | • |

| 1 | 126       | 5.03                       | 0         | 0   | 1 | 1                       | 1 | 1 | 1 | 1 | 0 | 0                                    | 1 | 1 | 1 | 1 | 1 | 0 |

| 1 | 127       | 5.05                       | 0         | 0   | 1 | 1                       | 1 | 1 | 1 | 1 | 1 | 0                                    | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | Overflow  | ≥ 5.07                     | 0         | 1   | 1 | 1                       | 1 | 1 | 1 | 1 | 1 | 0                                    | 1 | 1 | 1 | 1 | 1 | 1 |

|   |           |                            |           |     |   |                         |   |   |   |   |   |                                      |   |   |   |   |   |   |

Table 2. Mode Selection

| CE1 | CE2 | BIT 0<br>to BIT 6  | UNFL, OVFL         |

|-----|-----|--------------------|--------------------|

| X   | 0   | High-<br>impedance | High-<br>impedance |

| 0   | 1   | Active             | Active             |

| 1   | 1   | High-<br>impedance | Active             |

PNA7509

#### APPLICATION INFORMATION

The minimum and maximum values provided in the data sheet are guaranteed over the whole voltage and temperature range. This note gives additional information to the data sheet where the typical values indicate the behavior under nominal conditions;  $V_{DD5} = 5V$ ,  $V_{DD10} = 10V$

| SYMBOL                                | PARAMETER                                                                                                                                               | TYP            | UNIT       |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|------------|

| I <sub>DD5</sub>                      | Supply current (Pins 3, 12, 23)                                                                                                                         | 51             | mA         |

| I <sub>DD10</sub>                     | Supply current (Pin 24)                                                                                                                                 | 11             | mA         |

| f <sub>CLK</sub>                      | Maximum clock frequency                                                                                                                                 | 25             | MHz        |

| В                                     | Bandwidth (-3dB)                                                                                                                                        | 20             | MHz        |

| PD                                    | Total power dissipation                                                                                                                                 | 365            | mW         |

|                                       | Peak error (non-harmonic noise)                                                                                                                         | 1.5            | LSB        |

| f <sub>2, 3</sub><br>f <sub>4-7</sub> | Suppression of harmonics<br>sum of:<br>f <sub>2nd</sub> + f <sub>3rd</sub><br>f <sub>4th</sub> + f <sub>5th</sub> + f <sub>6th</sub> + f <sub>7th</sub> | 31<br>39       | dB<br>dB   |

| INL<br>DNL                            | Non-linearity<br>integral<br>differential                                                                                                               | ± 1/4<br>± 1/3 | LSB<br>LSB |

| $D_G$                                 | Differential gain                                                                                                                                       | ± 3            | %          |

| D <sub>P</sub>                        | Differential phase                                                                                                                                      | ± 1            | %          |

| P <sub>e</sub>                        | Large-signal phase error                                                                                                                                | 10             | deg        |

| S/N                                   | Signal-to-noise ratio (non-harmonic noise)                                                                                                              | -40            | dB         |

#### NOTE:

1. Typical values are measured on sample base.

#### Application Recommendation

Spikes at the 10V supply input have to be avoided (e.g., overshoots during switching). Even a spike duration of less than 1µs can destroy the device.

#### **Test Philosophy**

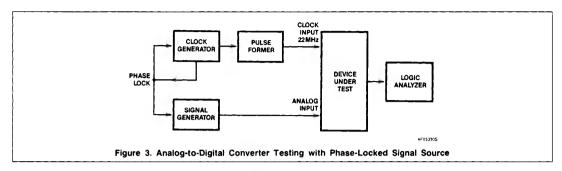

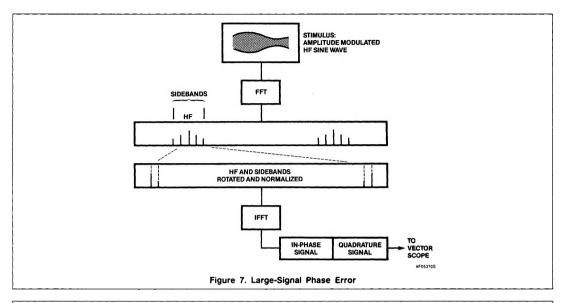

Figure 3 is a block diagram showing analog-to-digital testing with a phase-locked signal source. The signal generator provides a SMHz sine wave for the device under test (except for the linearity test). The 22MHz clock input is provided by the clock generator.

The phase relationship between signal and clock generator is shifted by 100ps each signal period to provide an effective clock rate of 10GHz for analysis.

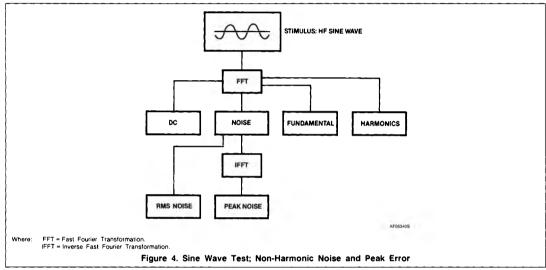

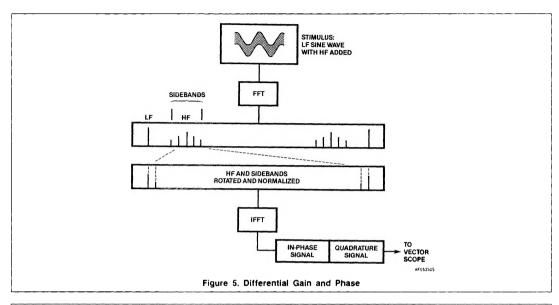

Most calculations are carried out in the spectral domain using Fast Fourier Transformation (FFT) and the inverse FFT to return to time domain.

The successive processing completes the specific measurement (Figures 4, 5, 6, and 7).

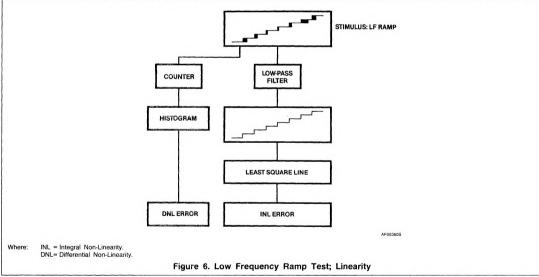

The non-linearities of the converter, integral (INL) and differential (DNL), are measured

using a low frequency ramp signal. Within a general uncertain range of conversion between two steps, the output signal of the converter randomly switches.

After low-pass filtering, the different step width is used for calculating the line of least squares to obtain integral non-linearity.

To calculate differential non-linearity, a counter is used to count the frequency of each step. A histogram is calculated from the counter result to provide the basis for further computation (Figure 6).

PNA7509

December 1988 5-78

## PNA7509

December 1988 5-79

## PNA7509

December 1988 5-80