# **Signetics**

# NE5150/5151/5152 Triple 4-Bit RGB D/A Converter With and Without Memory

**Product Specification**

#### Linear Products

### DESCRIPTION

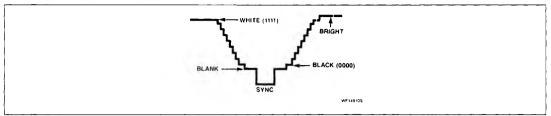

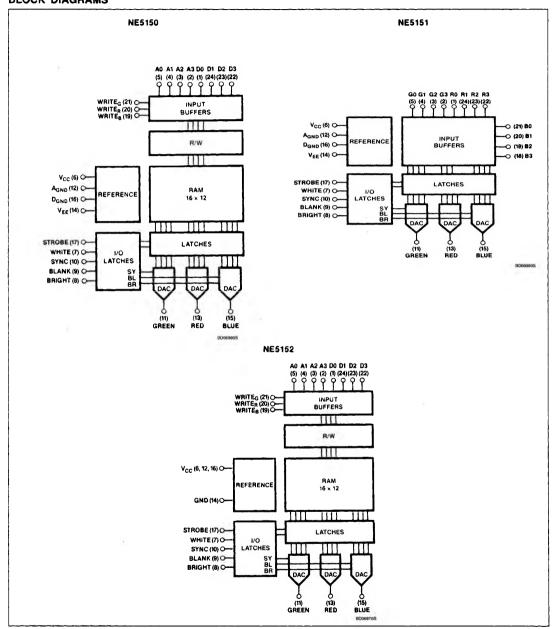

The NE5150/5151/5152 are triple 4-bit DACs intended for use in graphic display systems. They are a high performance - vet cost effective - means of interfacing digital memory and a CRT. The NE5150/5152 are single integrated circuit chips containing special input buffers, an ECL static RAM, high-speed latches, and three 4-bit DACs. The input buffers are user-selectable as either ECL or TTL compatible for the NE5150. The NE5152 is similar to the NE5150, but is TTL compatible only, and operates off of a single +5V supply. The RAM is organized as 16 × 12, so that 16 "color words" can be down-loaded from the pixel memory into the chip memory. Each 12-bit word represents 4 bits of red, 4 bits of green and 4 bits of blue information. This system gives 4096 possible colors. The RAM is fast enough to completely reload during the horizontal retrace time. The latches resynchronize the digital data to the DACs to prevent glitches. The DACs include all the composite video functions to make the output waveforms meet RS-170 and RS-343 standards, and produce 1V<sub>P,P</sub> into 75 $\Omega$ . The composite functions (reference white, bright, blank, and sync) are latched to prevent screen-edge distortions generally found on "video DACs." External components are kept to an absolute minimum (bypass capacitors only as needed) by including all reference generation circuitry and termination resistors on-chip, by building in

high-frequency PSRR (eliminating separate V<sub>EE</sub>s and costly power supplies and filtering), and by using a single-ended clock. The guaranteed maximum operating frequency for the NE5150/5152 is 110MHz over the commercial termperature range. The devices are housed in a standard 24-pin package and consume less than 1W of power.

The NE5151 is a simplified version of the NE5150, including all functions except the memory. Maximum operating frequency is 150MHz.

### **FEATURES**

- Single-chip

- On-board ECL static RAM

- 4096 colors

- ECL and TTL compatible

- 110MHz update rate (NE5150, 5152)

- 150MHz update rate (NE5151)

- Low power and cost

- $\bullet$  Drives 75 $\Omega$  cable directly

- Internal reference

- 40dB PSRR

- No external components necessary

### **APPLICATIONS**

- Bit-mapped graphics

- Super high-speed DAC

- Home computers

- Raster-scan displays

#### ORDERING INFORMATION

| DESCRIPTION        | TEMPERATURE RANGE | ORDER CODE |

|--------------------|-------------------|------------|

| 24-Pin Ceramic DIP | 0°C to +70°C      | NE5150F    |

| 24-Pin Ceramic DIP | 0°C to +70°C      | NE5151F    |

| 24-Pin Ceramic DIP | 0°C to +70°C      | NE5152F    |

| 24-Pin Plastic SOL | 0°C to +70°C      | NE5152D    |

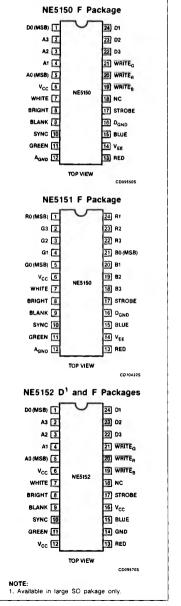

### PIN CONFIGURATIONS

# NE5150/5151/5152

### **BLOCK DIAGRAMS**

# NE5150/5151/5152

# ABSOLUTE MAXIMUM RATINGS

| SYMBOL                             | PARAMETER                                                  | RATING                                     | UNIT        |  |

|------------------------------------|------------------------------------------------------------|--------------------------------------------|-------------|--|

| T <sub>A</sub><br>T <sub>STG</sub> | Temperature range<br>Operating<br>Storage                  | 0 to +70<br>-65 to +150                    | °C<br>°C    |  |

| V <sub>CC</sub><br>V <sub>EE</sub> | Power supply                                               | 7.0<br>-7.0                                | V           |  |

|                                    | Logic levels<br>TTL-high<br>TTL-low<br>ECL-high<br>ECL-low | 5.5<br>-0.5<br>0.0<br>0 to V <sub>FF</sub> | V<br>V<br>V |  |

DC ELECTRICAL CHARACTERISTICS  $V_{CC}$  = +5V (TTL), 0V (ECL),  $V_{EE}$  = -5V, 0°C < T<sub>A</sub> < +70°C, for NE5150/5151;  $V_{CC}$  = +5V (TTL), GND = 0V for NE5152, unless otherwise noted.

|                 | 242445752                                                                      |                     |                   |                   |          |  |

|-----------------|--------------------------------------------------------------------------------|---------------------|-------------------|-------------------|----------|--|

| SYMBOL          | PARAMETER                                                                      | Min                 | Тур Мах           |                   | UNIT     |  |

|                 | Resolution                                                                     | 4                   |                   |                   | bits     |  |

|                 | Monotonicity                                                                   | 4                   |                   |                   | bits     |  |

| NL              | Non-linearity                                                                  |                     | ± 1/16            | ± 1/2             | LSB      |  |

| DNL             | Differential non-linearity                                                     |                     | ± 1/8             | ± 1               | LSB      |  |

|                 | Offset error (25°C) [1111] (BRT = 1)                                           |                     | - 1/5             | ± 1               | LSB      |  |

|                 | Gain error (25°C) [0000] (BRT = 1)                                             |                     | ± 1/2             | ± 1               | LSB      |  |

| V <sub>CC</sub> | Positive power supply (TTL mode) (NE5150)<br>(TTL mode) (NE5151)<br>(ECL mode) | 4.5<br>4.75<br>-0.1 | 5.0<br>5.0<br>0.0 | 5.5<br>5.5<br>0.1 | V<br>V   |  |

| VEE             | Negative power supply (TTL or ECL mode) (NE5150/5151)                          | -4.75               | -5.0              | -5.5              | V        |  |

| lcc             | Positive supply current (NE5150/5151)<br>(NE5152)                              |                     | 15<br>175         | 25<br>210         | mA<br>mA |  |

| IEE             | Negative supply current (NE5150)<br>(NE5151)                                   |                     | 175<br>145        | 210<br>175        | mA<br>mA |  |

|                 | Analog voltage range (ZS to FS)                                                |                     | 603               |                   | mV       |  |

|                 | Gain tracking (any two channels)                                               |                     |                   | ± 1/4             | LSB      |  |

| LSB             | Least significant bit                                                          |                     | 40.2              |                   | m۷       |  |

| EWH             | Enhanced white level (25°C) <sup>2</sup>                                       |                     | 0                 |                   | mV       |  |

| BS              | Bright shift (25°C)(0 to 1)                                                    |                     | 71.4              |                   | mV       |  |

| EBL             | Enhanced blanking level (25°C) <sup>2</sup>                                    |                     | -674              |                   | mV       |  |

| ESY             | Enhanced sync level (25°C) <sup>2</sup>                                        | -960                |                   |                   | mV       |  |

| R <sub>O</sub>  | Output resistance (25°C)                                                       | 67.5                | 75.0              | 82.5              | Ω        |  |

| V <sub>IH</sub> | TTL logic input high                                                           | 2.0                 |                   |                   | ٧        |  |

| VIL             | TTL logic input low                                                            |                     |                   | 0.8               | V        |  |

| 1 <sub>IH</sub> | TTL logic high input current (V <sub>IN</sub> = 2.4V)                          |                     |                   | 20                | μΑ       |  |

| կլ              | TTL logic low input current (V <sub>IN</sub> = 0.4V)                           |                     |                   | -1.6              | mA       |  |

| V <sub>IH</sub> | ECL logic input high                                                           | -1.045              | _                 |                   | ٧        |  |

| V <sub>IL</sub> | ECL logic input low                                                            |                     |                   | -1.48             | ٧        |  |

| I <sub>IH</sub> | ECL logic high input current (V <sub>IN</sub> = -0.8V)                         |                     |                   | -1.0              | mA       |  |

| l <sub>IL</sub> | ECL logic low input current (V <sub>IN</sub> ≈ -1.8V)                          |                     |                   | -1.0              | mA       |  |

# NE5150/5151/5152

**TEMPERATURE CHARACTERISTICS**  $V_{CC} = +5V$  (TTL), 0V (ECL),  $V_{EE} = -5V$ ,  $0^{\circ}C < T_A < +70^{\circ}C$ , for NE5150/5151;  $V_{CC} = +5V$  (TTL), GND = 0V for NE5152, unless otherwise noted.

| 0.44501 | PARAMETER                           |     | LIMITS |        |        |  |

|---------|-------------------------------------|-----|--------|--------|--------|--|

| SYMBOL  |                                     | Min | Тур    | Max    | UNIT   |  |

|         | Offset TC <sup>1</sup>              |     | ± 50   | ± 100  | ppm/°C |  |

|         | Gain TC <sup>1</sup>                |     | ± 70   | ± 200  | ppm/°C |  |

|         | Gain Tracking TC (any two channels) |     | ± 20   | ± 50   | ppm/°C |  |

|         | Enhanced white level TC1            |     | ± 50   | ± 100  | ppm/°C |  |

|         | Bright shift TC                     |     | ± 70   | ± 200  | ppm/°C |  |

|         | Enhanced blanking level TC          |     | ± 100  | ± 300  | ppm/°C |  |

|         | Enhanced sync level TC              |     | ± 100  | ± 300  | ppm/°C |  |

|         | Output resistance TC                |     | + 1000 | + 2000 | ppm/°C |  |

### NOTES:

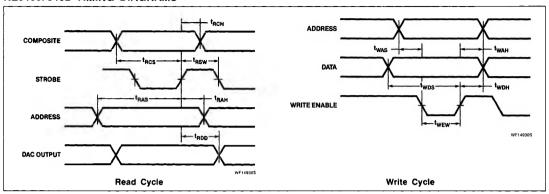

AC ELECTRICAL CHARACTERISTICS  $V_{CC}$  = +5V (TTL), 0V (ECL),  $V_{EE}$  = -5V, 0°C < T<sub>A</sub> < +70°C, for NE5150/5151;  $V_{CC}$  = +5V (TTL), GND = 0V for NE5152, unless otherwise noted.

| 01/11/001        |                                                 |                           | LIMITS |     |      |

|------------------|-------------------------------------------------|---------------------------|--------|-----|------|

| SYMBOL           | PARAMETER                                       | Min                       | Тур    | Max | UNIT |

| f <sub>MAX</sub> | Maximum operating frequency (NE5150/5152)       | 110                       |        |     | MHz  |

| twas             | Write address setup (NE5150/5152)               | 0                         |        |     | ns   |

| t <sub>WAH</sub> | Write address hold (NE5150/5152)                | 0                         |        |     | ns   |

| t <sub>WDS</sub> | Write data setup (NE5150/5152)                  | 4                         |        |     | ns   |

| twoH             | Write data hold (NE5150/5152)                   | 2                         |        |     | ns   |

| t <sub>WEW</sub> | Write enable pulse width (NE5150/5152)          | 3                         |        |     | ns   |

| t <sub>RCS</sub> | Read composite <sup>1</sup> setup (NE5150/5152) | 3                         |        |     | ns   |

| t <sub>RCH</sub> | Read composite <sup>1</sup> hold (NE5150/5152)  | 2                         |        |     | ns   |

| tRAS             | Read address setup (NE5150/5152)                |                           |        |     | ns   |

| t <sub>RAH</sub> | Read address hold (NE5150/5152)                 |                           |        |     | ns   |

| t <sub>RSW</sub> | Read strobe pulse width (NE5150/5152)           |                           | -      |     | ns   |

| t <sub>RDD</sub> | Read DAC delay (NE5150/5152)                    |                           | 8      |     | ns   |

| f <sub>MAX</sub> | Maximum operating frequency (NE5151)            | 150                       |        |     | MHz  |

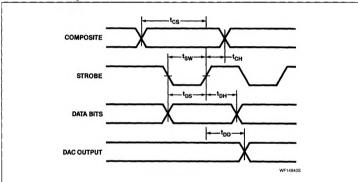

| tcs              | Composite <sup>1</sup> setup (NE5151)           | 3                         |        |     | ns   |

| tсн              | Composite <sup>1</sup> hold (NE5151)            | 2                         | 2      |     | ns   |

| t <sub>DS</sub>  | Data-bits setup (NE5151)                        | 1                         |        | ns  |      |

| t <sub>DH</sub>  | Data-bits hold (NE5151)                         | 5                         |        |     | ns   |

| t <sub>SW</sub>  | Strobe pulse width (NE5151)                     | pe pulse width (NE5151) 3 |        |     | ns   |

| t <sub>DD</sub>  | DAC delay (NE5151)                              |                           | 8      |     | ns   |

| t <sub>R</sub>   | DAC rise time (10 - 90%)                        |                           | 3      |     | ns   |

| ts               | DAC full-scale settling time <sup>2</sup>       |                           | 10     |     | ns   |

| C <sub>OUT</sub> | Output capacitance (each DAC)                   |                           | 10     |     | ρF   |

| SR               | Slew rate                                       |                           | 200    |     | V/μs |

<sup>1.</sup> Normalized to full-scale (603mV).

<sup>2.</sup> With respect to [1111] (BRT = 1).

# NE5150/5151/5152

| SYMBOL            | 242445752                                                    |     |     |     |      |

|-------------------|--------------------------------------------------------------|-----|-----|-----|------|

|                   | PARAMETER                                                    | Min | Тур | Max | UNIT |

| GE                | Glitch energy                                                |     |     | 30  | pV-s |

| PSRR <sup>3</sup> | Power supply rejection ratio (to red, green or blue outputs) |     |     |     |      |

|                   | V <sub>EE</sub> at 1kHz                                      |     | 43  |     | dB   |

|                   | V <sub>EE</sub> at 10MHz                                     | 1   | 28  |     | dB   |

|                   | V <sub>EE</sub> at 50MHz                                     |     | 14  |     | dB   |

|                   | V <sub>CC</sub> at 1kHz                                      |     | 80  |     | dB   |

|                   | V <sub>CC</sub> at 10MHz                                     |     | 50  |     | dB   |

|                   | V <sub>CC</sub> at 50MHz                                     | 1   | 36  |     | dB   |

#### NOTES:

- 1. Composite implies any of the WHITE, BRIGHT, BLANK or SYNC signals.

- 2. Setting to ± ½ LSB, measured from STROBE 50% point (rising edge). This time includes the delay throught the strobe input buffer and latch.

- 3. Listed PSRR is for the NE5150/51. The NE5152 PSRR specs are identical to the VEE numbers in the table.

#### **NE5150 PIN DESCRIPTION**

Write enable inputs use negative-true logic while all other inputs are positive-true. All inputs operate synchronously with the positive edge-triggered strobe input. When  $V_{\rm CC}$  is taken high (5V), all inputs are TTL compatible. When  $V_{\rm CC}$  is grounded, all inputs are ECL compatible. All DACs are complementary, so that all ones is the highest absolute voltage and all zeroes is the lowest. All ones is called zero-scale (ZS) and all zeroes is called full-scale (FS). The analog output voltage is approximately 0V (ZS) to -1V (SYNC).

Pins 1, 24, 23, 22: **DATA** bits D0 (MSB) through D3, used to input digital information to the memory during the write phase. During this phase, the data bits are presented to the internal latches (noninverted) and the DACs will output the analog equivalent of the stored word, unless overridden by WHITE, BLANK or SYNC.

Pins 5, 4, 3, 2: ADDRESS lines A0 (MSB) through A3, used for selecting a memory address to write to or read from.

Pin 7: WHITE command. Presets the latches to all ones [1111] and outputs 0V absolute on all DACs. Can be modified to -71mV absolute when BRIGHT is taken low. Will be overridden by either a BLANK or SYNC command.

Pin 8: **BRIGHT** command. A low input here turns on an additional -71mV (10 IRE unit) switch, shifting all other levels downward. Not overridden by any other input.

Pin 9: **BLANK** command. Presets the latches to all zeroes [0000] and turns on an additional –71mV (10 IRE unit) switch. Absolute output is –671mV. Can be modified another –71mV to –742mV absolute when BRIGHT is taken low. Will override WHITE, and will be overridden by SYNC.

Pin 10: SYNC command. Presets the latches to all zeroes [0000] and turns on the BLANK switch. Additionally turns on a -286mV (40 IRE unit) switch in the green channel only. Absolute output is -671mV for the red and blue channels, and -957mV for the green channel. All levels can be shifted -71mV by taking BRIGHT low. Overrides WHITE and BLANK.

Pins 11, 13, 15: **GREEN, RED, BLUE.** Analog outputs with  $75\Omega$  internal termination resistors. Can directly drive  $75\Omega$  cable and should be terminated at the display end of the line with  $75\Omega$ . Output voltage range is approximately 0V to -1V, independent of whether the digital inputs are ECL or TTL compatible. All outputs are simultaneously affected by the WHITE, BLANK or BRIGHT commands. Only the GREEN channel carries SYNC information.

#### NOTE:

There are 100 IRE units from WHITE to BLANK. One IRE unit is approximately 7.1mV. Full-scale is 90 IRE units and 10 IRE units is ½ of full-scale (e.g., BRIGHT function).

Pins 19, 20, 21: WRITE<sub>B</sub>, WRITE<sub>R</sub>, WRITE<sub>G</sub>. Write enable commands for each of the three  $16\times 4$  memories. When all write commands are high, then the READ operation is selected. This is the normal display mode. To write data into memory, the write enable pin is taken low. Data D0 – D3 will be written into address A0 – A3 of each memory when its corresponding write enable pin goes low.

Pin 17: **STROBE.** The strobe signal is the main system clock and is used for resynchronizing digital signals to the DACs. Preventing data skew eliminates glitches which would otherwise become visible color distortions on a CRT display. The strobe command has no special drive requirements and is TTL or ECL compatible.

Pins 12, 16:  $A_{GND}$ ,  $D_{GND}$ . Both Analog and Digital ground carry a maximum of approximately 100mA of DC current. For proper operation, the difference voltage between  $A_{GND}$  and  $D_{GND}$  should be no greater than 50mV, preferably less.

Pin 14: **V**<sub>EE</sub>. The negative power supply is the main chip power source. V<sub>CC</sub> is only used for TTL input buffers. As is usual, good bypassing techniques should be used. The chip itself has a good deal of power supply rejection — well up into the VHF frequency range — so no elaborate power supply filtering is necessary.

Pin 18: **NC.** This unused pin should be tied high or low.

# NE5150/5151/5152

#### NE5150/5152 TIMING DIAGRAMS

# NE5151 PIN DESCRIPTION AND TIMING DIAGRAM

The eleven digital inputs D0 – D3, A0 – A3, WRITE  $_{\mathrm{G/R/B}}$ , and the unused Pin 18 of the NE5150 are replaced in the NE5151 with the three 4-bit DAC digital inputs G0 – G3, R0 – R3, and B0 – B3. All other pin functions (e.g., composite functions, power supplies, strobe, etc.) are identical to the NE5150.

### **NE5152 PIN DESCRIPTION**

The NE5152 is a TTL-compatible-only version of the NE5150, operating off of a single +5V supply.  $V_{\rm CC}$  Pins 6, 12 and 16 should be connected to +5V and Pin 14 to 0V. DAC output is referenced to  $V_{\rm CC}$ .

# NE5151 TIMING DIAGRAM

### NE5150/NE5151/NE5152 LOGIC TABLE

| SYNC | BLANK | WHITE | BRIGHT | DATA   | ADDRESS | OUTPUT <sup>3</sup> | CONDITION                  |

|------|-------|-------|--------|--------|---------|---------------------|----------------------------|

| 1    | X     | ×     | 0      | ×      | X       | -1031mV             | SYNC <sup>1</sup>          |

| 1    | ×     | ×     | } 1    | X      | X       | -960mV              | Enhanced SYNC <sup>1</sup> |

| 0    | 1     | ×     | 0      | X      | X       | -746mV              | BLANK                      |

| 0    | 1     | X     | 1 1    | X      | X       | -674mV              | Enhanced BLANK             |

| 0    | 0     | 1     | 0      | X      | \ x     | -71mV               | WHITE                      |

| 0    | 0     | 1     | 1      | X      | X       | 0mV                 | Enhanced WHITE             |

| 0    | 0     | 0     | 0      | [0000] | Note 2  | -674mV              | BLACK (FS)                 |

| 0    | 0     | 0     | 1      | [0000] | Note 2  | ~603mV              | Enhanced BLACK (EFS)       |

| 0    | 0     | 0     | 0      | [1111] | Note 2  | -71mV               | WHITE (ZS)                 |

| 0    | 0     | 0     | 1      | [1111] | Note 2  | 0mV                 | Enhanced WHITE (EZS)       |

### NOTES:

- 1. Green channel output only. RED and BLUE will output BLANK or Enhanced BLANK under these conditions.

- 2. For the NE5150/5152 the DATA column represents the memory data accessed by the specific address. For the NE5151, the DATA is the direct digital inputs.

3. Note output voltages in Logic Table are referenced to  $V_{\text{CC}}$  for the NE5152 only.

# NE5150/5151/5152

# COMPOSITE VIDEO WAVEFORM