## ADDRESSABLE RELAY DRIVER

#### DESCRIPTION

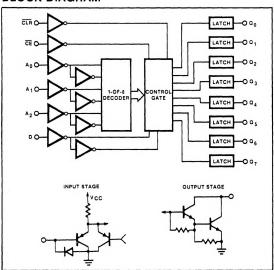

The NE5090 addressable relay driver is a high current latched driver, similar in function to the 9934 address decoder. The device has 8 open collector Darlington power outputs, each capable of 150mA load current. The outputs are turned on or off by respectively loading a logic "1" or logic "0" into the device data input. The required output is defined by a 3 bit address. The device must be enabled by a  $\overline{\text{CE}}$  input line which also serves the function of further address decoding. A common clear input,  $\overline{\text{CLR}}$ , turns all outputs off when a logic "0" is applied. The device is packaged in a 16 pln plastic or CERDIP package.

## **FEATURES**

- 8 high current outputs

- . Low-loading bus compatible inputs

- Power-on clear ensures safe operation

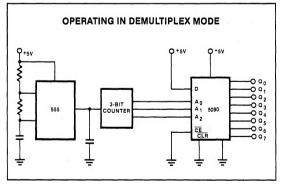

- Will operate in addressable or demultiplex mode

- . Allows random (addressed) data entry

- Easily expandable

- Pin compatible with 9334

#### **APPLICATIONS**

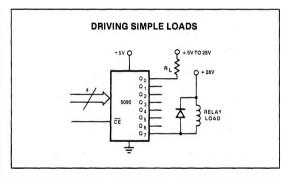

- Relay driver

- · Indicator lamp driver

- Triac trigger

- · LED display digit driver

- Stepper motor driver

#### **BLOCK DIAGRAM**

## **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$  °C unless otherwise specified.

|                                                      | PARAMETER                                                       | RATING                            | UNIT    |

|------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------|---------|

| V <sub>cc</sub>                                      | Supply voltage                                                  | - 0.5 to + 7                      | ٧       |

| VIN                                                  | Input voltage                                                   | - 0.5 to + 15                     | l v     |

| VOUT                                                 | Output voltage                                                  | 0 to + 30                         | l v     |

| IGND                                                 | Ground current                                                  | 500                               | mA      |

| lout                                                 | Output current                                                  | 200                               | mA      |

| P <sub>D</sub><br>Amble                              | Each output Power dissipation <sup>1</sup> nt temperature range | 1                                 | w<br>°C |

| T <sub>A</sub><br>T <sub>J</sub><br>T <sub>STG</sub> | NE5090<br>Junction<br>Storage                                   | 0 to + 70<br>150<br>- 65 to + 150 |         |

| T <sub>sold</sub>                                    | Lead soldering temperature<br>(10 sec max)                      | 300                               | °C      |

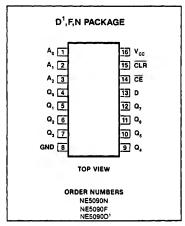

#### PIN CONFIGURATION

#### NOTE

- 1. SOL Released in Large SO package only.

- 2. SOL and non-standard pinout.

- 3. SO and non-standard pinouts.

# **ADDRESSABLE RELAY DRIVER**

## PIN DESIGNATION

| PIN NO.   | SYMBOL | NAME AND FUNCTION                                                                                                                                                                              |

|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-3       | A0-A2  | A 3-bit binary address on these pins defines which of the 8 output latches is to receive the data.                                                                                             |

| 4-7, 9-12 | Q0-Q7  | The 8 device outputs.                                                                                                                                                                          |

| 13        | D      | The data input. When the chip is enabled, this data bit is transferred to the defined output such that: "1" turns output switch "ON" "0" turns output switch "OFF"                             |

| 14        | CE     | The chip enable. When this input is low, the output latches will accept data. When CE goes high, all outputs will retain their existing state, regardless of address of data input conditions. |

| 15        | CLR    | The clear Input. When CLR goes low all output switches are turned "OFF". The high data input will override the clear function on the addressed latch.                                          |

## **TRUTH TABLE**

| INPUTS           |                  |        |                |                |                | OUTPUTS                               |                |                |                |                |                |                      | MODE           |             |

|------------------|------------------|--------|----------------|----------------|----------------|---------------------------------------|----------------|----------------|----------------|----------------|----------------|----------------------|----------------|-------------|

| CLR              | CE               | D      | A <sub>0</sub> | A <sub>1</sub> | A <sub>2</sub> | Q <sub>0</sub>                        | Q <sub>1</sub> | Q <sub>2</sub> | Q <sub>3</sub> | Q <sub>4</sub> | Q <sub>5</sub> | Q <sub>6</sub>       | Q <sub>7</sub> |             |

| L                | н                | х      | х              | Х              | х              | Н                                     | Н              | Н              | Н              | Н              | Н              | Н                    | Н              | Clear       |

| L<br>L<br>L<br>L | L<br>L<br>L      | LHLHLH | L              | LLLHH          | LLLHH          | TLITI                                 | HHHHH          | IIIIII         | IIIIII         | IIIIII         | IIIIII         | IIIIII               | 11111          | Demultiplex |

| н                | Н                | X      | X              | X              | X              | Q <sub>N</sub>                        | -1-            |                |                |                |                |                      | -              | Memory      |

| 11111            | L<br>L<br>L<br>L | LHLHLH |                | LLLLHH         | LLLHH          | H O <sub>N-1</sub> L O <sub>N-1</sub> |                |                |                |                |                | Addressable<br>Latch |                |             |

## DC ELECTRICAL CHARACTERISTICS $V_{CC} = 4.75V$ to 5.25V, $0^{\circ}C \le T_A \le 70^{\circ}C$ unless otherwise specified (NE5090)<sup>2</sup>.

|                  | PARAMETER                                       | TEST CONDITIONS                                                     |     |                |              |      |  |

|------------------|-------------------------------------------------|---------------------------------------------------------------------|-----|----------------|--------------|------|--|

|                  | PARAMETER                                       | TEST CONDITIONS                                                     | Min | Тур            | Max          | UNIT |  |

| V <sub>IH</sub>  | Input voltage<br>High<br>Low                    |                                                                     | 2.0 |                | 0.8          | v    |  |

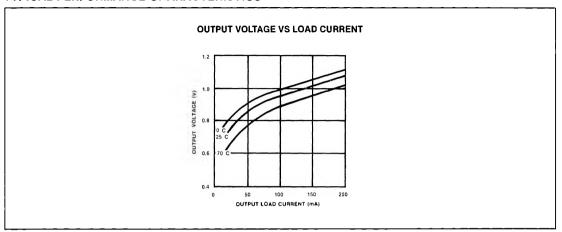

| V <sub>OL</sub>  | Output voltage<br>Low                           | I <sub>OL</sub> = 150mA, T <sub>A</sub> = 25 °C<br>Over temperature |     | 1.05           | 1.30<br>1.50 | v    |  |

| I <sub>IH</sub>  | Input current<br>High<br>Low                    | V <sub>IN</sub> = V <sub>CC</sub><br>V <sub>IN</sub> = 0V           |     | < 1.0<br>- 3.0 | 10<br>- 250  | μΑ   |  |

| I <sub>OH</sub>  | Leakage current                                 | V <sub>OUT</sub> = 28V,                                             |     | 5              | 250          | μΑ   |  |

| I <sub>CCL</sub> | Supply current All outputs low All outputs high | V <sub>CC</sub> = 5.25V NE5090                                      |     | 35<br>22       | 60<br>50     | mA   |  |

### NOTES

X = Don't care condition

QN-1 = Previous output state

L = Low voltage level/"ON" output state

H = High voltage level/"OFF" output state

<sup>1.</sup> Derate power dissipation as indicated above threshold ambient temperature NE5090 N at 9.3mW/°C above 85°C NE5090 F at 7.5mW/°C above 65°C

<sup>2.</sup> All typical values are at  $V_{CC} = 5V$  and  $T_A = 25^{\circ}C$

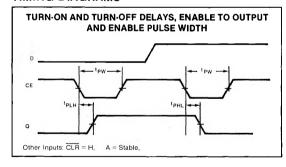

**SWITCHING CHARACTERISTICS**  $V_{CC} = 5V$ ,  $T_A = 25$  °C,  $V_{OUT} = 5V$ ,  $I_{OUT} = 100$  mA,  $V_{IL} = 0.8V$ ,  $V_{IH} = 2.0V$

|                                            | PARAMETER                                                                      | то                         | FROM                  | Min          | Тур        | Max         | UNIT |

|--------------------------------------------|--------------------------------------------------------------------------------|----------------------------|-----------------------|--------------|------------|-------------|------|

| t <sub>PLH</sub>                           | Propagation delay time<br>Low to high <sup>1</sup><br>High to low <sup>1</sup> | Output                     | Œ                     |              | 900<br>130 | 1800<br>260 | ns   |

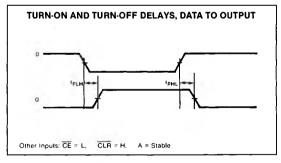

| t <sub>PLH</sub><br>t <sub>PHL</sub>       | Low to high <sup>2</sup><br>High to low <sup>2</sup>                           | Output                     | Data                  |              | 920<br>130 | 1850<br>260 | ns   |

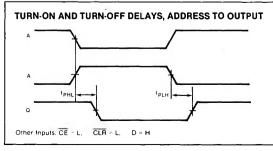

| t <sub>PLH</sub><br>t <sub>PHL</sub>       | Low to high <sup>3</sup><br>High to low <sup>3</sup>                           | Output                     | Address               |              | 900<br>130 | 1800<br>260 | ns   |

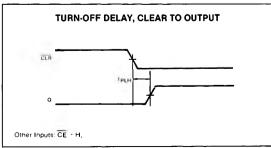

| t <sub>PLH</sub><br>t <sub>PHL</sub>       | Low to high <sup>4</sup><br>High to low <sup>4</sup>                           | Output                     | CLR                   |              | 920        | 1850        | ns   |

| SWITC                                      | HING SETUP REQUIREMENT                                                         | S                          |                       |              |            |             |      |

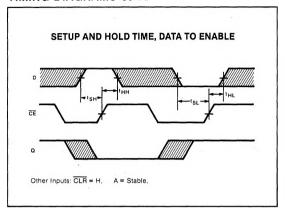

| t <sub>s(H)</sub> 5<br>t <sub>s(L)</sub> 5 |                                                                                | Chip enable<br>Chip enable | High data<br>Low data | 5<br>10      | 20<br>30   |             | ns   |

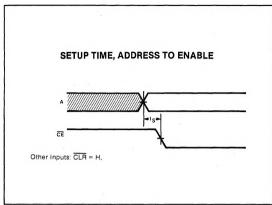

| t <sub>s(A)</sub> 6                        |                                                                                | Chip enable                | Address               | 0            | 20         |             | ns   |

| t <sub>n(H)</sub> 5<br>t <sub>H(L)</sub> 5 |                                                                                | Chip enable<br>Chip enable | High data<br>Low data | + 10<br>+ 10 | 0          |             | ns   |

| t <sub>pw(E)</sub> 1                       | Chip enable pulse width <sup>1</sup>                                           |                            |                       | 0            | 20         |             | ns   |

#### NOTES

- 1. See Turn-On and Turn-Off Delays, Enable to Output and Enable Pulse Width timing diagram.

- 2. See Turn-On and Turn-Off Delays, Data to Output timing diagram.

- 3. See Turn-On and Turn-Off Delays, Address to Output timing diagram.

- 4. See Turn-Off Delay, Clear to Output timing diagram.

- 5. See Setup and Hold Time, Data to Enable timing diagram.

- 6. See Setup Time, Address to Enable timing diagram.

#### **TIMING DIAGRAMS**

## **NE5090**

# **ADDRESSABLE RELAY DRIVER**

## TIMING DIAGRAMS (Cont'd)

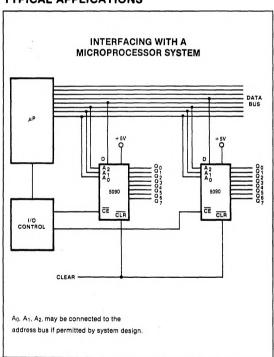

## TYPICAL APPLICATIONS

## **TYPICAL PERFORMANCE CHARACTERISTICS**