# **OKI semiconductor** MSM82C84ARS/GS

CLOCK GENERATOR AND DRIVER

#### **GENERAL DESCRIPTION**

The MSM82C84ARS/GS is a clock generator designed to generate MSM80C86 and MSM80C88 system clocks. Due to the use of silicon gate CMOS technology, standby current is only 100µA (MAX.), and the power consumption is very low with 10 mA (MAX.) when a 5 MHz clock is generated.

## **FEATURES**

- Operating frequency of 6 to 15 MHz (CLK output 2 to 5 MHz)

- $\bullet$   $3\mu$  silicon gate CMOS technology for low power consumption

- Built-in crystal oscillator circuit

- 3V ~ 6V single power supply

- Built-in synchronized circuit for MSM80C86 and MSM80C88 READY and RESET

- TTL compatible

- Built-in Schmitt trigger circuit (RES input)

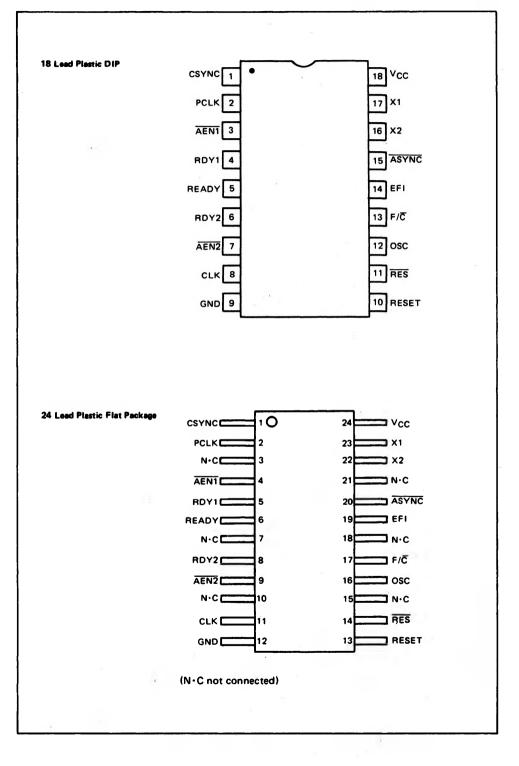

- 18-pin DIP (MSM82C84ARS)

- 24-pin flat package (MSM82C84AGS)

#### PIN CONFIGURATION

# I/O·MSM82C84ARS/GS

# ABSOLUTE MAXIMUM RATINGS

| Parameter           | Sumbal | Lin         | nits                 | Unit | Conditions     |

|---------------------|--------|-------------|----------------------|------|----------------|

|                     | Symbol | MSM82C84ARS | MSM82C84AGS          |      |                |

| Supply Voltage      | Vcc    | -0.5        | ~ +7                 | v    |                |

| Input Voltage       | VIN    | -0.5 ~ \    | / <sub>CC</sub> +0.5 | v    | Respect to GND |

| Output Voltage      | Vout   | -0.5 ~ \    | /CC +0.5             | v    | }              |

| Storage Temperature | Tstg   | -55 ~ +150  |                      | °C   | _              |

| Power Dissipation   | PD     | 0.8         | 0.7                  | w    | Ta = 25°C      |

# **OPERATING RANGES**

| Parameter             | Symbol | Limits    | Unit |

|-----------------------|--------|-----------|------|

| Supply Voltage        | Vcc    | 3~6       | v    |

| Operating Temperature | Тор    | -40 ~ +85 | °C   |

# RECOMMENDED OPERATING CONDITIONS

| Parameter                            | Symbol | MIN  | TYP | MAX                  | Unit |

|--------------------------------------|--------|------|-----|----------------------|------|

| Supply Voltage                       | Vcc    | 4.5  | 5   | 5.5                  | v    |

| Operating Temperature                | Тор    | -40  | +25 | +85                  | °C   |

| "L" Level Input Voltage              | VIL    | -0.3 |     | +0.8                 | v    |

| "H" Level Input Voltage (except RES) |        | 2.2  |     |                      | v    |

| "H" Level Input Voltage (RES)        | — ∨ін  | 3.0  |     | V <sub>CC</sub> +0.3 | v    |

## DC CHARACTERISTICS

| Parameter                | Symbol        | MIN  | MAX  | Unit | Conditions                                                                                                                                                                                                                 | ;                               |

|--------------------------|---------------|------|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| "L" Level Output Voltage | VOL           | -    | 0.45 | v    | I <sub>OL</sub> = 5mA                                                                                                                                                                                                      |                                 |

| "H" Level Output Voltage | Voн           | 3.7  | -    | v    | IOH = −1mA                                                                                                                                                                                                                 |                                 |

| RES Input Hysteresis     | VIHR<br>-VILR | 0.25 | -    | v    |                                                                                                                                                                                                                            |                                 |

| Input Leak Current       | 1.1           | -10  | 10   | μA   | 0 ≦ VIN ≦ VCC                                                                                                                                                                                                              | V <sub>CC</sub> = 4.5V          |

| Standby Supply Current   | Iccs          | -    | 100  | μA   | $\begin{array}{c} X1 \stackrel{>}{=} V_{CC} - 0.2V \\ X2 \stackrel{<}{\leq} 0.2V \\ F/\overline{C} \stackrel{>}{=} V_{CC} - 0.2V \\ V_{IH} \stackrel{>}{=} V_{CC} - 0.2V \\ V_{IL} \stackrel{\leq}{\leq} 0.2V \end{array}$ | ~ 5.5V<br>Ta = -40°C<br>~ +85°C |

| Operating Supply Current | Icc           | -    | 10   | mA   | Input frequency<br>15 MHz<br>Output load capecitance<br>CL = OpF                                                                                                                                                           |                                 |

# AC CHARACTERISTICS

$(V_{CC} = 5V \pm 10\%, Ta = -40 \sim 85^{\circ}C)$

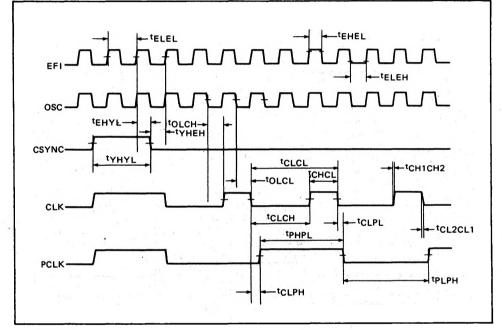

(1)

| Parameter                                                     | Symbol             | MIN       | ΜΑΧ | Unit | Cond            | litions                |

|---------------------------------------------------------------|--------------------|-----------|-----|------|-----------------|------------------------|

| EFI "H" Pulse Width                                           | TEHEL              | 20        |     | ns   | 90%-90%         |                        |

| EFI "L" Pulse Width                                           | TELEH              | 20        |     | ns   | 10%-10%         |                        |

| EFI Cycle Time                                                | TELEL              | 66        |     | ns   |                 |                        |

| Crystal Oscillator Frequency                                  |                    | 6         | 15  | MHz  | a.              |                        |

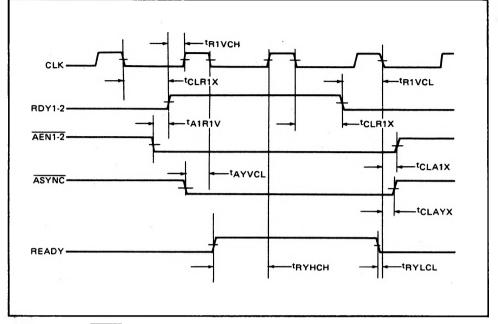

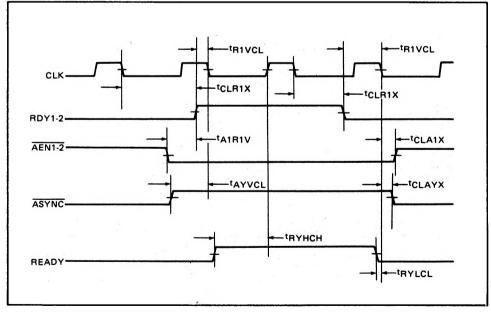

| Set Up Time of RDY1 or RDY2 to<br>CLK Falling Edge (Active)   | tR1VCL             | 35        |     | ns   | ASYNC<br>= High |                        |

| Set Up Time of RDY1 or RDY2 to CLK Rising Edge (Active)       | <sup>t</sup> R1VCH | 35        |     | ns   | ASYNC<br>= Low  |                        |

| Set Up Time of RDY1 or RDY2 to<br>CLK Falling Edge (Inactive) | <sup>t</sup> R1VCL | 35        |     | ns   |                 | Output load            |

| Hold Time of RDY1 or RDY2 to<br>CLK Falling Edge              | <sup>t</sup> CLR1X | 0         |     | ns   |                 | capacitance            |

| Set Up Time of ASYNC to CLK<br>Falling Edge                   | TAYVCL             | 50        |     | ns   |                 | C <sub>L</sub> = 100pF |

| Hold Time of ASYNC to CLK<br>Falling Edge                     | <sup>t</sup> CLAYX | 0         |     | ns   |                 | Others 30pF            |

| Set Up Time of AEN1 (AEN2) to<br>RDY1 (RDY2) Rising Edge      | <sup>t</sup> A1R1V | 15        |     | ns   |                 |                        |

| Hold Time of AEN1 (AEN2) to<br>CLK Falling Edge               | <sup>t</sup> CLA1X | 0         |     | ns   |                 |                        |

| Set Up Time of CSYNC to EFI<br>Rising Edge                    | <sup>t</sup> YHEH  | 20        |     | ns   |                 |                        |

| Hold Time of CSYNC to EFI Rising<br>Edge                      | <sup>t</sup> ehyl  | 10        |     | ns   |                 |                        |

| CSYNC Pulse Width                                             | <sup>t</sup> YHYL  | 2 × tELEL |     | ns   | \$              | ]                      |

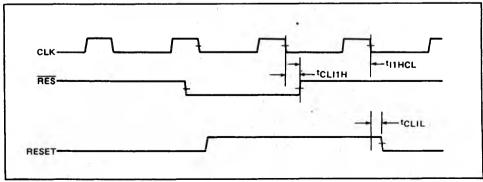

| Set Up Time of RES to CLK Falling<br>Edge                     | ti1HCL             | 65        |     | ns   |                 |                        |

| Hold Time of RES to CLK Falling<br>Edge                       | <sup>t</sup> CLI1H | 20        |     | ns   |                 |                        |

| Input Rising Edge Time                                        | tilih              |           | 20  | ns   | 1               |                        |

| Input Falling Edge Time                                       | THIL               |           | 20  | ns   |                 |                        |

Note: Parameters where timing has not been indicated in the above table are measured at  $V_L$  = 1.5V and  $V_H$  = 1.5V for both inputs and outputs.

## AC CHARACTERISTICS

$(V_{CC} = 5V \pm 10\%, Ta = -40 \sim 85^{\circ}C)$

(2)

| Parameter                                            | Symbol                                     | MIN | MAX | Unit | Cond      | itions                    |

|------------------------------------------------------|--------------------------------------------|-----|-----|------|-----------|---------------------------|

| CLK Cycle Time                                       | <sup>†</sup> CLCL                          | 200 |     | ns   |           |                           |

| CLK "H" Pulse Width                                  | <sup>t</sup> CHCL                          | 65  |     | ns   |           |                           |

| CLK "L" Pulse Width                                  | 1CLCH                                      | 119 |     | ns   |           |                           |

| CLK Rising and Falling Edge Times                    | <sup>t</sup> CH1CH2<br><sup>t</sup> CL2CL1 |     | 15  | ns   | 1.0V-3.5V |                           |

| PCLK "H" Pulse Width                                 | <sup>t</sup> PHPL                          | 180 |     | ns   |           |                           |

| PCLK "L" Pulse Width                                 | <sup>t</sup> PLPH                          | 180 |     | ns   |           |                           |

| Time from READY Falling Edge to<br>CLK Falling Edge  | <sup>t</sup> RYLCL                         | -8  |     | ns   |           | Output load               |

| Time from READY Rising Edge to<br>CLK Rising Edge    | <b>tRYHCH</b>                              | 114 |     | ns   |           | capacitance<br>CLK output |

| Delay from CLK Falling Edge to<br>RESET Falling Edge | <sup>t</sup> CLIL                          |     | 40  | ns   |           | CL = 100pF<br>Others 30pF |

| Delay from CLK Falling Edge to<br>PCLK Rising Edge   | <sup>t</sup> CLPH                          |     | 22  | ns   |           |                           |

| Delay from CLK Falling Edge to<br>PCLK Falling Edge  | <sup>t</sup> CLPL                          |     | 22  | ns   |           |                           |

| Delay from OSC Falling Edge to CLK<br>Rising Edge    | <sup>t</sup> OLCH                          | -5  | 22  | ns   |           |                           |

| Delay from OSC Falling Edge to CLK<br>Falling Edge   | tOLCL                                      | 2   | 35  | ns   |           |                           |

| Output Rising Edge Time (Except CLK)                 | toloh                                      |     | 15  | ns   | 0.8V~2.2V |                           |

| Output Falling Edge Time (Except CLK)                | 10HOL                                      |     | 15  | ns   | 2.2V~0.8V |                           |

Note: Parameters where timing has not been indicated in the above table are measured at  $V_{L}$  = 1.5V and  $V_{H}$  = 1.5V for both inputs and outputs.

## PIN DESCRIPTION

| Pin symbol   | Name                               | Input/<br>output | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|--------------|------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

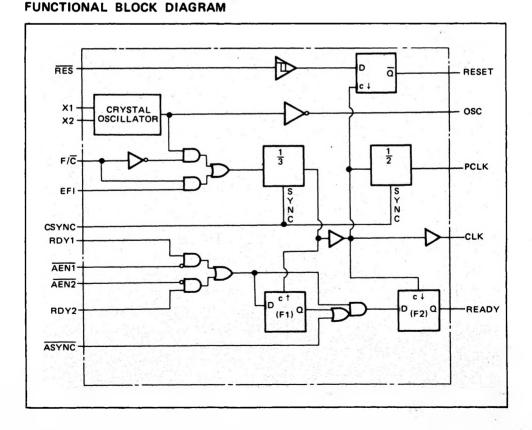

| CSYNC        | Clock<br>synchronization<br>signal | Input            | Synchronizing signal for output of in-phase CLK signals when more<br>than one MSM82C84A is used.<br>The internal counter is reset when this signal is at high level, and a<br>high level CLK output is generated. The internal counter is sub-<br>sequently activated and a 33% duty CLK output is generated when<br>this signal is switched to low level.<br>When this signal is used, external synchronization of EFI is necessary.<br>When the internal oscillator is used, it is necessary for this pin to<br>be kept to be low level. |  |  |  |  |

| PCLK         | Peripheral clock<br>output         | Output           | This peripheral circuit clock signal is output in a 50% duty cycle at a frequency half that of the clock signal.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| AEN1<br>AEN2 | Address enable<br>signals          | Input            | The AEN1 signal enables RDY1, and the AEN2 signal enables RDY2.<br>The respective RDY inputs are activated when the level applied to<br>these pins is low.<br>Although two separate inputs are used in multi-master systems, only<br>the AEN which enables the RDY input to be used is to be switched<br>to low level in the case of not using multi-master systems.                                                                                                                                                                       |  |  |  |  |

| RDY1<br>RDY2 | Bus ready signals                  | Input            | Completion of data bus reading and writing by the device conr<br>to the system data bus is indicated when one of these sigr<br>switched to high level.<br>The relevant RDY input is enabled only when the corresponding<br>is at low level.                                                                                                                                                                                                                                                                                                |  |  |  |  |

| READY        | Ready output                       | Output           | This signal is obtained by synchronizing the bus ready signal with CLK.<br>This signal is output after guaranteeing the hold time for the CPU in phase with the RDY input.                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| CLK          | Clock output                       | Output           | This signal is the clock used by the CPU and peripheral devices con-<br>nected to the CPU system data bus. The output waveform is gener-<br>ated in a 33% duty cycle at a frequency 1/3 the oscillating frequency<br>of the crystal oscillator connected to the X1 and X2 pins, or at a<br>frequency 1/3 the EFI input frequency.                                                                                                                                                                                                          |  |  |  |  |

| RES          | Reset in                           | Input            | This low-level active input is used to generate a CPU reset signal.<br>Since a Schmitt trigger is included in the input circuit for this signal,<br>"power on resetting" can be achieved by connection of a simple RC<br>circuit.                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| RESET        | Reset output                       | Output           | This signal is obtained by CLK synchronization of the input signal applied to RES and is output in opposite phase to the RES input. This signal is applied to the CPU as the system reset signal.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| F/C          | Clock select signal                | Input            | This signal selects the fundamental signal for generation of the CLK sig-<br>nal. The CLK is generated from the crystal oscillator output when this<br>signal is at low level, and from the EFI input signal when at high level.                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| EFI          | External clock<br>signal           | Input            | The signal applied to this input pin generates the CLK signal when $F/\overline{C}$ is at high level. The frequency of the input signal needs to be three times greater than the desired CLK frequency.                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| X1, X2       | Crystal oscillator connecting pins | Input            | Crystal oscillator connections.<br>The crystal oscillator frequency needs to be three times greater than<br>the desired CLK frequency.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| OSC          | Crystal resonator<br>output        | Output           | Crystal oscillator output. This output frequency is the same as the oscillating frequency of the oscillator connected to the X1 and X2 pins. As long as a Xtal oscillator is connected to the X1 and X2 pins, this output signal can be obtained independently even if F/C is set to high level to enable the EFI input to be used for CLK generation purposes.                                                                                                                                                                            |  |  |  |  |

# I/O·MSM82C84ARS/GS =

| Pin symbol | Name                                      | Input/<br>output | Function                                                                                                                                                                                                                                                                                                                                                                               |

|------------|-------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ASYNC      | Ready<br>synchronization<br>select signal | Input            | Signal for selection of the synchronization mode of the READY<br>signal generator circuit. When this signal is at low level, the READY<br>signal is generated by double synchronization. And when at high<br>level, the READY signal is generated by single synchronization.<br>Since this pin has not been equipped with internal pull-up resistance,<br>this pin must not be opened. |

| vcc        |                                           |                  | +5V power supply                                                                                                                                                                                                                                                                                                                                                                       |

| GND        |                                           |                  | GND                                                                                                                                                                                                                                                                                                                                                                                    |

### TIMING CHART

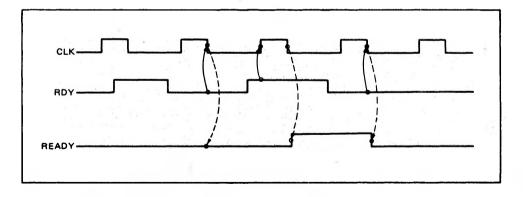

#### READY waveform (ASYNC = L)

#### DESCRIPTION OF OPERATION

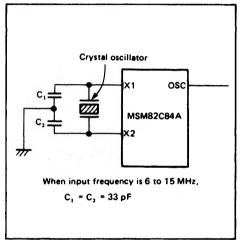

#### (1) Oscillator Circuit

The MSM82C84A internal oscillator circuit can be driven by connecting a crystal oscillator to the X1 and X2 pins.

The frequency of the crystal oscillator in this case needs to be three times greater than the desired CLK frequency.

Since the oscillator circuit output (the same output as for the crystal resonator frequency) appears at the OSC pin, independent use of this output is also possible.

#### Recommended Oscillator Circuit

#### (2) Clock Generator Circuit

This circuit generates two clock outputs-CLK obtained by dividing the input external clock or crystal oscillator circuit output by three, and PCLK obtained by halving CLK. CLK and PCLK are generated from the external clock applied to the EFI pin when  $F/\overline{C}$  is at high level, and are generated from the crystal oscillator circuit when at low level.

#### (3) Reset Circuit

Since a Schmitt trigger circuit is used in the RES input, the MSM82C84A can be reset by "power on" by connection to a simple RC circuit. If the 80C86 or 80C88 is used as the CPU in this case, it is necessary to keep the RES input at low level for at least 50  $\mu$ s after V<sub>CC</sub> reaches the 4.5V level.

#### (4) Ready Circuit

The READY signal generator circuit can be set to synchronization mode by ASYNC.

- (i) When ASYNC is at low level

- The RDY input is output as the READY signal by double synchronization.

The high-level RDY input is synchronized once by the rising edge of the CLK of the first stage flipflop (F1 in the circuit diagram), and then synchronized again by the falling edge of the CLK of the next stage flip-flop (F2 in the circuit diagram), resulting in output of a high-level READY output signal (see diagram below).

The low-level RDY input is synchronized directly by the falling edge of the CLK of the next stage flip-flop, resulting in output of a low-level READY output signal (see diagram below).

synchronized by the falling edge of the CLK of the

(ii) When ASYNC is at high level The RDY input is output as the READY signal by

next stage flip-flop, resulting in output of respective low-level and high-level READY output signals single synchronization. · Both low-level and high-level RDY inputs are (see diagram below).

CLK. RDY READY

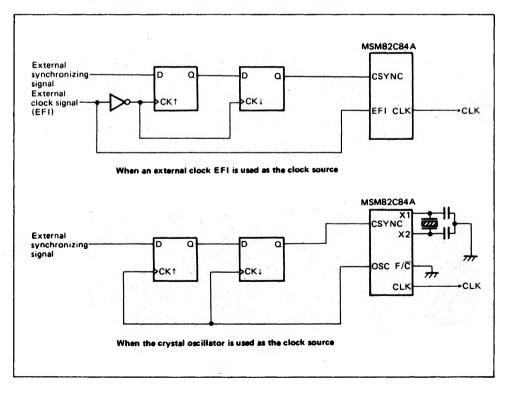

#### EXAMPLE OF USE (CSYNC)

The 82C84A 1/3 frequency divider counter is unsettled when the power is switched on. Therefore, the CSYNC pin has been included to synchronize CLK with another signal. When CSYNC is at high level, both CLK and PCLK are high-level outputs. If CSYNC is then

switched to low level, CLK is output from the next input clock rising edge, and is divided by 3.

If CSYNC has not been synchronized with the input clock, use the following circuit to achieve the required synchronization.