# **OKI** semiconductor

# MSM82C12RS/GS

## 8-BIT INPUT/OUTPUT PORT

### GENERAL DESCRIPTION

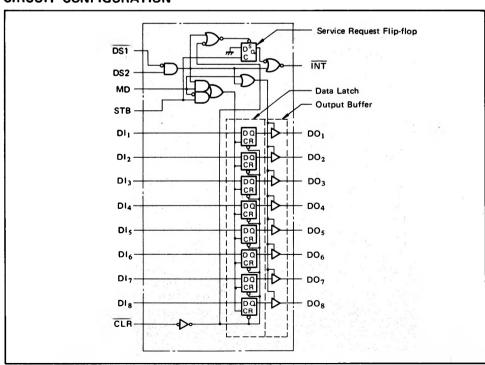

The MSM82C12 is an 8 bit input output port employing 3  $\mu$  silicon gate CMOS technology. It insures low operating power. This device incorporates a service request flip-flop for generation and control of interrupts for a CPU, in addition to an 8-bit latch circuit having a three-state output buffer.

It is effective when used as an address latch device to separate the time division bus line outputs in systems employing the MSM80C85A CPU or similar processors using multiplexed address/data bus line.

#### **FEATURES**

- Operated on low power consumption due to silicon gate CMOS.

- 3 V ~ 6 V single power supply

- Full static operation

- Parallel 8-bit data register and buffer

- Provided with an interrupt generating function through the adoption of a service request flip-flop

- Equipped with a clear terminal which operates asynchronously

- TTL compatible

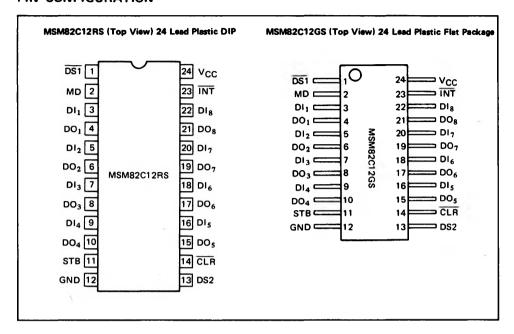

- 24-pin DIP (MSM82C12RS)

- 24-pin flat package (MSM82C12GS)

- Functionally compatible with the 8212

## CIRCUIT CONFIGURATION

## PIN CONFIGURATION

# PIN DESCRIPTION

| Pin Name Item DI <sub>1</sub> ~DI <sub>8</sub> Data input |                     | Input/Output | Function                                                                                                                                                                                                     |  |  |

|-----------------------------------------------------------|---------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                           |                     | Input        | These pins are 8-bit data inputs. The data input is connected to the input D pins of the 8-bit data latch circuit built inot the device.                                                                     |  |  |

| DO <sub>1</sub> ~DO <sub>8</sub>                          | Data output         | Output       | These pins are 8-bit data outputs. Each bit is composed of 3-<br>state output buffers.<br>These buffers can be made into enable or disable (high imped-<br>ance status).                                     |  |  |

| MD                                                        | Mode input          | Input        | This pin is a clock input for the data latch. It is also used to reset the internal service request flip-flop at the same time.                                                                              |  |  |

| STB                                                       | Strobe input        | Input        | This pin is a clock input for the data latch. It is also used to reset the internal service request flip-flop at the same time.                                                                              |  |  |

| DS1, DS2                                                  | Device select input | Input        | The AND of these two input functions make the status control of output buffers or becomes a clock input to the data latch. It also functions to perform set/reset of the internal service request flip-flop. |  |  |

| CLR                                                       | Clear input         | Input        | This pin clears the internal data latch in low level. It also sets the internal service request flip-flop at this time. The clear is operated asynchronously to the clock.                                   |  |  |

| INT                                                       | Interrupt<br>output | Output       | This pin is the ouput of the internal service request flip-flop, but is inverted to ouptut it in low level operation.                                                                                        |  |  |

| Vcc                                                       |                     |              | +5V power supply                                                                                                                                                                                             |  |  |

| GND                                                       |                     |              | GND                                                                                                                                                                                                          |  |  |

## **FUNCTIONAL DESCRIPTION**

# Output Buffer Status Control and Data Latch Clock Input

When the input MD is at high level, the ouptut buffer is enabled and the device select input (DS1.DS2) becomes the clock input to the data latch. When the input MD is in low level, the status of the output buffer is determined by the device select input (DS1.DS2) (the output buffer is enabled when (DS1.DS2) is in high level). At this time, the input STB becomes the clock input to the data latch.

| MD | (DS1 - DS2) | STB | DO1 ~ DO8             |

|----|-------------|-----|-----------------------|

| 0  | 0           | 0   | High impedance status |

| 0  | 0           | 1   | High impedance status |

| 1  | 0           | 0   | Data latch            |

| 1  | 0           | 1   | Data latch            |

| 0  | 1 0         | 0   | Data latch            |

| 0  | 1           | 1   | Data in               |

| 1  | 0 1         | 0   | Data in               |

| 1  | 1           | 1   | Data in               |

|    |             |     |                       |

#### Service Request Flip-flop

The service request flip-flop is used to generate and control the interrupt for the CPU when the MSM82C12 is used as an input/output port in a microcomputer system. The flip-flop is set asynchronously by input CLR. When the flip-flop is set, the system is in non-

| inter | rupt | sta | tus. |

|-------|------|-----|------|

|       |      |     | _    |

| CLR | (DS1 · DS2) | STB | a | INT |

|-----|-------------|-----|---|-----|

| 0   | 0           | 0   | 1 | 1   |

| 0   | 1           | 0   | 1 | 0   |

| 1   | 1           | 7_  | 1 | 0   |

| 1   | 1           | 0   | 1 | 0   |

| 1   | o           | 0   | 1 | 1   |

| 1   | 0           | _   | 0 | 0   |

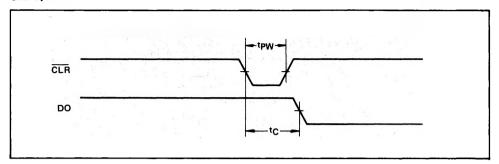

#### Clear

When the clear input becomes low level, the internal data latch is cleared irrespective of the clock and becomes low level.

# **ABSOLUTE MAXIMUM RATINGS**

| Danamana            | Cumbal            | A         | Lin         |                              |      |  |

|---------------------|-------------------|-----------|-------------|------------------------------|------|--|

| Parameter           | Symbol Conditions |           | MSM82C12RS  | MSM82C12GS                   | Unit |  |

| Supply Voltage      | Vcc               | With      | -0.5 to     | +7                           | V    |  |

| Input Voltage       | VIN               | respect   | -0.5 to '   | V                            |      |  |

| Output Voltage      | Vout              | to GND    | -0.5 to     | -0.5 to V <sub>CC</sub> +0.5 |      |  |

| Storage Temperature | Tstg              |           | -55 to +150 |                              | °c   |  |

| Power Dissipation   | PD                | Ta = 25°C | 0.9         | 0.7                          | W    |  |

## **OPERATING RANGE**

| Parameter             | Symbol | Limits     | Unit |

|-----------------------|--------|------------|------|

| Supply Voltage        | Vcc    | 3 to 6     | V    |

| Operating Temperature | TOP    | -40 to +85 | °c   |

# RECOMMENDED OPERATING CONDITION

| Parameter             | Symbol | Min. | Typ. | Max.                 | Unit |

|-----------------------|--------|------|------|----------------------|------|

| Supply Voltage        | Vcc    | 4.5  | 5    | 5.5                  | V    |

| Operating Temperature | TOP    | -40  | +25  | +85                  | °C   |

| "L" (nput Voltage     | VIL    | -0.3 |      | +0.8                 | V    |

| "H" Input Voltage     | VIH    | 2.2  |      | V <sub>CC</sub> +0.3 | ٧    |

# DC CHARACTERISTICS

| Parameter                       | Parameter Symbol Conditions |                                                                     |                                    | Min. | Тур. | Max. | Unit |

|---------------------------------|-----------------------------|---------------------------------------------------------------------|------------------------------------|------|------|------|------|

| "L" Output Voltage              | VOL                         | I <sub>OL</sub> = 4mA                                               |                                    | 1    |      | 0.4  | V    |

| "H" Output Voltage              | Voн                         | I <sub>OH</sub> = -4mA                                              |                                    | 3.7  |      |      | V    |

| Input Leak Current              | <sup>1</sup> LI             | 0≦V <sub>IN</sub> ≦V <sub>CC</sub>                                  | V <sub>CC</sub> = -4.5V<br>to 5.5V | -10  |      | 10   | μА   |

| Output Leak Current             | lLO                         | 0≦V <sub>OUT</sub> ≦V <sub>CC</sub>                                 | Ta = -40°C                         | -10  |      | 10   | μА   |

| Supply Current (Standby)        | ¹ccs                        | $V_{\text{IH}} \geq V_{\text{CC}} - 0.2V$ $V_{\text{IL}} \leq 0.2V$ | to +85°C                           |      | 0.1  | 100  | μА   |

| Average Supply Current (active) | lcc                         | f = 1 MHz                                                           |                                    |      |      | 1    | mA   |

### AC CHARACTERISTICS

$(V_{CC} = 4.5 \sim 5.5V, Ta = -40^{\circ}C + 85^{\circ}C)$

| Parameter                    | Symbol          | Min. | Тур. | Max. | Unit | Remarks     |

|------------------------------|-----------------|------|------|------|------|-------------|

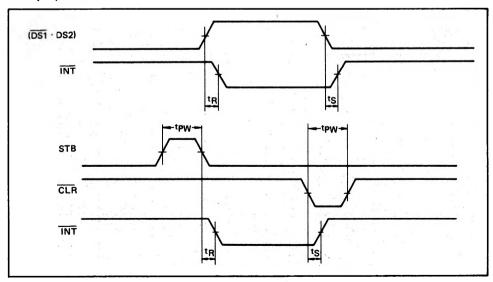

| Pulse Width                  | <sup>t</sup> PW | 30   |      |      | ns   |             |

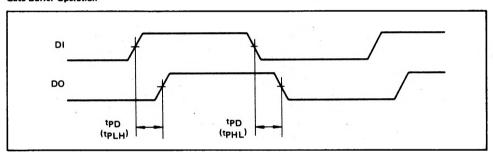

| Data to Output Delay         | tPD             |      | 20   | 45   | ns   | 1           |

| Write Enable to Output Delay | tWE             |      | 31   | 60   | ns   | - in-       |

| Data Set Up Time             | tSET            | 15   |      |      | ns   | Lood 200E   |

| Data Hold Time               | tH              | 30   |      |      | ns   | Load 30pF   |

| Clear to Output Delay        | tC              |      | 19   | 40   | ns   | 1           |

| Reset to Output Delay        | tR              |      | 21   | 45   | ns   | 1           |

| Set to Output Delay          | ts              |      | 25   | 45   | ns   | 1           |

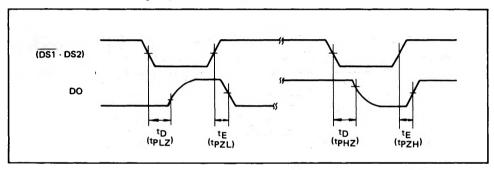

| Output Enable Time           | t <sub>E</sub>  |      | 52   | 90   | ns   | Load 20pF + |

| Output Disable Time          | tD              |      | 30   | 55   | ns   | 1 kΩ        |

Note: TYP is measured where V<sub>CC</sub> = 5 V and Ta = 25°C.

Timing is measured where VL = VH = 1.5V in both input and output.

$t_{E}$  and  $t_{D}$  are measured at  $V_{OL}$  + 0.5V or  $V_{OH}$  – 0.5V when the two are made into high impedance status.

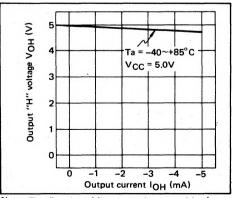

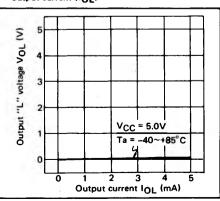

# **OUTPUT CHARACTERISTICS (DC Characteristics Reference Value)**

# (1) Output "H" voltage (V<sub>OH</sub>) vs. output current (I<sub>OH</sub>)

# (2) Output "L" voltage (VOL) vs. output current (IOL)

Note: The direction of flow in is taken as positive for output current.

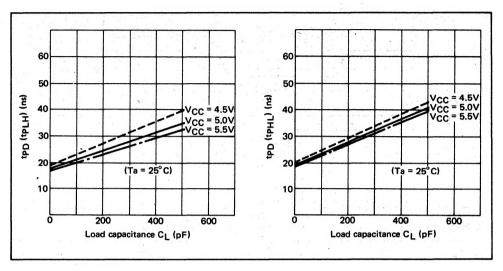

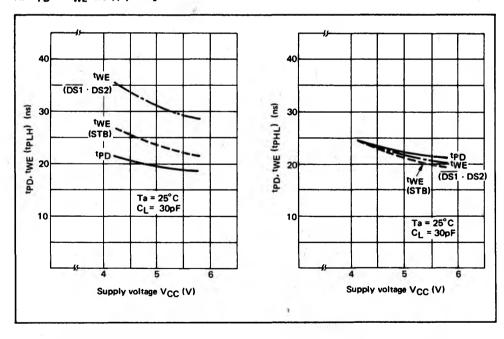

# **OUTPUT CHARACTERISTICS** (AC Characteristics Reference Value)

## (1) tpD vs. load capacitance

### (2) tpD and twe vs. supply voltage

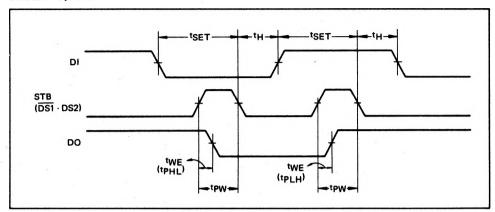

# **TIMING CHART**

# **Data Latch Operation**

## **Gate Buffer Operation**

### Interrupt Operation

# ■ I/O·MSM82C12RS/GS ■

# **Clear Operation**

# Output Buffer Enable/Disable (High Impedance Status) Operation

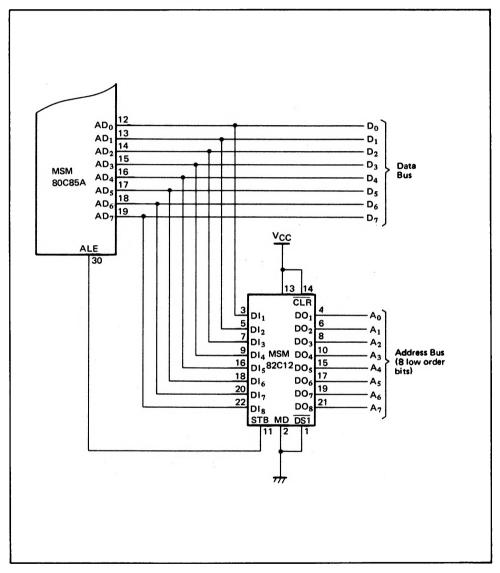

## **EXAMPLE OF APPLICATION OF MSM82C12**

### Address Latch of MSM80C85A

Used to separate the time division data bus (8 low order bits of the address bus and 8-bit data bus) into

the address bus and data bus by means of the ALE (Address Latch Enable) signal.