# **4-CHANNEL ADPCM VOICE SYNTHESIS LSI**

### **GENERAL DESCRIPTION**

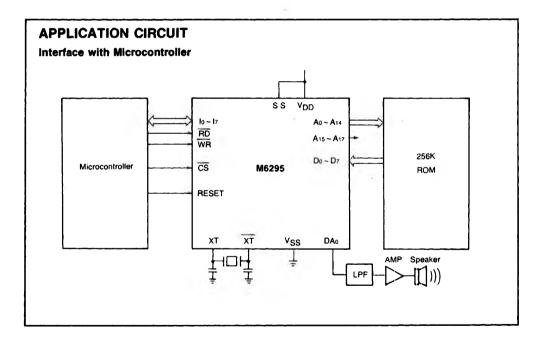

The Oki MSM6295 is a 4-channel ADPCM voice synthesis LSI which is fabricated using Oki's low power CMOS silicon gate technology.

The MSM6295 can access an external ROM, where speech or sound effect data is stored. The maximum size ROM is 256K bytes.

The MSM6295 has a 4-channel synthesis stage which allows the simultaneous playback of four different channels. So, it is quite useful to have a voice with BGM effect, instrumental sound, echo etc.

### FEATURES

- Oki straight ADPCM algorithm

- Number of bits/sample: 4

- 18 address lines for external ROM

- 8-bit control bus for mode setting

- External memory capacity 2M-bit

- Interface with common CPU and MPU

- Clock frequency: 1 MHz and 4 MHz

- Sampling frequency: 6.4 kHz and 8 kHz

(@ 1 MHz clock) 25.6 kHz and 32 kHz (@ 4 MHz clock)

- Number of words: 127 maximum

- Vocalization time: 60 sec maximum (@ 8 kHz, straight)

- Built-in DA converter: 12-bit

- DA output format: A class

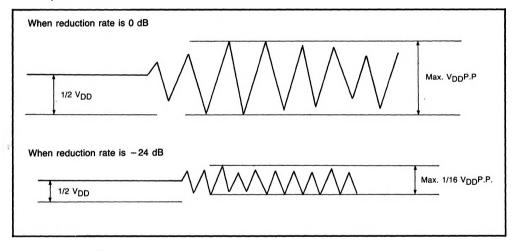

- Voice level reduction on each channel: -3 dB ~ -24 dB (8 steps) -3 dB/step

- Low power CMOS process

- 3 V or 5 V single power supply

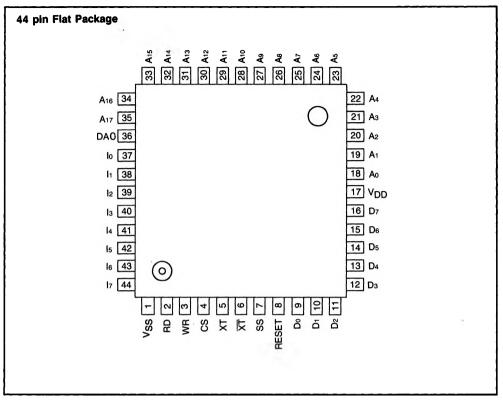

- 44 pin plastic flat package

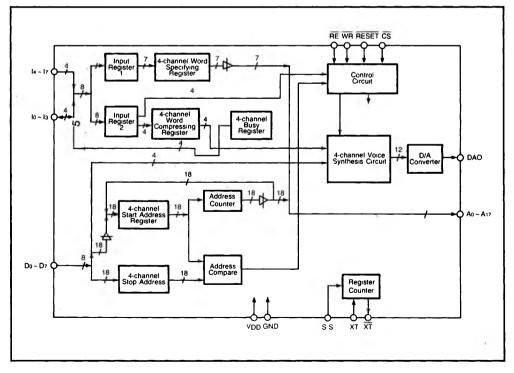

# **BLOCK DIAGRAM**

### **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| Pin Symbol                                  | Pin No.                                      | 1/0                                                  | Function                                                                                                                                                                                                                         |

|---------------------------------------------|----------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0<br> 1<br> 2<br> 3<br> 4<br> 5<br> 6<br> 7 | 37<br>38<br>39<br>40<br>41<br>42<br>43<br>44 | /O<br> /O<br> /O<br> /O<br> <br> <br> <br> <br> <br> | Data bus and condition output<br>These terminals are inputs of phrase<br>specification. Maximum number of phrases is 127.<br>Also, $10 \sim 13$ terminals are outputs of<br>operating state, busy state, for $1 \sim 4$ channel. |

| WR                                          | 3                                            | 1                                                    | Writing input<br>Write the data on the data bus of lo~l7.<br>The data is written by the setting-up of WR.                                                                                                                        |

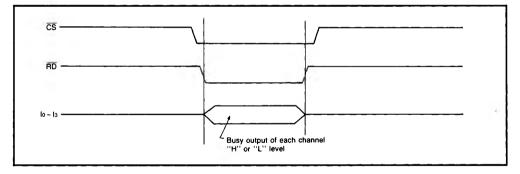

| RD                                          | 2                                            | 1                                                    | Reading out input<br>Output busy state of 1~4 channel on the<br>data bus of Io~I3. "L" level or "H" level is<br>output while RD is "L". When it becomes<br>"H", busy state is output.                                            |

.

# **PIN DESCRIPTION (continued)**

| Pin Symbol         | Pin No.            | 1/0 | Function                                                                                                                                                                                                    |  |  |

|--------------------|--------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| CS                 | 4                  | 1   | Chip selection input Input "L" level either when $\overline{WR}$ signal is input or when $\overline{RD}$ signal is input.                                                                                   |  |  |

| RESET              | 8                  | 1   | Reset input<br>Reset condition is available by inputting "L" level.<br>All functions are suspended during reset.                                                                                            |  |  |

| Ao<br><br>A17      | 18<br>(<br>)<br>35 |     | Address output<br>These terminals are to addresses the external<br>ROM in which original voice data is stored.                                                                                              |  |  |

| Do<br>(<br>)<br>D7 | 9<br>5<br>16       | 5   | Input of original voice data<br>Input the data from external ROM which stores<br>original voice data.                                                                                                       |  |  |

| SS                 | 7                  | 1   | Sampling input<br>Selecting sampling frequency.<br>When oscillation frequency is 1.18 MHz or<br>4.13 MHz, following choices are available by<br>inputting "H" level or "L" level into SS.<br> SS="H" SS="L" |  |  |

|                    |                    | = 0 | Oscillation frequency 1.18 MHz 8 kHz 6.4 kHz<br>Oscillation frequency 4.13 MHz 32 kHz 25.6 kHz                                                                                                              |  |  |

| DAo                | 36                 | 0   | Voice synthesis output<br>Voice synthesized analog signal is output from<br>this terminal.                                                                                                                  |  |  |

| хт                 | 5                  | 1   | Crystal oscillator connector terminal.                                                                                                                                                                      |  |  |

| XT                 | 6                  | 0   | Same as above                                                                                                                                                                                               |  |  |

| V <sub>DD</sub>    | 17                 | 1   | Power supply terminal                                                                                                                                                                                       |  |  |

| V <sub>SS</sub>    | 1                  | 1   | Ground                                                                                                                                                                                                      |  |  |

# FUNCTION EXPLANATION

### 1. Phrase Specification

Phrases are specified and read into the 2 byte data which is made up of  $l_0 \sim l_7$  data bus. The phrases specification data are latched when WR goes high while CS keeps low (L). Format of phrase specification input is as follows.

|        | 17 | 16       | 15                        | 14 | l3  | 12        | 11        | lo   |  |  |  |

|--------|----|----------|---------------------------|----|-----|-----------|-----------|------|--|--|--|

| 1 Byte | 1  |          | Phrase specification data |    |     |           |           |      |  |  |  |

| 2 Byte | Ch | annel sp | pecificati                | on | Rec | duction s | specifica | tion |  |  |  |

As shown in the above chart,  $1_7$  of the first 1 byte data is 1.  $1_0 \sim 1_6$  of the first 1 byte data specifies the phrase. Phrase specification data has a selection of 127 phrases which corresponds to 0000001 ~1111111. The phrase specification data is equivalent to A<sub>3</sub> ~ A<sub>9</sub> address outputs, and specify both start and stop address which are stored in the external out ROM.

### CORRESPONDENSE BETWEEN PHRASE SPECIFICATION DATA AND ROM ADDRESS

| Phrase<br>specification<br>data                                | -                                         | <b>l</b> 6       | 15               | 14               | 13               | 12               | 11               | 10               | _                | _                | _                |

|----------------------------------------------------------------|-------------------------------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|------------------|

| External ROM<br>address                                        | A17~A10                                   | Аэ               | Ав               | <b>A</b> 7       | A6               | A5               | <b>A</b> 4       | Аз               | A2               | A1               | Ao               |

| Specification<br>Not Valid<br>Phrase 1<br>Phrase 2<br>Phrase 3 | 0 ~ 0<br>0 ~ 0<br>0 ~ 0<br>0 ~ 0<br>0 ~ 0 | 0<br>0<br>0<br>0 | 0<br>0<br>0<br>0 | 0<br>0<br>0<br>0 | 0<br>0<br>0<br>0 | 0<br>0<br>0<br>0 | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 | 0<br>0<br>0<br>0 | 0<br>0<br>0<br>0 | 0<br>0<br>0<br>0 |

| Phrase 127                                                     | 0~                                        | 1                | 1                | 1                | 12               | 1                | 1                | 1                | 0                | o                | 0                |

\* Phrases cannot be specified with all 0s.

The second byte of data specifies the synthesis operation channel as well as channel specific reduction of playback synthesis sound. As to the format of channel specification, please refer to the following chart for channel specification format.

| Channel | 17 | <b>l</b> 6 | l5 | 14 |

|---------|----|------------|----|----|

| 1       | 0  | 0          | 0  | 1  |

| 2       | 0  | 0          | 1  | 0  |

| 3       | 0  | 1          | 0  | 0  |

| 4       | 1  | 0          | 0  | 0  |

#### **CHANNEL SPECIFICATION**

It is impossible to specify multiple channels at the same time. For example, it is impossible to specify channel 1 and channel 3 simultaneously.

#### **REDUCTION SPECIFICATION**

All 0 is considered as 0 dB, the analyzed sound itself. The reduction is made through 8 levels from about -3 dB to -24 dB with the steps of about -3 dB. As to the format for reduction, please refer to the following chart.

| Reduction rate | la | 12 | h | lo |

|----------------|----|----|---|----|

| 0 dB           | 0  | 0  | 0 | 0  |

| – 3.2 dB       | 0  | 0  | 0 | 1  |

| – 6.0 dB       | 0  | 0  | 1 | 0  |

| – 9.2 dB       | 0  | 0  | 1 | 1  |

| – 12.0 dB      | 0  | 1  | 0 | 0  |

| – 14.5 dB      | 0  | 1  | 0 | 1  |

| – 18.0 dB      | 0  | 1  | 1 | 0  |

| 20.5 dB        | 0  | 1  | 1 | 1  |

| –24.0 dB       | 1  | 0  | 0 | 0  |

#### **REDUCTION SPECIFICATION**

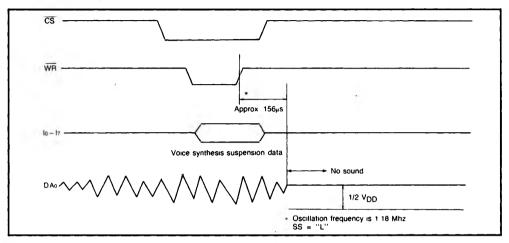

#### 2. Channel Voice Synthesis Suspension

Voice synthesis operation of any channel can be suspended. Its data consists of 1 byte of data. To suspend a channel, make  $I_7 = 0$ . And  $I_3 \sim I_6$  represent the channel which should be suspended.

| Suspended channel | 17 | <b>l</b> 6 | 15 | 14 | - <b>1</b> 3 | 12 | 11 | lo |

|-------------------|----|------------|----|----|--------------|----|----|----|

| 1                 | 0  | 0          | 0  | 0  | 1            | x  | x  | x  |

| 2                 | 0  | 0          | 0  | 1  | 0            | х  | x  | x  |

| 3                 | 0  | 0          | 1  | 0  | 0            | X  | x  | x  |

| 4                 | 0  | 1          | 0  | 0  | 0            | x  | x  | х  |

Channel suspension occurs even if multiple channels are specified. For example, if  $I_3 \sim I_6$  are all 1, channels 1  $\sim$  4 are suspended simultaneously.

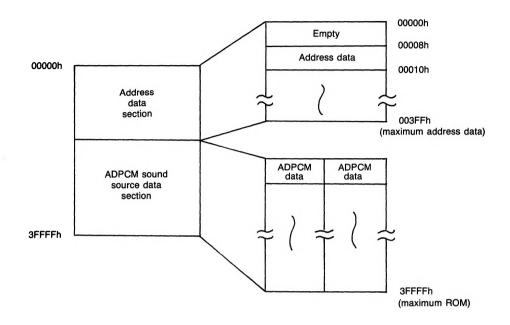

### 3.Data ROM

#### 1. ADDRESS DATA

This specifies start and stop address of ADPCM sound source data. One sound address data consists of 8 bytes. The first 3 bytes show start address while the last 3 bytes show stop address. The other 2 bytes are empty.

By specifying the first address in which the start address is stored, the sound source which should be synthesized is selected.

| Address 0 | SA1   |

|-----------|-------|

| 1         | SA2   |

| 2         | SA3   |

| 3         | EA1   |

| 4         | EA2   |

| 5         | EАз   |

| 6         | EMPTY |

| 7         | EMPTY |

|           | L     |

Start address (SA1  $\sim$  SA3) and stop addresses (EA1  $\sim$  EA3) are stored according to the chart shown below.

|          | D7         | D6          | D5          | D4          | D3          | D2          | D1          | Do  |

|----------|------------|-------------|-------------|-------------|-------------|-------------|-------------|-----|

| SA1, EA1 | 0          | 0           | 0           | 0           | 0           | 0           | <b>A</b> 17 | A16 |

| SA2, EA2 | A15        | <b>A</b> 14 | <b>A</b> 13 | <b>A</b> 12 | <b>A</b> 11 | <b>A</b> 10 | A9          | Aa  |

| SA3, EA3 | <b>A</b> 7 | A6          | A5          | A4          | Аз          | <b>A</b> 2  | A1          | Ao  |

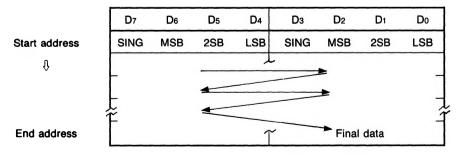

#### 2. ADPCM SOUND SOURCE DATA

ADPCM sound source data consists of 1 sample for every 4 bits. So, 1 byte stores data of 2 samples. Data arrangement proceeds from higher rank bits ( $D4 \sim D7$ ) to lower rank bits ( $D0 \sim D3$ ). The construction of sound source data should always be ended with lower rank bit. So, construct it with even number of samples.

Sound source data is compatible with the data which is analyzed by MSM5218 or MSM6258. In addition, the data which is analyzed by analyzer is usable, too.

#### 3. STRUCTURE OF SOUND SOURCE DATA ROM

Following chart shows the memory map of the sound source data ROM.

When the maximum 127 phrases are selected in address data section, the data is written up to ROM address 003FFh.

When 1 phrase is selected, address data is written from ROM address 00008h to 0000Fh, and the rest is used as the ADPCM data section.

# FUNCTIONAL DESCRIPTION

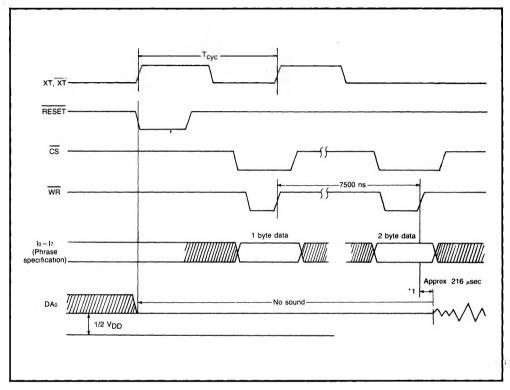

# 1. Phrase Specifying Input

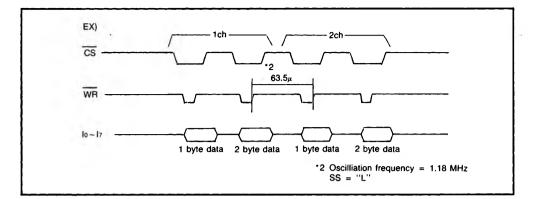

This procedure is to input phrase specifying data onto the data bus input  $I_0 \sim I_7$ . The data is latched inside when WR goes "L" to "H" while CS remains "L".

Voice synthesis operation does not start till the second byte is fully latched.

Phrase specifying input is from channel 1 to channel 4 continuously. <sup>1</sup> An interval of 15 Tcyc (max.) is needed between phrases.

.

Voice synthesis operation can be started from any channel, 1 to 4. The arrangement of each channel is of no concern.

### 2. Reduction of Synthesized Sound

This procedure is made by the second byte of phrase specifying data. Considering all 0 data of  $l_0 \sim l_3$  as 0 dB, synthesized sound is reduced between approx. -3 dB and -24 dB with the steps of -3 dB.

### 3. Channel Voice Synthesis Suspension

This is accomplished by inputting synthesis suspension data onto data bus input  $I_3 \sim I_7$ . The data is latched inside when WR goes from "L" to "H" while CS remains active (L). Since synthesis suspension data is 1 byte data, synthesis operation is suspended right after WR is input. Multiple channels can be specified. Therefore it is possible to make suspended channels  $1 \sim 4$  simultaneously.

# 4. Reading-out of Busy State

While  $\overline{CS}$  is "L" and  $\overline{RD}$  is "L", each operation state, busy state of channels  $1 \sim 4$  is output on  $10 \sim 13$ . "H" is output during the operation.

# 5. Output of Voice Synthesized Sound

MSM6295 has a 12 bit A class (voltage type) DA converter on chip. So, analog signal is available from DAo terminal.

DAo turns approx. 1/2  $V_{DD}$  (when no sound is output) right after power supply is on. This terminal outputs the amplitude of max.  $V_{DD}p.p.$

To output sound connects LPF and AMP to DA<sub>0</sub> terminal.