# **OKI** semiconductor

# MSM5056

# CMOS 4BIT SINGLE CHIP VERY LOW POWER MICROCONTROLLER WITH LCD DRIVER

#### **GENERAL DESCRIPTION**

The OKI MSM5056 is a low-power, high-performance single-chip microcontroller employing complementary metal oxide semiconductor technology. Integrated onto a single chip are a 4-bit ALU, 25K bits of mask programmable ROM, 360 bits of data RAM, crystal oscillator, voltage doubler, timer, LCD driver, input port, output port and overcharge protection circuit for connection to a solar cell.

The MSM5056 is widely used in electronic products requiring low power operation, for example, solar calculator watches and games.

#### **FEATURES**

- Low Power Consumption 3 μA Typical

- 1792 × 14 Internal ROM

- 90 × 4 Internal RAM

- 4 Input Port

- 4 Output Port

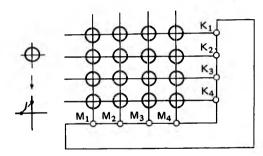

- 4 × 4 Kev Matrix Input (K₁~K₄, M₁~M₄)

- 38 LCD Driver (1/2 Duty, 1/2 Bias, 88 Segment)

- 42 Instructions

- 1.5 V Operating Voltage

(The solar cell can be connected.)

- 32,768 kHz Crystal Oscillator

- 122.1 μs Instruction Cycle

- −20 to 75°C Operating Temperature

- 68 pad die

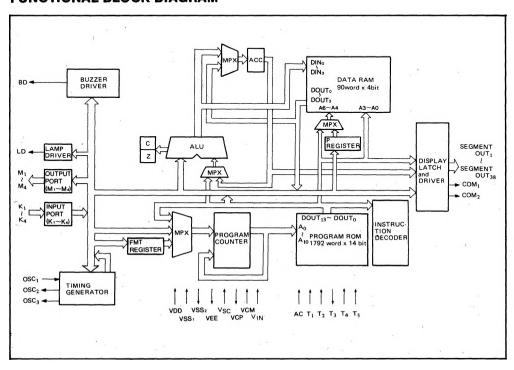

## **FUNCTIONAL BLOCK DIAGRAM**

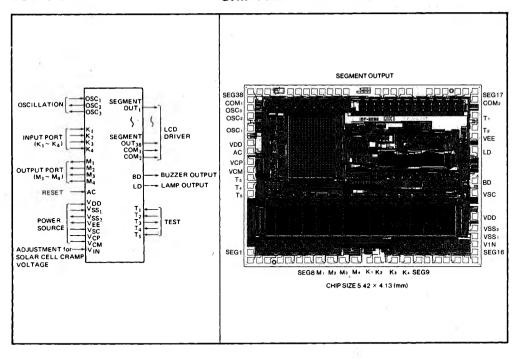

## LOGIC SYMBOL

## CHIP PAD LAYOUT

## PIN DESCRIPTION

| Designation                                                                                                                           | Function                                                                                                                                         |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| V <sub>DD</sub>                                                                                                                       | Circuit ground potential                                                                                                                         |  |  |  |  |  |  |  |

| V <sub>SS</sub> ,                                                                                                                     | Power source (-1.5 V)                                                                                                                            |  |  |  |  |  |  |  |

| V <sub>SC</sub>                                                                                                                       | Solar cell connection terminal                                                                                                                   |  |  |  |  |  |  |  |

| V <sub>SS2</sub> Power source for LCD driver (-3.0 V) This terminal is connected to V <sub>DD</sub> terminal through a 0.1 μF capacit |                                                                                                                                                  |  |  |  |  |  |  |  |

| VEE                                                                                                                                   | Power source for internal logic ( $-1.5$ to $-3.0$ V)<br>This terminal is connected to V <sub>DD</sub> terminal through a 0.1 $\mu$ F capacitor. |  |  |  |  |  |  |  |

| V <sub>CP</sub> , V <sub>CM</sub>                                                                                                     | Booster capacitor connection terminals V <sub>CP</sub> terminal is connected to V <sub>CM</sub> terminal through a 0.1 $\mu$ F capacitor.        |  |  |  |  |  |  |  |

| XT, XT                                                                                                                                | Input and output terminals of oscillator inverter, 32.768 kHz crystal is connected to these terminals.                                           |  |  |  |  |  |  |  |

| T <sub>1</sub> ~ T <sub>5</sub>                                                                                                       | Terminals to test internal logic, $T_1 \sim T_3$ and $T_5$ are pulled down to $V_{SS_1}$ . $T_4$ is output. Test pins must be normaly open.      |  |  |  |  |  |  |  |

| AC                                                                                                                                    | Terminal to clear internal logic pulled down to V <sub>SS1</sub> .  After power is turned on, the MSM5056 must be reset by this terminal.        |  |  |  |  |  |  |  |

| BD                                                                                                                                    | Buzzer output                                                                                                                                    |  |  |  |  |  |  |  |

| LD                                                                                                                                    | Lamp output                                                                                                                                      |  |  |  |  |  |  |  |

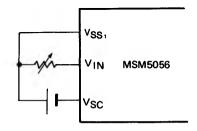

| VIN                                                                                                                                   | Adjustment for solar cell cramp voltage This terminal is connected to VSS , terminal through 50 $\sim$ 200 k $\Omega$ resistor.                  |  |  |  |  |  |  |  |

#### **FUNCTIONAL DESCRIPTION**

A block diagram of the MSM5056 is given on page 111. Each block of logic will be briefly discussed. For more information, please refer to the MSM5056 user's manual

#### Program ROM

The MSM5056 will address up to 1.75 K words of internal mask programmable ROM. Each word consists of 14 bits and all instructions are one word. The instructions are routed to a programmed logic array which generates the signals necessary for control of logic.

#### Data RAM

Data is organized in 4 bit nibbles. Internal data RAM consists of 90 nibbles.

The RAM is addressed by page address and column address. Normally page address is specified with the page register, but direct addressing is available at Page 0.

Column address is directly addressed by the operands of various instructions.

#### ALL

The ALU performs 4-bit parallel operation of RAM and AC contents, or RAM contents and an immediate digit. It sets or resets the flags (Z, C) depending on the condition.

#### Program Counter (PC)

The program counter is an 11-bit wide counter and specifies the address of the program ROM.

The PC is incremented by one at every execution of an instruction, and then specifies the next instruction to be executed. However, the contents of the PC are rewritten by the execution of a Jump or Branch instruction.

There is no boundary in the ROM, so a Jump or Branch instruction can be put anywhere in the ROM.

#### Input/Output Port

#### Input Port (K1 ~ K2)

The input port (K1  $\sim$  K4) is a 4-bit parallel input port. Each pin of the port is pulled down to VSS1 by an internal resistor, and the status of the port can be fetched by an input instruction.

#### Output Port (M1 ~ M4)

The output port (M1  $\sim$  M4) is a 4-bit parallel output port. This port consists of data latches and buffers. The contents of data latches are rewritten by an output instruction. A key matrix is used in combination with K1 to K4.

#### **Display Function**

The MSM5056 is provided with a segment output terminal which can directly drive a 1/2 bias, 1/2 duty LCD and common drive output terminals. COM1 and COM2. The segment drive circuit consists of the display data latch, multiplexer and driver. If the data is sent to the display data latch with the display instruction, the LCD drive waveform is output to the segment drive output terminal.

#### Time Base

Time base of the CPU is provided by connecting a 32.768 kHz crystal to the OSC1 and OSC3 pin. One machine cycle is 122.1 µs.

A hardware divider up to 1 Hz is provided enabling programs to implement and a clock function by counting signals between 16 and 1 Hz

#### Solar Cell Overcharge Protection Circuit

When a solar cell is connected to prolong the usefull life of the battery, a resistor is inserted between the V<sub>IN</sub> pin and V<sub>SS1</sub> to adjust the overcharge protection voltage.

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter           | Symbol                             | Conditions | Limits                         | Unit |

|---------------------|------------------------------------|------------|--------------------------------|------|

| Supply Voltage 1    | V <sub>DD</sub> - V <sub>SS1</sub> | Ta = 25°C  | , -0.3 to +3.0                 | V    |

| Supply Voltage 2    | V <sub>DD</sub> - V <sub>SC</sub>  | Ta = 25°C  | -0.3 to +3.5                   | V    |

| Supply Voltage 3    | V <sub>DD</sub> - V <sub>SS2</sub> | Ta = 25°C  | -0.3 to +6.0                   | V    |

| Supply Voltage 4    | V <sub>DD</sub> – V <sub>EE</sub>  | Ta = 25°C  | -0.3 to +6.0                   | V    |

| Input Voltage       | VIN,                               | Ta = 25°C  | V <sub>SS</sub> , -0.3 to +0.3 | ٧    |

| Storage Temperature | Tstg                               |            | -55 to 125                     | °C   |

## **OPERATING CONDITIONS**

| Parameter             | Symbol                             | Limits       | Unit |

|-----------------------|------------------------------------|--------------|------|

| Operating Voltage     | V <sub>DD</sub> -V <sub>SS</sub> , | 1.25 to 1.65 | V    |

| Operating Temperature | Topr                               | -20 to 75    | °C   |

## DC CHARACTERISTICS

$(V_{DD} = 0V, V_{SS_1}, V_{EE} = -1.55V, V_{SS_2} = -3.0V, C_I = 30k\Omega, C_G = 30pF, Ta = 25^{\circ}C)$

| Parameter                     | Sumbal            | Condit                                               |                         | Limits | Unit      |      |      |  |  |

|-------------------------------|-------------------|------------------------------------------------------|-------------------------|--------|-----------|------|------|--|--|

| Parameter                     | Symbol            | ion                                                  | Min.                    | Тур.   | Мах.      | Onit |      |  |  |

| Operating voltage 1           | -V <sub>SS1</sub> | V <sub>SS</sub> , terminal                           |                         | 1.25   | 1.55      | 2.0  | ٧    |  |  |

| Operating voltage 2           | -V <sub>SC</sub>  | V <sub>SC</sub> terminal                             |                         | 0      | 2.0       | 3.0  | ٧    |  |  |

| Power supply current          | IDD               | VSS, terminal                                        |                         | -      | 3.0       | _    | μΑ   |  |  |

| Oscillation start voltage     | -vosc             | Within 10 seconds<br>VSS1 terminal                   |                         | 1.45   | - 8       | -    | ٧    |  |  |

|                               | lOH₁              | V <sub>OH₁</sub> = -0.2V                             |                         | -4     | _         | _    | μΑ   |  |  |

| Output current 1<br>COM       | IOM <sub>1</sub>  | $V_{OM_1} = V_{SS_1} \pm 0.2$                        | V                       | 4/-4   | _         | _    |      |  |  |

| 00111                         | I <sub>OL</sub> 1 | $V_{OL_1} = -2.8V$                                   |                         | 4      | _         |      |      |  |  |

| Output current 2              | IOH <sub>2</sub>  | V <sub>OH₂</sub> = -0.2V                             |                         | -0.4   | _         | _    | 1    |  |  |

| SEGMENT                       | IOL2              | $V_{OL_2} = -2.8V$                                   |                         | 0.4    |           | _    | - μΑ |  |  |

| Output current 3              | lOH₃              | V <sub>SS</sub> , V <sub>EE</sub> -1.25V             | V <sub>OH3</sub> −0.4 V | -100   | -         | -    |      |  |  |

| M₁ ~ M₄                       | I <sub>OL3</sub>  | V <sub>SS2</sub> -2.3V                               | V <sub>OL3</sub> -0.85V | 3      |           | 8    | μΑ   |  |  |

| Output current 4              | IOH₄              | $V_{OH_4} = -0.4V$                                   |                         | -50    | -100 -200 |      | ij,  |  |  |

| BD                            | lOL₄              | $V_{OL_4} = -1.15V$                                  | 0.1                     | 3_     | 10        | 30   | μΑ   |  |  |

| Input current                 | ήн,               | VIN = -0V                                            |                         | 5      | 10        | 15   |      |  |  |

| K1~K4                         | I <sub>IL</sub> , | $V_{IN} = -1.55V$                                    |                         | T -    | -         | -0.2 | μΑ   |  |  |

| Oscillator built-in capacitor | CD                |                                                      |                         | _      | 20        | _    | pF   |  |  |

| Solar battery cramp resistor  | R <sub>IN</sub>   | V <sub>SS1</sub> = −1.8V<br>V <sub>IN</sub> terminal |                         | 50     | _         | 200  | kΩ   |  |  |

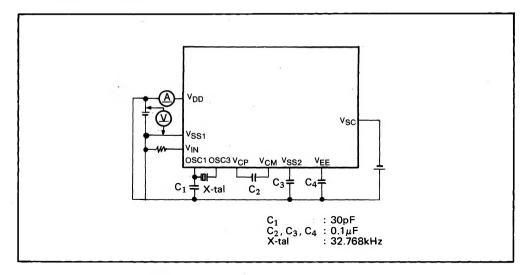

## **MEASURING CIRCUIT**

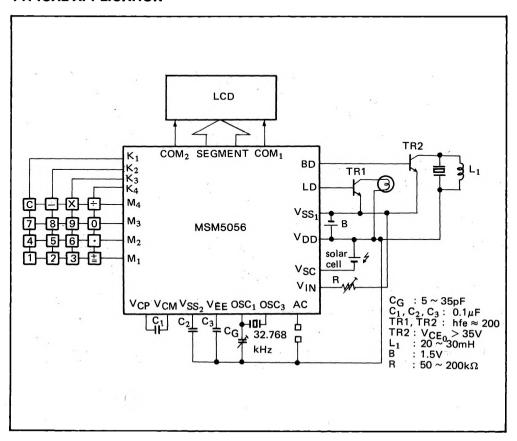

## TYPICAL APPLICATION

# **DESCRIPTION OF INSTRUCTIONS**

|                      |             |    |    |    |    | Ins | stru | ctic | on C | Cod      | е |   |     |     |                   | Operation                                   |  |  |  |

|----------------------|-------------|----|----|----|----|-----|------|------|------|----------|---|---|-----|-----|-------------------|---------------------------------------------|--|--|--|

|                      | Mnemonic    | 13 | 12 | 11 | 10 | 9   | 8    | 7    | 6    | 5        | 4 | 3 | 2   | 1   | 0                 | Орегация                                    |  |  |  |

|                      | ADD ACC, AP | 0  | 0  | 0  | 0  | 0   | Р    | 0    | 1    | 0        | 0 |   | Α   |     |                   | AP ← (AP) + (ACC)                           |  |  |  |

|                      | ADD #D, AP  | 0  | 1  | 1  | 0  | 0   | Р    |      |      | <u> </u> |   |   | Α   |     |                   | AP ← (AP) — D                               |  |  |  |

|                      | ADC AP      | 0  | 0  | 0  | 0  | 0   | Р    | 0    | 1    | 0        | 1 |   | A   |     |                   | AP ← Decimal adjust<br>{(AP) + (ACC) + (C)} |  |  |  |

| 5                    | SUB ACC, AP | 0  | 0  | ò  | 0  | 1   | P    | 0    | 1    | 0        | 0 |   | Α   |     |                   | AP - (AP) - (ACC)                           |  |  |  |

| erat                 | SUB #D, AP  | 0  | /1 | 1  | 0  | 1   | Р    |      | [    | )        |   |   | Ą   |     |                   | AP ← (AP) — D                               |  |  |  |

| Arithmetic operation | SBC AP      | 0  | 0  | 0  | 0  | 1   | Р    | 0    | 1    | 0        | 1 |   | A   |     |                   | AP ← Decimal adjust<br>{(AP) – (ACC) – (C)} |  |  |  |

| m<br>m               | CMP ACC, AP | 0  | 0  | 0  | 0  | 1   | P    | 1    | 1    | 1        | 0 |   | Α   |     |                   | (AP) - (ACC)                                |  |  |  |

| Arit                 | CMP #D, AP  | 0  | 1- | 0  | 1  | 1   | Р    |      |      | )        |   |   | Α   |     |                   | (AP) — D                                    |  |  |  |

|                      | INC AP      | 0  | 1  | 1  | 0  | 0   | Р    | 0    | 0    | 0        | 1 |   | Α   |     |                   | AP ← (AP) + 1                               |  |  |  |

|                      | DEC AP      | 0  | 1  | 1  | 0  | 1   | Р    | 0    | 0    | 0        | 1 |   | A   |     |                   | A ← (AP) — 1                                |  |  |  |

|                      | XOR ACC, AP | 0  | 0  | 0  | 0  | 0   | Р    | 0    | 1    | 1        | 1 |   | Α   |     |                   | AP ← (AP) ★ (ACC)                           |  |  |  |

|                      | XOR #D, AP  | 0  | 1  | 1  | 1  | 1   | Р    |      |      | )        |   |   | Α   | - 3 |                   | AP ← (AP) V D                               |  |  |  |

|                      | BIT ACC, AP | 0  | 0  | 0  | 0  | 0   | Р    | 1    | 1    | 1        | 0 | Α |     |     | (AP) V (ACC)      |                                             |  |  |  |

| Ξ                    | BIT #D, AP  | 0  | 1  | 0  | 1  | 0   | Р    |      | (    | )        |   |   | A   |     |                   | (AP) V D                                    |  |  |  |

| ratio                | BIS ACC, AP | 0  | 0  | 0  | 0  | 0   | Р    | 0    | 1    | 1        | 0 |   | Α   |     | AP ← (AP) V (ACC) |                                             |  |  |  |

| Bit operation        | BIS #D, AP  | 0  | 1  | 0  | 0  | 0   | P    |      |      | )        |   |   | Α   |     |                   | AP ← (AP) V D                               |  |  |  |

| Bit                  | BIC ACC, AP | 0  | 0  | 0  | 0  | 1   | P    | 0    | 1    | 1        | 0 |   | A   |     | AP ← (AP) Λ(ACC)  |                                             |  |  |  |

|                      | BIC #D, AP  | 0  | 1  | 0  | 0  | 1   | P    |      |      | )        |   |   | A   |     |                   | $AP \leftarrow (AP) \wedge \overline{D}$    |  |  |  |

| ¥                    | ASR AP      | 0  | 0  | 0  | 0  | 0   | Р    | 0    | 0    | 1        | 1 |   | Α   |     |                   | (C) 0 → (AP)-                               |  |  |  |

| Shift                | ASL AP      | 0  | 0  | 0  | 0  | 1   | P    | 0    | 0    | 1        | 1 |   | A   |     |                   | (C) ← (AP) ← 0                              |  |  |  |

| -                    | CLZ         | 0  | 0  | 0  | 0  | 0   | 0    | 1    | 0    | 1        | 0 | 0 | 0   | 0   | 0                 | Z ← 0                                       |  |  |  |

| <u>6</u>             | CLC         | 0  | 0  | 0  | 0  | 0   | 0    | 1    | 0    | 0        | 1 | 0 | 0   | 0   | 0                 | <b>c</b> ← 0                                |  |  |  |

| Flag operation       | CLA         | 0  | 0  | 0  | 0  | 0   | 0    | 1    | 0    | 1        | 1 | 0 | 0   | 0   | 0                 | z 0, c 0                                    |  |  |  |

| got                  | SEZ         | 0  | 0  | 0  | 0  | 1   | 0    | 1    | 0    | 1        | 0 | 0 | 0   | 0   | 0                 | Z ← 1                                       |  |  |  |

| Flag                 | SEC         | 0  | 0  | 0  | 0  | 1   | 0    | 1    | 0    | 0        | 1 | 0 | 0   | 0   | 0                 | C ← 1                                       |  |  |  |

|                      | SEA         | 0  | 0  | 0  | 0  | 1   | 0    | 1    | 0    | 1        | 1 | 0 | 0   | ō   | 0                 | Z ← 1, C ← 1                                |  |  |  |

|                      | MOV ACC, AP | 1  | 1  | 1  | 1  | 0   | P    | 0    | 0    | 0        | 0 | Γ | Α   |     |                   | AP - (ACC)                                  |  |  |  |

|                      | MOV ACC, AX | 1  | 1  | 1  | 1  | 0   | 0    | 0    |      | Х        |   |   | Δ   |     |                   | AX ← (ACC)                                  |  |  |  |

| sfer                 | MOV #D, AP  | 0  | 1  | 1  | 1  | 0   | Р    |      | -    | D        |   |   | A   | Ţ.  |                   | AP ← D                                      |  |  |  |

| tran                 | MOV AP, ACC | 1  | 1  | 1  | 1  | 1   | P    | 0    | 0    | 0        | 0 |   | A   | `   |                   | ACC ← (AP)                                  |  |  |  |

| Data transfe         | MOV AX, ACC | .1 | 1  | 1  | 1  | 1   | 0    | 0    |      | X        |   | Γ | - 4 | `   |                   | ACC ← (AX)                                  |  |  |  |

| ۵                    | CHG AP      | 1  | 1  | 1  | 0  | 0   | P    | 0    | 0    | 0        | 0 | Γ | A   | `   |                   | (ACC) ← (AP)                                |  |  |  |

|                      | CHG AX      | 1  | 1  | 1  | 0  | 0   | 0    | 0    |      | Х        |   | Γ | A   | · · |                   | (ACC) (AX)                                  |  |  |  |

# DESCRIPTION OF INSTRUCTIONS (CONT.)

|                  | Mnemonic         | ructi | ion | Cod | de   |                |                |    |                | Operation |                |                       |                |                |                       |                                           |  |  |  |  |

|------------------|------------------|-------|-----|-----|------|----------------|----------------|----|----------------|-----------|----------------|-----------------------|----------------|----------------|-----------------------|-------------------------------------------|--|--|--|--|

|                  | Minemonic        | 13    | 12  | 11  | 10   | 9              | 8              | 7  | 6              | 5         | 4              | 3                     | 2              | 1              | 0                     | Operation                                 |  |  |  |  |

|                  | JMP adrs         | 1     | 0   | 0   | a 10 | a <sub>9</sub> | а <sub>в</sub> | a, | a <sub>6</sub> | a 5       | a4             | <b>a</b> <sub>3</sub> | a <sub>2</sub> | a 1            | <b>a</b> <sub>0</sub> | PC ← adrs                                 |  |  |  |  |

| Ī                | JMP @AP          | 0     | 0   | 0   | 0    | 0              | Р              | 1  | 1              | 0         | 1              |                       | A              |                |                       | PC ← (PC) + (AP) + 1                      |  |  |  |  |

|                  | JMPIO @AP        | 0     | 0   | 0   | 0    | 1              | Р              | 1  | 1              | 0         | 1              |                       | A              |                |                       | PC ← (PC) + {(AP)Λ7H } + +1               |  |  |  |  |

|                  | BEQ +n<br>BZE +n | 0     | 0   | 0   | 1    | 1              | 0              | 0  | 1              | 0         | n <sub>4</sub> | n <sub>3</sub>        | n <sub>2</sub> | n 1            | n <sub>o</sub>        | $PC \leftarrow (PC) + n + 1$ , if $Z = 1$ |  |  |  |  |

| Jump             | BNE +n<br>BNZ +n | 0     | 0   | 0   | 1    | 1              | 0              | 1  | 1              | 0         | n <sub>4</sub> | n <sub>3</sub>        | n <sub>2</sub> | n 1            | n <sub>o</sub>        | PC ← (PC) +n+1, if Z=0                    |  |  |  |  |

| JL               | BCS +n<br>BLT +n | 0     | 0   | 0   | 1    | 1              | 0              | 0  | 0              | 1         | n <sub>4</sub> | n <sub>3</sub>        | n <sub>2</sub> | n <sub>1</sub> | n <sub>o</sub>        | PC ← (PC) + n + 1, if C = 1               |  |  |  |  |

| 10               | BCC +n<br>BGE +n | 0     | 0   | 0   | 1    | 1              | 0              | 1  | 0              | 1         | n <sub>4</sub> | n <sub>3</sub>        | n <sub>2</sub> | n 1            | n <sub>o</sub>        | PC ← (PC) +n + 1, if C = 0                |  |  |  |  |

|                  | BGT +n           | 0     | 0   | 0   | 1    | 1              | 0              | 1  | 1              | 1         | n <sub>4</sub> | n <sub>3</sub>        | n <sub>2</sub> | n <sub>1</sub> | n <sub>o</sub>        | PC ← (PC) +n + 1, if Z = 0<br>and C = 0   |  |  |  |  |

|                  | BLE +n           | 0     | 0   | 0   | 1    | 1              | 0              | 0  | 1              | 1         | n <sub>4</sub> | n <sub>3</sub>        | n <sub>2</sub> | n 1            | n <sub>o</sub>        | PC ← (PC) + n + 1, if Z = 1<br>or C = 1   |  |  |  |  |

| \ ±              | INP Port, AP     | 1     | 1   | 0   | 1    | 0              | Р              |    | Po             | ort       |                |                       | -              | `              |                       | AP ← (Port)                               |  |  |  |  |

| Input/<br>Output | OUT AP, Port     | 1     | 1   | 0   | 1    | 1              | Р              |    | Po             | ort       |                |                       | -              | \              |                       | Port ← (AP)                               |  |  |  |  |

|                  | OUT #D, Port     | 0     | 0   | 0   | 1    | 0              | 0              |    | P              | ort       |                |                       | 0              |                |                       | Port ← D                                  |  |  |  |  |

| olay             | DSP digit, AP    | 0     | 0   | 1   | 0    | 0              | Р              |    | di             | git       |                |                       | -              | `              |                       | digit ← (AP), (ACC)                       |  |  |  |  |

| CPU Display      | DSPF digit, AP   | 0     | 0   | 1   | 1    | 0              | Р              |    | di             | git       |                |                       | -              | \              |                       | digit ← (AP) via table                    |  |  |  |  |

| To               | HALT             | 0     | 0   | 0   | 1    | 0              | 0              | 0  | 0              | 0         | 0              | 0                     | 0              | 0              | 0                     | Halt CPU                                  |  |  |  |  |

| <u> </u>         | NOP              | 0     | 0   | 0   | 0    | 0              | 0              | 0  | 0              | 0         | 0              | 0                     | 0              | 0              | 0                     | No Operation                              |  |  |  |  |