# MM54C/MM74C Voltage Translation/Buffering

National Semiconductor Memory Brief 18 John Jorgensen Thomas P. Redfern

## INTRODUCTION

A new series of MM54C/MM74C buffers has been designed to interface systems operating at different voltage levels. In addition to performing voltage translation, the MM54C901/MM74C901 through MM54C904/MM74C904 hex buffers can drive two standard TTL loads at  $V_{CC}$  = 5V. This is an increase of ten times over the two LpTTL loads that the standard MM54C/MM74C gate can drive. These new devices greatly increase the flexibility of the MM54C/MM74C family when interfacing to other logic systems.

### PMOS TO CMOS INTERFACE

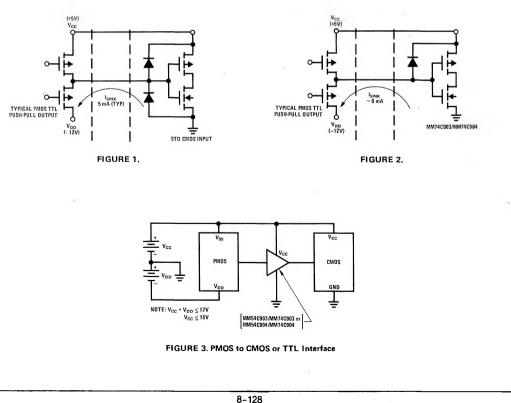

Since most PMOS outputs normally can pull more negative than ground, the conventional CMOS input diode clamp from input to ground poses problems. The least of these is increased power consumption. Even though the output would be clamped at one diode drop (-0.6V), all the current that flows comes from the PMOS negative supply. For TTL compatible PMOS this is -12V. A PMOS output designed to drive one TTL load will typically sink

5 mA. The total power per TTL output is then 5 mA x 12V = 60 mW. The second problem is more serious. Currents of 5 mA or greater from a CMOS input clamp diode can cause four-layer diode action on the CMOS device. This, at best, will totally disrupt normal circuit operation and, at worst, will cause catastrophic failure.

To overcome this problem the MM74C903 and MM74C904 have been designed with a clamp diode from inputs to V<sub>CC</sub> only. This single diode provides adequate static discharge protection and, at the same time, allows voltages of up to -17V on any input. Since there is essentially no current without the diode, both the high power dissipation and latch up problems are eliminated.

To demonstrate the above characteristics, Figures 1, 2, and 3 show typical TTL compatible PMOS circuits driving standard CMOS with two clamp diodes, TTL compatible PMOS driving MM74C903/MM74C904, and the TTL compatible PMOS to CMOS system interface, respectively.

### CMOS TO CMOS OR TTL INTERFACE

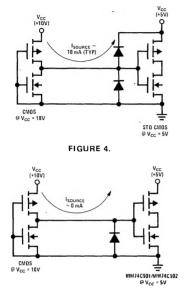

When a CMOS system which is operating at  $V_{CC} = 10V$  must provide signals to a CMOS system whose  $V_{CC} = 5V$ , a problem similar to that found in PMOS-to-CMOS interface occurs. That is, current would flow through the upper input diode of the device operating at the lower  $V_{CC}$ . This current could be in excess of 10 mA on a typical 74C device, as shown in *Figure 4*. Again, this will cause increased power as well as possible four layer diode action.

#### FIGURE 5.

Using the MM74C901 or MM74C902 will eliminate this problem. This occurs simply because these parts are designed with the upper diode removed, as shown in

Figure 5. With this diode removed the current being sourced goes from about 10 mA to the leakage current of the reverse biased input diode.

Since the MM74C901 and MM74C902 are capable of driving two standard TTL loads with only normal input levels, the output can be used to directly drive TTL. With the example shown, the inputs of the MM74C901 are in excess of 5V. Therefore, they can drive more than two TTL loads. In this case the device would drive four loads with  $V_{IN} = 10V$ . If the MM74C902 were used, the output drive would not increase with increased input voltage. This is because the gate of the output n-channel device is always being driven by an internal inverter whose output equals that of  $V_{CC}$  of the device.

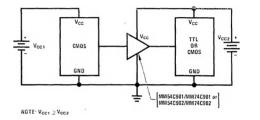

The example used was for systems of  $V_{CC} = 10V$  on one system and  $V_{CC} = 5V$  on the second, but the MM74C901 and MM74C902 are capable of using any combination of supplies up to 15V and greater than 3V, as long as  $V_{CC1}$  is greater than or equal to  $V_{CC2}$  and grounds are common. *Figure 6* diagrams this configuration.

FIGURE 6. CMOS to TTL or CMOS at a Lower VCC

The inputs on these devices are adequately protected with the single diode, but, as with all MOS devices, normal care in handling should be observed.