# National Semiconductor

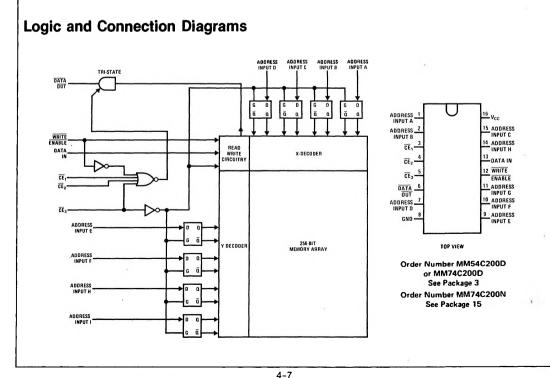

## MM54C200/MM74C200 256-Bit TRI-STATE® Random Access Read/Write Memory

### **General Description**

The MM54C200/MM74C200 is a 256-bit random access read/write memory. Inputs consist of eight address lines, and three chip enables. The eight binary address inputs are decoded internally to select each of the 256 locations. The internal address register, latches, and address information are on the positive to negative edge of  $\overline{CE}_3$ . The TRI-STATE® data output line, working in conjunction with  $\overline{CE}_1$  or  $\overline{CE}_2$  inputs, provides for easy memory expansion.

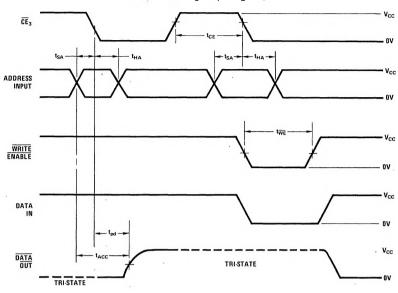

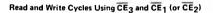

Address Operation: Address inputs must be stable  $t_{SA}$  prior to the positive to negative transition of  $\overline{CE_3}$ . It is therefore unnecessary to hold address information stable for more than  $t_{HA}$  after the memory is enabled (positive to negative transition).

Note: The timing is different from the DM74200 in that a positive to negative transition of the  $\overline{CE}_3$  must occur for the memory to be selected.

**Read Operation:** The data is read out by selecting the proper address and bringing  $\overline{CE}_3$  low and  $\overline{WE}$  high.

TRI-STATE is a registered trademark of National Semiconductor Corp.

Holding either  $\overline{CE}_1$ ,  $\overline{CE}_2$ , or  $\overline{CE}_3$  at a high level forces the output into TRI-STATE. When used in bus-organized systems,  $\overline{CE}_1$ , or  $\overline{CE}_2$ , a TRI-STATE control provides for fast access times by not totally disabling the chip.

Write Operation: Data is written into the memory with  $\overline{CE}_3$  low and  $\overline{WE}$  low. The state of  $\overline{CE}_1$  or  $\overline{CE}_2$  has no effect on the write cycle. The output assumes TRI-STATE with  $\overline{WE}$  low.

#### Features

- Wide supply voltage range

- Guaranteed noise margin

- High noise immunity

- TTL compatibility

- Low power

- Internal address register

3.0 V to 15 V 1.0 V 0.45 V<sub>CC</sub> (typ.) fan out of 1 driving standard TTL 500 nW (typ.)

## Absolute Maximum Ratings (Note 1)

| Voltage at Any Pin                       | -0.3 V to V <sub>CC</sub> + 0.3 V |

|------------------------------------------|-----------------------------------|

| Operating Temperature Range              |                                   |

| MM54C200                                 | -55°C to +125°C                   |

| MM74C200                                 | -40°C to +85°C                    |

| Storage Temperature Range                | -65°C to +150°C                   |

| Package Dissipation                      | 500 mW                            |

| Operating V <sub>CC</sub> Range          | 3.0 V to 15 V                     |

| Absolute Maximum V <sub>CC</sub>         | 18 V                              |

| Lead Temperature (Soldering, 10 seconds) | 300°C                             |

# DC Electrical Characteristics Min./max. limits apply across temperature range, unless otherwise noted.

|                     | Parameter                            | Conditions                                                                                              | Min.                                           | Тур.     | Max.       | Units    |

|---------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------|----------|------------|----------|

|                     | CMOS to CMOS                         | · · · · · · · · · · · · · · · · · · ·                                                                   |                                                |          |            |          |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage            | $V_{CC} = 5.0 V$ $V_{CC} = 10 V$                                                                        | 3.5<br>8.0                                     |          |            | v<br>v   |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage            | $\begin{array}{l} V_{CC}=5.0V\\ V_{CC}=10V \end{array}$                                                 |                                                |          | 1.5<br>2.0 | v<br>v   |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage           | $V_{CC} = 5.0 \text{ V}, \ I_O = -10 \mu \text{A}$<br>$V_{CC} = 10 \text{ V}, \ I_O = -10 \mu \text{A}$ | 4.5<br>9.0                                     |          |            | v<br>v   |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage           | $V_{CC} = 5.0 \text{ V}, I_{O} = +10 \mu \text{A}$<br>$V_{CC} = 10 \text{ V}, I_{O} = +10 \mu \text{A}$ |                                                |          | 0.5<br>1.0 | v<br>v   |

| 1 <sub>IN(1)</sub>  | Logical "1" Input Current            | $V_{CC} = 15 V, V_{IN} = 15 V$                                                                          |                                                | 0.005    | 1.0        | μA       |

| l <sub>IN(0)</sub>  | Logical "0" Input Current            | $V_{CC} = 15 V, V_{IN} = 0 V$                                                                           | -1.0                                           | -0.005   |            | μΑ       |

| lcc                 | Supply Current                       | $V_{CC} = 15 V$                                                                                         |                                                | 0.10     | 600        | μΑ       |

|                     | CMOS/TTL Interface                   |                                                                                                         |                                                |          |            |          |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage            | $\begin{array}{ccc} 54C & V_{CC} = 4.5  V \\ 74C & V_{CC} = 4.75  V \end{array}$                        | V <sub>CC</sub> – 1.5<br>V <sub>CC</sub> – 1.5 |          |            | V<br>V   |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage            | $\begin{array}{ll} 54C & V_{CC} = 4.5  V \\ 74C & V_{CC} = 4.75  V \end{array}$                         |                                                |          | 0.8<br>0.8 | v<br>v   |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage           | 54C $V_{CC} = 4.5 V$ , $I_O = -1.6 mA$<br>74C $V_{CC} = 4.75$ , $I_O = -1.6 mA$                         | 2.4<br>2.4                                     |          |            | v<br>v   |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage           | 54C $V_{CC} = 4.5 V$ , $I_O = 1.6 mA$<br>74C $V_{CC} = 4.75$ , $I_O = 1.6 mA$                           |                                                |          | 0.4        | v        |

|                     | Output Drive (See 54C/74C Fai        | mily Characteristics Data Sheet) (Sh                                                                    | ort Circuit                                    | Current) |            |          |

| ISOURCE             | Output Source Current<br>(P-Channel) | $V_{CC} = 5.0 V, V_{OUT} = 0 V$<br>$T_A = 25^{\circ}C$                                                  | -4.0<br>-1.8                                   | -6.0     |            | mA<br>mA |

| SOURCE              | Output Source Current<br>(P-Channel) | $V_{CC} = 10 V, V_{OUT} = 0 V$<br>$T_A = 25^{\circ}C$                                                   | −16.0<br>−1.5                                  | -25      |            | mA<br>mA |

| I <sub>SINK</sub>   | Output Sink Current<br>(N-Channel)   | $V_{CC} = 5.0 \text{ V}, V_{OUT} = V_{CC}$<br>$T_A = 25^{\circ}\text{C}$                                | 5.0                                            | 8.0      |            | mA       |

| I <sub>SINK</sub>   | Output Sink Current<br>(N-Channel)   | $V_{CC} = 10 V$ , $V_{OUT} = V_{CC}$<br>$T_A = °C$                                                      | 20                                             | 30       |            | mA       |

|                   | Parameter                                                     | Conditions                          | Min.                                                                                                            | Тур.       | Max.       | Units    |

|-------------------|---------------------------------------------------------------|-------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------|------------|----------|

| t <sub>ACC</sub>  | Access Time from Address                                      | $V_{CC} = 5.0V$ $V_{CC} = 10V$      |                                                                                                                 | 450<br>200 | 900<br>400 | ns<br>ns |

| t <sub>pd</sub>   | Propagation Delay from $\overline{CE}_3$                      | $V_{CC} = 5.0 V$ $V_{CC} = 10 V$    |                                                                                                                 | 360<br>120 | 700<br>300 | ns<br>ns |

| t <sub>pCE1</sub> | Propagation Delay from $\overline{CE}_1$ or $\overline{CE}_2$ | $V_{CC} = 5.0 V$<br>$V_{CC} = 10 V$ |                                                                                                                 | 250<br>85  | 700<br>200 | ns<br>ns |

| t <sub>SA</sub>   | Address Setup Time                                            | $V_{CC} = 5.0 V$<br>$V_{CC} = 10 V$ | 200<br>100                                                                                                      | 80<br>30   |            | ns<br>ns |

| t <sub>HA</sub>   | Address Hold Time                                             | $V_{CC} = 5.0 V$<br>$V_{CC} = 10 V$ | 50<br>25                                                                                                        | 15<br>5.0  |            | ns<br>ns |

| twe               | Write Enable Pulse Width                                      | $V_{CC} = 5.0 V$<br>$V_{CC} = 10 V$ | 300<br>150                                                                                                      | 160<br>70  |            | ns<br>ns |

| t <sub>CE</sub>   | $\overline{CE}_3$ Pulse Widths                                | $V_{CC} = 5.0 V$<br>$V_{CC} = 10 V$ | 400<br>160                                                                                                      | 200<br>80  |            | ns<br>ns |

| CIN               | Input Capacity                                                | Any Input (Note 2)                  | 1811 - 1811 - 1811 - 1811 - 1811 - 1811 - 1811 - 1811 - 1811 - 1811 - 1811 - 1811 - 1811 - 1811 - 1811 - 1811 - | 5.0        |            | pF       |

| Солт              | Output Capacity in TRI-STATE®                                 | (Note 2)                            |                                                                                                                 | 9.0        |            | рF       |

| CPD               | Power Dissipation Capacity                                    | (Note 3)                            |                                                                                                                 | 400        |            | рF       |

MM54C200/MM74C200

$C_L = 50 \, pF$

|                    | Parameter                                                     | ameter Conditions                               | MM54C200<br>T <sub>A</sub> = -55°C to +125°C |             | $MM74C200 T_{A} = -45^{\circ}C \text{ to } +85^{\circ}C$ |             | Units    |

|--------------------|---------------------------------------------------------------|-------------------------------------------------|----------------------------------------------|-------------|----------------------------------------------------------|-------------|----------|

|                    |                                                               |                                                 | Min.                                         | Max.        | Min.                                                     | Max.        |          |

| t <sub>ACC</sub>   | Access Time from Address                                      | $V_{CC} = 5.0V$ $V_{CC} = 10V$                  |                                              | 1200<br>520 | ių.                                                      | 1100<br>480 | ns<br>ns |

| t <sub>pd</sub>    | Propagation Delay from $\widetilde{\text{CE}}_3$              | $V_{CC} = 5.0V$ $V_{CC} = 10V$                  | · + ·                                        | 950<br>400  | - ) -                                                    | 850<br>360  | ns<br>ns |

| t <sub>pdCE1</sub> | Propagation Delay from $\overline{CE}_1$ or $\overline{CE}_2$ | $V_{CC} = 5.0 V$ $V_{CC} = 10 V$                |                                              | 650<br>300  |                                                          | 600<br>275  | ns<br>ns |

| t <sub>SA</sub>    | Address Setup Time                                            | $V_{CC} = 5.0V$ $V_{CC} = 10V$                  | 250<br>120                                   |             | 250<br>120                                               |             | ns<br>ns |

| t <sub>HA</sub>    | Address Hold Time                                             | $V_{CC} = 5.0 V$ $V_{CC} = 10 V$                | 100<br>50                                    |             | 100<br>50                                                |             | ns<br>ns |

| twe                | Write Enable Pulse Width                                      | V <sub>CC</sub> = 5.0V<br>V <sub>CC</sub> = 10V | 450<br>225                                   |             | 400<br>200                                               |             | ns<br>ns |

| t <sub>CE</sub>    | Disable Pulse Width                                           | $V_{CC} = 5.0V$ $V_{CC} = 10V$                  | 500<br>250                                   |             | 460<br>230                                               |             | ns<br>ns |

| t <sub>HD</sub>    | Data Hold Time                                                | $V_{CC} = 5.0 V$ $V_{CC} = 10 V$                | 50<br>25                                     |             | 50<br>25                                                 |             | ns<br>ns |

Note 1: "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. Except for "Operating Range" they are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" provides conditions for actual device operation.

Note 2: Capacitance is guaranteed by periodic testing.

Note 3: C<sub>PD</sub> determines the no load AC power consumption of any CMOS device. For complete explanation see 54C/74C Family Characteristics application note, AN-90.

4-9

## **Switching Time Waveforms**

Read and Write Cycles Using CE3 (CE1 = CE2 = logic 0)