# StarLAN ENCODER DECODER

• CONFORMS WITH STARLAN SPECIFICA-TION

SGS-THOMSON MICROELECTRONICS

- SUPPORTS MULTI-POINT EXTENSION

- AUTO COMPENSATION FOR LINE REVER-SAL

- COMPATIBLE WITH MK5032 VLANCE AND INTEL 82586/82588

- CLOSE PIN COMPATIBILITY WITH SEEQ8023

- DATA RATES TO 2.66Mbps SUPPORTED

- MANCHESTER DATA ENCODING/DECODING

- COLLISION DETECTION CIRCUITRY WITH THE FOLLOWING FEATURES :

- detects missing mid-bit transitions

- transitions too close together

- transitions too far apart

- external collision input pin

- carrier dropout

- watchdog timer

- AT&T release 1 collision presence signal

echo timeout

- RECEIVE END-OF-FRAME DETECTION

input protection at end-of-frame

- LOOPBACK CAPABILITY

- RECEIVE CARRIER AUTOMATICALLY CON-VERTED TO A LEVEL SIGNAL

- ECHO TIMER TO SIGNAL ERROR IF TRANS-MITTED FRAME IS NOT RECEIVED

- HEARTBEAT GENERATION

- IN 82586 MODE, INSENSITIVE TO EXTRA BITS AHEAD OF PREAMBLE

- DIGITAL PHASE-LOCKED LOOP

- ON CHIP CRYSTAL OSCILLATOR, 8X OR 6X OPERATION

- CMOS TECHNOLOGY

- 20-PIN DIP

- SINGLE 5-VOLT SUPPLY

- ALL INPUTS AND OUTPUTS TTL COMPATIBLE\*

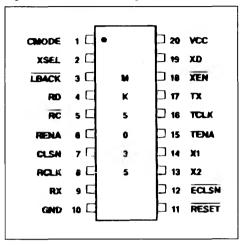

## Figure 1 : MK5035 Pin Assignment.

#### **GENERAL DESCRIPTION**

The MK5035 is a Manchester Encoder/Decoder chip incorporating several features that make it an ideal StarLAN station chip. The MK5035 performs three functions. It encodes data from a controller chip into Manchester data. It decodes Manchester data from the line transceiver and produces NRZ data and clock for the controller chip. It also detects collisions and signals the controller chip that a collision has occurred.

The MK5035 has several enhancements for Star-LAN and Multi-Point extension (MPE) StarLAN. These include auto compensation for wiring reversal, echo timer, external collision detect, watchdog timer, and heartbeat, among others.

\* Crystal inputs have CMOS thresholds.

## **PIN DESCRIPTION**

| CONTRO | OLLER INT | ERFACE                                                                                                                                   |

|--------|-----------|------------------------------------------------------------------------------------------------------------------------------------------|

| RX     | Output    | RX is the serial receive data after decoding.                                                                                            |

| RENA   | Output    | This signal indicates that data is available to the controller on the RX output.                                                         |

| RCLK   | Output    | RCLK is the receive data clock recovered from the incoming data RD.                                                                      |

| тх     | Input     | TX is the serial data to be transmitted. It is clocked into the chip by TCLK.                                                            |

| TENA   | Input     | This signal indicates that data<br>is valid on the TX input. It goes<br>active with the first bit of trans-<br>mission.                  |

| TCLK   | Output    | TCLK is the transmit data clock. All transmit interface signals are synchronized to this clock.                                          |

| CLSN   | Output    | This signal is asserted when a manchester violation is detected on the RD line or when the external collision input (ECLSN) goes active. |

#### TRANSCEIVER INTERFACE

| XD  | Output | Encoded transmit data output. |  |  |  |  |

|-----|--------|-------------------------------|--|--|--|--|

| XEN | Output | Transmit output enable. This  |  |  |  |  |

- signal goes low to indicate XD RESET active. It goes high at the end of transmission.

- RD Input Encoded receive data input.

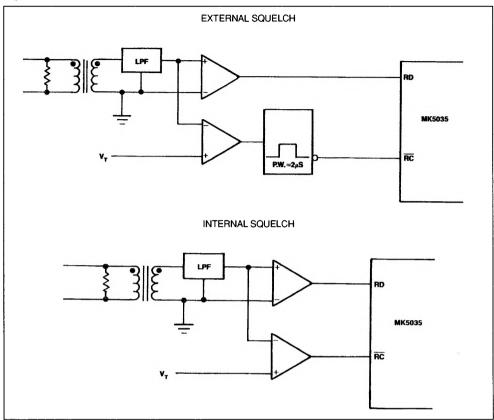

- RC Input Receive carrier input. Receive carrier can be either a pulse stream or an active low signal to indicate carrier active. The chip contains internal squelch circuitry, as shown in figure 3, to convert a pulse signal to a level signal. ECLSN Input External collision input. When this pin is held low for at least

20nS, an external collision is signaled. OTHER PINS CMODE Input This input allows the part to be used with either Mostek or Intel controllers :

CMODE = 0, 82586/82588 (see note)

Transmit data (TX) is sampled on the rising edge of TCLK. Receive data (RX) transitions on the rising edge of RCLK.

TENA - active low

RENA - active low - goes active when phase lock loop is locked.

CLSN - active low

CMODE = 1, SGS-THOMSON VLANCE MK5032

Transmit data (TX) is sampled on the falling edge of TCLK. Receive data (RX) transitions on the falling edge of RCLK.

TENA - active high

RENA - active high - goes active when phase lock loop is locked.

CLSN - active high

LBACK Input When this input is low the part will be put into internal loopback. The transmit data will be internally looped back as receive data. See figure 2. The outputs XD and XEN will be held inactive during loopback.

> Input When this pin is low the chip is in reset mode. All interface signals will be inhibited except TCLK. RESET should remain active for three TCLK periods.

Input This input selects the clock divider.

If XSEL = 0, it is 8X.

If XSEL = 1, it is 6X.

X1. X2 Crystal oscillator inputs. A Inputs crystal can be connected between these inputs, or a CMOS level square wave can be connected to X1 while X2 is left unconnected. VCC Input + 5V ± 5%

Note : Compatible with controller chips based on preliminary controller data sheets.

XSEL

GND

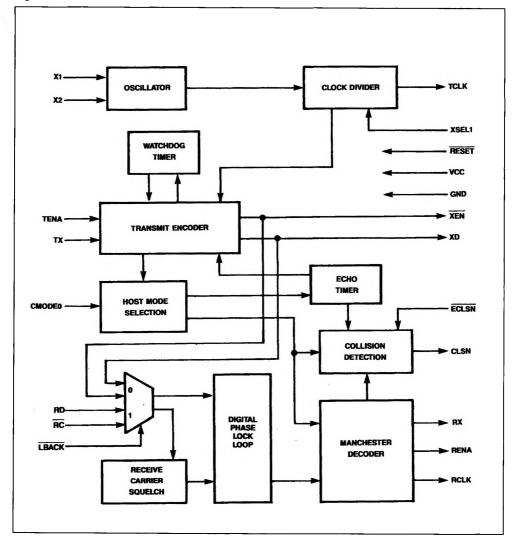

Figure 2 : StarLAN Encoder Decoder. MK5035.

-

Figure 3 : Internal Versus External Time Squelch.

## CIRCUIT DESCRIPTION

## TRANSMITTER

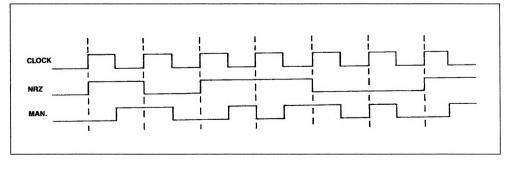

The transmitter encodes NRZ data from the control-

ler chip into the Manchester data. The diagram below shows the two encoding schemes.

Data encoding and transmission begin when the controller chip brings TENA active. The start of data encoding is delayed by two bits when in 82586/82588 mode.  $T_X$  is sampled using TCLK as the clock. The encoded data is output on XD. XEN goes low with the first bit of data output on XD. The transmit delay, delay from TENA active to XEN active, is less than 1.5 TCLKs. The controller chip signals end of data by bringing TENA inactive.

XD will be held high for an additional 1.5 TCLKs if the last data bit is a one, and for 2 TCLKs if the last data bit is a zero. During this time XEN is held active.

#### RECEIVER

The receiver consists of four major sections.

- 1) Receive carrier squelch

- 2) Internal loopback

- 3) Digital phase locked loop

- 4) Manchester decoder

The receiver takes Manchester data in on RD, when receive carrier (RC) is active, and decodes the data into NRZ data and also produces clock (RCLK) from the data. The NRZ data is output to the controller on RX.

#### RECEIVE CARRIER SQUELCH

The Receive carrier pin has internal squelch logic that allows the signal to be either a level signal or a pulse train. Receive carrier is active low. The receive carrier must be present for 3 clock samples to be considered a valid carrier. Once the carrier is considered valid then it must be active for only one clock sample time every two bit times to remain valid. (see figure 3).

#### Automatic Compensation For Wiring Reversal

When installing twisted pair telephone wiring, it is often difficult and expensive to maintain proper polarity on the wire pairs. The MK5035 will automatically compensate for this reversal. Any frame that is received with inverse polarity will be detected and decoded with the correct polarity.

#### LOOPBACK

When loopback is enabled (LBACK low), RD and RC are ignored. Transmit data is internally looped

back as receive data. The transmitter outputs XD and XEN are disabled during loopback.

#### DIGITAL PHASE LOCKED LOOP (DPLL)

The digital phase locked loop is implemented with a counter that clears on each transition of the receive data. The phase locked loop will declare "lock" after receiving data that has two "long transitions". A long transition occurs when the receive data does not change for at least 4/6 (5/8 in 8X mode) of a bit time.

#### MANCHESTER DECODER

The receive data (after inversion if needed) is fed into the decoder along with the recovered 2X clock from the DPLL. The decoder changes the receive data to NRZ data. The NRZ data is output on TX. RENA signals the controller chip that data is available. (see mode pin descriptions). RCLK is a 1X clock output that is synchronous with the data on RX.

#### PROTECTION TIME

After the end of a received frame the receiver is disabled for 20 bit times. This protection time guarantees immunity to spikes caused by transformer coupling after the end of frame.

#### COLLISION

CLSN is an output to the controller chip that indicates a possible problem with the data. There are several sources of collision.

- Transitions too close together Collision is signaled if the receive data stream transitions a second time in less than 2/6 (3/8 in 8X mode) bit times.

- Transitions too far apart Collision is signaled if the receive data stream does not transition again within 9/6 (10/8 in 8X mode) bit times.

- Manchester violation

If the data violates Manchester coding rules, then collision is signaled.

A Manchester violation is a missing mid-bit transition.

- 4) Watchdog timer

If the watchdog timer expires, then collision will be signaled.

## MK5035N

5) Echo timer

If the echo timer expires without receive carrier going active, then collision will be signaled.

- External collision If the external collision pin (ECLSN) goes low for at least 20ns, then collision will be signaled.

- Receive carrier lost during transmission If the MK5035 is transmitting and the receive carrier goes active and then inactive before it is through transmitting, then collision is signaled.

#### 8) Heartbeat

Collision, as a result of heartbeat, will be signaled 8 TCLKs after TENA goes away, and collision will remain active for at least 8 TCLKs.

Once CLSN is activated it remains active until both TENA and RENA go inactive. The exception to this is heartbeat. If heartbeat signals collision, then collision is guaranteed to remain for 8 TCLKs.

#### WATCHDOG TIMER

The watchdog timer ensures that the MK5035 will not transmit for more than 101K bit times. The timer is started when TXEN goes active. The timer resets when TXEN goes inactive. If TXEN remains active for more than 101K bit times, then the timer will timeout causing collision to be asserted and XEN to go inactive. If loopback is enabled, watchdog timeout will occur after 325 bit times. This particular timer value allow StarLAN HUBs to activate their own jabber functions, thereby alerting net management.

#### ECHO TIMER

When the echo timer is enabled the MK5035 expects the data that it is transmitting to be received on RC/RD within 510 bit times. The echo timer is activated when TXEN goes active. If 510 bit times elapse before RENA goes active, then the timer will time out causing collision to be activated.

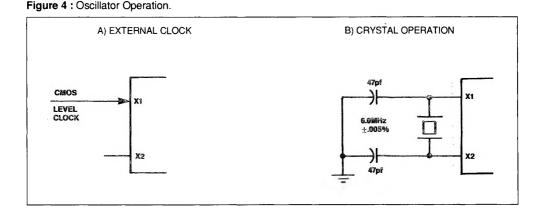

#### Oscillator

The MK5035 will accept two forms of clock input : a CMOS input or a crystal. If pin X2 is left unconnected, a 6.0/8.0MHz  $\pm$  0.01% CMOS clock may be applied to pin X1. Alternately, a crystal circuit may be connected between X1 and X2 to form the basis of an oscillator. Typically, a 6.0/8.0  $\pm$  0.005% parallel resonant crystal is needed to insure the  $\pm$  0.01% frequency accuracy required for StarLAN. Refer to figure 4. A fundamental mode, parallel resonance type crystal should be used with the manufacturer's suggested load capacitance.

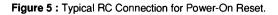

#### **Reset Input**

The reset pin is an active low Schmidt trigger input. A simple RC network may be used to insure correct operation upon power-up. Refer to fig. 5.

## **ELECTRICAL SPECIFICATIONS**

This chapter provides tabular presentations for Absolute Maximum Ratings, DC Characteristics, Capacitance and AC Timing Specifications. In addition, illustrations are provided for an Output Load Diagram (figure 9) and Station Timing Diagrams.

#### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Paramter                                  | Value                        | Unit |

|------------------|-------------------------------------------|------------------------------|------|

| TA               | Temperature Under Bias                    | -25 to +100                  | °C   |

| T <sub>stg</sub> | Storage Temperature                       | - 65 to + 150                | °C   |

| V <sub>I</sub>   | Voltage on any Pin with Respect to Ground | -0.5 to V <sub>CC</sub> +0.5 | v    |

| PD               | Power Dissipation (no load)               | 50                           | mW   |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC CHARACTERISTICS (T<sub>A</sub> = 0°C to 70°C, $V_{cc}$ = + 5V ± 5% unless otherwise specified)

| Symbol          | Test conditions                        | Min.  | Max.                  | Units |

|-----------------|----------------------------------------|-------|-----------------------|-------|

| ٧L              |                                        | - 0.5 | + 0.8                 | v     |

| V <sub>IH</sub> | Except X1                              | + 2.0 | V <sub>CC</sub> + 0.5 | V     |

| VIH             | X1                                     | + 3.5 | V <sub>CC</sub> + 0.5 | V     |

| V <sub>OL</sub> | @ I <sub>OL</sub> = 3.2mA, except X2   |       | + 0.5                 | V     |

| V <sub>OH</sub> | @ I <sub>OH</sub> = - 0.4mA, except X2 | + 2.4 |                       | V     |

| V <sub>OH</sub> | $@I_{OH} = -40\mu A$ , except X2       | + 3.2 |                       | v     |

| կլ              | @ $V_{IN} = 0.4$ to $V_{CC}$           |       | ± 10                  | μA    |

| lcc             |                                        |       | 8                     | mA    |

## CAPACITANCE : F = 1MHz

| Symbol          | Conditions | Min. | Max. | Units |

|-----------------|------------|------|------|-------|

| CIN             |            |      | 10   | pf    |

| COUT            |            |      | 10   | pf    |

| C <sub>IO</sub> |            |      | 20   | pf    |

## AC TIMING SPECIFICATIONS

$(T_A = 0^{\circ}C \text{ to } 70^{\circ}C, V_{CC} = +5V \pm 5\% \text{ unless otherwise specified}, V_{TH} = 2.0V, V_{TL} = 0.8V)$

| #  | Signal | Symbol              | $V \pm 5\%$ unless otherwise specified, $V_{TH} = 2.0V$ , $V_{TL} =$<br>Parameter | Min.<br>ns | Typ.<br>ns | Max.<br>ns |

|----|--------|---------------------|-----------------------------------------------------------------------------------|------------|------------|------------|

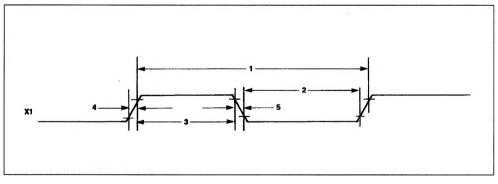

| 1  | X1     | T <sub>X1T</sub>    | X1 period                                                                         | 62         |            |            |

| 2  | X1     | T <sub>X1L</sub>    | X1 low time                                                                       | 24         |            |            |

| 3  | X1     | T <sub>X1H</sub>    | X1 high time                                                                      | 24         |            |            |

| 4  | X1     | T <sub>X1R</sub>    | Rise time of X1                                                                   | 0          |            | 8          |

| 5  | X1     | T <sub>X1F</sub>    | Fall time of X1                                                                   | 0          |            | 8          |

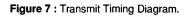

| 6  | XEN    | TXEN                | XEN delay from X1                                                                 |            | 40         | 65         |

| 7  | XD     | T <sub>XD</sub>     | XD delay from X1                                                                  |            | 40         | 65         |

| 8  | XD     | J <sub>XD</sub>     | Transmit jitter $ T_{XD} \uparrow - T_{XD} \downarrow   \div 2$                   |            | 4          | 6          |

| 9  | TCLK   | T <sub>CLK</sub>    | TCLK delay from X1                                                                |            |            | 70         |

| 10 | ΤХ     | T <sub>TXST1</sub>  | TX setup to falling edge of TCLK, CMODE = 1                                       | 90         |            |            |

| 11 | TX     | T <sub>TXHT1</sub>  | TX hold from falling edge of TCLK, CMODE = 1                                      | 15         |            |            |

| 12 | ΤХ     | T <sub>TXS</sub>    | TX setup to X1                                                                    | 15         |            |            |

| 13 | ΤХ     | Т <sub>тхн</sub>    | TX hold from X1                                                                   | 15         |            |            |

| 14 | TENA   | T <sub>TNAST1</sub> | TENA setup to falling edge of TCLK, CMODE = 1                                     | 90         |            |            |

| 15 | TENA   | T <sub>TNAST1</sub> | TENA hold from falling edge of TCLK, CMODE = 1                                    | 15         |            |            |

| 16 | TENA   | TTENAS              | TENA setup to X1                                                                  | 15         |            |            |

| 17 | TENA   | TTENAH              | TENA hold from X1                                                                 | 15         |            |            |

| 18 | ΤХ     | T <sub>TXSTO</sub>  | TX setup to rising edge of TCLK, CMODE = 0                                        | 90         |            |            |

| 19 | ТХ     | T <sub>TXSTO</sub>  | TX hold to rising edge of TCLK, CMODE = 0                                         | 15         |            |            |

| 20 | ΤХ     | T <sub>TXS</sub>    | TX setup to X1, CMODE = 0                                                         | 15         |            |            |

| 21 | ΤХ     | Т <sub>тхн</sub>    | TX hold from X1, CMODE = 1                                                        | 15         |            |            |

| 22 | TENA   | T <sub>TNASTO</sub> | TENA setup to positive edge of TCLK, CMODE = 0                                    | 90         |            |            |

| 23 | TENA   | T <sub>TNAHTO</sub> | TENA hold to positive edge of TCLK, CMODE = 0                                     | 15         |            |            |

| 24 | TENA   | T <sub>TNAS</sub>   | TENA setup to X1, CMODE = 0                                                       | 15         |            |            |

| 25 | TENA   | T <sub>TNAH</sub>   | TENA hold from X1, cmode = 0                                                      | 15         |            |            |

| 26 | CLSN   | T <sub>CLSN</sub>   | CLSN delay from X1                                                                |            |            | 70         |

| 27 | ECLSN  | TECLSN              | Minimum detected pulse width                                                      |            | 5          | 20         |

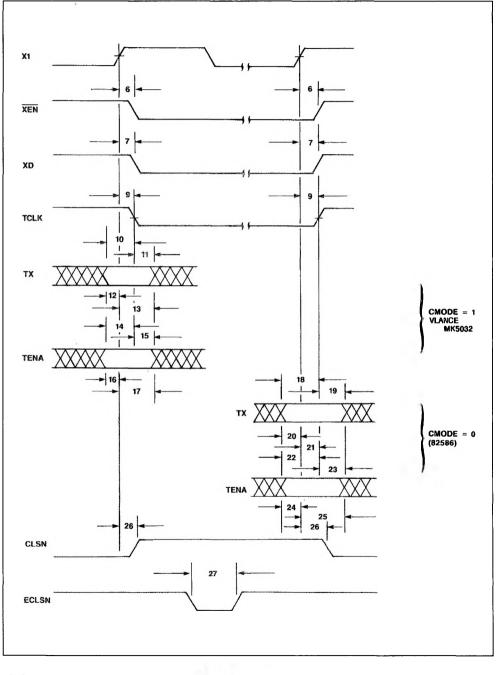

| 28 | RC     | TRCS                | RC setup to X1                                                                    | 15         |            |            |

| 29 | RC     | TRCH                | RC hold from X1                                                                   | 15         |            |            |

# AC TIMING SPECIFICATIONS (continued)

-

| #  | Signal | Symbol               | Parameter                                                                                                | Min.<br>ns             | Typ.<br>ns | Max.<br>ns           |

|----|--------|----------------------|----------------------------------------------------------------------------------------------------------|------------------------|------------|----------------------|

| 30 | RD     | T <sub>RCH</sub>     | RD setup to X1                                                                                           | 15                     |            |                      |

| 31 | RD     | T <sub>RDS</sub>     | RD hold from X1                                                                                          | 15                     |            |                      |

| 32 | RD     | J <sub>RD6</sub>     | RD Incoming Jitter Tolerance,<br>6X mode, X1 = 6MHz, $T_{X1T} -  T_{RDS} \uparrow - T_{RDS} \downarrow $ |                        | 165        | 161                  |

| 33 | RD     | J <sub>RD8</sub>     | RD Incoming Jitter Tolerance,<br>8X mode, X1 = 8MHz, $T_{X1T} -  T_{RDS} \uparrow - T_{RDS} \downarrow $ |                        | 123        | 119                  |

| 34 | RCLK   | T <sub>RCLK</sub>    | RCLK delay from X1, CMODE = 1                                                                            |                        | 40         | 65                   |

| 35 | ТΧ     | T <sub>RXRCK1</sub>  | RX delay from falling RCLK, CMODE = 1                                                                    | - 30                   |            | 30                   |

| 36 | RX     | T <sub>RX</sub>      | RX delay from X1, CMODE =1                                                                               |                        | 40         | 65                   |

| 37 | RENA   | T <sub>RNARCK1</sub> | RENA delay from falling RCLK, CMODE =1                                                                   | - 30                   |            | 30                   |

| 38 | RENA   | T <sub>RENA</sub>    | RENA delay from X1, CMODE =1                                                                             |                        | 45         | 65                   |

| 39 | CLSN   | T <sub>CSNRCK1</sub> | CLSN delay from falling edge RCLK, CMODE = 1                                                             | - 30                   |            | 30                   |

| 40 | CLSN   | T <sub>CLSN</sub>    | CLSN delay from X1, CMODE = 1                                                                            |                        |            | 70                   |

| 41 | RCLK   | T <sub>RCLK0</sub>   | RCLK delay from X1, CMODE = 0                                                                            |                        | 40         | 65                   |

| 42 | RCLK   | P <sub>RCLK</sub>    | RCLK pulse width, CMODE = 0                                                                              | T <sub>X1T</sub> 20    |            | T <sub>X1T</sub> +20 |

| 43 | RCLK   | T <sub>RXCLK</sub>   | RCLK delay from RX stable, CMODE = 0                                                                     | T <sub>X1T</sub> 20    |            |                      |

| 44 | RX     | T <sub>CLKRX</sub>   | RX hold from falling edge of RCLK, CMODE = 0                                                             | 2*T <sub>X1T</sub> -20 |            |                      |

| 45 | RCLK   | T <sub>RNACLK</sub>  | RCLK delay from RENA stable, CMODE = 0                                                                   | T <sub>X1T</sub> 20    |            |                      |

| 46 | RENA   | T <sub>CLKRNA</sub>  | RENA hold from falling edge of RCLK, CMODE = 0                                                           | 2*T <sub>X11</sub> -20 |            |                      |

| 47 | RCLK   | T <sub>CSNCLK</sub>  | Rising RCLK delay from CLSN stable, CMODE = 0                                                            | 2*T <sub>X1T</sub> -20 |            |                      |

| 48 | CLSN   | T <sub>CLKCSN</sub>  | CLSN delay from rising edge of RCLK, CMODE = 0                                                           | T <sub>X1T</sub> -20   |            |                      |

# Figure 6 : External X1 Timing Diagram.

SGS-THOMSON MICROELECTRONICS

5

## Figure 8 : Receiver Timing Diagram.

•

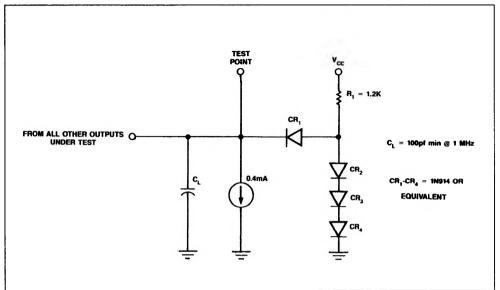

## Figure 9 : Output Load Diagram.

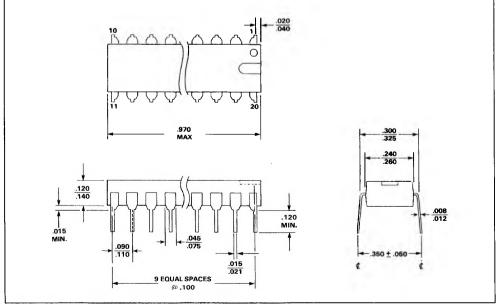

## PACKAGE DESCRIPTION

#### 20 Pin Plastic - MK5035N

Note : Overall length includes .010 flash on either end of package.