# MK48H98/99(N) -20/30/40

## 73,728-BIT 8 K X 8/9 CMOS PARITY SRAM

## ADVANCE DATA

## PIN CONNECTION

- BYTEWYDE 8K x 9 CMOS STATIC RAM

- CONFIGURABLE: x9/ or x8 plus PARITY

- 20,30,40ns DATA ACCESS TIMES

- 25.35.45ns PARITY ERROR ACCESS TIMES

- FAST CYCLE TIMES = 25,35,45ns

- 28-PIN 300 MIL PLASTIC DIP

## DESCRIPTION

The MK48H98/99 is a 73,728-bit CMOS Parity SRAM, organized 8K x 9 using SGS-THOMSON Microelectronics' advanced HCMOS process technology. The MK48H98/99 has a Chip Enable power down feature which sustains an automatic standby mode whenever Chip Enable ( $\overline{\rm E}$ ) goes inactive high. An Output Enable ( $\overline{\rm G}$ ) pin provides a fast high impedance control, allowing fast read/write cycles to be achieved with the common-I/O data bus.

This device offers a high performance CMOS static RAM with a parity generator/checker option on chip. The PE input allows the device to be configured with or without the parity function. When parity is enabled, true parity is generated and stored internally during write operations. Parity data is accessed and checked during read operations. The MK48H98 employs an internal even parity scheme, while the MK48H99 employs an odd parity scheme. The PERR pin is an open-collector output for parity error detection, and easy wired-OR system implementation. If parity is disabled, then DQ8 is simply another data I/O buffer with a totempole configuration. The Parity SRAM requires a single +5 volt supply ± 10%, and all inputs and outputs are TTL compatible.

|                 |    |   | Plastic DIP |   |          |                |

|-----------------|----|---|-------------|---|----------|----------------|

| Α .             | 4  |   |             | 7 | 20       | Vee            |

| A 4             | 1  |   |             | H | 28<br>27 | Vcc            |

| A 5<br>A 6      | 2  |   |             | K | 26       | PE             |

| A 7             | 4  |   |             | F | 25       | A <sub>2</sub> |

| A 8             | 5  |   |             | F | 24       | A 1            |

| A 9             | 6  |   |             | F | 23       | Ao             |

| A 10            | 7  |   | MK48H98     | F | 22       | G              |

| A 11            | 8  |   | MK48H99     | F | 21       | A <sub>3</sub> |

| A 12            | 9  |   |             | 5 | 20       | E              |

| DQ 0            | 10 |   |             | F | 19       | DQ 8 /PERI     |

| DQ 1            | 11 | _ |             | F | 18       | DQ 7           |

| DQ 2            | 12 |   |             | 5 | 17       | DQ 6           |

|                 | 13 |   |             |   | 16       |                |

| Vss             | 14 |   |             |   | 15       | _              |

| DQ <sub>3</sub> | 13 |   |             |   | 16       | DQ 5           |

### PIN NAMES

| A <sub>0</sub> -A <sub>12</sub>  | Address Inputs                       |

|----------------------------------|--------------------------------------|

| DQ <sub>0</sub> -DQ <sub>7</sub> | Data I/O <sub>0-7</sub>              |

| DQ <sub>8</sub> /PERR            | Data I/O <sub>8</sub> , Parity Error |

| Ē <sub>1</sub>                   | Chip Enable                          |

| PE                               | Parity Enable                        |

| G                                | (OE) Output Enable                   |

| W                                | Write/read Enable                    |

| Vcc,Vss                          | +5V, GND                             |

#### MODES OF OPERATION

As previously mentioned, the PE input can configure the MK48H98/99 to internally generate and check true parity. When the PE input is a logic zero (V<sub>IL</sub>), the parity function (parity generator/checker) is enabled. If PE is a logic one (V<sub>IH</sub>), the device is configured as a standard 8K x 9 SRAM. The device configuration can be accomplished by tying the PE input either high or low, depending upon the desired mode of operation. For diagnostic purposes, a parity error can be forced by writing a false parity bit pattern (PE= V<sub>IH</sub>), and reading with parity true (PE= V<sub>IL</sub>). This defines a dynamic approach for **mix-mode** operation in addition to the basic device modes.

The mix-mode operation allows the parity function to be enabled while Writing (PE =  $V_{II}$ ). and disabled during Read operations (PE = VIH). This provides the user with self-generated parity from the Parity SRAM, with an external system parity bit. Conversely, parity can be disabled while Writing (PE = VIH), and true parity checked internally with a device parity error detection (PERR) during Read operations (PE = V<sub>II</sub>). This mode allows the device to check system generated parity without designing external parity logic. However, transceiver logic is required for DQ<sub>8</sub>/PERR in this mode. The MK48H98/99 Truth table depicts all modes of operation. This includes either static or dynamic mode operations.

#### MK48H98/99 TRUTH TABLE

| E | W | G | PE | MODE                     | DQ   |

|---|---|---|----|--------------------------|------|

| Н | Χ | Χ | X  | Standby                  | Hi-Z |

| L | L | Х | Н  | Write X 9 <sup>(1)</sup> | DIN  |

| L | Н | L | Н  | Read X 9 <sup>(1)</sup>  | Dout |

| L | Н | Н | Н  | Read X 9 <sup>(1)</sup>  | Hi-Z |

| L | L | Х | L  | Write X 8 <sup>(2)</sup> | DIN  |

| L | Н | L | L  | Read X 8 <sup>(2)</sup>  | Dout |

| L | Н | Н | L  | Read X 8 <sup>(2)</sup>  | Hi-Z |

#### NOTES :

### READ MODE

The MK48H98/99 is in the Read mode whenever Write Enable (W) is high and Chip Enable (E) is low. This provides access to data from nine of 73,728 locations in the static memory array. If Parity Enable (PE) is high, data is accessed as a 9-bit word; if PE is low data is accessed as an 8-bit word plus parity error (PERR). The unique address is specified by the 13 address inputs. Valid data will be available at the DQ Output pins within tayov after the last stable address, and PERRwill be valid within taypy of the last stable address providing G. E. and PE are low (see truth table for logic options). If E, PE, or G access times are not met, data access and parity error access times will be measured from the limiting parameter telov, telpy, tpelpy, tpehov, tglov, or tglpy rather than the address.

#### WRITE MODE

The MK48H98/99 is in the Write mode whenever the W and E pins are low. Either E or W must be inactive during Address transitions. The Write begins with the concurrence of E and W being active low. Therefore, address setup times are referenced to W, E, and/or PE as tavwl tavel and tavpel respectively, and is determined to the latter occurring edge. The Write cycle can be terminated by the earlier rising edge of Write Enable or Chip Enable. Parity Enable (PE) allows the on-board parity function to generate true parity if active low, but cannot terminate a write cycle by going high.

If the Output is enabled (E = low, and G = low), then W will return the outputs to high impedance within  $t_{WLOZ}$  of its falling edge. Care must be taken to avoid bus contention in this type of operation. Data-in must be valid for towh to the rising edge of W, E or PE, whichever occurs first, and remain valid  $t_{WHDX}$ .

<sup>(1)</sup> Operation and configuration as an 8K X 9 SRAM (PE= High)

<sup>(2)</sup> Generate and store true parity during Write Cycles; PERR enabled and valid during Read Cycles (PE= Low)

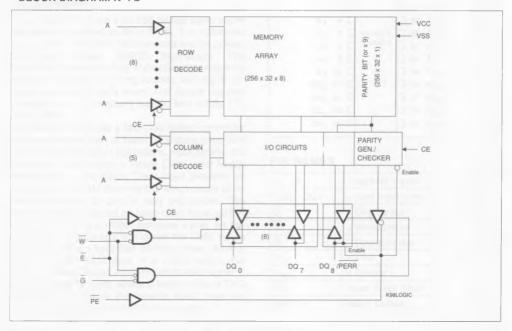

## MK48H98/99 BLOCK DIAGRAM NO. 1

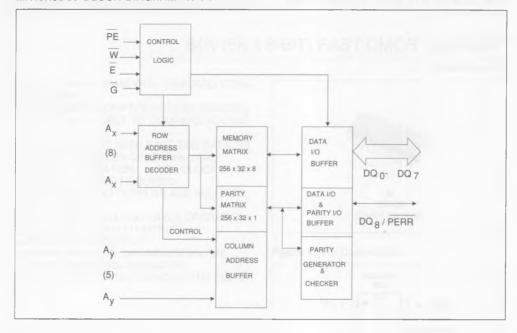

## BLOCK DIAGRAM N<sup>O</sup>. 2