# MK48H64/MK48H65(N,P) -35/45/55/70

# 64K (8K $\times$ 8-BIT) CMOS FAST STATIC RAM

ADVANCED DATA

- 35, 45, 55, AND 70 ns ADDRESS ACCESS TIME

- EQUAL ACCESS AND CYCLE TIMES

- STATIC OPERATION NO CLOCKS OR TIMING STROBES REQUIRED

- LOW V<sub>CC</sub> DATA RETENTION 2 VOLTS

- ALL INPUTS AND OUTPUTS ARE CMOS AND TTL COMPATIBLE

- LOW POWER OPERATION, 10μA CMOS STAND-BY CURRENT UTILIZING FULL CMOS 6-T CELL

- **THREE STATE OUTPUT**

- STANDARD 28-PIN PACKAGE IN 600 MIL PLAS-TIC OR 600 MIL CERAMIC DIP. MK48H65 AVAIL-ABLE IN 300 MIL PLASTIC DIP.

### MK48H64/MK48H65 TRUTH TABLE

| W | Eſ | E2 | Ğ | MODE     | DQ               | POWER   |

|---|----|----|---|----------|------------------|---------|

| Х | Н  | X  | X | Deselect | High-Z           | Standby |

| X | X  | L  | Х | Deselect | High-Z           | Standby |

| Н | L  | Н  | Н | Read     | High-Z           | Active  |

| Н | L  | Н  | L | Read     | Q <sub>OUT</sub> | Active  |

| L | L  | Н  | Х | Write    | D <sub>IN</sub>  | Active  |

### DESCRIPTION

The MK48H64 and MK48H65 are 65,536-bit fast static RAMs organized as 8K  $\times$  8 bits. They are fabricated using SGS-THOMSON's low power, high performance, CMOS technology. The devices feature fully static operation requiring no external clocks or timing strobes, with equal address access and cycle times. They require a single  $+5V \pm 10$ % supply, and are fully TTL compatible.

The MK48H64 and MK48H65 have a Chip Enable power down feature which sustains an automatic standby mode whenever either Chip Enable goes inactive (E1 goes high or E2 goes low). An Output

| FIGURE 1. PIN CONNECTIONS |      |   |   |            |     |  |  |  |

|---------------------------|------|---|---|------------|-----|--|--|--|

|                           |      |   |   |            |     |  |  |  |

| N/C                       | 1 [  | • |   | □ 28       | Vcc |  |  |  |

| A12                       | 2    |   |   | □ 27       | W   |  |  |  |

| A7                        | 3 □  |   |   | □ 26       | E2  |  |  |  |

| A6                        | 4 🗆  |   |   | □ 25       | A8  |  |  |  |

| A5                        | 5 🗆  |   |   | □ 24       | A9  |  |  |  |

| A4                        | 6 □  |   |   | □ 23       | A11 |  |  |  |

| A3                        | 7 🗆  |   |   | □ 22       | G   |  |  |  |

| A2                        | 8 🗆  |   |   | □ 21       | A10 |  |  |  |

| A1                        | 9 🗆  |   |   | □ 20       | E1  |  |  |  |

| A0                        | 10 🗆 |   |   | □ 19       | DQ7 |  |  |  |

| DQ0                       | 11 🗆 |   |   | □ 18       | DQ6 |  |  |  |

| DQ1                       | 12 🗆 |   |   | <b></b> 17 | DQ5 |  |  |  |

| DQ2                       | 13 🗆 |   |   | □ 16       | DQ4 |  |  |  |

| V <sub>ss</sub>           | 14 🗆 |   |   | □ 15       | DQ3 |  |  |  |

|                           |      |   | - |            |     |  |  |  |

|                           |      |   |   |            |     |  |  |  |

### PIN NAMES

| A0-A12          | Address Inputs    |  |

|-----------------|-------------------|--|

| DQ0-DQ7         | Data Input/Output |  |

| E1, E2          | Chip Enable       |  |

| W               | Write Enable      |  |

| G               | Output Enable     |  |

| V <sub>CC</sub> | +5V               |  |

| V <sub>SS</sub> | Ground            |  |

| N/C             | No Connection     |  |

|                 |                   |  |

Enable (G) pin provides a high speed tristate control, allowing fast read/write cycles to be achieved with the common-I/O data bus. Operational modes are determined by device control inputs W, G, E1,

and E2, as summarized in the truth table.

The MK48H65 is a space saving 300 mil plastic DIP. The MK48H64 offers the standard 600 mil Plastic or Ceramic DIP.

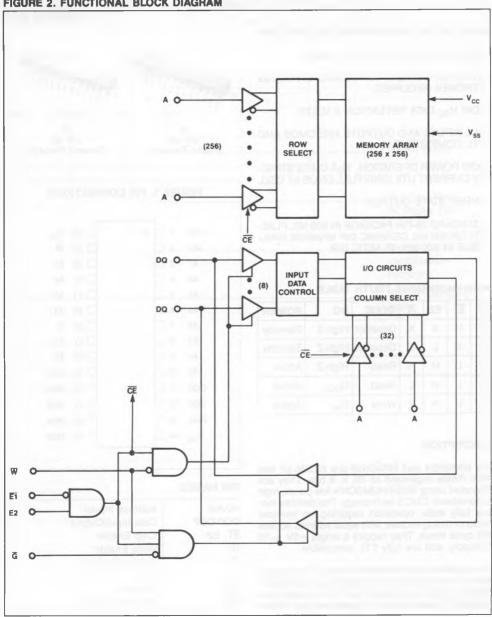

FIGURE 2. FUNCTIONAL BLOCK DIAGRAM

### **READ CYCLE TIMING**

| SYM              | BOLS               |                                      | 48H    | 5X-35    | 48H    | X-45     | 48H6   | SX-55    | 48H    | 6X-70    |          |       |

|------------------|--------------------|--------------------------------------|--------|----------|--------|----------|--------|----------|--------|----------|----------|-------|

| ALT.             | STD.               | PARAMETER                            | MIN    | MAX      | MIN    | MAX      | MIN    | MAX      | MIN    | MAX      | UNITS    | NOTES |

| t <sub>RC</sub>  | t <sub>AVAV</sub>  | Read Cycle Time                      | 35     |          | 45     |          | 55     |          | 70     |          | ns       |       |

| t <sub>AA</sub>  | t <sub>AVQV</sub>  | Address Access Time                  |        | 35       |        | 45       |        | 55       |        | 70       | ns       | 1     |

| t <sub>CEA</sub> | t <sub>E1LQV</sub> | Chip Enable 1 & 2<br>Access Time     |        | 35<br>35 |        | 45<br>45 |        | 55<br>55 |        | 70<br>70 | ns<br>ns | 1     |

| t <sub>OEA</sub> | t <sub>GLOV</sub>  | Output Enable Access<br>Time         |        | 20       |        | 25       |        | 30       |        | 35       | ns       | 1     |

| t <sub>CEL</sub> | t <sub>E1LQX</sub> | Chip Enable 1 & 2 to<br>Output Low-Z | 5<br>5 |          | 5<br>5 |          | 5<br>5 |          | 5<br>5 |          | ns<br>ns | 2     |

| t <sub>OEL</sub> | t <sub>GLQX</sub>  | Output Enable to Low-Z               | 0      |          | 0      |          | 0      |          | 0      |          | ns       | 2     |

| t <sub>CEZ</sub> | t <sub>E1HQZ</sub> | Chip Enable 1 & 2 to<br>High-Z       |        | 15<br>15 |        | 20<br>20 |        | 25<br>25 |        | 30<br>30 | ns<br>ns | 2     |

| t <sub>OEZ</sub> | t <sub>GHQZ</sub>  | Output Enable to<br>High-Z           |        | 15       |        | 20       |        | 25       |        | 30       | ns       | 2     |

| tон              | t <sub>AXQX</sub>  | Output Hold From<br>Address Change   | 5      |          | 5      |          | 5      |          | 5      |          | ns       | 1     |

#### **OPERATIONS**

### **READ MODE**

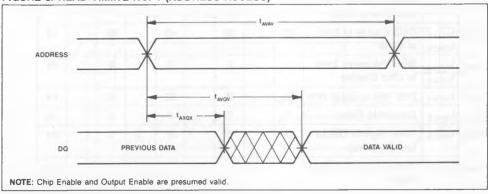

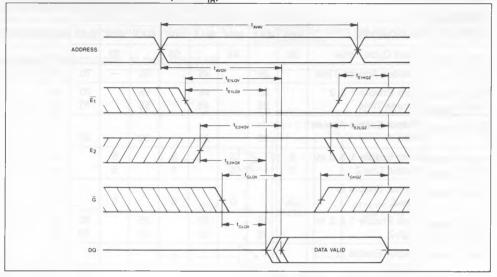

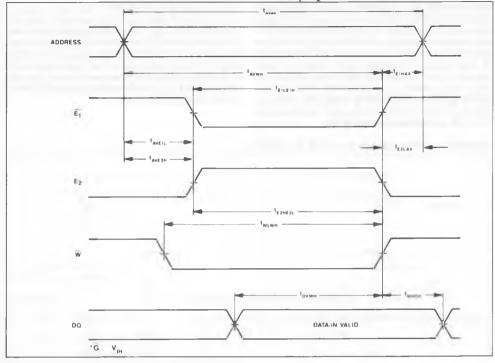

The MK48H64 and MK48H65 are in the read mode whenever Write Enable (W) is high with Output Enable (G) low, and both Chip Enables (E1 and E2) are active. This provides access to data from eight of 65,536 locations in the static memory array. The unique address specified by the 13 Address Inputs defines which one of the 8192 8-bit bytes is to be accessed.

Valid data will be available at the eight Output pins within  $t_{\text{AVQV}}$  after the last stable address, providing  $\overline{G}$  is low,  $\overline{E}1$  is low, and E2 is high. If Chip Enable or Output Enable access times are not met, data access will be measured from the limiting parameter ( $t_{\text{E1LQV}}$ ,  $t_{\text{E2HQV}}$ , or  $t_{\text{GLQV}}$ ) rather than the address. The state of the DQ pins is controlled by the  $\overline{E}1$ ,  $\overline{E}2$ ,  $\overline{G}$ , and  $\overline{W}$  control signals. Data out may be indeterminate at  $t_{\text{E1LQX}}$ ,  $t_{\text{E2HQX}}$ , and  $t_{\text{GLQX}}$ , but data lines will always be valid at  $t_{\text{AVQV}}$ .

FIGURE 3. READ TIMING NO. 1 (ADDRESS ACCESS)

FIGURE 4. READ TIMING NO. 2  $\overline{(W} = V_{IH})$

### WRITE CYCLE TIMING

| SYM              | BOLS                |                                         | 48H | 6X-35 | 48H | 5X-45 | 48H | 6X-55 | 48H | 6X-70 |       |       |

|------------------|---------------------|-----------------------------------------|-----|-------|-----|-------|-----|-------|-----|-------|-------|-------|

| ALT.             | STD.                | PARAMETER                               | MIN | MAX   | MIN | MAX   | MIN | MAX   | MIN | MAX   | UNITS | NOTES |

| t <sub>WC</sub>  | t <sub>AVAV</sub>   | Write Cycle Time                        | 35  |       | 45  |       | 55  |       | 70  |       | ns    |       |

| t <sub>AS</sub>  | t <sub>AVWL</sub>   | Address Set-up Time to Write Enable Low | 0   |       | 0   |       | 0   |       | 0   |       | ns    |       |

| t <sub>AS</sub>  | t <sub>AVE1L</sub>  | Address Set-up Time to Chip Enable      | 0   |       | 0   |       | 0   |       | 0   |       | ns    |       |

| t <sub>AW</sub>  | t <sub>AVWH</sub>   | Address Valid to End of Write           | 25  |       | 35  |       | 45  |       | 60  |       | ns    |       |

| t <sub>WEW</sub> | t <sub>WLWH</sub>   | Write Pulse Width                       | 25  |       | 35  |       | 45  |       | 60  |       | ns    |       |

| t <sub>AH</sub>  | t <sub>WHAX</sub>   | Address Hold Time after End of Write    | 0   |       | 0   |       | 0   |       | 0   |       | ns    |       |

| t <sub>CEW</sub> | t <sub>E1LE1H</sub> | Chip Enable to End of Write             | 25  |       | 35  |       | 45  |       | 60  |       | ns    |       |

| t <sub>WR</sub>  | t <sub>E1HAX</sub>  | Write Recovery Time to Chip Disable     | 0   |       | 0   |       | 0   |       | 0   |       | ns    |       |

| t <sub>DW</sub>  | t <sub>DVWH</sub>   | Data Valid to End of Write              | 25  |       | 30  |       | 30  |       | 40  |       | ns    |       |

| t <sub>DH</sub>  | t <sub>WHDX</sub>   | Data Hold Time                          | 0   |       | 0   |       | 0   |       | 0   |       | ns    |       |

| t <sub>WEL</sub> | twhax               | Write High to Output<br>Low-Z (Active)  | 0   |       | 0   |       | 0   |       | 0   |       | ns    | 2     |

| t <sub>WEZ</sub> | twLQZ               | Write Enable to Output<br>High-Z        |     | 15    |     | 20    |     | 25    |     | 30    | ns    | 2     |

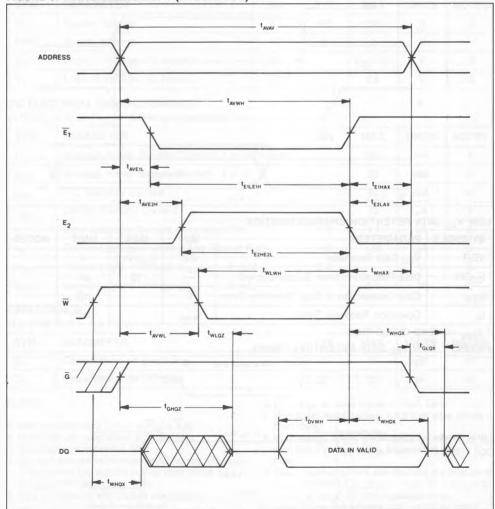

### WRITE MODE

The MK48H64 and MK48H65 are in the Write mode whenever the  $\overline{W}$  and  $\overline{E1}$  pins are low, with E2 high. Either Chip Enable pin or  $\overline{W}$  must be inactive during Address transitions. The Write begins with the concurrence of both Chip Enables being active with  $\overline{W}$  low. Therefore address setup times are referenced to Write Enable and both Chip Enables as  $t_{AVWL}$ ,  $t_{AVE1L}$ , and  $t_{AVE2H}$  respectively, and is determined to the latter occurring edge. The Write cycle can be terminated by the earlier rising edge of  $\overline{E1}$  or  $\overline{W}$ , or the falling edge of E2.

If the Output is enabled ( $\overline{E1} = low$ , E2 = high,  $\overline{G} = low$ ), then  $\overline{W}$  will return the outputs to high impedance within  $t_{WLOZ}$  of its falling edge. Care must be taken to avoid bus contention in this type of operation. Data-in must be valid for  $t_{DVWH}$  to the rising edge of Write Enable, or to the rising edge of  $\overline{E1}$  or the falling edge of E2, whichever occurs first, and remain valid  $t_{WHDX}$  after the rising edge of  $\overline{E1}$  or  $\overline{W}$ , or the falling edge of E2.

FIGURE 5. WRITE TIMING NO. 1 (W CONTROL)

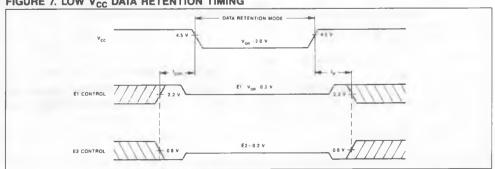

# LOW Voc DATA RETENTION CHARACTERISTICS

| SYMBOLS            | PARAMETERS                              | MIN                 | MAX                   | UNIT | NOTES |

|--------------------|-----------------------------------------|---------------------|-----------------------|------|-------|

| VDR                | V <sub>CC</sub> Data Retention          | 2.0                 | V <sub>CC</sub> (min) | V    |       |

| I <sub>CC</sub> DR | Data Retention Power Supply Current     | _                   | 10                    | μА   |       |

| t <sub>CDR</sub>   | Chip Deselection to Data Retention Time | 0                   |                       | nS   |       |

| t <sub>R</sub>     | Operation Recovery Time                 | t <sub>AVAV</sub> . |                       | nS   |       |

<sup>\*</sup> t<sub>AVAV</sub> = READ CYCLE TIME

# FIGURE 7. LOW VCC DATA RETENTION TIMING

#### ARSOLLITE MAXIMUM RATINGS

| ADOUGH I MAAMMUM I HAIMUU                       |                  |

|-------------------------------------------------|------------------|

| Voltage on any pin relative to GND              | –1.0 V to +7.0 V |

| Ambient Operating Temperature (T <sub>A</sub> ) |                  |

| Ambient Storage Temperature (Plastic)           | 55°C to +125°C   |

| Ambient Storage Temperature (Ceramic)           | 65°C to +150°C   |

| Total Device Power Dissipation                  |                  |

|                                                 | 50 mA            |

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

### RECOMMENDED DC OPERATING CONDITIONS

$(0^{\circ}C \leq T_A \leq 70^{\circ}C)$

| SYM             | PARAMETER                   | MIN  | TYP | MAX                  | UNITS | NOTES |

|-----------------|-----------------------------|------|-----|----------------------|-------|-------|

| V <sub>cc</sub> | Supply Voltage              | 4.5  | 5.0 | 5.5                  | V     | 3     |

| GND             | Supply Voltage              | 0    | 0   | 0                    | ٧     |       |

| V <sub>IH</sub> | Logic 1 Voltage, All Inputs | 2.2  |     | V <sub>CC</sub> +0.3 | ٧     | 3     |

| V <sub>IL</sub> | Logic 0 Voltage, All Inputs | -0.3 |     | 0.8                  | V     | 3     |

### DC ELECTRICAL CHARACTERISTICS

$(0^{\circ}C \le T_A \le 70^{\circ}C)$  (V<sub>CC</sub> = 5.0 V ± 10 percent)

| SYM              | PARAMETER                                         | MIN | MAX | UNITS | NOTES |

|------------------|---------------------------------------------------|-----|-----|-------|-------|

| I <sub>CC1</sub> | Average Power Supply Current f = min cycle        |     | 90  | mA    | 4     |

| I <sub>CC2</sub> | Average Power Supply Current f = 0                |     | 20  | mA    | 5     |

| I <sub>SB1</sub> | TTL Standby Current                               |     | 10  | mA    | 6     |

| I <sub>SB2</sub> | CMOS Standby Current                              |     | 10  | μΑ    | 7     |

| IIL              | Input Leakage Current (Any Input Pin)             | -1  | +1  | μΑ    | 8     |

| I <sub>OL</sub>  | Output Leakage Current (Any Output Pin)           | -10 | +10 | μΑ    | 9     |

| V <sub>OH</sub>  | Output Logic 1 Voltage (I <sub>OUT</sub> = -4 mA) | 2.4 |     | V     | 3     |

| VOL              | Output Logic 0 Voltage (I <sub>OUT</sub> = +8 mA) |     | 0.4 | V     | 3     |

#### CAPACITANCE

$(T_A = 25 \,{}^{\circ}\text{C}, f = 1.0 \text{ MHz})$

| SYM            | PARAMETER                 | TYP | MAX | UNITS | NOTES |

|----------------|---------------------------|-----|-----|-------|-------|

| C <sub>1</sub> | Capacitance on input pins | 4   | 5   | pF    | 10    |

| C <sub>2</sub> | Capacitance on DQ pins    | 8   | 10  | pF    | 10    |

### NOTES

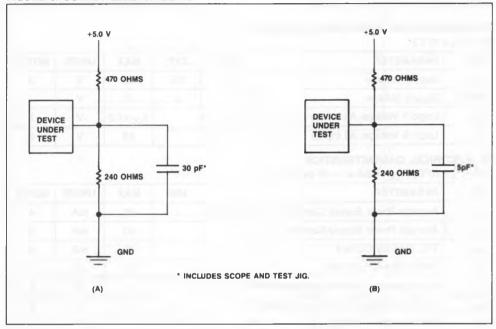

- 1. Measured with load shown in Figure 8(A).

- 2. Measured with load shown in Figure 8(B).

- 3. All voltages referenced to GND.

- 4. I<sub>CC1</sub> is measured as the average AC current with V<sub>CC</sub> = V<sub>CC</sub> (max) and with the outputs open circuit. t<sub>AVAV</sub> = t<sub>AVAV</sub> (min) duty cycle 100%.

- I<sub>CC2</sub> is measured with outputs open circuit.

- 6. E1 = VIH, all other inputs = Don't Care.

- V<sub>CC</sub> (max), and E2≤V<sub>SS</sub> + 0.3 V, all other Inputs = Don't Care.

- Input leakage current specifications are valid for all V<sub>IN</sub> such that 0 V < V<sub>IN</sub> < V<sub>CC</sub>. Measured at V<sub>CC</sub> = V<sub>CC</sub> (max).

- Output leakage current specifications are valid for all V<sub>OUT</sub> such that 0 V < V<sub>OUT</sub> < V<sub>CC</sub>, E1 = V<sub>IH</sub> or E2 = V<sub>IL</sub>, and V<sub>CC</sub> in valid operating range.

- 10. Capacitances are sampled and not 100% tested.

## **AC TEST CONDITIONS**

| Input Levels                                   | to 3.0 V |

|------------------------------------------------|----------|

| Transition Times                               |          |

| Input and Output Signal Timing Reference Level | 1.5 V    |

| Ambient Temperature                            | to 70°C  |

| $V_{CC}$                                       | percent  |

## FIGURE 8. OUTPUT LOAD CIRCUITS