# FEATURES

- Static operation

- Organization: 1K x 8 bit RAM JEDEC pinout

- □ Pin compatible with Mostek's BYTEWYDE™ memory family

- □ 24/28 pin ROM/PROM compatible pin configuration

- High performance

### DESCRIPTION

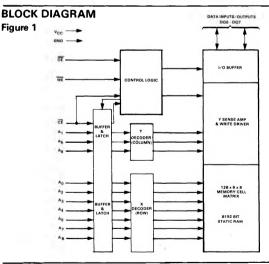

The MK4801A uses Mostek's Scaled POLY 5<sup>™</sup> process and advanced circuit design techniques to package 8,192 bits of static RAM on a single chip. Static operation is achieved with high performance and low power dissipation by utilizing Address Activated<sup>™</sup> circuit design techniques.

## **TRUTH TABLE**

| CE        | ŌE   | WE  | Mode     | DQ              |

|-----------|------|-----|----------|-----------------|

| VIH       | x    | x   | Deselect | High Z          |

| VIL       | x    | VIL | Write    | D <sub>IN</sub> |

| VIL       | VIL  | VIH | Read     | DOUT            |

| VIL       | VIH  | VIH | Read     | High Z          |

| X = Don'i | Care |     |          |                 |

#### □ CE and OE functions facilitate bus control

| Part No.   | Access Time | R∕W<br>Cycle Time |

|------------|-------------|-------------------|

| MK4801A-55 | 55 nsec     | 55/65 nsec        |

| MK4801A-70 | 70 nsec     | 70/80 nsec        |

| MK4801A-90 | 90 nsec     | 90/100 nsec       |

The MK4801A excels in high speed memory applications where the organization requires relatively shallow depth with a wide word format. The MK4801A presents the user a high density cost effective alternative to bipolar and previous generation N-MOS fast memory.

PIN CONNECTIONS Figure 2

|                     | 0  | L                |

|---------------------|----|------------------|

| A7 1                | •  | ⊇ 24 V <b>CC</b> |

| <b>A</b> 6 2 □      |    | 🗆 23 A8          |

| A5 3 ⊑              |    | ⊒22 Ag           |

| A4 4 🗆              |    | □21 WE           |

| A3 5 ⊡              |    | 20 OE            |

| A <sub>26</sub> □   |    | 19 NC            |

| A17[                | 'i | □18 CE           |

| A08C                |    | 17 DQ7           |

| D00 9⊡              |    | 16 DQ6           |

| DQ110               |    | ] 15 <b>DQ</b> 5 |

| DQ211               |    | 14 DQ4           |

| V <sub>SS12</sub> ⊏ |    | ]13DQ3           |

|                     |    |                  |

## **PIN NAMES**

| AO-A9 Address Inputs<br>CE Chip Enable<br>VSS Ground<br>VCC Power (+5V) | WE<br>OE<br>NC<br>DQ <sub>0</sub> -DQ <sub>7</sub> | Write Enable<br>Output Enable<br>No Connection<br>Data In/<br>Data Out |

|-------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|

|-------------------------------------------------------------------------|----------------------------------------------------|------------------------------------------------------------------------|

## **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on any pin relative to V <sub>SS</sub> | 5V to + 7.0V   |

|------------------------------------------------|----------------|

| Operating Temperature T <sub>A</sub> (Ambient) |                |

| Storage Temperature (Ambient)(Ceramic)         |                |

| Storage Temperature (Ambient)(Plastic)         | 55°C to +125°C |

| Power Dissipation                              | 1 Watt         |

| Output Current                                 | 20mA           |

|                                                |                |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

# **RECOMMENDED DC OPERATING CONDITIONS<sup>7</sup>**

$(0^{\circ}C \le T_{A} \le +70^{\circ}C)$

| SYM             | PARAMETER                    | MIN  | ТҮР | MAX  | UNITS | NOTES |

|-----------------|------------------------------|------|-----|------|-------|-------|

| V <sub>cc</sub> | Supply Voltage               | 4.75 | 5.0 | 5.25 | V     | 1     |

| V <sub>SS</sub> | Supply Voltage               | 0    | 0   | 0    | v     | 1     |

| VIH             | Logic "1" Voltage All Inputs | 2.2  |     | 7.0  | v     | 1     |

| V <sub>IL</sub> | Logic "0" Voltage All Inputs | -2.0 | 1   | .8   | V     | 1,9   |

## DC ELECTRICAL CHARACTERISTICS<sup>1,7</sup>

$(0^{\circ}C \le T_{A} \le +70^{\circ}C) (V_{CC} = 5.0 V \pm 5\%)$

| SYM              | PARAMETER                                           | MIN | ТҮР | MAX | UNITS | NOTES |

|------------------|-----------------------------------------------------|-----|-----|-----|-------|-------|

| I <sub>CC1</sub> | Average V <sub>CC</sub> Power Supply Current        |     | 60  | 125 | mA    | 8     |

| ۱ <sub>۱L</sub>  | Input Leakage Current (Any Input)                   | -10 |     | 10  | μΑ    | 2     |

| IOL              | Output Leakage Current                              | -10 |     | 10  | μA    | 2     |

| V <sub>OH</sub>  | Output Logic "1" Voltage I <sub>OUT</sub><br>= 1 mA | 2.4 |     |     | V     |       |

| V <sub>OL</sub>  | Output Logic "0" Voltage I <sub>OUT</sub><br>= 4 mA |     |     | 0.4 | V     |       |

## CAPACITANCE<sup>1,7</sup>

(0°C  $\leq$  T<sub>A</sub>  $\leq$  +70°C) (V<sub>CC</sub> = +5.0 V  $\pm$  5%)

| SYM              | PARAMETER             | TYP   | MAX   | NOTES |

|------------------|-----------------------|-------|-------|-------|

| CI               | All pins (except D/Q) | 4 pF  | 6 pF  |       |

| C <sub>D/Q</sub> | D/Q pins              | 10 pF | 12 pF | 6     |

## **AC ELECTRICAL CHARACTERISTICS 3,4**

$(0^{\circ}C \le T_{A} \le 70^{\circ}) (V_{CC} = 5.0 \text{ V} \pm 5\%)$

|                  | PARAMETER                      | MK48 | MK4801A-55 |     | MK4801A-70 |     | MK4801A-90 |       |             |

|------------------|--------------------------------|------|------------|-----|------------|-----|------------|-------|-------------|

| SYM              |                                | MIN  | MAX        | MIN | MAX        | MIN | MAX        | UNITS | NOTES       |

| t <sub>RC</sub>  | Read Cycle Time                | 55   |            | 70  |            | 90  |            | ns    |             |

| t <sub>AA</sub>  | Address Access Time            |      | 55         |     | 70         |     | 90         | ns    | 5           |

| t <sub>CEA</sub> | Chip Enable Access Time        |      | 25         |     | 35         |     | 45         | ns    | 5           |

| t <sub>CEZ</sub> | Chip Enable Data Off Time      | 5    | 15         | 5   | 20         | 5   | 30         | ns    |             |

| t <sub>OEA</sub> | Output Enable Access<br>Time   |      | 25         |     | 35         |     | 45         | ns    | 5           |

| t <sub>OEZ</sub> | Output Enable Data Off<br>Time | 5    | 15         | 5   | 20         | 5   | 30         | ns    |             |

| t <sub>AZ</sub>  | Address Data Off Time          | 10   |            | 10  |            | 10  |            | ns    |             |

| t <sub>WC</sub>  | Write Cycle Time               | 65   |            | 80  |            | 100 |            | ns    |             |

| t <sub>AS</sub>  | Address Setup Time             | 0    |            | 0   |            | 0   |            | ns    | see<br>text |

| t <sub>AH</sub>  | Address Hold Time              | 15   |            | 20  |            | 30  |            | ns    | see<br>text |

| t <sub>DSW</sub> | Data To Write Setup Time       | 5    |            | 5   |            | 5   |            | ns    |             |

| t <sub>DHW</sub> | Data From Write Hold<br>Time   | 10   |            | 10  |            | 10  |            | ns    |             |

| t <sub>WD</sub>  | Write Pulse Duration           | 25   |            | 30  |            | 40  |            | ns    | see<br>text |

| t <sub>WEZ</sub> | Write Enable Data Off Time     | 5    | 10         | 5   | 15         | 5   | 25         | ns    |             |

| t <sub>WPL</sub> | Write Pulse Lead Time          | 40   |            | 50  |            | 60  |            | ns    |             |

#### NOTES:

- 1. All voltages referenced to V<sub>SS</sub>. 2. Measured with .4  $\leq$  V<sub>I</sub>  $\leq$  5.0 V, outputs deselected and V<sub>CC</sub> = 5 V.

- 3. AC measurements assume Transition Time = 5 ns, levels  $V_{SS}$  to 3.0 V.

- 4. Input and output timing reference levels are at 1.5 V.

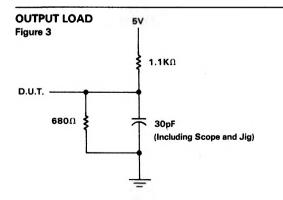

- 5. Measured with a load as shown in Figure 3.

- 6. Output buffer is deselected.

- 7. A minimum of 2 ms time delay is required after application of V<sub>CC</sub> (+5 V) before proper device operation can be achieved.

- 8. ICC measured with outputs open.

- 9. Negative undershoots to a minimum of -1.5 V are allowed with a maximum of 50 ns pulse width.

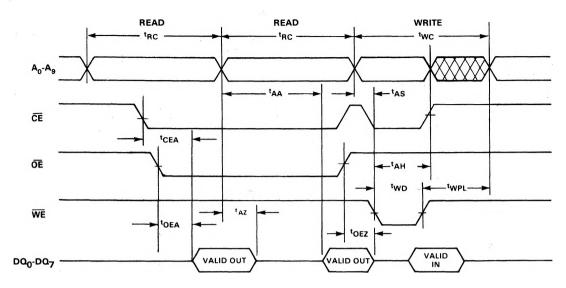

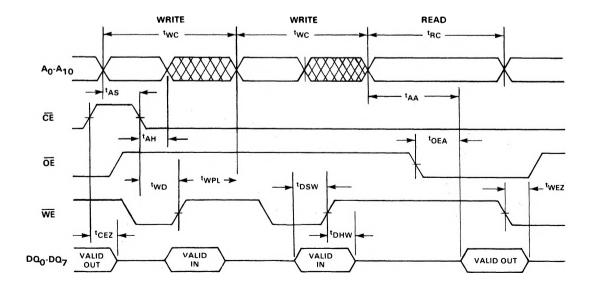

## TIMING DIAGRAM Figure 4

TIMING DIAGRAM Figure 5

The MK4801A features a fast  $\overline{CE}$  (50% of Address Access) function to permit memory expansion without impacting system access time. A fast  $\overline{OE}$  (50% of access time) is included to permit data interleaving for enhanced system performance.

The MK4801A is pin compatible with Mostek's BYTEWYDE™ memory family of RAMs, ROMs and EPROMs.

### OPERATION

#### **Read Mode**

The MK4801A is in the READ MODE whenever the Write Enable Control input (WE) is in the high state.

In the READ mode of operation, the MK4801A provides a fast address ripple-through access of data from 8 of 8192 locations in the static storage array. Thus, the unique address specified by the 10 Address Inputs (An) define which 1 of 1024 bytes of data is to be accessed.

A transition on any of the 10 address inputs will disable the 8 Data Output Drivers after  $t_{AZ}$ . Valid Data will be available to the 8 Data Output Drivers within  $t_{AA}$  after the last address input signal is stable, providing that the CE and OE access times are satisfied. If CE or OE access times are not met, data access will be measured from the limiting parameter

$(t_{CEA} \text{ or } t_{OEA})$  rather than the address. The state of the 8 data I/O signals is controlled by the Chip Enable (CE) and Output Enable (OE) control signals.

#### Write Mode

The MK4801A is in the Write Mode whenever the Write Enable ( $\overline{WE}$ ) and Chip Enable ( $\overline{CE}$ ) control inputs are in the low state.

The WRITE cycle is initiated by the WE pulse going low provided that CE is also low. The leading edge of the WE pulse is used to latch the status of the address bus.

NOTE: In a write cycle the latter occurring edge of either  $\overline{WE}$  or  $\overline{CE}$  will determine the start of the write cycle. Therefore,  $t_{AS'}, t_{WD}$  and  $t_{AH}$  are referenced to the latter occurring edge of  $\overline{CE}$  or  $\overline{WE}$ . Addresses are latched at this time. All write cycles whether initiated by  $\overline{CE}$  or  $\overline{WE}$  must be terminated by the rising edge of  $\overline{WE}$ . If the output bus has been enabled ( $\overline{CE}$  and  $\overline{OE}$  low) then  $\overline{WE}$  will cause the output to go to the high Z state in  $t_{WE7}$ .

Data In must be valid  $t_{DSW}$  prior to the low to high transition of  $\overline{WE}$ . The Data In lines must remain stable for  $t_{DHW}$  after  $\overline{WE}$  goes inactive. The write control of the MK4801A disables the data out buffers during the write cycle; however  $\overline{OE}$  should be used to disable the data out buffers to prevent bus contention between the input data and data that would be output upon completion of the write cycle.