SGS-THOMSON MICROELECTRONICS

# VERY HIGH-SPEED CMOS CLOCKED FIFO

PRELIMINARY DATA

## 1024 x 5 ORGANIZATION

## VERY HIGH PERFORMANCE

| Part No. | Cycle Time | Cycle<br>Frequency | Access<br>Time |

|----------|------------|--------------------|----------------|

| 4505-25  | 25 ns      | 40 MHz             | 15 ns          |

| 4505-33  | 33 ns      | 30 MHz             | 20 ns          |

| 4505-50  | 50 ns      | 20 MHz             | 25 ns          |

- RISING EDGE TRIGGERED CLOCK INPUTS

- SUPPORTS FREE-RUNNING 40% TO 60% DUTY CYCLE CLOCK INPUTS

- SEPARATE READ AND WRITE ENABLE INPUTS

- BIPORT<sup>™</sup> RAM ARCHITECTURE ALLOWS FUL-LY ASYNCHRONOUS AND SIMULTANEOUS READ/WRITE OPERATION

- CASCADABLE TO ANY DEPTH WITH NO AD-DITIONAL LOGIC

- WIDTH EXPANDABLE TO MORE THAN 40 BITS WITH NO ADDITIONAL LOGIC

- HALF FULL STATUS FLAG

- FULL AND EMPTY FLAGS, ALMOST FULL, ALMOST EMPTY, INPUT READY, OUTPUT VALID STATUS FLAGS (4505M)

- FULLY TTL COMPATIBLE

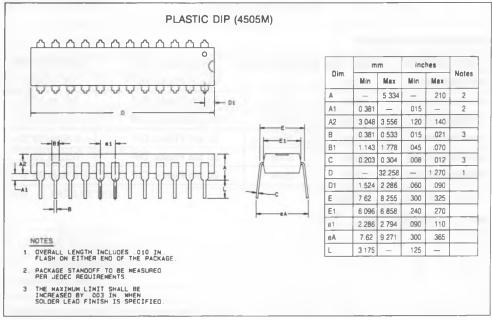

- 300 MIL PLASTIC DIP

#### **PIN NAMES**

| D <sub>0</sub> - D <sub>4</sub>   | - Data Input           |

|-----------------------------------|------------------------|

| $Q_0 - Q_4$                       | - Data Output          |

| CK <sub>W</sub> , CK <sub>R</sub> | - Write and Read Clock |

| WE <sub>1</sub>                   | - Write Enable Input 1 |

| RE <sub>1</sub>                   | - Read Enable Input 1  |

| RS                                | - Reset (Active Low)   |

| HF                                | - Half Full Flag       |

| V <sub>CC</sub> , V <sub>SS</sub> | - +5 Volt, Ground      |

Supersedes publication for January 1988.

| D,  | 1 [  |         | 24   | Var | ο,              | 1 [   |         | 20   | Vec |

|-----|------|---------|------|-----|-----------------|-------|---------|------|-----|

| D,  |      |         | 23   |     | 0,              | 2 [   |         |      | CK. |

| -,  |      |         |      | WE, | -3<br>D,        | 3 [   |         | ] 18 | WE, |

| 0,  |      |         |      | FF  | -2<br>D,        | 4 [   |         | ] 17 | WE, |

| 0,  | s 🗆  |         | 20   | DR  | D               | s□    | MK45055 | 16   | HF  |

| AE  | 6 🗆  | MK4505M | ] 19 | HF  | AS              | 6 [   |         | 3 15 | ۵,  |

| RS  | 7 [  |         | ] 18 | AF  | RE,             | 7 [   |         | 1_   | α,  |

| av  | e C  |         | 17   | ۵,  | AE,             | a C   |         | ] 13 | ٥,  |

| EF  | 9 [  |         | 3 16 | ۵,  | CK.             | 9 []  |         | ] 12 | ۵,  |

| AE, | 10   |         | 15   | ۵,  | V <sub>SS</sub> | 10 [] |         | ] 11 | ٩,  |

| CK. | 11 - |         | 14   | ۵,  | 33              |       |         | 1    | 0   |

|     | 12   |         | ] 13 | ۵,  |                 |       |         |      |     |

| (4505M (                           | (4505M Only)                                                                                                                    |  |  |  |  |  |  |  |  |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| FF, EF<br>AF, AE<br>DR, QV         | <ul> <li>Full and Empty Flag (Active Low)</li> <li>Almost Full, Almost Empty Flag</li> <li>Input Ready, Output Valid</li> </ul> |  |  |  |  |  |  |  |  |

| (45055 0                           | Only)                                                                                                                           |  |  |  |  |  |  |  |  |

| WE <sub>2</sub><br>RE <sub>2</sub> | <ul> <li>Write Enable Input 2</li> <li>Read Enable Input 2 (Rising Edge<br/>Triggered 3 State Control)</li> </ul>               |  |  |  |  |  |  |  |  |

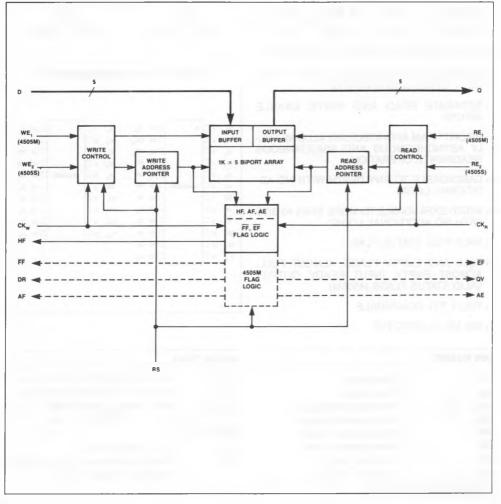

## DESCRIPTION

The MK4505 is a Very High Speed 1K x 5 Clocked FIFO memory. It achieves its high performance through the use of a pipelined architecture, a  $1.2\mu$  full CMOS, single poly, double level metal process, and a memory array constructed using SGS-THOMSON's 8 transistor BiPORT memory cell.

The device is designed for use in applications where data is moving through a system on a square wave clock; applications such as digitized video and audio, image processing, A-to-D and D-to-A conversions, high speed data links, Radar return sampling or data tracing.

#### FIGURE 2. BLOCK DIAGRAM MK4505M/4505S

The device is available in two versions; a Master, the MK4505M, and a Slave, the MK4505S. The Master provides all of the control signals necessary for reliable, full speed, fully asynchronous width expansion and/or depth expansion. The Master also provides a full compliment of status flags, including Output Valid, Empty, Almost Empty, Half Full, Almost Full, Full, and Input Ready. The Master cannot be written while Full or read while Empty. The Slave, in contrast, can be forced to write and/or read continuously regardless of device status; a feature useful in triggered data acquisitions, or for retransmit (repeat reading) applications.

| CKw | PR | ESEN | T ST/ | ITE | NEXT      | NEXT STATE |    |            |  |

|-----|----|------|-------|-----|-----------|------------|----|------------|--|

|     | RS | WE1  | FF    | DR  | OPERATION | FF         | DR | D          |  |

| Х   | 0  | X    | х     | X   | Reset     | 1          | 1  | Don't Care |  |

| 1   | 1  | 0    | 0     | 0   | No-Op     | 2          | ?  | Don't Care |  |

| Ť   | 1  | 0    | 1     | 1   | No Op     | 1          | 1  | Don't Care |  |

| 1   | 1  | 1    | 0     | 0   | No Op     | ?          | 2  | Don't Care |  |

| †   | 1  | 1    | 1     | 1   | Write     | ?          | ?  | Data In    |  |

### 4505M (MASTER) WRITE TRUTH TABLE

? = The "Next State" logic level is unknown due to the possible occurrence of a read operation.

#### 4505M (MASTER) READ TRUTH TABLE

|     | PR | ESEN            | T ST/ | TE | NEXT      | NEXT STATE |    |            |  |

|-----|----|-----------------|-------|----|-----------|------------|----|------------|--|

| CKR | RS | RE <sub>1</sub> | EF    | ۵۷ | OPERATION | EF         | av | Q          |  |

| Х   | 0  | X               | х     | X  | Reset     | 0          | 0  | Hi Z       |  |

| t   | 1  | 0               | 0     | 0  | Inhibit   | 7          | 0  | Hi Z       |  |

| Ť   | 1  | 0               | 0     | 1  | Inhibit   | 2          | 0  | Hi Z       |  |

| t   | 1  | 0               | 1     | 0  | Hold      | 1          | 1  | Previous O |  |

| t   | 1  | 0               | 1     | 1  | Hold      | 1          | 1  | Previous Q |  |

| 1   | 1  | 1               | 0     | 0  | Inhibit   | ?          | 0  | Hi Z       |  |

| 1   | 1  | 1               | 0     | 1  | Inhibit   | 2          | 0  | Hi Z       |  |

| Ť   | 1  | 1               | 1     | 0  | Read      | 2          | 1  | Data Out   |  |

| Ť   | 1  | 1               | 1     | 1  | Read      | ?          | 1  | Data Out   |  |

? = The "Next State" logic level is unknown due to the possible occurrence of a write operation

|     | PRE   | SENT S |                 | NEXT      | NEXT STATE |  |  |

|-----|-------|--------|-----------------|-----------|------------|--|--|

| CKW | RS WE |        | WE <sub>2</sub> | OPERATION | D          |  |  |

| Х   | 0     | X      | х               | Reset     | Don't Care |  |  |

| Ť   | 1     | 0      | 0               | No Op     | Don't Care |  |  |

| 1   | 1     | 0      | 1               | No-Op     | Don't Care |  |  |

| 1   | 1     | 1      | 0               | No Op     | Don't Care |  |  |

| Ť   | 1     | 1      | 1               | Write     | Data In    |  |  |

#### 4505S (SLAVE) WRITE TRUTH TABLE

#### 4505S (SLAVE) READ TRUTH TABLE

|     | PRESENT STATE |                 |                 | NEXT      | NEXT STATE |  |  |

|-----|---------------|-----------------|-----------------|-----------|------------|--|--|

| CKR | RS            | RE <sub>1</sub> | RE <sub>2</sub> | OPERATION | ۵          |  |  |

| х   | 0             | x               | X               | Reset     | Hi Z       |  |  |

| Ť   | 1             | 0               | 0               | Inhibit   | HiZ        |  |  |

| Ť   | 1             | 0               | 1               | Hold      | Previous Q |  |  |

| 1   | 1             | 1               | 0               | Inhibit   | Hi Z       |  |  |

| Ť   | 1             | 1               | 1               | Read      | Data Out   |  |  |

X = Don't care

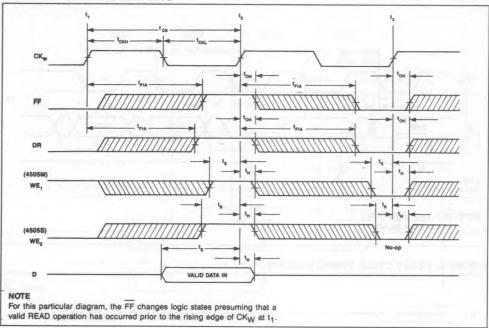

#### WRITE OPERATIONS

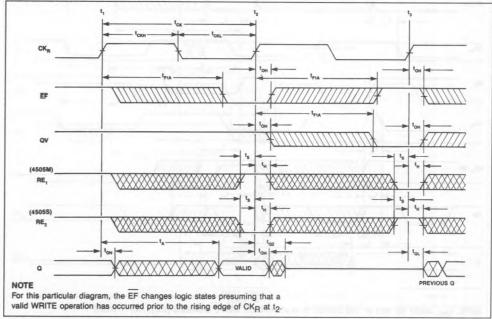

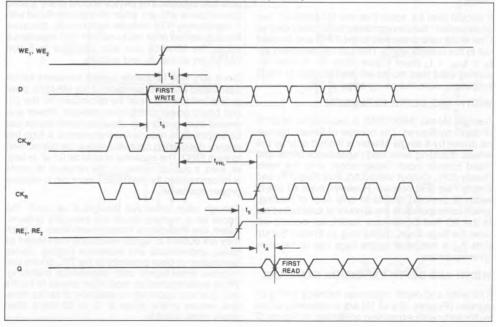

The device will perform a Write on the next rising edge of the Write Clock (CK<sub>W</sub>) whenever (see figure 3):

- (4505S) WE<sub>1</sub> and WE<sub>2</sub> are high at the rising edge of the clock.

- (4505M) WE<sub>1</sub> and FF are high at the rising edge of the clock.

Because the device only re-evaluates and updates the Full Flag (FF) on the rising edge of  $CK_W$ , the appearance of an active Full Flag at valid flag access time,  $t_{F1A}$ , assures the user that the next rising edge of  $CK_W$  will generate a NO-OP condition.

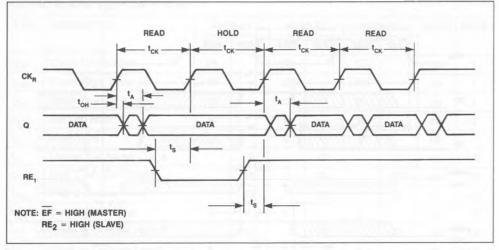

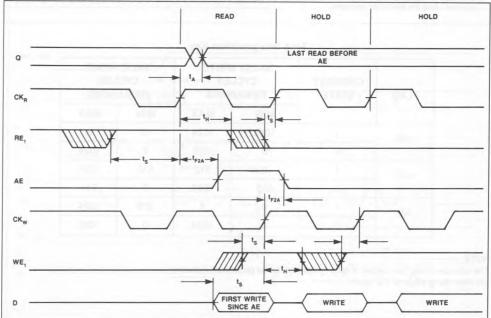

### **READ AND HOLD OPERATIONS**

The device will perform a Read on the next rising edge of the Read Clock ( $CK_R$ ) whenever (see figure 4):

- (4505S)  $RE_1$  and  $RE_2$  are high at the rising edge of the clock.

- (4505M)  $RE_1$  and  $\overline{EF}$  are high at the rising edge of the clock.

Because the device only re-evaluates and updates the Empty Flag (EF) on the rising edge of CK<sub>R</sub>, the appearance of an active Empty Flag at valid flag access time, t<sub>F1A</sub>, assures the user that the next rising edge of CK<sub>R</sub> will generate an inhibit condition. All Q outputs will be High Z at t<sub>QZ</sub> from the rising edge of CK<sub>R</sub>.

The device will perform a Hold Cycle (hold over previous data) if  $RE_1$  is low at the rising edge of the clock (CK<sub>R</sub>). If EF (4505M) or  $RE_2$  (4505S) is low at the rising edge of the clock, then the outputs will go to High-Z.

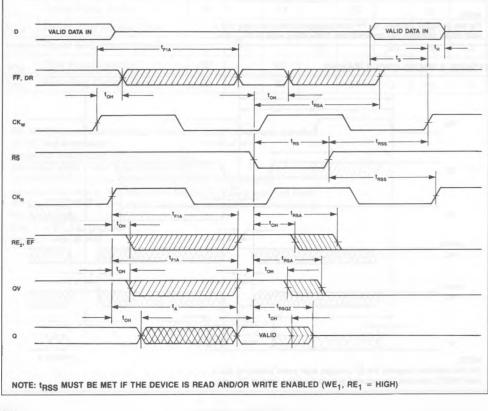

#### RESET

RS is an asynchronous master reset input. A Reset is required after power-up, before first write. Reset commences on the falling edge of RS irrespective of the state of any other input or output. The user is required to observe Reset Set Up Time ( $t_{RSS}$ ) only if the device is enabled (see Figure 6). The  $t_{RSS}$  specification is a don't care if the device remains disabled (WE<sub>1</sub> = RE<sub>1</sub> = LOW). All status flag outputs will be valid  $t_{RSA}$  from the falling edge of RS, and all Q data outputs will be high impedance  $t_{RSQZ}$  from the same falling edge.

After Reset, if no valid Read operations have been performed since Reset, the "previous data" that will be output when executing the first Hold cycle will be all zeros (see Figure 7.)

# AC ELECTRICAL CHARACTERISTICS

$(T_A = 0^{\circ} \text{ to } 70^{\circ}\text{C}, V_{CC} = 5.0 \pm 10\%)$

| SYM               | PARAMETER                         | 450 | 5-25 | 450 | 5-33 | 450 | 5-50 | UNITS | NOTE |

|-------------------|-----------------------------------|-----|------|-----|------|-----|------|-------|------|

|                   |                                   | MIN | MAX  | MIN | MAX  | MIN | MAX  |       |      |

| t <sub>CK</sub>   | Clock Cycle Time                  | 25  |      | 33  |      | 50  |      | ns    | 1    |

| t <sub>CKH</sub>  | Clock High Time                   | 10  |      | 13  |      | 20  |      | ns    | 1    |

| t <sub>CKL</sub>  | Clock Low Time                    | 10  |      | 13  |      | 20  |      | ns    | 1    |

| ts                | Set Up Time                       | 10  |      | 13  |      | 16  |      | ns    | 1    |

| t <sub>H</sub>    | Hold Time                         | 0   |      | 0   |      | 0   |      | ns    |      |

| t <sub>A</sub>    | Output (Q) Access Time            |     | 15   |     | 20   |     | 25   | ns    | 1,2  |

| t <sub>F1A</sub>  | Flag 1 Access Time <sup>(7)</sup> |     | 15   |     | 20   |     | 25   | ns    | 1,2  |

| t <sub>F2A</sub>  | Flag 2 Access Time <sup>(8)</sup> |     | 20   |     | 25   |     | 30   | ns    | 1,2  |

| t <sub>OH</sub>   | Output Hold Time                  | 5   |      | 5   |      | 5   |      | ns    | 1,2  |

| toz               | Clock to Outputs High-Z           |     | 15   |     | 20   |     | 25   | ns    | 1,3  |

| toL               | Clock to Outputs Low-Z            | 5   |      | 5   |      | 5   |      | ns    | 1,3  |

| t <sub>RSS</sub>  | Reset Set Up Time                 | 12  |      | 16  |      | 25  |      | ns    | 1,4  |

| t <sub>RS</sub>   | Reset Pulse Width                 | 25  |      | 33  |      | 50  |      | ns    |      |

| t <sub>RSA</sub>  | Reset Flag Access Time            |     | 50   |     | 66   |     | 100  | ns    | 1,3  |

| t <sub>RSQZ</sub> | Reset to Outputs High-Z           |     | 25   |     | 33   |     | 50   | ns    | 1,3  |

| tFRL              | First Read Latency                | 50  | -    | 66  |      | 100 |      | ns    | 1,5  |

| t <sub>FFL</sub>  | First Flag Cycle Latency          | 25  |      | 33  |      | 50  |      | ns    | 1,6  |

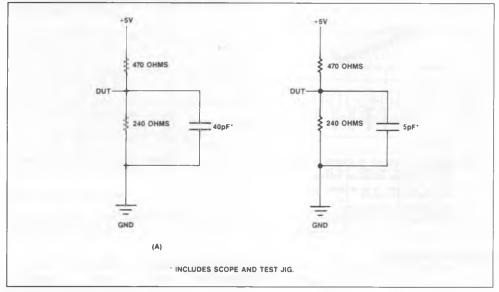

All AC Electrical Characteristics measured under conditions specified in "AC Test Conditions".

- 2. Measured w/40pf Output Load (Figure 15A).

- 3. Measured w/5pf Output Load (Figure 15B).

- 4. Need not be met unless device is Read and/or Write Enabled.

- 5. Minimum first Write to first Read delay required to assure valid first Read.

- Minimum first Write to first Read Clock delay required to assure clearing the Empty Flag.

- 7. Flag 1 = EF, FF, QV, DR.

- 8. Flag 2 = AE, AF, HF.

# FIGURE 3. WRITE CYCLE TIMING

# FIGURE 4. READ CYCLE TIMING

# FIGURE 5. HOLD CYCLE TIMING

# FIGURE 7. FIRST HOLD AFTER RESET

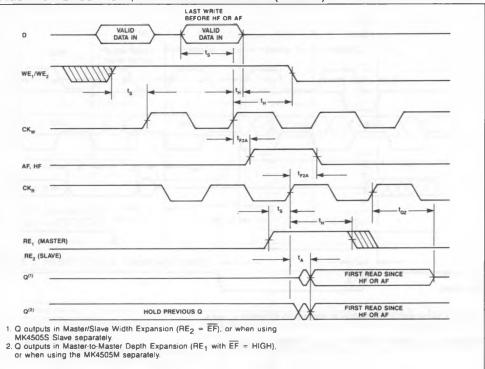

# FIGURE 8. ALMOST EMPTY FLAG TIMING (4505M)

# FIGURE 9. ALMOST FULL, HALF FULL FLAG TIMING (4505M/S)

## **Flag Interpretation Key**

| FLAG | CURRENT<br>STATE | VALID<br>CYCI<br>REMA | LES  | CYC  | READ<br>LES |

|------|------------------|-----------------------|------|------|-------------|

|      |                  | MIN                   | MAX  | MIN  | MAX         |

| AE   | 1                | 1016                  | 1024 | 0    | 8           |

|      | 0                | 0                     | 1015 | 9    | 1024        |

| HF   | 1                | 0                     | 512  | 512  | 1024        |

|      | 0                | 513                   | 1024 | 0    | 511         |

| AF   | 1                | 0                     | 8    | 1016 | 1024        |

|      | 0                | 9                     | 1024 | 0    | 1015        |

## NOTE

The table describes the number of valid cycles that can be performed, including the next rising edge of the clock.

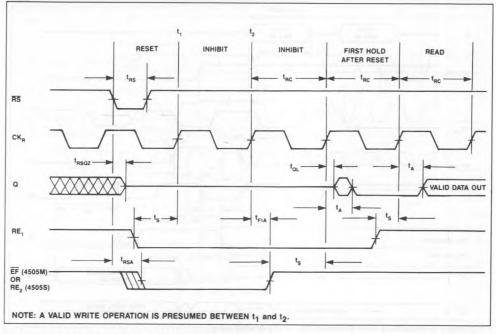

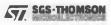

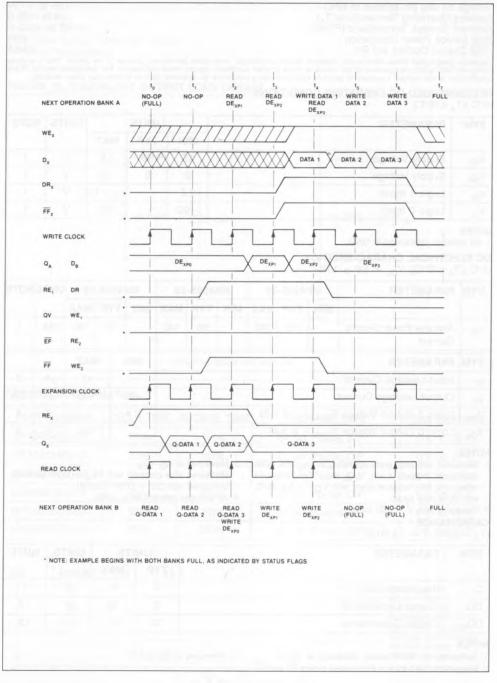

FIGURE 10. SIMULTANEOUS WRITE/READ TIMING (4505M)

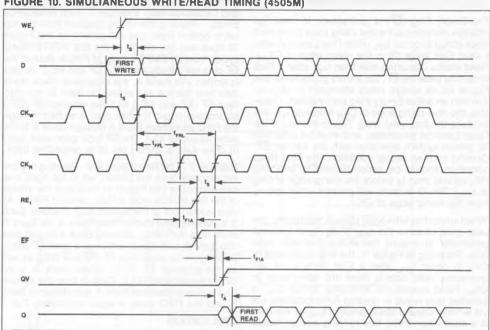

FIGURE 11. SIMULTANEOUS WRITE/READ TIMING (4505S)

### SIMULTANEOUS WRITE/READ TIMING

The Empty Flag (EF) is guaranteed to clear (go HIGH)in response to the first rising edge of the read clock (CK<sub>R</sub>) to occur t<sub>FFL</sub> (First Flag Latency) after a valid First Write (from the rising edge of CKw). Read clocks occurring less than t<sub>FFL</sub> after a First Write may clear the EF, but are not guaranteed (see Figure 10). As always, reads attempted in conjunction with an active Empty Flag are inhibited. Therefore, the next rising edge of CK<sub>B</sub> following t<sub>FFL</sub> will produce the first valid read. This is the tFRI (First Read Latency) parameter, and must be observed for proper system operation with the latched EF. Coming from an empty condition, the First Read operation should be accomplished by enabling RE<sub>1</sub> no less than t<sub>S</sub> before the rising edge of CK<sub>R</sub> at tFBL. The Q outputs will present valid data ta from the rising edge of CK<sub>B</sub>.

When using the MK4505S (Slave) separately, the user must observe the  $t_{FRL}$  (First Read Latency) parameter to ensure first-write-to-first-read valid data. Referring to Figure 11, the first rising edge of CK<sub>R</sub> to occur  $t_{FRL}$  after a First Write clock will guarantee valid data  $t_A$  from the rising edge of CK<sub>R</sub>. Read operations attempted before  $t_{FRL}$  is satisfied may result in reading RAM locations not yet written. Careful observance of  $t_{FRL}$  by the user is a must when using free running asynchronous read/write clocks on the MK4505S; there is no automatic read and write protection circuitry in the Slave.

It should also be noted that the MK4505M/S has an expected "fall-through delay time" described as First Write data presented to the FIFO and clocked out to the outside world. This can be calculated as:  $t_{\rm S} + t_{\rm FRL} + t_{\rm A}$  (from Figure 10 or 11). Further occurring valid read clocks will present data to the Q outputs  $t_{\rm A}$  from the rising edge of CK<sub>R</sub>.

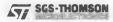

#### WIDTH AND DEPTH EXPANSION

A single Master (MK4505M) is required for each 1k of depth configured. The number of Slaves that can be driven by a single Master is limited only by the effects of adding extra load capacitance (Write and Read Enable Input Capacitance) onto the Input Ready (DR), Output Valid (QV), Full Flag (FF) and Empty Flag (EF) outputs. However, even 40 bits of width (8 devices) results in only 40pf of loading, which corresponds to the amount of load called out in the AC Test Conditions. Additional loading will slow the flags down, but as long as Enable Set Up time ( $t_S$ ) is met, slowing the flags has no negative consequences.

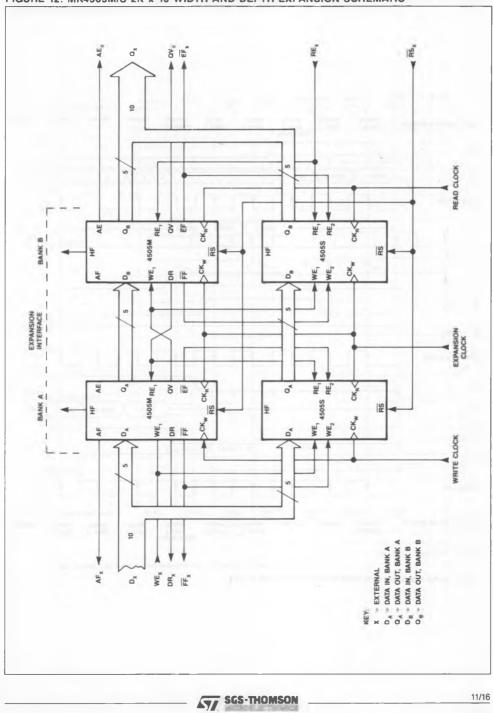

#### WIDTH AND DEPTH EXPANSION EXAMPLES

The width and depth expansion interface timing diagrams (Figures 13 and 14) are in reference to the width and depth expansion schematic in Figure 12 (For simplicity all clocks have the same frequency and transistion rate). Example 1 - First Write Since Empty - Reading the timing diagram from the top left to bottom right, one can determine that Figure 13 illustrates the effects of the first WRITE/READ cycles from an EMPTY array of FIFOs. Both of the EF pins are initially low (EF<sub>x</sub>, EF and RE<sub>2</sub>). As data is written into Bank A, the expansion clock reads data from Bank A and writes it to Bank B, the interface EF (EF and RE<sub>2</sub>) and the external EF (EF<sub>x</sub>) go inactive (logic 1) while data is shifted through the FIFO array from Bank A through Bank B to the external output (Q<sub>x</sub>). The EF logic goes valid (logic 0) once data is shifted out of its respective bank.

Example 2 - First Read Since Full - Reading the timing diagram from the bottom left to top right, one can determine that Figure 14 illustrates the effects of the first READs from a FULL array of FIFOs. As data is read out of the system ( $Q_x$ ), it allows Bank B to receive data shifted from Bank A. As Bank B shifts data out via  $Q_x$ , allowing Bank A to shift data into Bank B, both banks will show a reset FF status (logic 1) on the expansion FF (FF and WE<sub>2</sub>) as well as the external FF (FF<sub>x</sub>). When Bank A is no longer considered FULL, Data In from the system ( $D_x$ ) is now written into Bank A and shifted to Bank B until the FIFO array is again completely Full.

### APPLICATION

The MK4505 operates from a 5.0 volt supply. It is compatible with all standard TTL families on all inputs and outputs. The device should share a solid ground plane with any other devices interfaced with it, particularly TTL devices. Additionally, because the outputs can drive rail-to-rail into high impedance loads, the MK4505 can also interface to 5 volt CMOS on all inputs and outputs.

Since very high frequency current transients will be associated with the operation of the MK4505, power line inductance must be minimized on the circuit board power distribution network. Power and ground trace gridding or separate power planes can be employed to reduce line inductance. A high frequency decoupling capacitor should be placed next to each FIFO. The capacitor should be 0.1  $\mu$ F or larger. Also, a pull-up resistor in the range of 1K ohms is recommended for the RESET input pin to improve proper operation.

Though often times not thought of as such, the traces on a memory board are basically unterminated, low impedance transmission lines. As such they are subject to signal reflections manifested as noise, undershoots and excessive ringing. Series termination in close proximity to the TTL drivers can improve driver/signal path impedance matching. While experimentation most often proves to be the only practical approach to selection of series resistors, values in the range of 10 to 33 ohms often prove most suitable.

FIGURE 12. MK4505M/S 2K x 10 WIDTH AND DEPTH EXPANSION SCHEMATIC

#### FIGURE 13. EXAMPLE 1 - WIDTH AND DEPTH EXPANSION INTERFACE TIMING

## ABSOLUTE MAXIMUM RATINGS\*

| Voltage on any pin relative to GND                                                                        | 1.0V to +7.0V           |

|-----------------------------------------------------------------------------------------------------------|-------------------------|

| Ambient Operating Temperature (T <sub>A</sub> )                                                           | 0 to +70 C              |

| Ambient Storage Temperature (Plastic)                                                                     | 55 to +125 C            |

| Total Device Power Dissipation                                                                            | 1 Watt                  |

| RMS Output Current per Pin                                                                                |                         |

| "Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the de | avice. This is a stress |

"Stresses greater than those listed under "Absolute Maximum Hatings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

# **RECOMMENDED DC OPERATING CONDITIONS** $(0^{\circ}C \le T_{A} \le 70^{\circ}C)$

| SYM             | PARAMETER      |      |     | UNITS                | NOTE |   |

|-----------------|----------------|------|-----|----------------------|------|---|

|                 |                | MIN  | ΤΥΡ | MAX                  |      |   |

| V <sub>cc</sub> | Supply Voltage | 4.5  | 5.0 | 5.5                  | V    | 1 |

| V <sub>SS</sub> | Supply Voltage | 0    | 0   | 0                    | V    | 1 |

| VIH             | Logic 1 Input  | 2.2  |     | V <sub>CC</sub> +1.0 | V    | 1 |

| V <sub>IL</sub> | Logic 0 Input  | -0.3 |     | 0.8                  | V    | 1 |

#### NOTES

1. All voltages referenced to GND.

## DC ELECTRICAL CHARACTERISTICS

$(0^{\circ}C \le T_A \le 70^{\circ}C), V_{CC} = 5.0 \pm 10\%)$

| SYM             | PARAMETER                                         | MK4505-25 |     |     | MK4505-33 |     |     | MK4505-50 |     |     | UNITS | NOTE |

|-----------------|---------------------------------------------------|-----------|-----|-----|-----------|-----|-----|-----------|-----|-----|-------|------|

|                 |                                                   | MIN       | ТҮР | MAX | MIN       | ΤΥΡ | MAX | MIN       | ΤΥΡ | MAX |       |      |

| I <sub>cc</sub> | Average Power Supply<br>Current                   |           | 115 | 140 |           | 95  | 140 |           | 75  | 140 | mA    | 1    |

| SYM             | PARAMETER                                         |           |     |     |           |     | MIN | 1 1       | XAN |     |       |      |

| I <sub>IL</sub> | Input Leakage Current                             |           |     |     |           | -1  |     | +1        | μA  | 2   |       |      |

| IOL             | Output Leakage Current                            |           |     |     |           | -10 | )   | +10       | μA  | 2,3 |       |      |

| V <sub>OH</sub> | Logic 1 Output Voltage (I <sub>OUT</sub> = -4 mA) |           |     |     |           | 2.4 |     |           | V   | 4   |       |      |

| V <sub>OL</sub> | Logic 0 Output Voltage (I <sub>OUT</sub> = 8 mA)  |           |     |     |           |     |     | 0.4       | V   | 4   |       |      |

## NOTES

1. Measured with both ports operating at t<sub>CK</sub> Min, 50% duty cycle, outputs open, V<sub>CC</sub> max. Typical values reflect t<sub>CK</sub> Min, outputs open, with V<sub>CC</sub> = 5.0, 25°C, with 50% duty cycle.

2. Measured with V = 0.0V to V<sub>CC</sub>.

#### CAPACITANCE

$(T_A = 25^{\circ}C, f = 1.0 \text{ MHz})$

| SYM             | PARAMETER          | LIMITS |     |    | NOTE |

|-----------------|--------------------|--------|-----|----|------|

|                 |                    | ТҮР    | MAX |    |      |

| CI              | Input Capacitance  | 4      | 5   | pf | 1    |

| CO1             | Output Capacitance | 8      | 10  | pf | 1,2  |

| CO <sub>2</sub> | Output Capacitance | 12     | 15  | pf | 1,3  |

#### NOTES

1. Sampled, not 100% tested. Measured at 1MHz.

2. Measured at all data and flag outputs except EF and FF

3. Measured at EF and FF.

3. Measured at Q0 - Q4.

Measured after clocking with RE<sub>2</sub> = LOW (4505S).

Measured with QV = LOW (4505M).

4. All voltages referenced to GND.

## **AC TEST CONDITIONS**

| Input Levels                      | Volts |

|-----------------------------------|-------|

| Transition Times                  | .5 ns |

| Input and Output Reference Levels | Volts |

| Ambient Temperature 0 to          | 70 C  |

| V <sub>CC</sub>                   |       |

# FIGURE 15. EQUIVALENT OUTPUT LOAD CIRCUIT

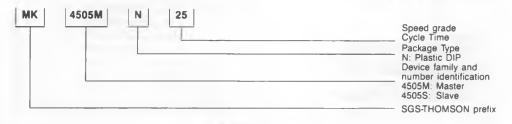

# **ORDERING INFORMATION**

| PART NUMBER   | CYCLE TIME | ACCESS TIME | PACKAGE TYPE       | TEMPERATURE |

|---------------|------------|-------------|--------------------|-------------|

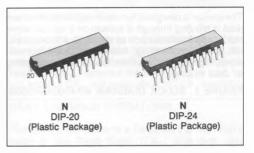

| MK4505M(N)-25 | 25ns       | 15ns        | 24 pin Plastic DIP | 0°C to 70°C |

| MK4505M(N)-33 | 33ns       | 20ns        | 24 pin Plastic DIP | 0°C to 70°C |

| MK4505M(N)-50 | 50ns       | 25ns        | 24 pin Plastic DIP | 0°C to 70°C |

| MK4505S(N)-25 | 25ns       | 15ns        | 20 pin Plastic DIP | 0°C to 70°C |

| MK4505S(N)-33 | 33ns       | 20ns        | 20 pin Plastic DIP | 0°C to 70°C |

| MK4505S(N)-50 | 50ns       | 25ns        | 20 pin Plastic DIP | 0°C to 70°C |

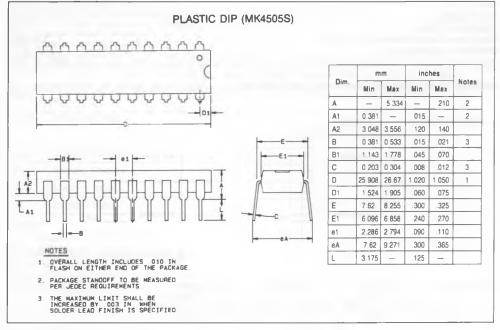

## 20 PIN "N" PACKAGE

## 24 PIN "N" PACKAGE