### FEATURES

- The Z80 is fully software compatible with the 8080A CPU. The 78 instructions of the 8080A are a subset of the Z80's 158 instructions.

- The extensive instruction set includes relative and indexed addressing, block searches and block transfers, word, byte, and bit data operations.

- □ The architecture provides duplicate sets of general purpose Flag and Index registers to allow background/ foreground programming and easier single level interrupt processing and to facilitate array and table processing.

- On chip Dynamic memory refresh counter

- □ Single +5 V supply

- Single phase system clock

- Vectored interrupt handling system. This system allows for a Daisy Chain arrangement of a priority interrupt scheme with little if any additional hardware.

#### INTRODUCTION

The Mostek Z80 family of components is a significant advancement in the state-of-the-art of microcomputers. These components can be configured with any type of standard semiconductor memory to generate computer systems with an extremely wide range of capabilities. For example, as few as two LSI circuits and three standard TTL MSI packages can be combined to form a simple controller. With additional memory and I/O devices, a computer can be constructed with capabilities that only a minicomputer could previously deliver. This wide range of computational power allows standard modules to be constructed by a user that can satisfy the requirements of an extremely wide range of applications.

The Z80 Central Processing Unit is the heart of the Z80 family. It provides arithmetic and bus control to operate with the bussed peripheral controllers such as the Parallel I/O, Serial I/O, Counter/Timer, and Direct Memory Access Circuits. The Z80-CPU utilizes N channel silicon gate depletion load technology and is packaged in a 40 pin DIP.

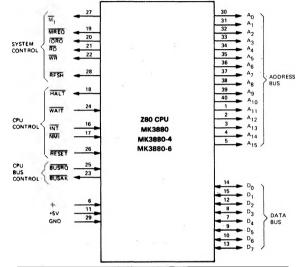

# Z80 PIN CONFIGURATION Figure 1

#### **Z80-CPU PIN DESCRIPTION**

The Z80-CPU is packaged in an industry-standard 40 pin Dual In-Line Package. The I/O pins are shown in Figure 1, and the function of each is described below.

- A0-A15 Tri-state output, active high. Ao-A15 constitute a 16-bit address bus. The (Address Bus) address bus provides the address for memory (up to 64K bytes), data exchanges, and for I/O device data exchanges. I/O addressing uses the 8 lower address bits to allow the user to select up to 256 input or 256 output ports directly. An is the least significant address bit. During refresh time, the lower 7 bits contain a valid refresh address.  $D_0 - D_7$ Tri-state input/output, active high. Do-(Data Bus) D7 constitute an 8-bit bidirectional data

- bus. The data bus is used for data exchanges with memory and I/O devices.

| M <sub>1</sub><br>(Machine Cycle<br>one) | Output, active low, $\overline{M_1}$ indicates that<br>the current machine cycle is the OP<br>code fetch cycle of an instruction<br>execution. Note that during execution of<br>2-byte op-codes, $\overline{M_1}$ is generated as<br>each op code byte is fetched. These two<br>byte op-codes always begin with CBH,<br>DDH, EDH, or FDH. $\overline{M_1}$ also occurs with<br>$\overline{IORQ}$ to indicate an interrupt acknow-<br>ledge cycle. | WAIT*<br>(Wait)        | Output, active low. WAIT indicates to<br>the Z80-CPU that the addressed<br>memory or I/O devices are not ready for<br>a data transfer. The CPU continues to<br>enter wait states for as long as this<br>signal is active. This signal allows<br>memory or I/O devices of any speed to<br>be synchronized to the CPU.                           |

|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MREQ<br>(Memory Request)                 | Tri-state output, active low. The mem-<br>ory request signal indicates that the<br>address bus holds a valid address for a<br>memory read or memory write opera-<br>tion.                                                                                                                                                                                                                                                                         | (Interrupt<br>Request) | signal is generated by I/O devices. A re-<br>quest will be honored at the end of the<br>current instruction if the internal<br>software controlled interrupt enable<br>flip-flop (IFF) is enabled and if the<br>BUSRO signal is not active. When the<br>CPU accepts the interrupt, an acknow-                                                  |

| IORQ<br>(Input/Output<br>Request)        | Tri-state output, active low. The $\overline{IORQ}$ signal indicates that the lower half of the address bus holds a valid I/O address for an I/O read or write operation. An $\overline{IORQ}$ signal is also generated with an $\overline{M_1}$ signal when an interrupt is being acknowledged to indicate that an interrupt response                                                                                                            |                        | ledge signal ( $\overline{IORQ}$ during $M_1$ time) is<br>sent out at the beginning of the next<br>instruction cycle. The CPU can respond<br>to an interrupt in three different modes<br>that are described in detail in section 8<br>of the Technical Manual, which is<br>included in section IV of this data book.                           |

|                                          | Nuclear that an interrupt response vector can be placed on the data bus. Interrupt Acknowledge operations occur during $\overline{M_1}$ time while I/O operations never occur during $\overline{M_1}$ time.                                                                                                                                                                                                                                       | NMI                    | Input, negative edge triggered. The non<br>maskable interrupt request line has a<br>higher priority than INT and is always<br>recognized at the end of the current<br>instruction, independent of the status of                                                                                                                                |

| RD<br>(Memory Read)                      | Tri-state output, active low. $\overline{RD}$ indi-<br>cates that the CPU wants to read data<br>from memory or an I/O device. The<br>addressed I/O device or memory<br>should use this signal to gate data onto<br>the CPU data bus.                                                                                                                                                                                                              |                        | the interrupt enable flip-flop. $\overline{\text{NMI}}$ automatically forces the Z80-CPU to restart to location $OO66_{\text{H}}$ . The program counter is automatically saved in the external stack so that the user can return to the program that was interrupted. Note that continuous WAIT                                                |

| WR<br>(Memory Write)                     | Tri-state output, active low. WR indi-<br>cates that the CPU data bus holds valid<br>data to be stored in the addressed<br>memory or I/O device.                                                                                                                                                                                                                                                                                                  |                        | cycles can prevent the current instruc-<br>tion from ending, and that a BUSRQ will<br>override an NMI.                                                                                                                                                                                                                                         |

| RFSH<br>(Refresh)                        | Output, active low. RFSH indicates that<br>the lower 7 bits of the address bus<br>contain a refresh address for dynamic<br>memories and current $\overline{\text{MREO}}$ signal<br>should be used to do a refresh read to all<br>dynamic memories. A <sub>7</sub> is a logic zero<br>and the upper 8 bits of the Address Bus<br>contain the I Register.                                                                                           | RESET                  | Input, active low. RESET forces the<br>program counter to zero and initializes<br>the CPU. The CPU initialization will:<br>1) Disable the interrupt enable flip-flop<br>2) Set Register I = 00H<br>3) Set Register R = 00H<br>4) Set Interrupt Mode 0<br>During reset time, the address bus and                                                |

| HALT<br>(Halt state)                     | Output, active low. HALT indicates that<br>the CPU has executed a HALT software<br>instruction and is awaiting either a non<br>maskable or a maskable interrupt (with<br>the mask enabled) before operation can<br>resume. While halted, the CPU executes<br>NOP's to maintain memory refresh ac-<br>tivity.                                                                                                                                      | BUSRQ<br>(Bus Request) | data bus go to a high impedance state<br>and all control output signals go to the<br>inactive state. No refresh occurs.<br>Input, active low. The bus request signal<br>is used to request the CPU address bus,<br>data bus and tri-state output control<br>signals to go to a high impedance state<br>so that other devices can control buses |

to a high impedance state as soon as

the current CPU machine cycle is terminated.

BUSAK\* Output, active low. Bus acknowledge is used to indicate to the requesting device that the CPU address bus, data bus and tri-state control bus signals have been set to their high impedance state and the external device can now control these signals. \*While the Z80-CPU is in either a WAIT state or a Bus Acknowledge condition, Dynamic Memory Refresh will not occur.

For further details on this device, please consult the MK3880 Z80 CPU Technical Manual, included in Section IV.

### **ELECTRICAL SPECIFICATIONS**

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias                    | Specified Operating Range |

|-------------------------------------------|---------------------------|

| Storage Temperature                       | 65°C to +150°C            |

| Voltage on Any Pin with Respect to Ground | 0.3 V to +7V              |

| Power Dissipation                         | 1.5 W                     |

|                                           |                           |

All ac parameters assume a load capacitance of 50 pF max.

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# D.C. CHARACTERISTICS

$T_{A}$  = 0°C to 70°C,  $V_{CC}$  = 5 V  $\pm$  5% unless otherwise specified

| SYMBOL           | PARAMETER                                    | MIN               | ΤΥΡ | MAX                 | UNITS | TEST CONDITIONS                      |

|------------------|----------------------------------------------|-------------------|-----|---------------------|-------|--------------------------------------|

| V <sub>ILC</sub> | Clock Input Low Voltage                      | -0.3              |     | 0.8                 | v     |                                      |

| VIHC             | Clock Input High Voltage                     | V <sub>CC</sub> 6 |     | V <sub>CC</sub> +.3 | V     |                                      |

| V <sub>IL</sub>  | Input Low Voltage                            | -0.3              |     | 0.8                 | v     |                                      |

| VIH              | Input High Voltage                           | 2.0               |     | V <sub>cc</sub>     | v     |                                      |

| V <sub>OL</sub>  | Output Low Voltage                           |                   |     | 0.4                 | V     | I <sub>OL</sub> = 1.8 mA             |

| V <sub>OH</sub>  | Output High Voltage                          | 2.4               |     |                     | v     | I <sub>OH</sub> = -250 μA            |

| I <sub>cc</sub>  | Power Supply Current                         |                   |     | 150*                | mA    |                                      |

| l <sub>u</sub>   | Input Leakage Current                        |                   |     | ±10                 | μA    | $V_{IN} = 0$ to $V_{CC}$             |

| ILO              | Tri-State Output Leakage<br>Current in Float |                   |     | ±10                 | μΑ    | $V_{OUT} = 0.4 \text{ V to } V_{CC}$ |

\*200 mA for -4, -10 or -20 devices

# CAPACITANCE

$T_A = 25^{\circ}C$ , f = 1 MHz unmeasured pins returned to ground

| SYMBOL           | PARAMETER          | MAX | UNIT |

|------------------|--------------------|-----|------|

| CФ               | Clock Capacitance  | 35  | pF   |

| C <sub>IN</sub>  | Input Capacitance  | 5   | pF   |

| C <sub>OUT</sub> | Output Capacitance | 10  | pF   |

## MK3880-4, MK3880-6, MK3880-10 Z80-CPU

### AC CHARACTERISTICS

$T_A = 0^{\circ}C$  to 70°C,  $V_{CC} = +5 V \pm 5\%$ , Unless Otherwise Noted

|                   |                                   |                                                             | 3880 |           | 3880-4 |           | 3880-6  |           |

|-------------------|-----------------------------------|-------------------------------------------------------------|------|-----------|--------|-----------|---------|-----------|

| SIGNAL            | SYMBOL                            | MBOL PARAMETER                                              |      | MIN MAX   |        | MAX       | MIN MAX |           |

|                   |                                   |                                                             | (ns) | (ns)      | (ns)   | (ns)      | (ns)    | (ns)      |

|                   | t <sub>c</sub>                    | Clock Period                                                | 400  | [12]      | 250    | [12]      | 165     | [12]      |

|                   | -с<br>t <sub>w</sub> (ФН)         | Clock Pulse Width, Clock High                               | 180  | (D)       | 110    | (D)       | 65      | (D)       |

| Φ                 | t <sub>w</sub> (ΦL)               | Clock Pulse Width, Clock Low                                | 180  | 2000      | 110    | 2000      | 65      | 2000      |

|                   | t <sub>r,f</sub>                  | Clock Rise and Fall Time                                    |      | 30        |        | 30        |         | 20        |

|                   | t <sub>D(AD)</sub>                | Address Output Delay                                        |      | 145       |        | 110       |         | 90        |

|                   | t <sub>F(AD)</sub>                | Delay to Float                                              | 1    | 110       |        | 90        |         | 80        |

|                   | t <sub>acm</sub>                  | Address Stable Prior to MREQ (Memory Cycle)                 | [[1] |           | [13]   |           | [24]    |           |

| A <sub>0-15</sub> | t <sub>aci</sub>                  | Address Stable Prior to IORO, RD or WR<br>(I/O Cycle)       | [2]  |           | [14]   |           | [25]    |           |

|                   | t                                 | Address Stable From RD, WR, IORQ or MREQ                    | [3]  | 1         | [15]   |           | [26]    |           |

|                   | t <sub>ca</sub>                   | Address Stable From RD or WR During Float                   | [4]  |           | [16]   |           | [27]    |           |

|                   | t <sub>caf</sub>                  |                                                             |      |           |        |           | [27]    |           |

|                   | t <sub>D(D)</sub>                 | Data Output Delay<br>Delay to Float During Write Cycle      |      | 230<br>90 |        | 150<br>90 |         | 130<br>80 |

|                   | t <sub>F(D)</sub>                 | Data Setup Time to Rising Edge of Clock During              | 50   | 90        | 35     | 90        | 30      |           |

|                   | t <sub>S</sub> ⊕(D)               | M1 Cycle                                                    | 50   |           | 35     |           | 30      |           |

| D <sub>0-7</sub>  | ts <del></del> ⊕(D)               | Data Setup Time to Falling Edge at Clock During<br>M2 to M5 | 60   |           | 50     |           | 40      |           |

|                   | t <sub>dcm</sub>                  | Data Stable Prior to WR (Memory Cycle)                      | [5]  |           | [17]   |           | [28]    |           |

|                   | t <sub>dci</sub>                  | Data Stable Prior to WR (I/O Cycle)                         | [6]  |           | [18]   |           | [29]    |           |

|                   |                                   | Data Stable from WR                                         | [7]  | ł         | [19]   |           | [30]    | 1         |

|                   | t <sub>cdf</sub>                  | Input Hold Time                                             |      |           |        |           | 0       |           |

|                   | t <sub>H</sub>                    |                                                             |      |           |        |           |         |           |

|                   |                                   | MREQ Delay From Falling Edge of Clock,<br>MREQ Low          | 20   | 100       | 20     | 85        | 20      | 70        |

|                   | t <sub>DHΦ</sub> (MR)             | MREQ Delay From Rising Edge of Clock,<br>MREQ High          |      | 100       |        | 85        |         | 70        |

| MREQ              | t <sub>DH</sub> (MR)              | MREQ Delay From Falling Edge of Clock,<br>MREQ High         |      | 100       |        | 85        |         | 70        |

|                   | tw(MRL)                           | Pulse Width, MREQ Low                                       | [8]  |           | [20]   |           | [20]    |           |

|                   |                                   | Pulse Width, MREQ High                                      | [9]  |           | [21]   |           | [21]    |           |

|                   | tw(MRH)                           |                                                             |      |           |        |           | [= 1]   | <u> </u>  |

|                   | <sup>t</sup> DL⊈(IR)              | IORQ Delay From Rising Edge of Clock,<br>IORQ Low           |      | 90        |        | 75        |         | 65        |

| IORO              | tDL (IR)                          | IORO Delay From Falling Edge of Clock,<br>IORO Low          |      | 110       |        | 85        |         | 70        |

|                   | t <sub>DHΦ(IR)</sub>              | IORO Delay From Rising Edge of Clock,                       |      | 100       |        | 85        |         | 70        |

|                   |                                   | IORQ High                                                   |      | 1         | 1      | 05        |         |           |

|                   | t <sub>DH</sub> <del>o</del> (IR) | IORQ Delay From Falling Edge of Clock<br>Clock, IORQ High   |      | 110       |        | 85        |         | 70        |

|                   | t <sub>DL</sub> (RD)              | RD Delay From Rising Edge of Clock, RD Low                  |      | 100       |        | 85        |         | 70        |

| _                 | tDL (RD)                          | RD Delay From Falling Edge of Clock, RD Low                 |      | 130       |        | 95        |         | 80        |

| RD                | t <sub>DH</sub> (RD)              | RD Delay From Rising Edge of Clock, RD High                 | 15   | 100       | 15     | 85        | 15      | 70        |

|                   | tDHQ(RD)                          | RD Delay From Falling Edge of Clock, RD High                |      | 110       |        | 85        |         | 70        |

|                   |                                   | WR Delay From Rising Edge of Clock, WR Low                  |      | 80        |        | 65        |         | 60        |

| 100               |                                   | WR Delay From Falling Edge of Clock, WR Low                 | 1    | 90        | 1      | 80        |         | 70        |

| WR                |                                   | WR Delay From Falling Edge of Clock, WR High                | 1    | 100       |        | 80        |         | 70        |

|                   |                                   | Pulse Width, WR Low                                         | [10] |           | [22]   |           | [22]    |           |

|                   | tw(WRL)                           |                                                             | 1    | 1         | (=~)   |           | ()      | 1         |

#### NOTES:

A. Data should be enabled onto the CPU data bus when RD is active. During interrupt acknowledge data should be enabled when M1 and IORQ are both active. B. The RESET signal must be active for a minimum of 3 clock cycles. [Cont'd. on next page].

#### MK3880-4, MK3880-6, MK3880-10 Z80-CPU

|        | SYMBOL                                     | PARAMETER                                                                                                    | 3880        |             | 3880-4      |             | 388         | 30-6        |

|--------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|

| SIGNAL |                                            |                                                                                                              | MIN<br>(ns) | MAX<br>(ns) | MIN<br>(ns) | MAX<br>(ns) | MIN<br>(ns) | MAX<br>(ns) |

| M1     |                                            | Mi Delay From Rising Edge of Clock M1 Low<br>M1 Delay From Rising Edge of Clock M1 High                      |             | 130<br>130  |             | 100<br>100  |             | 80<br>80    |

| RFSH   | t <sub>DL(RF)</sub><br>t <sub>DH(RF)</sub> | RFSH Delay From Rising Edge of Clock,<br>RFSH Low<br>RFSH Delay From Rising Edge of Clock,<br>RFSH High      |             | 180<br>150  |             | 130<br>120  |             | 110<br>100  |

| WAIT   | t <sub>S(WT)</sub>                         | WAIT Setup Time to Falling Edge of Clock                                                                     | 70          |             | 70          |             | 60          |             |

| HALT   | t <sub>D(HT)</sub>                         | HALT Delay Time From Falling Edge of Clock                                                                   |             | 300         |             | 300         |             | 260         |

| INT    | t <sub>s(IT)</sub>                         | INT Setup Time to Rising Edge of Clock                                                                       | 80          |             | 80          |             | 70          |             |

| NMI    | t <sub>w(NMI)</sub>                        | Pulse Width, NMI Low                                                                                         | 80          |             | 80          |             | 70          |             |

| BUSRQ  | t <sub>S(BQ)</sub>                         | BUSRO Setup Time to Rising Edge of Clock                                                                     | 80          |             | 50          |             | 50          |             |

| BUSAK  | t <sub>DL(BA)</sub><br>t <sub>DH(BA)</sub> | BUSAK Delay From Rising Edge of Clock,<br>BUSAK Low<br>BUSAK Delay From Falling Edge of Clock,<br>BUSAK High |             | 120<br>110  |             | 100<br>100  |             | 90<br>90    |

| RESET  | t <sub>s(RS)</sub>                         | RESET Setup Time to Rising Edge of Clock                                                                     | 90          |             | 60          |             | 60          |             |

|        | t <sub>F(C)</sub>                          | Delay to/from Float (MREQ, IORQ, RD and WR)                                                                  |             | 100         |             | 80          |             | 70          |

|        | t <sub>mr</sub>                            | M1 Stable Prior to IORQ (Interrupt Ack.)                                                                     | [11]        |             | [23]        |             | [31]        |             |

| [1]  | $t_{ACM} = t_{W} (\Phi H) + t_{f} - 75$                   | [17] $t_{dcm} = t_c - 170$                     |

|------|-----------------------------------------------------------|------------------------------------------------|

| [2]  | $t_{aci} = t_c - 80$                                      | [18] $t_{dci} = t_w (\Phi L) + t_r - 170$      |

| [3]  | $t_{CA} = t_{W} (\Phi L) + t_{f} - 40$                    | [19] $t_{cdf} = t_w (\Phi L) + t_r -70$        |

| [4]  | $t_{caf} = t_W (\Phi L) + t_f - 60$                       | [20] t <sub>w</sub> (MRL) = t <sub>c</sub> -30 |

| [5]  | t <sub>dcm</sub> = t <sub>C</sub> - 210                   | [21] $t_{W}(MRH) = t_{W}(\Phi H) + t_{f} - 20$ |

| [6]  | $t_{dci} = t_{w} (\Phi L) + t_{r} - 210$                  | [22] $t_W(\overline{WR}) = t_C - 30$           |

| [7]  | $t_{cdf} = t_w (\Phi L) + t_r - 80$                       | [23] $t_{mr} = 2t_c + t_w (\Phi H) + t_f - 65$ |

| (8)  | t <sub>w</sub> (MRL) = t <sub>c</sub> - 40                | [24] $t_{ACM} = t_{W} (\Phi H) + t_{f} -50$    |

| [9]  | $t_W$ (MRH) = $t_W$ ( $\Phi$ H) + $t_f$ – 30              | [25] t <sub>aci</sub> = t <sub>c</sub> -55     |

| [10] | t <sub>w</sub> (WR) = t <sub>c</sub> - 40                 | [26] $t_{CA} = t_w (\Phi L) + t_r -50$         |

| [11] | $t_{mr} = 2 t_{c} + t_{w} (\Phi H) + t_{f} - 80$          | [27] $t_{caf} = t_w (\Phi L) + t_r - 45$       |

| [12] | $t_{c} = t_{w} (\Phi H) + t_{w} (\Phi L) + t_{r} + t_{f}$ | [28] t <sub>dcm</sub> = t <sub>C</sub> -140    |

| [13] | $t_{acm} = t_{W} (\phi H) + t_{f} - 65$                   | [29] $t_{dci} = t_w (\Phi L) + t_r - 140$      |

| [14] | t <sub>aci</sub> = t <sub>c</sub> -70                     | [30] $t_{cdf} = t_{W} (\Phi L) + t_{r} -55$    |

| [15] | $t_{ca} = t_w (\Phi L) + t_r -50$                         | [31] $t_{mr} = 2t_c + t_w (\Phi H) + t_f -50$  |

[16]  $t_{caf} = t_w (\Phi L) + t_r -45$

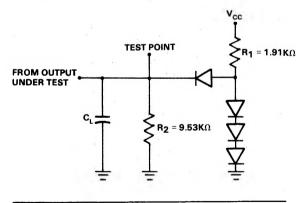

## LOAD CIRCUIT FOR OUTPUT

#### NOTES (Cont'd.)

C. Output Delay vs. Load Capacitance  $T_A = 70^{\circ}C V_{CC} = 5 V \pm 5\%$ Add 10 nsec delay for each 50 pF increase in load up to a maximum of 200 pF for the data bus and 100 pF for address and control lines.

D. Although static by design, testing guarantees  $t_{\rm W}$  (ΦH) of 200  $\mu sec$  maximum.

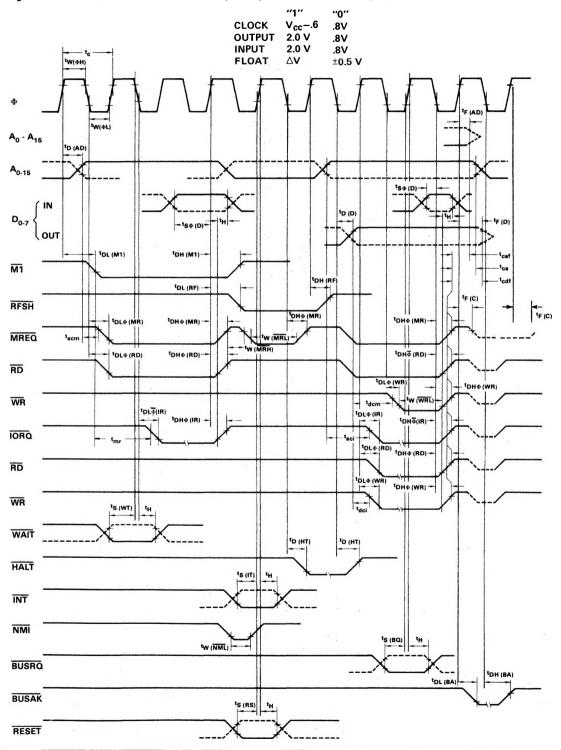

# A.C. TIMING DIAGRAM

Timing measurements are made at the following voltages, unless otherwise specified:

## **ORDERING INFORMATION**

| PART NO.           | PACKAGE TYPE | MAX CLOCK<br>FREQUENCY | TEMPERATURE RANGE |

|--------------------|--------------|------------------------|-------------------|

| MK3880N Z80-CPU    | Plastic      | 2.5 MHz                |                   |

| MK3880P Z80-CPU    | Ceramic      | 2.5 MHz                |                   |

| MK3880N-4 Z80-CPU  | Plastic      | 4.0 MHz                | 0° to + 70°C      |

| MK3880P-4 Z80-CPU  | Ceramic      | 4.0 MHz                |                   |

| MK3880P-10 Z80-CPU | Ceramic      | 2.5 MHz                | -40°C to +85°C    |