# MOS Read — ONLY Memory

# MOSTEK

## **FEATURES:**

- □ 850 ns Maximum Access Time

- 1.1 μs Maximum Cycle Time

- □ Low Power Dissipation -.02 mW/bit Typ.

- ☐ EA 4800/4900 Pin-for-Pin Replacement

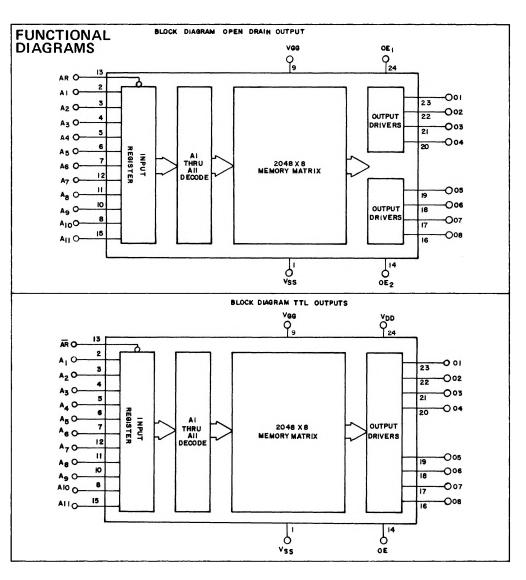

- Options Include 2Kx8 Organization with Three-State TTL Output Capability

- ☐ 2Kx8 or 4Kx4 Organization with Open Drain Outputs

- □ Standard Supplies +5 Volts, − 12 Volts

- □ Ion-Implanted for Full TTL/DTL Compatibility

# **DESCRIPTION:**

The MK 28000 is a mask programmable read only memory utilizing low-threshold lon-Implant , P-channel technology. The 28000 is a pin-for-pin replacement for the EA 4800/4900. The organization may be either 2Kx8 or 4Kx4 with open drain outputs. The 2Kx8 organization may have TTL three-state outputs with only one output enable.

Output data is stored indefinitely after each memory access. If the output enables are held low during access, the outputs will be in a high impedance state.

All inputs are protected against static charge accumulation. Pullup resistors on all inputs are available as a programmable option.

# PIN CONNECTIONS MK 28000 P

# **ABSOLUTE MAXIMUM RATINGS**

| Voltage on any terminal relative to V <sub>SS</sub> | .+0.3V to -20V |

|-----------------------------------------------------|----------------|

| Operating temperature range (Ambient)               | .0°C to 70°C   |

| Storage temperature range (Ambient)                 | 55°C to 150°C  |

# RECOMMENDED OPERATING CONDITIONS

$(0^{\circ} C \leqslant T_A \leqslant 70^{\circ} C)$

|                 | PARAMETER                | MIN                    | TYP  | MAX    | COMMENTS                                                         |

|-----------------|--------------------------|------------------------|------|--------|------------------------------------------------------------------|

| V <sub>ss</sub> | Supply Voltage           | +4.75V                 | +5V  | +5.25V |                                                                  |

| V <sub>DD</sub> | Supply Voltage           | _                      | 0    | _      |                                                                  |

| $V_{GG}$        | Supply Voltage           | -12.6V                 | -12V | -11.4V |                                                                  |

| VIL             | Input Voltage, Logic "0" |                        |      | +.8V   |                                                                  |

| V <sub>IH</sub> | Input Voltage, Logic "1" | V <sub>ss</sub> - 1.5V |      |        | Pullup resistors to $V_s$ ( $\approx$ 5K) available as an option |

# **ELECTRICAL CHARACTERISTICS**

$(V_{SS} = +5.0V \pm 5\%; V_{DD} = 0V; V_{GG} = -12V \pm 5\%; 0^{\circ}C \le T_{A} \le 70^{\circ}C)$

|                 | PARAMETER                 | MIN          | TYP   | MAX                  | COMMENTS                                                      |

|-----------------|---------------------------|--------------|-------|----------------------|---------------------------------------------------------------|

| I ss            | Supply Current            |              | 12 mA | 20 mA                | Outputs unconnected                                           |

| l <sub>GG</sub> | Supply Current            |              | 12 mA | 20 mA                | Inputs at V <sub>SS</sub>                                     |

| CIN             | Input Capacitance         |              |       | 10 pF                | See Note 1                                                    |

| LIN             | Input Leakage             |              |       | <b>10</b> μ <b>A</b> | See Note 2                                                    |

| R <sub>IN</sub> | Input Pullup Resistors    | <b>3 K</b> Ω |       | 9 Κ Ω                | Optional                                                      |

| V <sub>OL</sub> | Output Voltage, Logic "0" |              |       | 0.4V                 | I OL= 1.6 mA See Note 3                                       |

| Voh             | Output Voltage, Logic "1" | 2.5V         |       |                      | See Note 4                                                    |

| I OL            | Output Leakage Current    | –10 μA       |       | + 10 μA              | $V_0 = V_{SS} - 6V$ , $T = 25^{\circ}C$<br>(outputs disabled) |

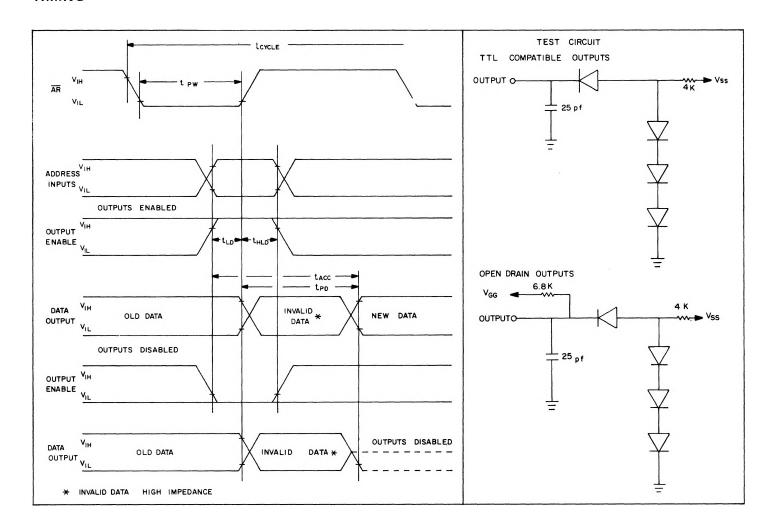

|                  | PARAMETER  AR Pulse Width | MIN 400 ns | TYP | MAX    | COMMENTS  See timing and test circuit                  |                  |

|------------------|---------------------------|------------|-----|--------|--------------------------------------------------------|------------------|

| t PW             |                           |            |     |        |                                                        |                  |

| tLD              | Address Lead Time         | 200 ns     |     |        |                                                        |                  |

| t <sub>HLD</sub> | Address Hold Time         | 200 ns     |     |        |                                                        |                  |

| t <sub>PD</sub>  | AR to Output Delay        | 650 ns     |     |        |                                                        |                  |

| t acc            | Access Time               |            |     | 850 ns | $t_{acc} = t_{Id} + t_{pd}$                            |                  |

| tcycle           | Cycle Time                | 1.1 μs     |     |        | t <sub>cycle</sub> = t <sub>pw</sub> + t <sub>pd</sub> | Read O<br>Memori |

**NOTES:**

V <sub>BIAS</sub> - V <sub>SS</sub> = 0v; f = 1 MHz

This parameter is for inputs without pullups (optional)

This parameter is for outputs with TTL compatible outputs.

For open drain outputs, a 6.8K Ω load to V<sub>GG</sub> is assumed. (See test circuits)

# **TIMING**

# MOSTEK 28000 ROM Punched Card Coding Format<sup>1</sup>

## First Card

Information Field Cols 1-30 Customer Customer Part Number MOSTEK Part Number<sup>2</sup> 31-50 60-72

# Second Card

1-30 **Engineer at Customer Site** 31-50 Direct Phone Number for Engineer

### Third Card

MOSTEK Part Number<sup>2</sup> 1-5 Organization (2048X8 or 4096X4) 10-16 Outputs (1=Open Drain,  $\phi$ =Push Pull TTL) 29 Number of Output Enable Pins (1 or 2) 31 Input Pullups (1=yes,  $\phi$ =no) 33

#### Fourth Card

Data Format<sup>3</sup> 1-9

Logic – ("Positive Logic" or "Negative Logic") Verification Code<sup>4</sup> 15-28

35-57

# **Data Cards**

# **MOSTEK Format**

or

**EA Format** (for EA Pin-for-Pin Replacement only)

1-4 **Decimal Address**

6-13 Output B8-B1 (MSB Thru LSB) 15-17 Octal Equivalent of Output Data

# **NOTES:**

- 1. Positive or negative logic formats are accepted as noted in the fourth card.

- 2. Assigned by MOSTEK; may be left blank

- 3. MOSTEK or Electronic Arrays Punched card coding format may be used. Specify which card format used by punching either "MOSTEK" or "EA". Start at column one.

- 4. Punched as: (a) VERIFICATION HOLD i.e. customer verification of the data as reproduced by MOSTEK is required prior to production of the ROM. To accomplish this MOSTEK supplies a copy of its Customer Verification Data Sheet (CVDS) to the customer. (b) VERIFICATION PROCESS — i.e. the customer will receive a CVDS but production will begin prior to receipt of customer verification.

- (c) VERIFICATION NOT NEEDED i.e. the customer will not receive a CVDS and production will begin immediately.