# 2560 BITS (256 x 10) MOS Read Only Memory

### FEATURES

- Ion-implanted for full TTL/DTL compatibility

- □ Chip enable permits wire-ORing

- □ Custom-programmed memory requires single mask modification

- $\Box$  550 ns cycle time (0°  $\leq$  T<sub>A</sub>  $\leq$  75°C)

- □ Static output storage latches

- □ Optional 3-bit, chip-select decoder available

- □ 2560 bits of storage, organized as 256 10-bit words

- $\Box$  Operates from +5V and -12V supplies

### APPLICATIONS

- Look-up table

- Code converter

- Stroke character generator

- Dot-matrix character generator

### DESCRIPTION

The MK 2400 P Series TTL/ DTL-compatible MOS Read-Only Memories (ROM's) are designed for a wide range of general-purpose memory applications where large quantity bit storage is required. Each ROM provides 2560 bits of programmable storage, organized as 256 words of 10 bits each. Low threshold-voltage processing, utilizing ion implantation with P-channel enhancement-mode MOS technology, provides direct input/output interface with TTL and DTL logic.

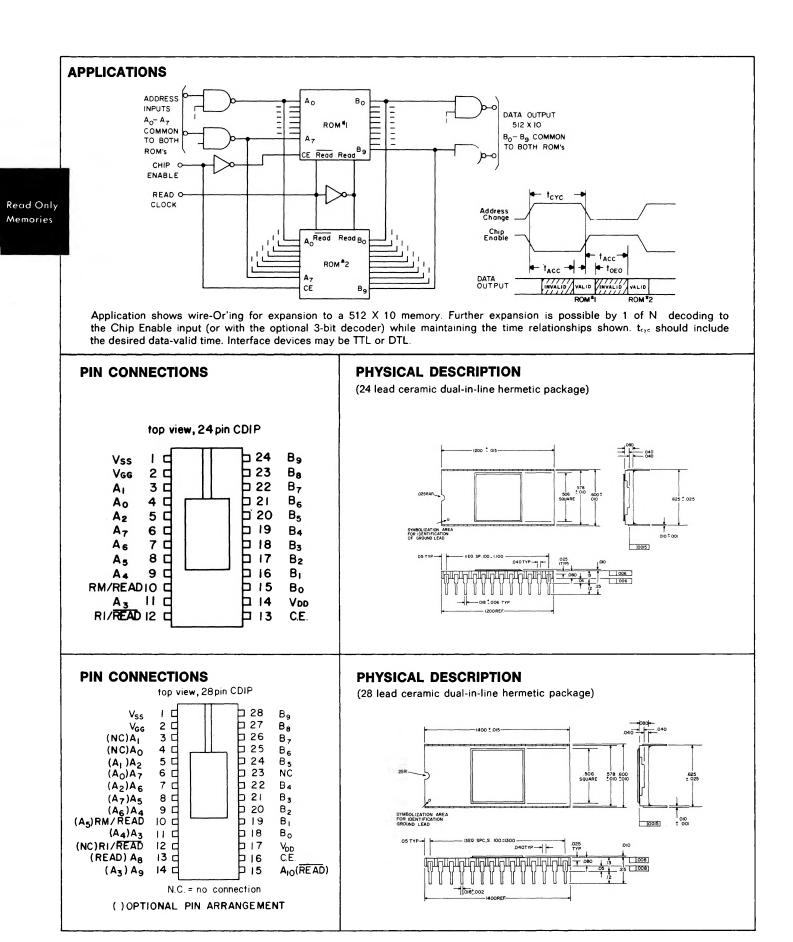

Programming is accomplished during manufacture by modification of a single mask, according to customer specifications. The MK 2400 P Series is available in either 24-lead or 28-lead ceramic dual-in-line packages. On the 28-pin ROM, an optional Chip Select Decoder may also be programmed according to customer specifications to provide a 3-bit Chip Select Code. Operation involves transferring addressed information from the memory matrix into the storage latches using the READ and READ inputs (see Timing). Information stored in the latches will remain despite address changes or chip disabling until the READ and READ inputs are again cycled. READ and READ input signals may be generated from separate timing circuits if desired, or either may be the inverse of the other.

The Chip Enable input forces the normally push-pull output buffer stages to an open-circuit condition when disabling the chip. If desired, new data can be stored in the storage latches while the chip is disabled. When the chip is reenabled, this data would be present at the outputs.

All inputs are protected against static charge accumulation. Pull-up resistors on all inputs are available as a programmable option.

For additional information regarding custom programming and coding sheets, contact your nearest Mostek representative.

# MK 2400 P SERIES

### FUNCTIONAL DIAGRAM 28 Pin CHIP SELECT Pockage INPUTS Only 0 DECODER A, 0-AIO 0 MATRIX INPUTS A 0 A 1 OUTPUTS 0 A 2 A 3 A 4 ADDRESS DECODER 99 83 0-256 X 10 STORAGE LATCHES OUTPUT BUFFERS .0-ADDRESS MEMORY -0 B 5 0-DATA A 5 A 6 A 7 Bб 0 0 0-0 0 0 **B** 7 õ Y δ Vss VDD VGG READ READ CHIP (RM) ENABLE (RI)

### **OPERATING NOTES**

| CHIP<br>ENABLE                                                                                                                                                                                                           | READ | READ | OUTPUT |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--------|--|--|--|

| 0                                                                                                                                                                                                                        | X    | X    | A      |  |  |  |

| 1                                                                                                                                                                                                                        | 0    | 1    | В      |  |  |  |

| 1                                                                                                                                                                                                                        | 1    | 0    | С      |  |  |  |

| "1" = V <sub>ss</sub> (+5V); "0" - V <sub>DD</sub> (0V)<br>X = No effect on output<br>A = Output open-circuited<br>B = Output retains data last stored in<br>latches<br>C = Output assumes state of ad-<br>dressed cells |      |      |        |  |  |  |

Read Only Memories

Read Mem **ABSOLUTE MAXIMUM RATINGS**

| Voltage on any terminal relative to $V_{ss}$ +0.3V to -10V |

|------------------------------------------------------------|

| Operating temperature range                                |

| Storage temperature range                                  |

## **RECOMMENDED OPERATING CONDITIONS** $(0^{\circ}C \le T_{A} \le 75^{\circ}C)$

|              |                                                                                                                                    | PARAMETER                                                                                                                                                                            | MIN                                   | ΤΥΡ                  | MAX                             | UNITS                                  | COMMENTS                                                              |

|--------------|------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------------|---------------------------------|----------------------------------------|-----------------------------------------------------------------------|

| POWER        | Vss<br>Vdd<br>Vgg                                                                                                                  | Supply voltage<br>Supply voltage<br>Supply voltage                                                                                                                                   | +4.75<br>                             | +5.0<br>0.0<br>-12.0 | + 5.25<br>                      | V<br>V<br>V                            | See note 1                                                            |

| INPUTS       |                                                                                                                                    | Input voltage, logic ''0''<br>Input voltage, logic ''1''                                                                                                                             | V <sub>ss</sub> — 1.5                 | 0<br>Vss             | +0.8                            | V                                      | Pull-up resistors (≈5K~) to<br>Vss available as programmab<br>option. |

| INPUT TIMING | t <sub>cyc</sub><br>t <sub>id</sub><br>t <sub>ig1</sub><br>t <sub>ig2</sub><br>t <del>rd</del><br>t <sub>r</sub><br>t <sub>r</sub> | Address change cycle time<br>Address to Read lead time<br>Read lag time 1<br>Read lag time 2<br>Read pulse width<br>Read pulse width<br>Rise time, any input<br>Fall time, any input | 550<br>250<br><b>05</b><br>300<br>0.3 |                      | .05<br>.05<br>100<br>100<br>100 | ns<br>μs<br>μs<br>ns<br>μs<br>ns<br>ns | See<br>Timing<br>Section                                              |

ELECTRICAL CHARACTERISTICS

(V<sub>ss</sub> =  $+5.0V \pm 0.25V$ , V<sub>GG</sub> =  $-12.0V \pm 0.6V$ , 0°C  $\leq T_A \leq +75$ °C, unless noted otherwise. Pull-up resistors not programmed.)

| i       |                                                                                 | PARAMETER                                                                                                                                        | MIN       | TYP*     | MAX                             | UNITS                      | CONDITIONS                                                                                                                                                                                                                                 |

|---------|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------|---------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER   |                                                                                 | Supply current (Vss)<br>Supply current (Vgg)                                                                                                     |           | 12<br>12 | 25<br>25                        | mA<br>mA                   | Outputs unconnected<br>See Note 2 and Note 3                                                                                                                                                                                               |

| INPUTS  | 1                                                                               | Input capacitance<br>Input leakage current                                                                                                       | ,         | 5        | 10<br>10                        | pF<br>μA                   | $V_{in} = V_{SS}, f_{meas} = 1MHz$<br>$V_{in} = V_{SS} - 6V  T_A = 25^{\circ}C$                                                                                                                                                            |

| OUTPUTS |                                                                                 | Output voltage, logical ''0''<br>Output voltage, logical ''1''<br>Output leakage current                                                         | 2.4<br>10 |          | 0.4<br>+ 10                     |                            | $\begin{array}{ll} I_{out} = 1.6 \text{ mA (into output)} & See \\ note \\ I_{out} = 0.4 \text{ mA} & 3 \\ (out of output) & \\ \hline V_{ss} - 6V \leq V_{out} \leq V_{ss} & \#1 \\ T_A = 25^{\circ}C & (outputs \ disabled) \end{array}$ |

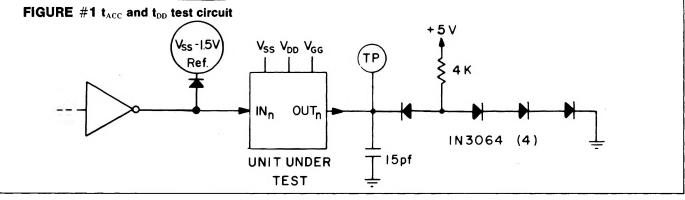

| UVNAMIC | $\begin{array}{c} t_{ACC} \\ t_{OD} \\ t_{OEO} \\ t_{CS} \\ t_{CD} \end{array}$ | Address-to-output access time<br>Output delay time<br>Output enable/disable time<br>Chip Select to Output Delay<br>Chip Deselect to Output Delay |           | 125      | 600<br>350<br>300<br>600<br>600 | ns<br>ns<br>ns<br>ns<br>ns | $t_{id} = 250ns$<br>$t_{ig1} = 0$<br>$t_{ig2} = 0$<br>See note 4<br>Section<br>and Figure #1                                                                                                                                               |

\*Typical values apply at  $V_{SS} = +5.0V$ ,  $V_{GG} = -12.0V$ ,  $T_A = 25^{\circ}C$

NOTES: 1. Supply voltages shown are for operation in a TTL/DTL system. Other supply voltages may be used if VDD and VGG maintain the same relationship to VSS, e.g., VSS=0V, VDD = -5V, VGG=-17V. Input voltages would also need to be adjusted accordingly.

2. Max measurements at 0°C. (MOS supply currents increase as temperature decreases.) Iss will increase 1.6mA (max) for each input at logic 0 when pull-up resistors are programmed.

3. Unit operated at minimum specified cycle time.

4. The outputs become open circuited when disabled or deselected. As shown in Fig. 1, an output with a "1" expected out does not transition through the 1.5V point when enabled (selected) or disabled (deselected); this is true because the TTL equivalent load pulls the open-circuited output to approximately 2 volts.

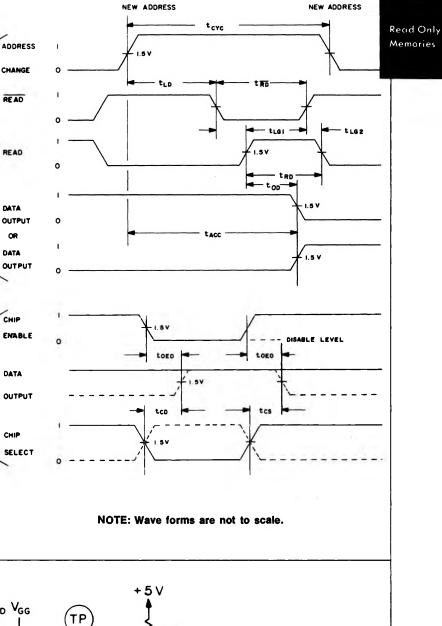

### TIMING

### Notes:

- 1. All times are referenced to the 1.5V point relative to VDD (ground) except rise and fall time measurements.

- 2. Chip enable =  $V_{ss}$  for all measurements except when measuring TOED.

- 3. Logic 0 is defined as  $V_{00}$  or ground; logic 1 as  $V_{ss}$  or +5V.

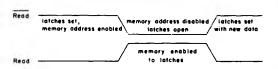

### **INTERNAL FUNCTION OF** READ/ READ SIGNALS

Set up time,  $t_{Id}$ , allows the input address to propagate through the address decoder and memory matrix prior to READ logic 0 time. As indicated above, READ at a logic 0 internally disables the input address so that an external address change may occur without affecting the location previously selected. The latches are also readied to receive new data which is enabled from the matrix when READ is at a logic 1. Data is set in the latches when READ is allowed to rise back to its logic 1 state. In actual use, the READ rising and falling edges can precede the falling and rising edges of READ, respectively, as implied by the specification of negative read lag times. This allows a very flexible timing relation between the two pulses, in that either input can be the inversion of the other or both may be generated from separate timing circuits.

Output data appears following the rise of the READ pulse but correct output data will not appear until READ has gone low. For this reason, READ is shown preceding READ even though other relationships are allowed. If READ is made to precede READ, delay time, top, should be referenced to the fall of READ rather than as shown.

The chip is disabled by applying a logical 0 to the chip enable input, forcing the outputs to an open-circuit condition. The output data present at the time of disable will again be present upon re-enabling unless a new read cycle was initiated for a different address while the chip was disabled, in which case the new data would be present at the outputs.

The programmable 3-bit chip select timing would be the same as the address inputs.

Memories

| Cols.   | Information Field                                                                             |                                    | "Negative Logic"                                                                                                                 |        |  |

|---------|-----------------------------------------------------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------|--|

| First C | ard                                                                                           | 35-57                              | Verification Code <sup>7</sup>                                                                                                   |        |  |

| 1-30    | Customer                                                                                      | 60-74                              | Package Choice <sup>®</sup>                                                                                                      |        |  |

| 31-50   | Customer Part Number                                                                          |                                    |                                                                                                                                  | -      |  |

| 60-72   | Mostek Part Number <sup>2</sup>                                                               | Data C                             | Data Cards                                                                                                                       |        |  |

|         |                                                                                               | 1-3                                | Decimal Address                                                                                                                  | Read C |  |

| Second  | l Card                                                                                        | 5                                  | Output B9                                                                                                                        | Memor  |  |

| 1-30    | Engineer at Customer Site                                                                     | 6                                  | Output B8                                                                                                                        |        |  |

| 31-50   | Direct Phone Number for Engineer                                                              | 7                                  | Output B7                                                                                                                        | 4      |  |

|         |                                                                                               | 8                                  | Output B6                                                                                                                        |        |  |

| Third C | Card                                                                                          | 9                                  | Output B5                                                                                                                        |        |  |

| 1-5     | Mostek Part Number <sup>2</sup>                                                               | 10                                 | Output B4                                                                                                                        |        |  |

| 10-16   | Organization <sup>3</sup>                                                                     | 11                                 | Output B3                                                                                                                        |        |  |

| 29      | A8 <sup>4</sup>                                                                               | 12                                 | Output B2                                                                                                                        |        |  |

| 30      | A9⁴                                                                                           | 13                                 | Output B1                                                                                                                        |        |  |

| 31      | A10⁴                                                                                          | 14                                 | Output B0                                                                                                                        |        |  |

| 32      | Pull-up Resistor⁵                                                                             | 16                                 | Octal Equivalent of: B9 <sup>9</sup>                                                                                             |        |  |

|         |                                                                                               | 17                                 | Octal Equivalent of: B8, B7, B6 <sup>9</sup>                                                                                     |        |  |

| Fourth  | Card                                                                                          | 18                                 | Octal Equivalent of: B5, B4, B3 <sup>9</sup>                                                                                     |        |  |

| 0-6     | Data Format <sup>4</sup> — "MOSTEK"                                                           | 19                                 | Octal Equivalent of: B2, B1, B0 <sup>9</sup>                                                                                     |        |  |

| 15-28   | Logic — "Positive Logic" or                                                                   |                                    |                                                                                                                                  |        |  |

| Notes:  | 1. Positive or negative logic formats are accept                                              | oted as noted ir                   | a the fourth card.                                                                                                               |        |  |

| 2       | 2. Assigned by Mostek Marketing Department;                                                   | may be left bla                    | ank.                                                                                                                             |        |  |

| 3       | 3. Punched as 0256x10.                                                                        |                                    |                                                                                                                                  |        |  |

| 4       | <ol> <li>A "0" indicates the chip is enabled by a lo<br/>a "Don't Care" condition.</li> </ol> | ogic 0, a "1" ir                   | dicates it is enabled by a logic 1, and a "2" indicates                                                                          |        |  |

| 5       | 5. A "1" indicates pull-ups; a "0" indicates no                                               | pull-ups.                          |                                                                                                                                  |        |  |

|         | 6. "MOSTEK" format only is accepted on this                                                   |                                    |                                                                                                                                  |        |  |

|         | Punched as: (a) VERIFICATION HOLD -                                                           | i.e. customer violation of the ROI | verification of the data as reproduced by MOSTEK is<br>M. To accomplish this MOSTEK supplies a copy of its<br>) to the customer. |        |  |

|         |                                                                                               | S—i.e. the c                       | ustomer will receive a CVDS but production will begin                                                                            |        |  |

|         | (c) VERIFICATION NOT NEE<br>will begin immediately.                                           | EDED — i.e. th                     | e customer will not receive a CVDS and production                                                                                |        |  |

| 8       | 8. "24 PIN", "28 PIN STANDARD", or "28 PIN                                                    | OPTIONAL'' (le                     | ft justified to column 60).                                                                                                      |        |  |

| -       | ). The octal parity check is created by brea                                                  | king up the ou                     | tput word into groups of three from right to left and<br>s. For example the output word 1010011110 would be                      |        |  |