### MK 1002 P MK 1002 N

## MOS Static Shift Register

# MOSTEK

#### **FEATURES:**

- Ion-implanted for full TTL/DTL compatibility no interface circuitry required

- □ Single-phase, TTL/DTL compatible clocks

- Dual 128-bit static shift registers 256 bits total

- Dual sections have independent clocks

- □ Recirculate logic built in

- DC to 1 MHz clock rates

- □ Low power dissipation 130 mW

- 🗋 16-pin dual-in-line package

#### APPLICATIONS

- Delay lines

- Buffer data storage

- Recycling test data sequencer

- Digital filtering

#### DESCRIPTION

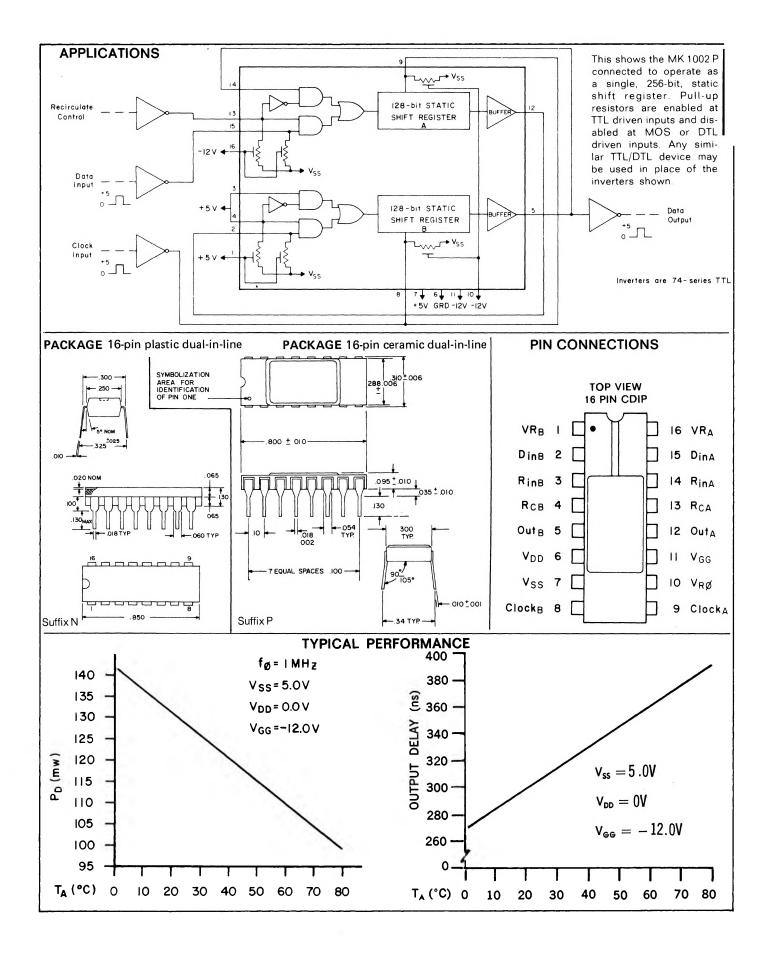

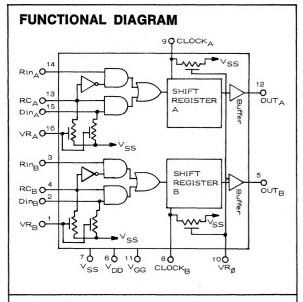

The MK 1002 is a P-channel MOS static shift register utilizing low threshold-voltage processing and ion-implantation to achieve full TTL/DTL compatibility. Each of the two independent 128 bit sections has a built-in clock generator to generate three internal clock phases from a single-phase TTL-level external input. In addition, each section has input logic for loading or recirculating data within the register. (See Functional Diagram.) The positive-logic Boolean expression for this action is:

OUT (delayed 128 bits) =  $(R_c) (D_{in}) + (\overline{R_c}) (R_{in})$

The Data, Recirculate Control, and Clock inputs are provided

with internal pull-up resistors to  $V_{ss}$  (+5V) for use when driving from TTL. These resistors can be disabled when driving from circuitry with larger output-voltage swings, such as DTL. Enabling of pull-up resistors is accomplished by connecting the appropriate terminal to  $V_{GG}$ ; disabling by connecting to  $V_{ss}$ . The Recirculate inputs are not provided with pull-up resistors since they are generally driven from MOS.

Shifting data into the register is accomplished while the Clock input is low. Output data appears following the positivegoing Clock edge. Data in each register can be held indefinitely by maintaining the Clock input high.

#### OPERATING NOTES

| Rc                                                                     | <b>R</b> <sub>in</sub>      | <b>D</b> <sub>in</sub> | DATA<br>ENTERED |  |  |

|------------------------------------------------------------------------|-----------------------------|------------------------|-----------------|--|--|

| 1                                                                      | Х                           | 1                      | 1               |  |  |

| 1                                                                      | х                           | 0                      | 0               |  |  |

| 0                                                                      | 1                           | х                      | 1               |  |  |

| 0                                                                      | 0                           | х                      | 0               |  |  |

| "1" = V <sub>ss</sub><br>"0" = V <sub>DE</sub><br>X = No<br>Dutput Log | $\mathbf{G} = \mathbf{Grd}$ | escriptio              | ٦.              |  |  |

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage, V <sub>DD</sub>      |   |  |   |  |  |  | $ V_{ss} = 10.0 V$ |

|--------------------------------------|---|--|---|--|--|--|--------------------|

| Supply Voltage, V <sub>GG</sub>      | • |  |   |  |  |  | $ V_{ss} = 20.0 V$ |

| Voltage at any Input or Output       |   |  |   |  |  |  |                    |

| Operating Free-air Temperature Range |   |  |   |  |  |  |                    |

| Storage Temperature Range            |   |  | • |  |  |  | —55°C to +150°C    |

#### **RECOMMENDED OPERATING CONDITIONS** ( $0^{\circ}C \leq T_{A} \leq 75^{\circ}C$ )

|              |                  | PARAMETER                     | MIN                | ТҮР          | MAX                | UNITS | COMMENTS       |

|--------------|------------------|-------------------------------|--------------------|--------------|--------------------|-------|----------------|

| E            | V <sub>ss</sub>  | Supply Voltage                | 4.75               | 5.0          | 5.25               | v     | $V_{DD} = 0 V$ |

| POWER        | V <sub>GG</sub>  | Supply Voltage <sup>(1)</sup> | —12.6              | <b>—12.0</b> | 11.4               | v     |                |

| STI          | V <sub>IL</sub>  | Input Voltage, Logic 0(2)     |                    | 0            | V <sub>ss</sub> _4 | v     |                |

| INPUTS       | V <sub>IH</sub>  | Input Voltage, Logic 1        | V <sub>ss</sub> —1 | 5.0          | V <sub>ss</sub>    | v     |                |

|              | f                | Clock Repetition Rate         | DC                 |              | 1                  | MHz   |                |

|              | t <sub>øp</sub>  | Clock Pulse Width             | 0.35               |              | 10                 | μS    |                |

|              | tød              | Clock Pulse Delay             | 0.4                |              |                    | μS    | See            |

| INPUT TIMING | t <sub>¢</sub> , | Clock Pulse Risetime          | .010               |              | 0.2                | μS    | Timing         |

| Ē            | t <sub>øf</sub>  | Clock Pulse Falltime          | .010               |              | 0.2                | μS    | Diagram        |

| Inat         | t <sub>did</sub> | Data Leadtime                 | 50                 |              |                    | ns    | -              |

| =            | t <sub>dlg</sub> | Data Lagtime                  | 200                |              |                    | ns    |                |

|              | t <sub>rid</sub> | Recirculate Control Leadtime  | 100                |              |                    | ns    |                |

|              | t <sub>fig</sub> | Recirculate Control Lagtime   | 300                |              |                    | ns    |                |

#### **ELECTRICAL CHARACTERISTICS**

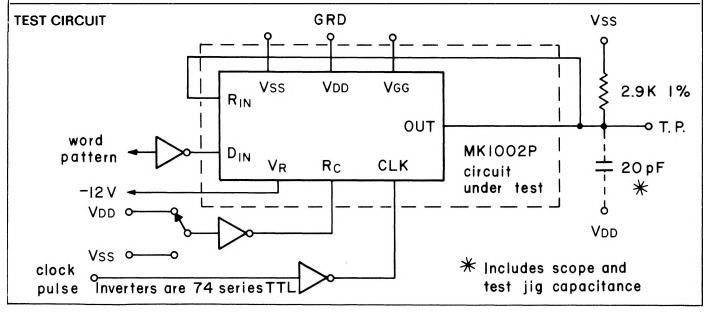

( $V_{SS} = +5 \pm 0.25V$ ,  $V_{GG} = -12 \pm 0.6V$ ,  $V_{DD} = 0V$ ,  $T_A = 0^{\circ}C$  to  $+75^{\circ}C$ , using test circuit shown, unless otherwise noted.)

|                  |                     | PARAMETER                                                                                    | MIN          | TYP <sup>3</sup> | MAX       | UNITS    | CONDITIONS                                                                                         |

|------------------|---------------------|----------------------------------------------------------------------------------------------|--------------|------------------|-----------|----------|----------------------------------------------------------------------------------------------------|

| POWER            | I <sub>ss</sub>     | Power Supply Current, V <sub>ss</sub>                                                        |              | 14               | 25        | mA       | $f_{\phi} = 1 \text{ MHz}$<br>Inputs & Outputs open                                                |

|                  | I <sub>GG</sub>     | Power Supply Current, V <sub>GG</sub>                                                        |              | 5                | 10        | mA       |                                                                                                    |

|                  | C <sub>i</sub>      | Input Capacitance, any Input                                                                 |              | 3                | 10        | pF       | $V_1 = V_{ss}$ , f = 1 MHz<br>$T_A = 25^{\circ}C$                                                  |

| INPUTS           | I <sub>IL</sub>     | Input Current, Logic 0:<br>Resistors Disabled <sup>2</sup><br>Resistors Enabled <sup>2</sup> | -0.3         |                  | 40<br>1.6 | μA<br>mA | $V_{1} = V_{ss} - 5V$ $V_{1} = +0.4V$                                                              |

|                  | I <sub>IH</sub>     | Input Current, Logic 1, Any Input                                                            |              |                  | 40        | μΑ       | $ \begin{array}{l} VR_{A},VR_{B},VR_{\phi}=V_{SS}\\ V_{I}=V_{SS} \end{array} $                     |

|                  | I <sub>IR{on}</sub> | Input Current at Recirculate Inputs <sup>2</sup>                                             |              |                  | - 40      | μΑ       | $ \begin{array}{l} VR_{A},  VR_{B},  VR_{\phi}  =  V_{GG} \\ V_{I}  =  V_{SS}  -  SV \end{array} $ |

| OUTPUTS          | V <sub>ol</sub>     | Output Voltage, Logic 0 (3)                                                                  |              |                  | 0.4       | V        | $I_L = -1.6 \text{ mA}$                                                                            |

| OUTF             | V <sub>он</sub>     | Output Voltage, Logic 1 (3)                                                                  | $V_{ss} - 1$ |                  |           | v        | $I_L = +100 \ \mu A$                                                                               |

| MIC<br>R.        | t <sub>DLH</sub>    | Output Delay, Low to High (3)                                                                |              |                  | 450       | ns       | See Timing                                                                                         |

|                  | t <sub>DHL</sub>    | Output Delay, High to Low (3)                                                                |              |                  | 450       | ns       | Diagram and                                                                                        |

| DYNAMIC<br>CHAR. | t <sub>vor</sub>    | Output Voltage Rise Time (3)                                                                 |              | 100              | 150       | ns       | Test                                                                                               |

| -                | t <sub>voF</sub>    | Output Voltage Fall Time (3)                                                                 |              | 100              | 150       | ns       | Circuit                                                                                            |

NOTES:

Other supply voltages are permissible providing that supply and input voltages are adjusted to maintain the same potential relative to Vss, e.g., Vss = OV, Vbb = -5 ± 0.25V, Veg = -17 ± 0.85V.

MOS pull-up resistors to + 5V are provided internally. These MOS resistors are enabled by connecting VRA, VRs and VR¢ to Veg, and disabled by connect, ing VRA, VRs and VR¢ to Vss. Pull-up resistors not provided at recirculate inputs.

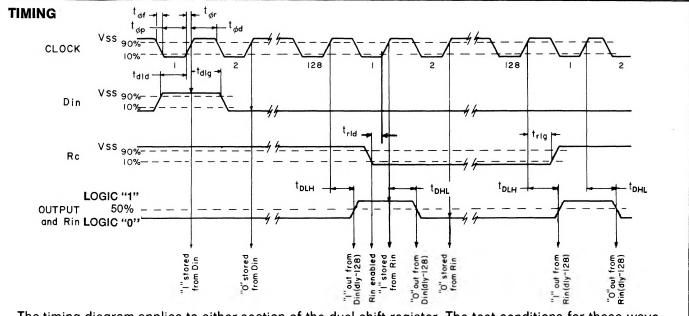

The timing diagram applies to either section of the dual shift register. The test conditions for these waveforms are illustrated below. A logic "1" is defined as +5 V and a logic "0" is defined as OV

As long as  $R_c$  is at a "1",  $R_{in}$  is disabled and  $D_{in}$  is enabled. The data that is present at  $D_{in}$  while the clock is at "0" is shifted in and will be stored as the clock goes to a "1" This data must have been present  $t_{did}$  time prior to the clock "1" edge. The data must also remain in that same state for  $t_{dig}$  time after that edge. These times are necessary to insure proper data storage in the first register-cell.

On the clock "1" edge, data is shifted through the register causing bit 127 to be shifted to position 128. This cell's output is buffered and appears at the output in the same logic polarity that appeared at the input 128 clocks prior. This data appears within  $t_{pd}$  time of the clock "1" edge.

$R_{in}$  may be hardwired to the data output. When  $R_c$  is at a "0",  $R_{in}$  is enabled and  $D_{in}$  is disabled. Therefore, the output data will appear at the input of the first cell. When  $R_{in}$  is tied to the data output, the output delay will insure  $t_{dig}$  and  $t_{did}$  times.  $R_c$  "0" time must lead the clock "1" edge by  $t_{rid}$  time and must lag that edge by  $t_{rig}$  time to insure proper data storage when recirculate storage is desired.