# MC4304F, L • MC4305F, L\* MC4004F, L, P • MC4005F, L, P\*

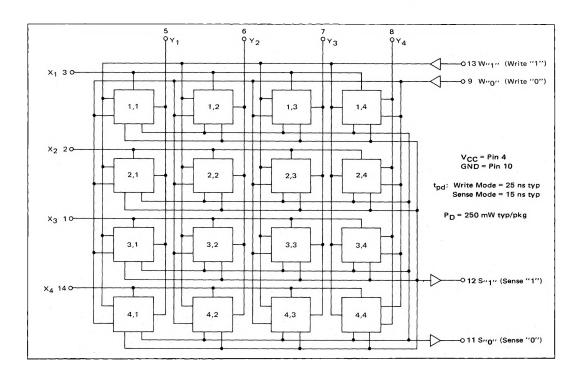

This 16-Bit memory cell serves as the basic building block for scratch pad memory systems having cycle times of less than 100 ns. The basic cell provides 16 words of one-bit memory operating in the non-destructive readout (NDRO) mode.

The memory contains 16 flip-flops arranged in a four-by-four matrix. A single bit of the matrix is selected by

driving one of four X select lines and one of four Y select lines above the select threshold. Two sense amplifiers are shared by all 16 bits and provide a double rail output from the selected bit. The sense output of many devices can be "wired ORed" together since the output stage does not have a pullup resistor or network. Two write amplifiers allow a "1" or a "0" to be written into a selected bit.

### - OPERATING SEQUENCE -

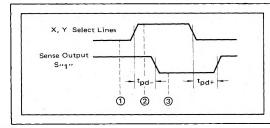

## FIGURE 1 - READ MODE TIMING DIAGRAM

- ① All X and Y selection lines and both write inputs are low (less than +0.8 V).

- ② Desired bit selected by driving the appropriate X and Y select lines more positive than +2.1 V.

- 3 After the turn-on delay time (tpd.), the S"1" output will be low (less than +0.45 V) and the S"0" output will be high (more than +2.5 V), providing that a "1" is stored in the selected bit.

<sup>\*</sup>F suffix = TO-86 ceramic flat package (Case 607).

L suffix = TO-116 ceramic dual in-line package (Case 632).

P suffix = TO-116 plastic dual in-line package (Case 605).

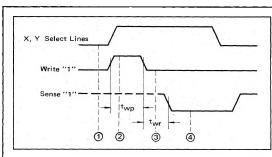

FIGURE 2 - WRITE MODE TIMING DIAGRAM

- ① All X and Y selection lines and both write inputs are low (less than +0.8 V).

- ② Bit location selected by driving the appropriate X and Y select lines more positive than +2.1 V. To write a "1", drive the write "1" input more positive than +2.1 V for a minimum time of 25 ns (t<sub>wp</sub>).

- 3 Write "1" line returned to low state.

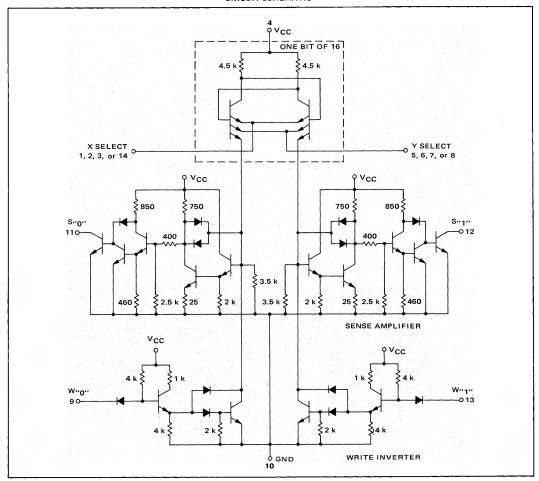

## CIRCUIT SCHEMATIC

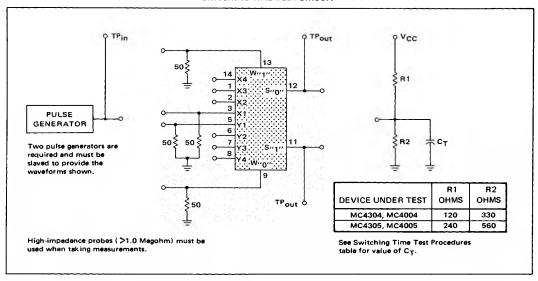

#### SWITCHING TIME TEST CIRCUIT

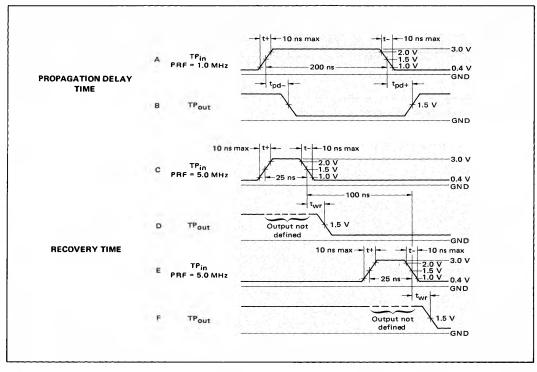

### **VOLTAGE WAVEFORMS AND DEFINITIONS**

#### SWITCHING TIME TEST PROCEDURES

(Letters shown in test columns refer to waveforms)

| Test                                                                     | Symbol | Pin<br>Under<br>Test | Input Pin |                     |                     |                      |         |                     |                     |                     |         |              | Output     |    |     | Limits             |                    |

|--------------------------------------------------------------------------|--------|----------------------|-----------|---------------------|---------------------|----------------------|---------|---------------------|---------------------|---------------------|---------|--------------|------------|----|-----|--------------------|--------------------|

|                                                                          |        |                      | 3         | 2<br>X <sub>2</sub> | 1<br>X <sub>3</sub> | 14<br>X <sub>4</sub> | 5<br>Y1 | 6<br>Y <sub>2</sub> | 7<br>Y <sub>3</sub> | 8<br>Y <sub>4</sub> | w0<br>∂ | 13<br>W··1·· | 11<br>S~0~ |    |     | MC4304-5<br>ns max | MC4004-5<br>ns max |

|                                                                          |        |                      | X1        |                     |                     |                      |         |                     |                     |                     |         |              |            |    |     |                    |                    |

| Turn-Off Delay Time<br>(Address Lines to<br>Sense "0" Output)            | •••    |                      | 3.0 V     | 3.0 V               | 3.0 V               | 3.0 V                | 3.0 V   | 3.0 ∨               | 3.0 V               | 3.0 V               | Gnd     | 3.0 V        | -          | _  | _   | _                  |                    |

|                                                                          | ••     |                      | 3.0 V     | Gnd                 | Gnd                 | Gnd                  | 3.0 ∨   | Ģnd                 | Gnd                 | Gnd                 | 3.0 V   | Gnd          | _          | _  |     |                    |                    |

|                                                                          | tpd+   | 11                   | A         | Gnd                 | Gnd                 | Gnd                  | Α .     | Gnd                 | Gnd                 | Gnd                 | Gnd     | Gnd          | В          | -  | 30  | 23                 | 23                 |

|                                                                          | tpd+   | 11                   | A         | Gnd                 | Gnd                 | Gnd                  | A       | Gnd                 | Gnd                 | Gnd                 | Gnd     | Gnd          | В          | -  | 200 | 35                 | 35                 |

| Turn-Off Delay Time<br>(Address Lines to<br>Sense "1" Output)            |        | -                    | 3.0 V     | 3.0 V               | 3.0 V               | 3.0 V                | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V               | 3.0 ∨   | Gnd          | _          | ~  |     | _                  | -                  |

|                                                                          |        | _                    | 3.0 V     | Gnd                 | Gnd                 | Gnd                  | 3.0 V   | Gnd                 | Gnd                 | Gnd                 | Gnd     | 3.0 V        | -          | _  | -   | -                  |                    |

|                                                                          | tpd+   | 12                   | Α         | Gnd                 | Gnd                 | Gnd                  | A       | Gnd                 | Gnd                 | Gnd                 | Gnd     | Gnd          | -          | В  | 30  | 23                 | 23                 |

|                                                                          | tpd+   | 12                   | Α         | Gnd                 | Gnd                 | Gnd                  | A       | Gnd                 | Gnd                 | Gnd                 | Gnd     | Gnd          | -          | В  | 200 | 35                 | 35                 |

| Turn-On Delay Time<br>(Address Lines to<br>Sense "0" Output)             | 1      |                      | 3.0 V     | 3.0 V               | 3.0 V               | 3.0 V                | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V               | Gnd     | 3.0 V        | -          | -  | _   |                    |                    |

|                                                                          | •••    | _                    | 3.0 V     | Gnd                 | Gnd                 | Gnd                  | 3.0 V   | Gnd                 | Gnd                 | Gnd                 | 3.0 V   | Gnd          | _          | _  | _   | -                  | -                  |

|                                                                          | tpd-   | 11                   | Α         | Gnd                 | Gnd                 | Gnd                  | Α       | Gnd                 | Gnd                 | Gnd                 | Gnd     | Gnd          | В          | _  | 30  | 23                 | 23                 |

|                                                                          | tpd-   | 11                   | A         | Gnd                 | Gnd                 | Gnd                  | A       | Gnd                 | Gnd                 | Gnd                 | Gnd     | Gnd          | В          | -  | 200 | 35                 | 35                 |

| Turn-On Delay Time<br>(Address Lines to<br>Sense "1" Output)             |        | -                    | 3.0 V     | 3.0 V               | 3.0 V               | 3.0 V                | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V               | 3.0 V   | Gnd          | _          | -  | _   |                    |                    |

|                                                                          |        | _                    | 3.0 V     | Gnd                 | Gnd                 | Gnd                  | 3.0 V   | Gnd                 | Gnd                 | Gnd                 | Gnd     | 3.0 V        | _          | ~  | _   | _                  | -                  |

|                                                                          | tpd-   | 12                   | Α         | Gnd                 | Gnd                 | Gnd                  | Α       | Gnd                 | Gnd                 | Gnd                 | Gnd     | Gnd          | -          | В  | 30  | 23                 | 23                 |

|                                                                          | tpd-   | 12                   | A         | Gnd                 | Gnd                 | Gnd                  | A       | Gnd                 | Gnd                 | Gnd                 | Gnd     | Gnd          | -          | В  | 200 | 35                 | 35                 |

| Turn-Off Delay Time<br>(4 Bits) (Address Lines<br>to Sense "0" Output)   |        | -                    | 3.0 V     | 3.0 V               | 3.0 V               | 3.0 V                | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V               | Gnd     | 3.0 V        | -          | _  | -   |                    | _                  |

|                                                                          | ••     | -                    | 3.0 V     | Gnd                 | Gnd                 | Gnd                  | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V               | 3.0 V   | Gnd          | _          |    | _   | -                  | _                  |

|                                                                          | tpd+   | 11                   | - A       | Gnd                 | Gnd                 | Gnd                  | Α       | Α                   | Α                   | Α                   | Gnd     | Gnd          | В          | -  | 30  | 35                 | 35                 |

| Turn-Off Delay Time<br>(4 Bits) (Address Lines<br>to Sense "1" Output)   | •••    | _                    | 3.0 V     | 3.0 V               | 3.0 V               | 3.0 V                | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V               | 3.0 V   | Gnd          | _          | _  |     | _                  |                    |

|                                                                          | ••     | _                    | 3.0 V     | Gnd                 | Gnd                 | Gnd                  | 3.0 V   | 3.0 V               | 3.0 V               | 3.0 V               | Gnd     | 3.0 V        |            | ~  | _   | -                  |                    |

|                                                                          | tpd+   | 12                   | Α         | Gnd                 | Gnd                 | Gnd                  | Α       | A                   | Α                   | A                   | Gnd     | Gnd          | -          | В  | 30  | 35                 | 35                 |

| Write Recovery Time                                                      | twr    | 12                   | 3.0 V     | Gnd                 | Gnd                 | Gnd                  | 3.0 ∨   | Gnd                 | Gnd                 | Gnd                 | E       | С            | -          | ٥  | 30  | 40                 | 40                 |

|                                                                          |        | 11                   | 3.0 V     | Gnd                 | Gnd                 | Gnd                  | 3.0 V   | Gnd                 | Gnd                 | Gnd                 | Ε       | С            | F          | ~  | 30  | 40                 | 40                 |

|                                                                          |        |                      |           |                     |                     |                      |         | •                   |                     |                     |         |              |            |    |     | ns min             | ns min             |

| Nrite Pulse Width t <sub>WD</sub> - Tested during t <sub>Wr</sub> tests. |        |                      |           |                     |                     |                      |         |                     |                     |                     |         |              | 25         | 25 |     |                    |                    |

<sup>\*</sup>Capacitance value for load of the Switching Time Test Circuit

<sup>• \*</sup>Preconditioning procedures for subsequent test.