# Smart Voltage Regulator for Peripheral Card Applications

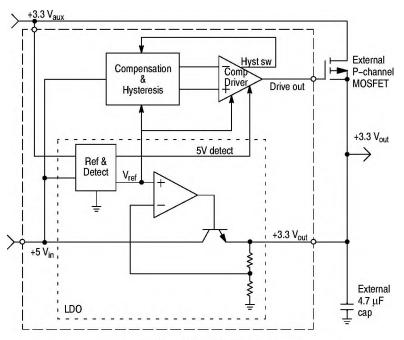

The MC33566 Low Dropout Regulator is designed for computer peripheral card applications complying with the *instantly available requirements* as specified by ACPI objectives. The MC33566 permits glitch–free transitions from "sleep" to "active" system modes and has internal logic circuitry to detect whether the system is being powered from the motherboard main 5.0 V power supply or the 3.3 V aux supply.

The MC33566 provides a regulated output voltage of 3.3 V via either an internal low dropout 5.0 V–to–3.3 V voltage regulator or an external P–channel MOSFET, depending on the operating status of the system in which the card is installed. During normal operating mode (5.0 V main supply available) the 3.3 V output is provided from the internal low dropout regulator at an output current of 0.4 A. When the motherboard enters sleep mode, the MC33566 operates from the 3.3 V aux supply and routes the aux current to the output via the external P–channel MOSFET bypass transistor controlled by the *drive out* pin. As a result, the output voltage provided to the peripheral card remains constant at 3.3 V even during host systems transitions to and from sleep mode.

## MC33566 Features:

- Output Current up to 0.4 A

- Excellent Line and Load Regulation

- Low Dropout Voltage

- Prevents Reverse Current Flow During Sleep Mode

- Glitch-Free Transfer from Sleep Mode to Active Mode

- Compatible with Instantly Available PC Systems

Figure 1. Simplified Block Diagram

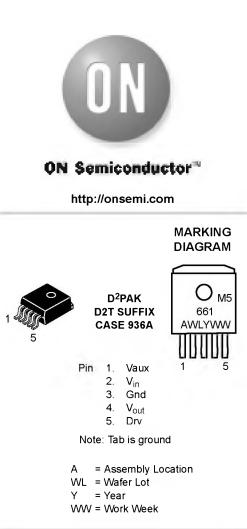

#### **ORDERING INFORMATION**

| Device         | Package            | Shipping         |

|----------------|--------------------|------------------|

| MC33566D2T-1   | D <sup>2</sup> PAK | 50 Units/Rail    |

| MC33566D2T-1RK | D <sup>2</sup> PAK | 2500 Tape & Reel |

# MC33566

## **PIN ASSIGNMENTS AND FUNCTIONS**

| Pin # | Pin Name              | Pin Description                                                                                                                                                                                                                                     |

|-------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | +3.3 V <sub>aux</sub> | Auxiliary input. Typical voltage 3.3 V.                                                                                                                                                                                                             |

| 2     | +5.0 V <sub>in</sub>  | This is the input supply for the IC. Typical voltage 5.0 V. (Notes 1 and 2)                                                                                                                                                                         |

| 3     | Gnd                   | Logic and power ground.                                                                                                                                                                                                                             |

| 4     | +3.3 V <sub>out</sub> | 3.3 V output provided to the application circuit (output current is sourced to this pin from the 5.0 V input.)                                                                                                                                      |

| 5     | Drive out             | This output drives a P–channel MOSFET with up to 2000 pF of "effective" gate capacitance.<br>Recommended devices are the MMFT5P03HD and MTSF1P02HD. Drive out has active internal<br>pull–up and pull–down circuitry to guarantee fast transitions. |

## MAXIMUM RATINGS (T<sub>C</sub> = 25°C, unless otherwise noted)

| Rating                                   | Symbol                    | Value         | Unit |

|------------------------------------------|---------------------------|---------------|------|

| +5.0 V <sub>in</sub> Supply Voltage      | V <sub>in</sub>           | 7.0           | Vdc  |

|                                          | V <sub>in</sub>           | –0.5 (Note 3) | Vdc  |

| Operating Ambient Temperature            | Ta                        | –5.0 to +85   | °C   |

| Operating Junction Temperature           | TJ                        | – 5.0 to +150 | °C   |

| Lead Temperature (Soldering, 10 seconds) | TL                        | 300           | °C   |

| Storage Temperature                      | T <sub>stg</sub>          | – 55 to +150  | °C   |

| Package Thermal Resistance               | R <sub>0JA</sub> (Note 4) | 65            | °C/W |

## AC ELECTRICAL SPECIFICATIONS (Notes 5, 6, and 7)

| Characteristic                                                                                                                                                         |                 | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|-----|------|

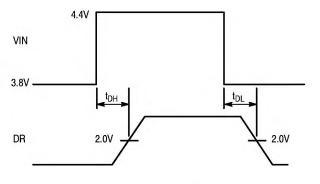

| Drive High Delay (V <sub>in</sub> ramping up)<br>C <sub>drive</sub> = 1.2 nF, measured from +5.0 V <sub>in</sub> = V <sub>thresHi</sub> to V <sub>Drive</sub> = 2.0 V  | t <sub>DH</sub> | Ţ.  | 0.5 | 3.5 | μS   |

| Drive Low Delay (V <sub>in</sub> ramping down)<br>C <sub>drive</sub> = 1.2 nF, measured from +5.0 V <sub>in</sub> = V <sub>thresLo</sub> to V <sub>Drive</sub> = 2.0 V | t <sub>DL</sub> | -   | 0.5 | 3.5 | μS   |

1. See 5.0 V Detect Thresholds Diagram. 2. Recommended source impedance for 5.0 V supply:  $\leq 0.12 \Omega$ . This will ensure that I<sub>o</sub> x R<sub>source</sub> < V<sub>hyst</sub>, thus avoiding driveout toggling during 5.0 V detect threshold transitions.

V detect threshold transitions.

V<sub>in</sub> should not be allowed to go negative relative to ground.

Mounted on recommended minimum PCB pad on FR4, 2–oz. copper circuit board.

AC specs are guaranteed by characterization, but not production tested after characterization.

See Figure 3. Application Block Diagram.

See Timing Diagram.

# MC33566

## DC ELECTRICAL CHARACTERISTICS (Note 8)

| Characteristic                                    | Symbol               | Min  | Тур | Мах | Unit |

|---------------------------------------------------|----------------------|------|-----|-----|------|

| +5.0 V <sub>in</sub> Supply Voltage Range         | +5.0 V <sub>in</sub> | 4.35 | 5.0 | 5.5 | Vdc  |

| Reverse Leakage Current from Output               | I <sub>reverse</sub> | -    | -   | 25  | μΑ   |

| V <sub>aux</sub> Quiescent Current                | l <sub>qaux</sub>    | -    | _   | 2.0 | mA   |

| +5.0 V <sub>in</sub> Quiescent Current, Operating | l <sub>qvin</sub>    | -    | -   | 10  | mA   |

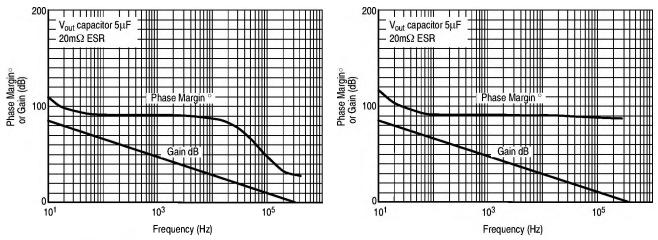

| Load Capacitance (Note 9)                         | Cload                | 4.7  | 22  | _   | μF   |

## **REGULATOR OUTPUT**

| Output Voltage<br>(4.35 V $\leq V_{in} \leq 5.5$ V, 0 mA $\leq I_0 \leq 400$ mA) T <sub>A</sub> = 25°C<br>(T <sub>J</sub> = -5°C to 150°C) | +3.3 V <sub>out</sub> | 3.267<br>3.234 | 3.30<br>3.30 | 3.333<br>3.366 | Vdc |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------|--------------|----------------|-----|

| In-to-Out Voltage (3.9 V $\leq$ V <sub>in</sub> $\leq$ 4.35 V, V <sub>aux</sub> = 3.3 V)                                                   | V <sub>d</sub>        | 3.0            | -            | -              | Vdc |

| Voltage Out at Max Voltage In<br>(V <sub>in</sub> = 7.0 V)                                                                                 | V <sub>outmax</sub>   | 3.1            | 3.3          | 3.5            | Vdc |

| Line Regulation<br>(I <sub>o</sub> = 400 mA)                                                                                               | Linereg               | -              | -            | 0.4            | %   |

| Load Regulation<br>(I <sub>o</sub> = 0 to 400 mA)                                                                                          | Loadreg               | -              |              | 0.8            | %   |

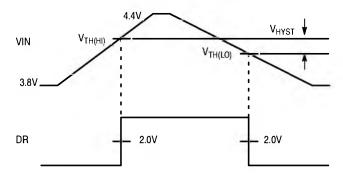

## 5.0 V DETECT

| Low Threshold Voltage<br>(+5.0 V <sub>in</sub> Falling, I <sub>o</sub> = 400 mA) | V <sub>thresLo</sub> | 3.9  | 4.05 | -    | Vdc |

|----------------------------------------------------------------------------------|----------------------|------|------|------|-----|

| High Threshold Voltage<br>(+5.0 V <sub>in</sub> Rising, I <sub>o</sub> = 400 mA) | V <sub>thresHi</sub> | -    | 4.2  | 4.35 | Vdc |

| Hysteresis                                                                       | V <sub>hyst</sub>    | 0.05 | -    | -    | Vdc |

## DRIVE OUTPUT

| Output Peak Source Current<br>(+5.0 V <sub>in</sub> > V <sub>thresHi</sub> )              | I <sub>peak</sub> | 15  | -   | -   | mA   |

|-------------------------------------------------------------------------------------------|-------------------|-----|-----|-----|------|

| Output Peak Sink Current<br>(+5.0 V <sub>in</sub> < V <sub>thresLo</sub> )                | I <sub>peak</sub> | 15  | 1   | -   | mA   |

| Low Output Voltage<br>(I <sub>oL</sub> = 200 μA, V <sub>in</sub> < V <sub>thresLo</sub> ) | V <sub>oL</sub>   | -   | 100 | 200 | mVdc |

| High Output Voltage<br>(I <sub>oH</sub> = 200 μA)                                         | V <sub>oH</sub>   | 3.4 | 1   | -   | Vdc  |

8.  $-5^{\circ}C < T_a < 70^{\circ}C$ , 4.35 V < V<sub>in</sub> < 5.5 V, C<sub>load</sub>  $\ge$  4.7  $\mu$ F unless otherwise noted. 9. 4.7  $\mu$ F minimum over temperature; 22  $\mu$ F recommended; 500 m $\Omega$  ESR maximum.

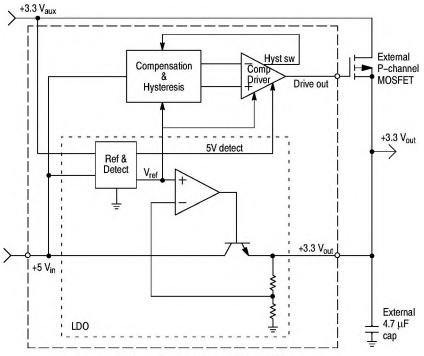

Figure 2. Functional Block Diagram

#### FUNCTIONAL DESCRIPTION

**Input Blocking** – The internal NPN pass transistor of the LDO regulator ensures that no significant reverse current will flow from  $+3.3 V_{out}$  back to the  $+5.0 V_{in}$  input when the 5.0 V input is not powered and the 3.3  $V_{in}$  supply is present.

**5.0 Volt Detect** – Internal circuitry detects the presence of the 5.0 V input supply. When the 5.0 V supply drops below a given threshold, the +3.3 V<sub>in</sub> bypass transistor (an external P–channel MOSFET) is enabled. The 5.0 V detect logic is active throughout the entire range of ramp–up from 0 to 5.5 V. Additionally, the drive out signal is never turned ON or OFF inappropriately during ramp–up of the +5.0 V<sub>in</sub> supply. Also, +3.3 V<sub>out</sub> never drops below 3.0 V while +5.0 V<sub>in</sub> is above the 5.0 V detect minimum threshold.

**Glitch-free Transfer** – The design of the 5.0 V detect circuitry and drive out control circuitry guarantees that the  $+3.3 V_{out}$  will not exceed the output voltage specification listed in the table of DC Operating Specifications even with  $+5.0 V_{in}$  ramping up and down at the extremes of the slew rates in the table of AC Operating Specifications.

**Offset Voltage Performance** – To ensure performance when external offsets are present on the  $+5.0 V_{in}$  and  $+3.3 V_{in}$  power inputs, the device has been designed to be capable of operating with either one or both of these inputs rising from or falling to zero volts, or with offsets of 0.05 V to 0.9 V as the inputs ramp up and down.

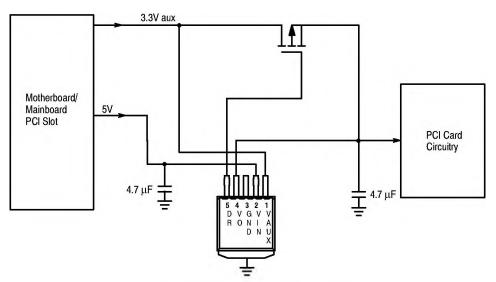

Figure 3. Application Block Diagram

## MC33566

NOTE:

NOTE:

(1)  $V_{in}$  rise and fall times (10% to 90%) to be  $\geq$  100  $\mu s.$

Figure 4. 5.0 V Detect Thresholds Diagram

Figure 5. Timing Diagram

(1)  $V_{in}$  rise and fall times (10% to 90%) to be  $\leq$  100 ns.

**NOTE:**  $V_{out}$  capacitor  $\ge 4.7 \ \mu$ F over operating temperature range. Maximum ESR permissable = 500 m $\Omega$  over operating temperature range.

> Figure 6. Predicted Gain and Phase at Zero Load Current

Figure 7. Predicted Gain and Phase at Full Load Current