# Advanced Information Lithium Battery Protection Circuit for Three Battery Packs

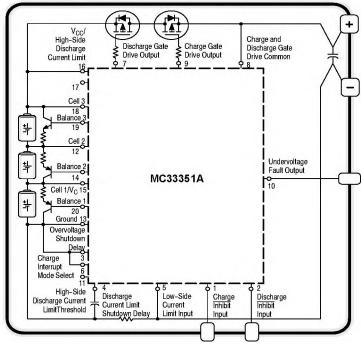

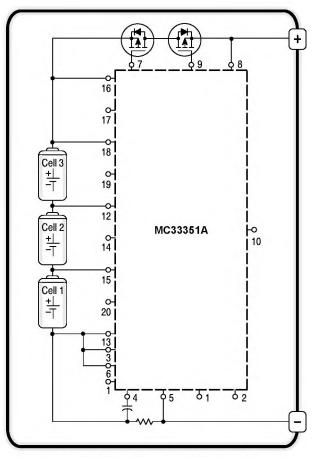

The MC33351A is a monolithic lithium battery protection circuit that is designed to enhance the useful operating life of three cell rechargeable battery packs. The MC33351A is specifically designed to be placed in a lithium battery pack where the battery cells continuously power it. In order to maintain cell operation within specified limits, the protection circuit senses cell voltages, and discharge current, and correspondingly controls the state of two P-channel MOSFET switches. These switches are connected in series with the positive terminal of the third cell and the positive terminal of the battery pack. During a fault condition, the MC33351A open circuits the pack by turning off one of these MOSFET switches.

# Features

- Selectable Charge Interrupt Voltage Sensing Mode for Precise Cell Voltage Measurements

- Programmable Overvoltage Delay

- Choice of Discharge Current Limit Sensing Elements consisting of either Low-Side Resistor or High-Side MOSFET Switches

- Programmable Discharge Current Limit Threshold and Shutdown Delay

- Selectable Cell Voltage Balancing

- Virtually Zero Current Sleepmode State when Cells are Discharged

- Minimum External Components for Inclusion within the Battery Pack

- Available in Low Profile Surface Mount Package

### Typical Three Cell Smart Battery Pack

http://onsemi.com

# ORDERING INFORMATION

| Device          | Device Package |                |

|-----------------|----------------|----------------|

| MC33351ADTB-1   | TSSOP-20       | 75 Units/Rail  |

| MC33351ADTB-1R2 | TSSOP-20       | 2500 Tape/Reel |

#### Smart Battery Pack with High-Side Discharge Current Sensing

http://onsemi.com 1182

Microcontroller Output Ports

# MAXIMUM RATINGS

| Ratings                                                 | Symbol           | Value      | Unit |

|---------------------------------------------------------|------------------|------------|------|

| Input Voltage (Measured with respect to Ground, Pin 13) | V <sub>IR</sub>  |            | V    |

| Cell 1/Vc (Pin 15)                                      |                  | 7.5        |      |

| Cell 2 (Pin 12)                                         |                  | 10         |      |

| Cell 3 (Pin 18)                                         |                  | 18         |      |

| Vcc/ High Side Discharge Current Limit (Pin 16)         |                  | 20         |      |

| Charge Inhibit Input (Pin 1)                            |                  | 7.5        |      |

| Discharge Inhibit Input (Pin 2)                         |                  | 7.5        |      |

| Overvoltage Shutdown Delay (Pin 3)                      |                  | 7.5        |      |

| Discharge Current Limit Shutdown Delay (Pin 4)          |                  | 20         |      |

| Low-Side Discharge Current Limit Input (Pin 5)          |                  | 7.5        |      |

| Voltage Sampling Mode Select (Pin 6)                    |                  | 7.5        |      |

| Discharge Gate Drive Output (Pin 7)                     |                  | 18         |      |

| Charge Gate Drive Common (Pin 8)                        |                  | 20         |      |

| Charge Gate Drive Output (Pin 9)                        |                  | 18         |      |

| Undervoltage Fault Output (Pin 10)                      |                  | 20         |      |

| High–Side Current Limit Threshold (Pin 11)              |                  | 7.5        |      |

| Cell Balancing Current (Note 1)                         | I <sub>bal</sub> |            | mA   |

| Balance 3, Source Current (Pin 19)                      |                  | 50         |      |

| Balance 1, Balance 2 Sink Current (Pin 20, 14)          |                  | 50         |      |

| Undervoltage Fault Output Sink Current (Pin 10)         | l <sub>flt</sub> | 10         | mA   |

| Thermal Resistance, Junction-to-Air                     | R <sub>θJA</sub> |            | °C/W |

| DTB Suffix, TSSOP Plastic Package, Case 948E            | 00/1             | 135        |      |

| DW Suffix, SO–20L Plastic Package, Case 751D            |                  | 105        |      |

| Operating Temperature (Note 1)                          | TJ               | -40 to 150 | °C   |

| Storage Temperature                                     | T <sub>stg</sub> | -55 to 150 | °C   |

**ELECTRICAL CHARACTERISTICS** ( $V_{cell 3}$  (Pin 18) = 10.5V,  $V_{cell 2}$  (Pin 12) = 7.0V,  $V_{cell 1}$  (Pin 15) = 3.5V,  $C_{dly}$  (Pin 4) = 1000 pF,  $T_A = 25^{\circ}C$ )

| Characteristic                                                 | Symbol                   | Min   | Тур                           | Max   | Unit |

|----------------------------------------------------------------|--------------------------|-------|-------------------------------|-------|------|

| VOLTAGE SENSING                                                |                          |       |                               |       |      |

| Cell Charging Cutoff (Pin 15 to 13, 12 to 15, 18 to 12)        |                          |       |                               |       |      |

| Overvoltage Threshold, V <sub>Cell</sub> Increasing MC33351A-1 | V <sub>th(OV)</sub>      | 4.207 |                               | 4.293 | v    |

| Overvoltage Hysteresis, V <sub>Cell</sub> Decreasing           | V <sub>H</sub>           | 50    | 125                           | 200   | mV   |

| Delay                                                          | t <sub>dly(OV)</sub>     |       |                               |       |      |

| One Overvoltage Sample (Pin 3 = Gnd)                           |                          | 0     | -                             | 1.2   | s    |

| Two Consecutive Overvoltage Samples (Pin 3 = Vc)               |                          | 1.0   | -                             | 2.3   | s    |

| Cell Discharging Cutoff MC33351A-1                             | V <sub>th(UV)</sub>      | 2.185 | 2.3                           | 2.415 | V    |

| Undervoltage Threshold, V <sub>Cell</sub> Decreasing           |                          |       |                               |       |      |

| Input Bias Current During Cell Voltage Sampling                | I <sub>IB</sub>          | -     | 28                            | -     | μΑ   |

| Cell Voltage Sampling Rate                                     | t <sub>(smpl)</sub>      | -     | 1.0                           | -     | s    |

| Charge Interrupt                                               | V <sub>th(Intrrpt)</sub> |       |                               |       | V    |

| Input Voltage Range (Pin 6)                                    |                          |       |                               |       |      |

| Enabled                                                        |                          | _     | $(V_c/2+0.2 \text{ to } V_c)$ | _     |      |

| Disabled                                                       |                          | -     | (0 to V <sub>c</sub> /2–0.2)  | _     |      |

| Enabled Charge Interrupt Time                                  | t <sub>Intrrp</sub>      | _     | 20                            | _     | ms   |

NOTE: 1 Maximum package power dissipation limits must be observed.

# **ELECTRICAL CHARACTERISTICS** ( $V_{cell 3}$ (Pin 18) = 10.5V, $V_{cell 2}$ (Pin 12) = 7.0V, $V_{cell 1}$ (Pin 15) = 3.5V, $C_{dly}$ (Pin 4) = 1000 pF, $T_A = 25^{\circ}C$ )

| Characteristic                                                    | Symbol                    | Min     | Тур               | Max | Unit |

|-------------------------------------------------------------------|---------------------------|---------|-------------------|-----|------|

| CELL VOLTAGE BALANCING                                            |                           | ·       |                   |     |      |

| Internal Balancing MOSFET On-Resistance                           | R <sub>DS(on)</sub>       |         |                   |     | Ω    |

| Balance 3, (Pin 19)                                               |                           | -       | 100               | -   |      |

| Balance 1, Balance 2 (Pin 20, 14)                                 |                           | -       | 50                | -   |      |

| CURRENT SENSING                                                   |                           |         |                   |     |      |

| High-Side Discharge Current Limit (Pin 16 to Pin 8)               |                           |         |                   |     |      |

| Threshold Voltage                                                 | V <sub>th(HSdschg)</sub>  |         |                   |     |      |

| R <sub>pin 11</sub> = 1.0 MΩ                                      | ( 0)                      | 200     | 280               | 380 | mV   |

| $R_{pin \ 11} = 2.0 M\Omega$                                      |                           | 100     | 170               | 230 | mV   |

| Delay                                                             |                           |         |                   |     |      |

| Overcurrent Detect (V <sub>sense</sub> = 250 mV)                  | t <sub>dly(HSdschg)</sub> | 2.5     |                   | 6.0 | ms   |

| Short Circuit Detect (V <sub>sense</sub> = 1.0 V)                 |                           | 0.0     |                   | 2.5 | ms   |

| Low-Side Discharge Current Limit (Pin 13 to Pin 5)                |                           |         |                   |     |      |

| Threshold Voltage                                                 | V <sub>th(LSdschg)</sub>  | 48      | _                 | 59  | mV   |

| Delay                                                             | (;                        |         |                   |     |      |

| Overcurrent Detect (V <sub>sense</sub> = 50 mV)                   | t <sub>dly(LSdschg)</sub> | 2.5     |                   | 6.0 | ms   |

| Short Circuit Detect (V <sub>sense</sub> = 200 mV)                |                           | 0.3     |                   | 0.4 | ms   |

| LOGIC                                                             |                           |         |                   |     |      |

| Charge and Discharge Inhibit Inputs (Pin 1, 2)                    |                           |         |                   |     |      |

| Threshold Voltage                                                 | V <sub>th(inhbt)</sub>    | -       | V <sub>c</sub> /2 | -   | V V  |

| Propagation Delay to Respective Gate Drive Output                 | t <sub>PL/H</sub>         | - 1 ÷ 1 | 100               | -   | μs   |

| Undervoltage Fault Output (Pin 10)                                |                           |         |                   |     |      |

| Low State Sink Resistance                                         |                           | -       | 100               | -   | Ω    |

| Off State Leakage Current (V <sub>drain</sub> = 16V)              |                           | _       | 100               | -   | nA   |

| Detection Delay Time Before Discharge MOSFET Turn Off<br>(Note 2) |                           | -       | 16                | -   | s    |

| Charge and Discharge Gate Drive Outputs (Pin 9, 7)                |                           |         |                   |     | Ω    |

| High State Source Resistance                                      | R <sub>DS(source)</sub>   | -       | 100               | -   |      |

| Low State Sink Resistance                                         | R <sub>DS(sink)</sub>     | -       | 100               | -   |      |

| TOTAL DEVICE                                                      |                           |         |                   |     | -    |

| Average Cell Current                                              | I <sub>CC</sub>           |         |                   |     |      |

| Operating (V <sub>CC</sub> = 12 V)                                |                           | -       | 15                | 20  | μA   |

| Sleepmode (V <sub>CC</sub> = 6.0 V)                               |                           | -       | -                 | 500 | nA   |

| Minimum Operating Cell Voltage                                    | V <sub>CC</sub>           |         |                   |     | V    |

| Cell 1 Voltage                                                    |                           | 1.5     | 1.8               | -   |      |

| Cell 2, or Cell 3 Voltage                                         |                           | 0.7     | 0.8               | -   |      |

NOTE: 2 Refer to "Voltage Sensing" text of Operating Description. Guaranteed by Design Only; NOT TESTED.

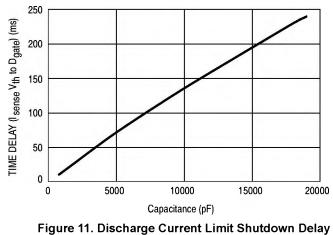

versus Capacitance

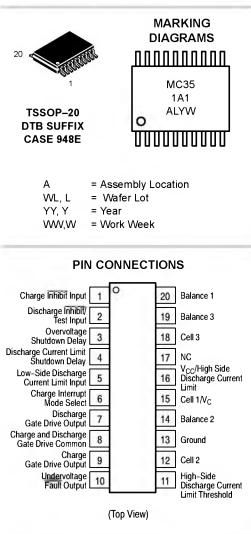

# PIN FUNCTION DESCRIPTION

| Pin<br>No. Function |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Function Description                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                   | Charge Inhibit Input                                                                                                                                                                                                                                                                                                                                                                                                                                                               | A logic low level at this input will disable battery pack charging. A 10 k internal pull–up resistor connects from this pin to $V_{\rm C}{\rm .}$                                                                                                                                                                                                        |  |  |  |

| 2                   | Discharge Inhibit Input                                                                                                                                                                                                                                                                                                                                                                                                                                                            | A logic low level at this input will disable battery pack discharging. A 10 k internal pull–up resistor connects from this pin to $V_c$ . Also, connecting this pin to 3.0V above $V_c$ the internal logic is held in reset state and both MOSFET switches are turned on.                                                                                |  |  |  |

| 3                   | Overvoltage Shutdown<br>Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                      | This input controls the required number of cell overvoltage events that must be detected before charge switch Q1 is turned off. With a logic level low at this input, charge switch Q1 turns off after a single overvoltage event is detected. With a logic level high, charge switch Q1 turns off after two successive overvoltage events are detected. |  |  |  |

| 4                   | Discharge Current<br>Limit Shutdown Delay                                                                                                                                                                                                                                                                                                                                                                                                                                          | A capacitor connects from this pin to ground and is used to program a time delay from when the discharge current limit is exceeded to when discharge switch Q2 is turned off.                                                                                                                                                                            |  |  |  |

| 5                   | Low–Side Discharge<br>Current Limit Input                                                                                                                                                                                                                                                                                                                                                                                                                                          | This pin is used to monitor the load induced voltage drop that appears across current sensing resisto $R_{lim(LS)}$ . This voltage drop is sensed by pins 13 and 5.                                                                                                                                                                                      |  |  |  |

| 6                   | Charge Interrupt Mode<br>Select                                                                                                                                                                                                                                                                                                                                                                                                                                                    | The logic level that is applied to this input determines if the charge current will be interrupted during the cell voltage sampling period. The charge current is interrupted when this input is connected to $V_C$ and not interrupted when connected to ground, pin 13.                                                                                |  |  |  |

| 7                   | Discharge Gate Drive<br>Output                                                                                                                                                                                                                                                                                                                                                                                                                                                     | This output connects to the gate of discharge switch Q2 allowing it to enable or disable battery pack discharging.                                                                                                                                                                                                                                       |  |  |  |

| 8                   | Charge and Discharge<br>Gate Drive Common                                                                                                                                                                                                                                                                                                                                                                                                                                          | This pin provides a gate turn-off path for charge switch Q1. The charge switch source and the batter<br>pack positive terminal connect to this point.                                                                                                                                                                                                    |  |  |  |

| 9                   | Charge Gate Drive<br>Output                                                                                                                                                                                                                                                                                                                                                                                                                                                        | This output connects to the gate of charge switch Q1 allowing it to enable or disable battery pack charging.                                                                                                                                                                                                                                             |  |  |  |

| 10                  | Undervoltage Fault<br>Output                                                                                                                                                                                                                                                                                                                                                                                                                                                       | This is an open drain output that is active low when an undervoltage fault limit has been exceeded. Discharge switch Q2 will turn off 16 seconds after the Fault goes low.                                                                                                                                                                               |  |  |  |

| 11                  | High–Side Discharge<br>Current Limit<br>Threshold                                                                                                                                                                                                                                                                                                                                                                                                                                  | A resistor connects from this pin to ground and is used to program the high-side discharge current limit threshold. The programmed threshold voltage is sensed by pins 16 and 8.                                                                                                                                                                         |  |  |  |

| 12                  | Cell 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | This pin connects to a high impedance node of the Cell Selector where it is used to monitor the positive terminal of Cell 2 and the negative terminal of Cell 3.                                                                                                                                                                                         |  |  |  |

| 13                  | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | This is the protection IC ground and all voltage ratings are with respect to this pin.                                                                                                                                                                                                                                                                   |  |  |  |

| 14                  | Balance 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | This pin is used if cell balancing is desired. It connects to the drain of an internal N-channel MOSFE and is active low during the balancing of Cell 2.                                                                                                                                                                                                 |  |  |  |

| 15                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 16                  | V <sub>CC</sub> /High–Side This is a multi–function pin that connects to a high impedance node of the Cell Selector where is used to monitor the positive terminal of Cell 3 and to provide positive supply voltage for the prot   Limit IC. This pin can also be used for high–side discharge current limit protection by monitoring the linduced voltage drop that appears across the on–resistance of switches Q2 and diode of Q1. T   voltage drop is sensed by pins 16 and 8. |                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 17                  | NC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | No Connection                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 18                  | Cell 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | This pin connects to a high impedance node of the Cell Selector where it is used to monitor the positive terminal of Cell 3 and V <sub>CC</sub> .                                                                                                                                                                                                        |  |  |  |

| 19                  | Balance 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | This pin is used if cell balancing is desired. It connects to the drain of an internal P–channel MOSFET and is active high during the balancing of Cell 3.                                                                                                                                                                                               |  |  |  |

| 20                  | Balance 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | This pin is used if cell balancing is desired. It connects to the drain of an internal N-channel MOSFE and is active low during the balancing of Cell 1.                                                                                                                                                                                                 |  |  |  |

# PROTECTION CIRCUIT OPERATING MODE TABLE

|                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Outputs                                            |                                                    |                                                    |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------|--|

|                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    | MOSFET Switches<br>(Note 3)                        |                                                    |  |

| Input Conditions<br>Cell Status                                                                                                                                                                                                                                                                             | Circuit Operation<br>Battery Pack Status                                                                                                                                                                                                                                                                                                                                                                                                          | Charge<br>Q1                                       | Discharge<br>Q2                                    | Balancing<br>Outputs                               |  |

| CELL CHARGING/DISCHARGING                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |                                                    |                                                    |  |

| Storage or Nominal Operation:<br>No current or voltage faults                                                                                                                                                                                                                                               | Both Charge MOSFET Q1 and Discharge MOSFET Q2 are on. The battery pack is available for charging or discharging.                                                                                                                                                                                                                                                                                                                                  | On                                                 | On                                                 | Active                                             |  |

| CELL CHARGING FAULT/RESET                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |                                                    |                                                    |  |

| Charge Voltage Limit Fault:<br>$V_{Cell} \ge V_{th(OV)}$ for $t_{dly(OV)}$<br>$t_{dly(OV)} =$<br>0 to 1.2 s, Pin 3 to 13<br>1.0 to 2.1 s, Pin 3 to 15                                                                                                                                                       | Charge MOSFET Q1 is latched off and the cells are<br>disconnected from the charging source. An internal<br>hysteresis voltage is generated when the overvoltage<br>cell is sensed. The shutdown delay is programmable<br>for either one or two successive overvoltage events<br>by the state of Pin 3. The battery pack is available for<br>discharging.                                                                                          | On to Off                                          | On                                                 | Active                                             |  |

| Charge Voltage Limit Reset: $V_{Cell}$ < $(V_{th(OV)} - V_H)$ for 1.2 s                                                                                                                                                                                                                                     | Charge MOSFET Q1 will turn on when the voltage<br>across the overvoltage cell talls sufficiently to overcome<br>the internal hysteresis voltage. This can be<br>accomplished by applying a load to the battery pack.                                                                                                                                                                                                                              | Off to On                                          | On                                                 | Active                                             |  |

| CELL DISCHARGING FAULT/RES                                                                                                                                                                                                                                                                                  | ET                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                    |                                                    |                                                    |  |

| $\begin{array}{l} \text{Discharge Current Limit Fault:} \\ V_{\text{Pin 16}} \geq (V_{\text{Pin 8}} + Vth_{(\text{HS dschg})} \\ \text{for } t_{\text{dly(HS dschg})} \text{ or} \\ V_{\text{Pin 5}} \geq (V_{\text{Pin 13}} + V_{th(\text{LS dschg})} \\ \text{for } t_{\text{dly(LS dschg})} \end{array}$ | Discharge MOSFET Q2 is latched off and the cells<br>are disconnected from the load. Q2 will remain in<br>the off state as long as $V_{Pin 16}$ exceeds $V_{Pin 8}$ by<br>$\approx V_{TH(HSdschrg)}$ . A discharge current limit fault can be<br>activated by either high–side or a low–side current<br>sensing methods. The battery pack is available for<br>charging.                                                                            | On                                                 | On to Off                                          | Active                                             |  |

| Discharge Current Limit Reset:<br>V <sub>Pin 16</sub> - V <sub>Pin 8</sub> < V <sub>TH(HSdschrg)</sub><br>V <sub>Pin 5</sub> - V <sub>Pin 13</sub> < V <sub>TH(LSdschrg)</sub>                                                                                                                              | The Sense Enable circuit will reset and turn on discharge MOSFET Q2 when $V_{Pin 16}$ no longer exceeds $V_{Pin 8}$ by 2.0 V. This can be accomplished by either disconnecting the load from the battery pack, or by connecting the battery pack to the charger.                                                                                                                                                                                  | On                                                 | Off to On                                          | Active                                             |  |

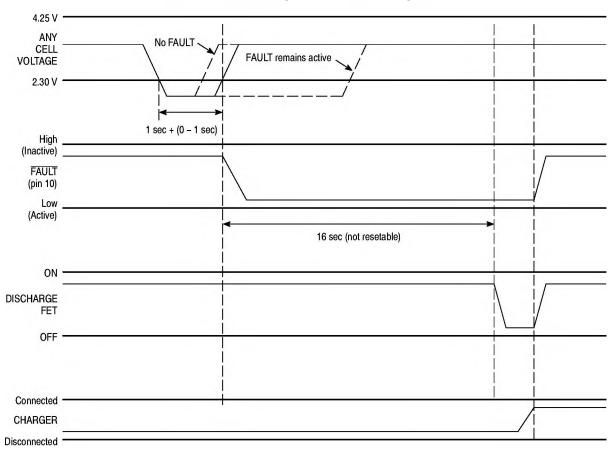

| Discharge Voltage Limit Fault: $V_{Cell} \leq V_{th(UV)} \text{ for } 2.1 \text{ s}$                                                                                                                                                                                                                        | ult: Undervoltage Fault Output (Pin 10) is driven low<br>after two successive undervoltage events are<br>detected. After a 16 second delay, discharge<br>MOSFET Q2 is latched off, the cells are<br>disconnected from the load, and the protection<br>circuit enters a low current sleepmode state. The<br>battery pack is available for charging.                                                                                                |                                                    | On to Off<br>after 16 s                            | Disabled                                           |  |

| Discharge Voltage Limit Reset:<br>V <sub>Pin 8</sub> > (V <sub>Pin 16</sub> + 0.6 V)                                                                                                                                                                                                                        | The Sense Enable circuit will reset and turn on discharge MOSFET Q2 when $V_{Pin\;8}$ exceeds $V_{Pin\;16}$ by 0.6 V. This can be accomplished by connecting the battery pack to the charger.                                                                                                                                                                                                                                                     | On                                                 | Off to On                                          | Active                                             |  |

| FAULTY CELL                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                    |                                                    |                                                    |  |

| Simultaneous Charge and<br>Discharge Voltage Limit Faults                                                                                                                                                                                                                                                   | This condition can happen if there is a defective cell<br>in the battery pack. The protection circuit will remain<br>in the sleepmode state until the battery pack is<br>connected to a charger. If Cell 2, or 3 is faulty and a<br>charger is connected, the protection circuit will cycle<br>in and out of sleepmode. If Cell 1 is faulty (<1.5 V)<br>the protection circuit logic will not function and the<br>battery pack cannot be charged. | Cycles<br>Cell 1 Good<br>Disabled<br>Cell 1 Faulty | Cycles<br>Cell 1 Good<br>Disabled<br>Cell 1 Faulty | Cycles<br>Cell 1 Good<br>Disabled<br>Cell 1 Faulty |  |

NOTE: 3 Charge switch Q1 and discharge switch Q2 can be selectively turned off via the appropriate inhibit input except during the sleepmode state.

#### **OPERATING DESCRIPTION**

#### INTRODUCTION

The demand for smaller lightweight portable electronic equipment has dramatically increased the requirements of battery performance. Today's most attractive chemistries include lithium–polymer, lithium–ion, and lithium–metal. Each of these chemistries require electronic protection in order to constrain cell operation to within the manufacturers limits.

Rechargeable lithium-based cells require precise charge and discharge termination limits for both voltage and current in order to maximize cell capacity, cycle life, and to protect the end user from a catastrophic event.

The MC33351A features internally–fixed cell voltage limits, programmable cell voltage balancing, low operating current, a virtually zero current sleepmode state, and requires few external components.

#### **OPERATING DESCRIPTION**

The MC33351A is specifically designed to be placed in the battery pack where it can be continuously powered from three lithium cells. In order to maintain cell operation within specified limits, the protection circuit senses both cell voltage and discharge current, and correspondingly controls the state of two P–channel MOSFET switches. These switches, Q1 and Q2, are placed within the series path of the positive terminal of cell 3 and the positive terminal of the battery pack. For lowside current limit sense, a resistor is placed within the series path of the negative terminal of Cell 1 and the negative terminal of the battery pack. This configuration allows the protection circuit to interrupt the appropriate charge or discharge path FET in the event that a programmed voltage or current limit for any cell has been exceeded.

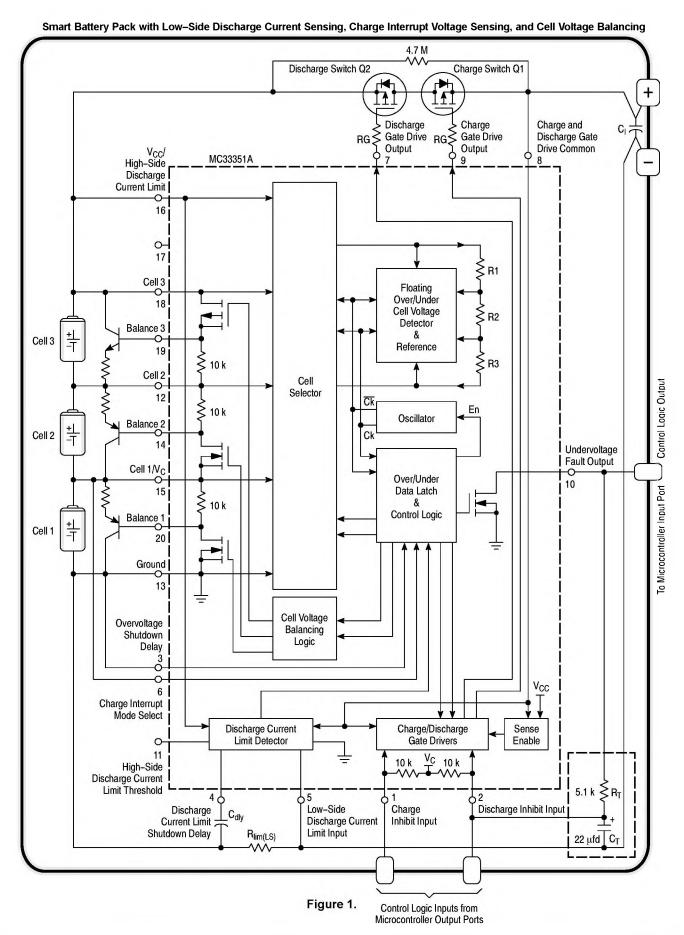

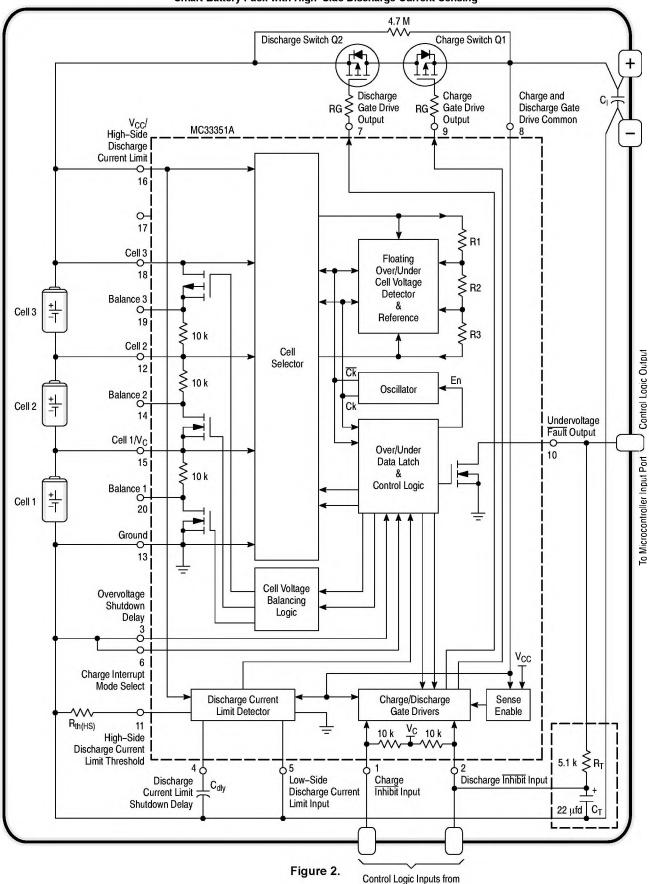

A functional description of the protection circuit blocks follows. Refer to the detailed block diagram shown in Figure 1.

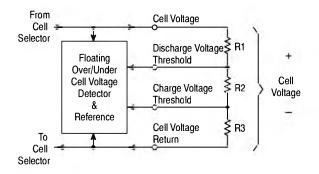

#### Voltage Sensing

Individual cell voltage sensing is accomplished by the use of the Cell Selector in conjunction with the Floating Over/Under Voltage Detector and Reference block. The Cell Selector applies the voltage of each cell across an internal resistor divider string. The voltage at each of the tap points is sequentially polled and compared to an internal reference. If a limit has been exceeded, the result is stored in the Over/Under Data Latch and Control Logic block. The Cell Selector is gated on for a 4.0 ms period at a fixed one second repetition rate. This low duty cycle sampling technique reduces the average load current that the divider presents across each cell, thus extending the useful battery pack capacity.

Figure 12. Simplified Smart Battery Pack

| Polling<br>Sequence | Time<br>(ms) | Cell<br>Sensed | Tested<br>Limit |

|---------------------|--------------|----------------|-----------------|

| 1                   | 0.25         | Cell 1         | Overvoltage     |

| 2                   | 0.25         | Cell 2         | Overvoltage     |

| 3                   | 0.25         | Cell 3         | Overvoltage     |

| 4                   | 0.25         | Cell 1         | Undervoltage    |

| 5                   | 0.25         | Cell 2         | Undervoltage    |

| 6                   | 0.25         | Cell 3         | Undervoltage    |

Cell Sensing Sequence

By incorporating this polling technique with a single floating comparator and voltage divider, a significant reduction of circuitry and trim elements is achieved. This results in a smaller die size, lower cost, and reduced operating current.

Figure 13. Cell Voltage Limit Sampling vs. Programming

The cell charge and discharge voltage limits are controlled by the values selected for the internal resistor divider string. As the battery pack reaches full charge, the Cell Voltage Detector will sense an overvoltage fault condition on the first cell that exceeds the pre-set overvoltage limit. The fault information is stored in a data latch and charge MOSFET Q1 is turned off, disconnecting the battery pack from the charging source. An internal current source pull-up is then applied to the lower tap of the divider when the overvoltage cell is again sensed. This creates an input hysteresis voltage with divider resistors R1 and R2. As a result of an overvoltage fault, the battery pack is available for discharging only.

The overvoltage fault is reset by applying a load to the battery pack. As the voltage across the highest voltage cell falls below the hysteresis level, charge MOSFET Q1 will turn on and the current source pull-up will turn off. The battery pack will now be available for charging or discharging.

As the load eventually depletes the battery pack charge, the Cell Voltage Detector will sense an undervoltage fault condition on the first cell that falls below the designed undervoltage limit. After an undervoltage cell is detected, undervoltage fault output goes low and discharge MOSFET Q2 is turned off, disconnecting the battery pack from the load after 16 seconds. The protection circuit will now enter a low current sleepmode state drawing less than 15.0 nA typically, thus preventing any further cell discharging. As a result of the undervoltage fault, the battery pack is available for charging only. An alternate method of turning discharge MOSFET Q2 can be employed using  $R_T$  and  $C_T$  as shown in Figures 1 and 2. Recommended value of  $R_T$  and  $C_T$  of 5.1 k $\Omega$  and 22 ufd respectively generates a time delay of 110  $\pm 10\%$  milliseconds.

The undervoltage fault is reset by applying charge current to the battery pack. When the voltage on Pin 8 exceeds Pin 16 by 0.6 V, discharge MOSFET Q2 will be turned on. The battery pack will now be available for charging or discharging.

#### **Cell Voltage Balancing**

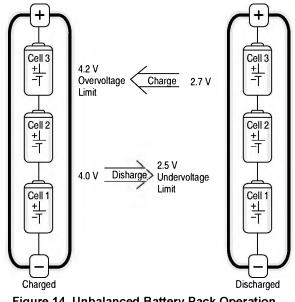

With series connected cells, successive charge and discharge cycles can result in a significant difference in cell voltage with a corresponding degradation of battery pack

capacity. Figure 13 illustrates the operation of an unbalanced three cell pack. As the cells become unbalanced, the full battery pack capacity is not realized. This is due to the requirement that charging must terminate when the highest voltage cell reaches the overvoltage limit, and discharging must terminate when the lowest voltage cell reaches the undervoltage limit. By employing a method of keeping the cell voltages equal, each of the cells can be charged and discharged to their specified limits, thus attaining the maximum possible capacity.

Figure 14. Unbalanced Battery Pack Operation

The MC33351A contains a Cell Voltage Balancing Logic circuit that controls three internal MOSFETs. These MOSFETs are connected to an external transistor and resistor combination across the individual cells. The circuit samples the voltage of each cell during the polling period. If all of the cells are below the programmed overvoltage fault limit, no cell balancing takes place. If one or more cells reach the overvoltage fault limit, a specific latch is set for each cell. At the end of the polling period, charge MOSFET O1 is turned off and the latches are interrogated. If all of the latches were set, no cell balancing takes place. If one, two, or three latches were set, the required cell balancing MOSFETs are then activated. The overvoltage cells are discharged to the pre-set level. As each cell attains this level, the balancing MOSFETs successively turn off. Upon completion of cell balancing, charge MOSFET Q1 is turned on. Cell voltage balancing can be active during charging and discharging, but is disabled during the low current sleepmode state.

## **Test Mode**

*A* test option is provided to speed up device and battery pack testing. By connecting Pin 2 to 3.0 V above  $V_c$  the internal logic is held in a reset state and both MOSFET switches are turned on. Upon release, the Control Logic becomes active and the cell are polled within 4.0 ms.

### **Discharge Current Sensing**

Discharge current limit protection can be selectively added to the battery pack with the addition of a sense resistor  $R_{lim(dschg)}$  on the Low–Side or by monitoring the voltage drop across the series FETs on the High–Side.

#### Sense resistor - low-side

The sense resistor  $R_{lim(dschg)}$  is placed in series with the negative terminal of Cell 1 and the negative terminal of the battery pack. Refer to Figure 1.

As the battery pack discharges, Pins 5 and 13 sense the voltage drop across  $R_{Lim(dschg)}$ .

A discharge current limit fault is detected if the voltage at Pin 5 is greater than Pin 13 by **50 mV for more than 3.0 ms**. The fault information is stored in a data latch and discharge MOSFET Q2 is turned off. disconnecting the battery pack from the load. As a result of the discharge current fault, the battery pack is available for charging only. The discharge current limit is given by:

$$I_{\text{Lim}(\text{dschg})} = \frac{V_{\text{th}(\text{dschg})}}{R_{\text{Lim}(\text{dschg})}} = \frac{50 \text{ mV}}{R_{\text{Lim}(\text{dschg})}}$$

#### Voltage across FETs – high-side

A  $1M\Omega$  or  $2M\Omega$  resistor connected from pin# 11 to ground is used to program the high–side discharge current limit threshold.

The discharge current fault is reset by either disconnecting the load from the battery pack, or by connecting the battery pack to the charger. When the voltage on Pin 16 no longer exceeds Pin 8 by approximately 2.0 V, the Sense Enable circuit will turn on discharge MOSFET Q2. Discharge current sensing can be disabled by connecting Pin 16 to Pin 8.

The discharge current protection *circuit contains a built* in response delay of 3.0 ms. This helps to prevent fault activation when the battery pack is subjected to pulsed currents during charging or discharging.

#### **Battery Pack Application**

Each of the application figures show a capacitor labeled C<sub>1</sub> that connects directly across the battery pack terminals, and two resistors labeled R<sub>g</sub> that are placed in series with the charge and discharge gate drive outputs. These components prevent excessive currents from flowing into the MC33351A when the battery pack terminals are shorted or arced and are **mandatory**. Capacitor C<sub>1</sub> is *a* 1.0  $\mu$ F ±20% *ceramic leaded or surface mount type*. It must be placed directly across the battery pack plus and minus terminals with extremely short lead lengths ( $\leq 1/16^{\circ}$ ) and as close to the IC as possible. The gate drive output resistors for both Q1 and Q2 are 10 k\Omega ±5.0% carbon film type.

In applications where inordinately low leakage MOSFETs are used, the protection circuit may take several seconds to reset from an overcurrent fault after the load is removed. If desired, this situation can be remedied by providing a small leakage path for charging  $C_{t_s}$  thus allowing Pin 8 to rapidly rise, so that it no longer exceeds Pin 16 by approximately 2.0 V. A 4.7 M $\Omega$  resistor placed across the MOSFET switches accomplishes this task with a minimum increase in cell discharge current when the battery pack is connected to the load.

Upon assembly of the battery pack, it is imperative that Cell 1 be connected first so that  $V_c$  is properly biased. The remaining cells can then be connected in any order. This assembly method prevents forward biasing the protection IC substrate which can result in overheating and non–functionality.

# MC33351A – Cell Voltage versus Undervoltage Fault