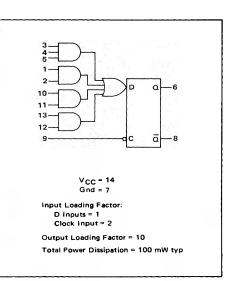

# MC3153F • MC3053F MC3153L • MC3053L,P

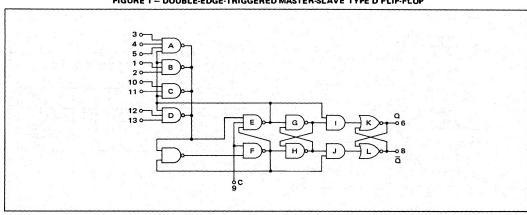

This double-edge-triggered master-slave type D flip-flop accepts data on the rising clock edge and transfers it to the output when the clock input changes back to the logic "O" state. A 4-wide, 2-2-2-3 input AND-OR gate is internally connected to the D input of the flip-flop. This makes the device useful in forming shift registers using one package per bit.

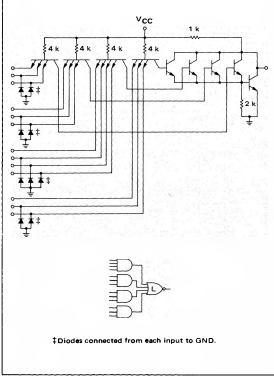

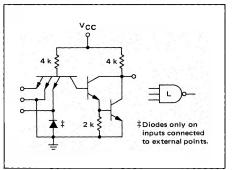

LOW LEVEL "AND-OR-INVERT" GATE

See General Information section for packaging information.

LOW-LEVEL "NAND" GATE

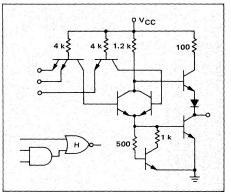

### HIGH LEVEL "AND-OR-INVERT" GATE

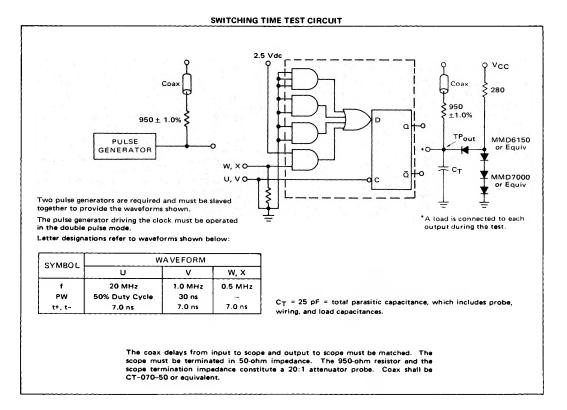

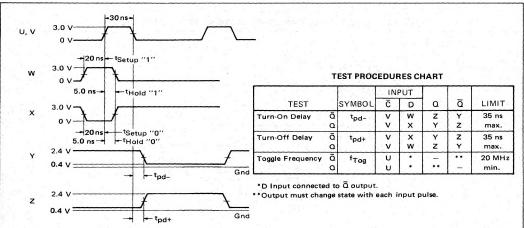

Test procedures are shown for only one of the input AND gates. Furthermore only one input on the AND gate is tested. To complete tasting, test other gates and inputs in the same manner.

|                                                                         |                     |       | -       | T            | L          | )              |                 |              |     |          |         |          |                    |          | G            | -    | -     | -   | -        | >    | N.                                                    | ~     | N   | ~     |       | 7                 | N        | >       | -   |           |

|-------------------------------------------------------------------------|---------------------|-------|---------|--------------|------------|----------------|-----------------|--------------|-----|----------|---------|----------|--------------------|----------|--------------|------|-------|-----|----------|------|-------------------------------------------------------|-------|-----|-------|-------|-------------------|----------|---------|-----|-----------|

|                                                                         |                     |       |         |              | 3          |                | _               |              |     |          |         |          |                    | Temper   | Temperature  | 10   | HO    | 5   | <u>e</u> | -    |                                                       | -     | *   | ARH V | S     | V CCL V CCH V max | HU S     | max     | -   |           |

|                                                                         |                     |       | 10.     | П            | 7          |                |                 |              |     |          |         |          |                    |          | -55°C        | 20.0 | -1.6  | 1.  | 1        | 0.4  | 1.1                                                   | 2.0   | 2.4 | 4.0   | 5.0   | 4.5               | 5.5      |         |     |           |

|                                                                         |                     |       | 0       |              |            | Ĩ              | 0               | 8            |     |          |         | <        | MC3153             | ~        | +25°C        | 20.0 | -1.6  | 1.0 | -10      | 0.4  | 1.1                                                   | 1.8   | 2.4 | 4.0   | 5.0   | 4.5               | 5.5      | 7.0     |     |           |

|                                                                         |                     |       |         |              |            |                |                 |              |     |          |         |          |                    | +        | +125°C       | 20.0 | -1.6  | •   | ,        | 0.4  | 0.8                                                   | 1.8   | 2.4 | 4.0   | 5.0   | 4.5               | 5.5      |         |     |           |

|                                                                         |                     |       |         |              |            |                |                 |              |     |          |         |          |                    | )        | 0°C          | 20.0 | -1.6  | '   | •        | 0.4  | 1.1                                                   | 2.0   | 2.5 | 4.0   | 5.0   | 4.75              | 5.25     | •       |     |           |

|                                                                         |                     |       |         |              |            |                |                 |              |     |          |         | ~        | MC3053             | ~        | +25°C        | 20.0 | -1.6  | 1.0 | -10      | 0.4  | 1.1                                                   | 1.8   | 2.5 | 4.0   | 5.0   | 4.75              | 5.25     | 7.0     |     |           |

|                                                                         |                     |       |         |              |            |                |                 |              |     |          |         | ÷.,      |                    | _        | +75°C        | 20.0 | -1.6  | •   | '        | 0.4  | 0.9                                                   | 1.8   | 2.5 | 4.0   | 5.0   | 4.75              | 5.25     |         |     |           |

|                                                                         |                     | Pin   |         | MC31         | 153 Te     | 53 Test Limits | nits            |              |     |          | MC305   | 3 Tes    | MC3053 Test Limits | s        |              |      |       | TES | T VO     | TAGE | TEST VOLTAGE/CURRENT APPLIED TO PINS LISTED BELOW     | D 10  | SNI | STED  | BELOW |                   |          |         | _   |           |

|                                                                         |                     | Under |         | 2°C          | +25°C      | 2°C            | +125°C          | 5°C          | 0°C |          | +25°C   |          | +75°C              |          | 1            |      | -     | -   | Ľ        | >    | V.                                                    | >     | >   | >     | >     | V V V             | >        | -       | :   | *         |

| Characteristic                                                          | loamyc              | IEST  | win max | XBM          |            | XBM            | XEM MIN XEM MIN | XEW          | UIN | WIN MAX  | XPW UIM |          | MIN MAX            | -        |              | 110. | HO.   | 5   | -        | -    |                                                       | H     | *   | HH    | 8     |                   | HOO.     |         |     | BID       |

| <b>Input</b><br>Forward Current<br>Data<br>Clock                        | $^{\mathrm{I}}_{F}$ | 1 6   |         | -1.6<br>-3.2 | 1.1        | -1.6<br>-3.2   | 1.1             | -1.6<br>-3.2 | i i | -1.6     |         | -1.6     |                    | -1.6     | mAdc<br>mAdc |      |       | 1.1 | 1.1      | 1 6  |                                                       | 1.1   |     | 1 13  | Si i  |                   | 14<br>14 |         |     |           |

| Reverse Current<br>Data<br>Clock                                        | I <sub>R</sub>      | 1 6   |         | 40<br>80     |            | 40<br>80       |                 | 40<br>80     | 1.1 | 40<br>80 |         | 40<br>80 |                    | 40<br>80 | µAdc<br>µAdc | , ,  |       |     |          |      | 11                                                    |       | 9 1 | 1.1   | 1.1   |                   | 14<br>14 | 1.1     | 1.1 | 2,7*      |

| Breakdown Voltage<br>Data<br>Clock                                      | BVin                | 1 6   | 1.1     | 1.1          | 5.5<br>5.5 | 1.1            | 1.1             |              |     | - 1 1    | 5.5     |          |                    |          | Vdc<br>Vdc   |      |       | 1 6 |          | 1 1  | 1.1                                                   |       |     |       | 1.1   |                   | 14<br>14 | · i - i |     | 2,7*<br>7 |

| Clamp Voltage<br>Data<br>Clock                                          | V <sub>D</sub>      | 1 6   | 1.1     |              |            | -1.5<br>-1.5   |                 |              | 1.1 |          | -1.5    |          |                    |          | Vdc<br>Vdc   |      |       | 1.1 | 46       |      |                                                       |       | 1.1 |       | 1.1   | 14<br>14          | 1.1      | 1.1     |     | ~ ~       |

| Output<br>Output Voltage                                                | VOL                 | 9     | i je s  | 0.4          | i          | 0.4            |                 | 0.4          |     | 0.4      |         | 0.4      |                    | 0.4      | Vdc          | 9    |       | '   | '        | '    | 1,2,3,4,5,<br>10,12,13                                | 11    | ı   | 1     | ,     | 14                | 1        | 1       | 6   | 5         |

|                                                                         |                     | ∞     | i,      | 0.4          | .1         | 0.4            | ı               | 0.4          |     | 0.4      | ,       | 0.4      | ,                  | 0.4      | Vdc          | 80   | ́т.   | '   | 1        | '    | 1,                                                    | 12,13 | • • | 1     | 1     | 14                |          | ,       | 6   | 2         |

|                                                                         | V <sub>OH</sub>     | 9 8   | 2.4     | 1.1          | 2.4        |                | 2.4             |              | 2.5 |          | 2.5     | 1 1      | 2.5                |          | Vdc          |      | 50 00 | 1 1 | 1.1      |      | 3, 4, 5, 10, 11, 12, 13<br>1, 3, 4, 5, 10, 11, 12, 13 | 3 1,2 |     | 13    | • •   | 14                |          |         | 66  |           |

| Power Requirements<br>(Total Device)<br>Maximum Power<br>Sumuly Current | Imax                | 14    | I       |              |            | 39             | ,               | . 1          |     |          | 1       | 39       |                    |          | mAdc         |      | '     |     |          | · ·  |                                                       | '     |     |       | ,     | 1                 |          | 14      |     | *-        |

| http://www.com                                                          | IPDH                | 14    | 1       | 30           | ,          | 30             | 1               | 30           |     | 30       |         | 30       | 1                  | 30       | mAdc         | 1    | •     | '   | 1        | -    | ,                                                     | 1     | '   | 1     | •     | 1                 | 14       | ,       | ,   | -         |

-GND

TEST VOLTAGE/CURRENT VALUES

# OPERATING CHARACTERISTICS

Data present at the D inputs 20 ns prior to and 5.0 ns following the rising edge of the clock pulse is stored in the flip-flop until the clock falling edge, when it is transferred to the outputs. The data may change any time except between the setup time (20 ns) and the hold time (5.0 ns) without affecting the outputs.

### VOLTAGE WAVEFORMS AND DEFINITIONS

# APPLICATIONS INFORMATION

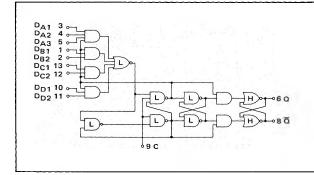

# LOGIC DESCRIPTION

This flip-flop performs the D function, with input logic defined by the following equation:

#### 6 = 1 • 2 + 3 • 4 • 5 + 10 • 11 + 12 • 13

The operation of the flip-flop is as follows (refer to Figure 1). Assume Q is "0". To set a "1" on the Q output, "1" must be applied to all the inputs on either gate A, B, C, or D. When the clock goes high, a "0" appears on the output of gate G and a "1" appears on the output of gate H. However, because the other input to gate J comes from gate G to gate I, the output of gate G and a "1". Appears on the clock goes low, the output of gates E and F go to "1". Thus gate J now has a "1" applied to both inputs and its output goes to "0", and this is coupled to gate K, which now has zero applied to both inputs causing it to go to a "1". The flip-flop has now switched and Q is a "1". Setting a "0" on the output may be followed through in a similar fashion.

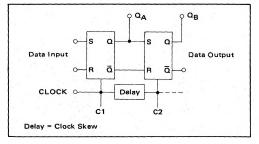

#### SYSTEM SKEW

Clock skew in a system is one of the most difficult problems that the system designer must solve. Consider the clock driver circuitry shown in Figure 2. Clock skew between C1 and C2 could be caused by a number of factors, including unequal loading, unequal wiring distances, and different turn-on and turn-off times between clock line driver gates that may be in the circuit between C1 and C2. Most flip-flops that are presently available in integrated form do not allow the system designer to control the amount of skew in the system. With the MC3153/3053, system clock skew can be adjusted.

Three basic types of flip-flops are now in use: (1) the chargecontrolled flip-flop, (2) the edge-triggered flip-flop, and (3) the master-slave flip-flop. Figure 2 is an example of a system in which the clock skew problem is encountered. The direct-coupled shift register can be made with the two most common types of flipflops -- the negative-edge-triggered flip-flop or the master-slave flipflop.

When negative-edge-triggered flip-flops are used to implement the shift register of Figure 2, the maximum allowable clock skew, Figure 3A, is the propagation delay from the falling edge of the clock to the output of flip-flop A minus the hold time of flip-flop B. It should be noted that the maximum propagation delay time and the minimum hold time from data sheets may not be used to calculate maximum allowable clock skew. Instead, the minimum propagation delay and maximum hold times must be used to calculate maximum clock skew to insure proper system operation over the entire temperature and power supply variations expected.

If the shift register of Figure 2 is constructed with master-slave flip-flops, the maximum allowable clock skew, Figure 3B, is the propagation delay from the falling edge of the clock to the output of flip-flop A plus the time required to transfer and latch the information into the master portion of flip-flop B. The minimum propagation delay and latch times must be used in calculating the maximum clock skew to guarantee proper system operation.

By using MC3153/3053 double-edge-triggered master-slave type D flip-flops in the circuit of Figure 2, the maximum clock skew, Figure 3C, is the propagation delay from the falling edge of the clock to the outout of flip-flop A minus the hold time of flip-flop B plus the clock pulse width. In this case, minimum propagation delay and maximum hold time must be used in the skew calculations. However, since the clock pulse width is part of the clock skew calculation, system clock skew can be adjusted to any value the system designer feels necessary to insure proper operation of the system simply by adjusting the clock pulse width. The ability to adjust clock skew is a feature that cannot be stressed too highly because it gives the system designer freedom from maximum allowable clock skew restrictions.

It should be noted in Figure 3C that the maximum clock frequency for the MC3153/3053 is the reciprocal of the propagation

FIGURE 1 - DOUBLE-EDGE-TRIGGERED MASTER-SLAVE TYPE D FLIP-FLOP

delay plus the hold time plus the system skew. Therefore, as the clock pulse width is increased to provide clock skew adjustment, the maximum operating frequency is reduced.

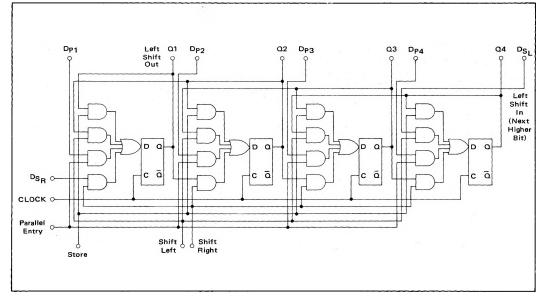

## INPUT LOGIC UTILIZATION

The input logic available on the MC3153/3053 makes this flipflop a very powerful logic block. Figure 4 shows four MC3153/ 3053's wired together to form a universal, clocked, shift register with the following features: (1) serial data entry and shift right, (2) parallel data entry, (3) shift left, and (4) hold the information (store). Since the  $\overline{Q}$ 's are also available, a one's complement could be formed by entering each  $\overline{Q}$  back into its flip-flop. In this shift register, four MC3153/3053's replace four type D flip-flops of another type plus 4-wide AND-OR-INVERT gates.

## FIGURE 2 - DIRECT-COUPLED SHIFT REGISTER

FIGURE 3 - CLOCK SKEW WAVEFORMS

# MC3153, MC3053 (continued)

FIGURE 4 ~ UNIVERSAL CLOCKED SHIFT REGISTER