# **MOS** INTEGRATED CIRCUITS

# PRELIMINARY DATA

# SINGLE CHIP ORGAN (SOLO + ACCOMPANIMENT)

- SIMPLE KEY SWITCH REQUIREMENTS FOR 61 KEYS, IN A MATRIX OF 12 × 6

- LOW TIME REQUIRED FOR A SCANNING CYCLE OF 576 μsec.

- ACCEPTANCE OF ALL KEYS PRESSED

- TWO KEYBOARD FORMATS: 61 KEYS (SOLO) OR 24+37 (M108), 17+44 (M208) KEYS (ACC. + SOLO) WITH POSSIBILITY OF AUTOMATIC CHORDS OF THE "ACCOMPANIMENT" SECTION

- TOP OCTAVE SYTHESIZER INCORPORATED FOR GENERATION OF 3 "FOOTAGES"

- MORE THAN ONE CHIP CAN BE EMPLOYED WITH SYNCHRONIZATION THROUGH THE RESET INPUT

- SEPARATED ANALOG OUTPUTS (FOR EACH FOOT) FOR "SOLO", "ACC." AND "BASS" SECTIONS (SQUARE WAVE 50% D.C.) WITH AVERAGE VALUE CONSTANT

- INTERNAL ANTI-BOUNCE CIRCUITS

- KEY DOWN AND TRIGGER OUTPUTS FOR "SOLO", "ACC." AND "BASS" SECTIONS

- SUSTAIN FOR THE LAST KEYS RELEASED IN THE "SOLO" SECTION

- CHOICE OF OPERATING MODE IN "ACC." SECTION

- MANUAL, WITH OR WITHOUT MEMORIZATION OF THE SELECTED KEYS (FREE CHORDS WITH ALTERNATE BASS)

- AUTOMATIC, WITH OR WITHOUT MEMORIZATION OF THE SELECTED KEY (PRIORITY TO THE LEFT FOR AUTOMATIC CHORDS AND BASS ARPEGGIO)

- MULTIPLE CHOICE POSSIBILITY ON THE CHORDS IN AUTOMATIC MODE

- MAJOR OR MINOR THIRD

- WITH OR WITHOUT SEVENTH

- LOW DISSIPATION OF ≤ 600 mW

- STANDARD SINGLE SUPPLY OF +12V ± 5%

- INPUTS PROTECTED FROM ELECTROSTATIC DISCHARGES

The M108 and M208 are realized on a single monilithic chip using N-channel silicon gate technology. They are available in a 40 lead dual in-line plastic package.

# **ABSOLUTE MAXIMUM RATINGS\***

| V <sub>DD</sub> **<br>V:** | Source supply voltage       | -0.3 to +20 | v  |

|----------------------------|-----------------------------|-------------|----|

| V;**                       | Input voltage               | -0.3 to +20 | V  |

| l <sub>o</sub>             | Output current (at any pin) | 3           | mΑ |

| T <sub>stg</sub>           | Storage temperature         | -65 to 150  | °C |

| T <sub>op</sub>            | Operating temperature       | 0 to 50     | °C |

\* Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other condition above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

\*\* This voltage is with respect to  $V_{SS}$  (GND) pin voltage.

#### ORDERING NUMBERS: M 108 B1 for dual in-line plastic package M 208 B1 for dual in-line plastic package

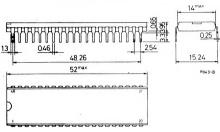

# MECHANICAL DATA (dimensions in mm)

Dual in-line plastic package

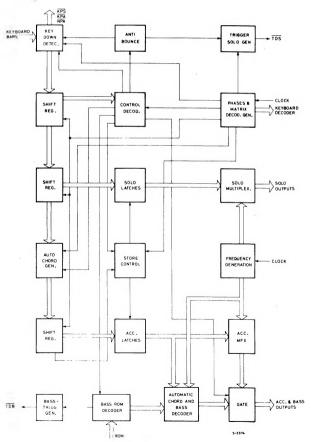

**BLOCK DIAGRAM**

# **PIN CONNECTIONS**

| w Voo                     |   |    |        | 1  |            |

|---------------------------|---|----|--------|----|------------|

| <b>¥</b> <sup>∨</sup> ss  | L | 1  | 41     | Г  | MCK        |

| RESET                     | Q | 2  | 3      | ٩P | TCK        |

| 8th/7th                   | ۵ | 3  | 3      | ۶þ | B1         |

| 475th                     | ۵ | 4  | 3      | p, | B2         |

| 8/3rd                     | C | 5  | 3      | 6þ | <b>B</b> 3 |

| 167 ROOT                  | C | 6  | 3      | ۶þ | B4         |

| BASS                      | C | 7  | 3      | 4þ | B5         |

| A                         | ۵ | 8  | 3      | зþ | B6         |

| в                         | ۵ | 9  | 3      | 20 | F1         |

| С                         | ۵ | 10 | 3      | ۱þ | F2         |

| NPA                       | ۵ | 11 | 3      | ٥þ | F3         |

| TDA                       | ۵ | 12 | 2      | эþ | F4         |

| TDS                       | ۵ | 13 | 2      | 80 | F5         |

| KPA                       | C | 14 | 2      | ۶þ | F6         |

| KPS                       | ۵ | 15 | . 2    | 6  | F7         |

| 16'                       | ۵ | 16 | 2      | ۶þ | F8         |

| 8'                        | ۵ | 17 | 2      | 4þ | F9         |

| 4'                        | ۵ | 18 | 2      | зþ | F10        |

| TEST                      | ۵ | 19 | 2      | 2þ | F 11       |

| <b>**</b> <sup>v</sup> DD | 0 | 20 | 2      | ۱þ | F12        |

|                           |   | L  | 5-3367 | -  |            |

\* V<sub>SS</sub> is the lowest supply voltage

\*\* VDD is the highest supply voltage

# **GENERAL CHARACTERISTICS**

The caracteristics of the M208 are similar to those of the M108; the only difference is the keyboard split, which is 24+37 for the M108 and 17+44 for the M208 when used in "accompaniment + solo" mode.

The circuit comprises:

- a) 2 pins for clock input: one for the matrix scanning, the other for the incorporated T.O.S.; by connecting both the clock inputs to the same matrix scanning clock (1000.12 KHz), the three "footages" generated are 16', 8' and 4'.

- b) 6 inputs from the octave bars (keyboard and control scanning

- c) 3 multiplexed data inputs for addressing the bass selection. These inputs normally come from the outputs of an external memory (negative or positive logic with control inside the chip)

- d) 8 signal outputs divided by section: 3 for the "SOLO" section (16', 8', 4'), 4 for the "ACC." section (16' or root, 8' or 3rd, 4' or 5th, 8th/7th according to operating mode), 1 for the bass

- e) 12 outputs for the matrix scanning

- f) 5 "trigger" and "key down" outputs: KPS (key pressed "SOLO"), TDS (trigger decay "SOLO"), KPA (key pressed "ACC."), NPA (pitch present in "ACC." outputs), TDB (trigger decay "BASS") respectively. These outputs, in conjunction with an external time constant, allow the formation of the envelope of the sustain and percussion effects. The duration of the trigger pulses is ≅ 9 msec.

- g) 1 input (reset) to synchronize the device or more than one device (with the same keyboard scanning and using a single contact per key). The reset action, provided by an external circuit, is of the "POWER ON RESET" (high active) type and its duration must be ≅ 0.5 msec.

- h) 1 TEST pin (in use it must be connected to  $V_{DD}$ )

- i) 2 supply pins.

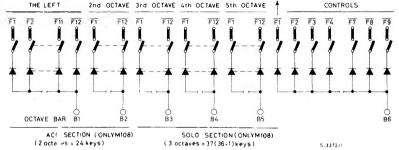

#### MATRIX ORGANIZATION (Keyboard and controls)

| M108/208          |                  |                       |                  | M108/2           | 08 Octave        | bar inputs                   |

|-------------------|------------------|-----------------------|------------------|------------------|------------------|------------------------------|

| Matrix<br>outputs | в1               | <b>B</b> <sub>2</sub> | B <sub>3</sub>   | B <sub>4</sub>   | <b>B</b> 5       | B <sub>6</sub>               |

| $\overline{F_1}$  | c1               | C <sub>2</sub>        | C <sub>3</sub>   | C4               | C <sub>5</sub>   | C <sub>6</sub>               |

| F <sub>2</sub>    | C <sub>1</sub> # | C <sub>2</sub> #      | C <sub>3</sub> # | C <sub>4</sub> # | C <sub>5</sub> # | 7th OFF/7th ON               |

| F <sub>3</sub>    | $D_1$            | D <sub>2</sub>        | D <sub>3</sub>   | $D_4$            | D <sub>5</sub>   | 3rd+/3rd-                    |

| F <sub>4</sub>    | D <sub>1</sub> # | D <sub>2</sub> #      | D <sub>3</sub> # | D4#              | D <sub>5</sub> # | Sust. OFF/Sust. ON           |

| F <sub>5</sub>    | Εl               | E2                    | E <sub>3</sub>   | E4               | E <sub>5</sub>   | Latch/Latch                  |

| F <sub>6</sub>    | F <sub>1</sub>   | F <sub>2</sub>        | F <sub>3</sub>   | F <sub>4</sub>   | F <sub>5</sub>   | Man/Auto                     |

| F <sub>7</sub>    | F <sub>1</sub> # | F <sub>2</sub> #      | F <sub>3</sub> # | F4#              | F <sub>5</sub> # | 61/24 + 37 (17 + 44)         |

| F <sub>8</sub>    | Gl               | G <sub>2</sub>        | G3               | G4               | G <sub>5</sub>   | Antibounce ON/Antibounce OFF |

| F <sub>9</sub>    | G <sub>1</sub> # | G <sub>2</sub> #      | G <sub>3</sub> # | G4#              | G <sub>5</sub> # | ROM Low/ROM High             |

| F <sub>10</sub>   | A <sub>1</sub>   | A <sub>2</sub>        | A <sub>3</sub>   | $A_4$            | A <sub>5</sub>   |                              |

| F <sub>11</sub>   | A1#              | A2#                   | A3#              | A4#              | A5#              |                              |

| F <sub>12</sub>   | B1               | B <sub>2</sub>        | B <sub>3</sub>   | B <sub>4</sub>   | B <sub>5</sub>   |                              |

The main feature of this chip is the possibility of formating the keyboard either with 61 keys (only "SOLO" without automatism) or separating it into two sections ("ACCOMPANIMENT + SOLO") with the possibility of chord and bass automatic in the first section.

# FEATURES

- a) The "61/24 + 37" (17 + 44) control chooses the keyboard operating mode, i.e. the whole keyboard dedicated to "SOLO" or 24 (17) keys dedicated to "ACCOMPANIMENT" and 37 (44) to "SOLO".

- b) The "Man/Auto" control, which operates only in case of "ACC.+ SOLO", chooses the manual or the automatic accompaniment.

- c) The "Sust OFF/Sust ON" allows the storage of the "SOLO" section and handles the whole keyboard or 37 (44) keys depending on the operating mode.

- d) The "Latch/Latch" similarly allows the storage of the "ACC." section and operates in "ACC.+ SOLO" only.

- e) The "3rd+/3rd-" which operates only in case of "ACC. + SOLO" and "AUTOMATIC", changes the automatic chord generated from major to minor or viceversa.

- f) The "7th OFF/7th ON" adds the seventh to the automatic chord generated.

- g) The "Antibounce ON/Antibounce OFF" disables the antibounce circuit which is usually enabled.

- h) The "ROM Low/ROM High" selects between ROMs with return to "1" (Low active) or with return to "0" (High active). Usually the chip is enabled for ROMs with return to "1" (Low active).

## "SOLO" Operation

In this case the chip recognizes the whole keyboard as "SOLO" and does not read the controls which concern the "ACC, + SOLO" operation.

The chip identifies all the keys pressed and transfers to the outputs of each section (ACC. and SOLO) the analog sum of corresponding pitches.

The outputs are current generators with average value constant, therefore it is sufficient to connect the pins to one load and send the signals on to the filters.

In the case of "Sustain OFF" each new key pressed or released is accepted or deleted in a time  $\leq 576 \,\mu$ sec. In the case of "Sustain ON" the chip has a different operation according to whether the new key (keys) is pressed or released: each new key pressed is always accepted in a time  $\leq 576 \,\mu$ sec., whereas each key released is deleted with a delay of 73 msec. and only if there are still keys pressed.

In fact, if after the 73 msec. there are no keys pressed, the last key (or keys) released remains stored until new keys are pressed.

In this mode it is possible to have Sustain, with external envelope shaping, for the last keys (or key) released.

The pitch envelope is controlled by a D.C. signal KPS (any key pressed) and there is also an A.C. signal TDS (trigger decay "SOLO") which provides a pulse whenever a key is pressed.

An appropriate antibounce circuit, inside the chip, solves the problems associated with the keyboard contacts.

## "SOLO + ACCOMPANIMENT" Operation

In this case the chip identifies the "ACCOMPANIMENT" on the first 24 (17) keys on the left, and the "SOLO" on the remaining 37 (44) keys and reads all the controls which concern the "ACC." section. The "SOLO" function is identical to "61 keys" mode, but for the "ACC." section there are two possibilities:

#### A) MANUAL

The chip identifies which keys are pressed in the "ACC." section, and transfers to the "ACC." outputs the analog sum of the corresponding pitches.

The "ACC." section is fully independent of the "SOLO" section and the signals (if there is no "LATCH") remain at the output only while the keys are pressed even if there is "SUSTAIN ON".

The "BASS" section gives at the bass output an alternating bass between the first on the left and the first on the right of the keys pressed in the "ACC." section; the pitch switching timing is dependent on an external ROM (3 bits).

The "LATCH" control stores the last keys released and the output signals, including the bass output, remain until new keys are pressed.

The TDB (trigger decay "BASS") output gives a pulse corresponding to every output change; there are also two D.C. signals, KPA (any key pressed accompaniment) and NPA (pitches in output accompaniment) relative only to the "ACC." section.

The first of these signals (analogous to KPS) concerns the keyboard and does not consider the "LATCH" condition.

The second on the contrary concerns the "ACC." output and considers the "LATCH" condition.

#### B) AUTOMATIC

The chip recognizes in the "ACC." section only the first on the left of the keys pressed and, according to the setting of the following controls, produces a major or minor chord with or without seventh only the 4' footage but with separated outputs for root, third, fifth and eighth (or seventh if the chord is with seventh).

The bass section gives the bass arpeggio among root, third, fourth, fifth, sixth, seventh and eighth with pitch switching dependent on an external ROM (3 bits).

In automatic mode the two octaves of the "ACC." section inside the chip are connected in parallel both for the chord and for the bass; therefore by pressing anyone of the two keys of the same note the chip generates the same chord.

The "LATCH" control stores the major chord and the bass pitches (until new keys are pressed); the modification of the chord stored (from major to minor, addition of seventh) is always possible by operating the proper controls: by releasing these controls the chord becomes major again.

It is possible to delete the stored pitches both is manual and in "AUTOMATIC" mode by a Latch control signal.

Once again there are KPA, NPA, and TDB information; however the TDB pulse, which normally appears at each arrival of the ROM codes, does not appear if there are no pitches in the "ACC." (and bass) outputs or, in the case of alternate bass (in manual mode) if the codes indicate conditions of indifference.

# **RECOMMENDED OPERATING CONDITIONS**

|                 | Parameter              | Test conditions | Min. | Тур. | Max. | Unit |

|-----------------|------------------------|-----------------|------|------|------|------|

| V <sub>SS</sub> | Lowest supply voltage  |                 | 0    |      | 0    | v    |

| VDD             | Highest supply voltage |                 | 11.4 | 12   | 12.6 | V    |

# **BASS TRUTH TABLES**

# LOW ACTIVE

| External<br>Memory Code |   | Bass Arpeggio Output | Alternate Bass Output |

|-------------------------|---|----------------------|-----------------------|

| СВ                      | A | (Automatic mode)     | (Manual mode)         |

| 1 1                     | 1 | No change            | No change             |

| 1 1                     | 0 | Root                 | 1st on the left       |

| 1 0                     | 1 | 3rd                  |                       |

| 1 0                     | 0 | 4th                  |                       |

| 0 1                     | 1 | 5th                  | 1st on the right      |

| 0 1                     | 0 | 6th                  |                       |

| 0 0                     | 1 | 7th                  |                       |

| 0 0                     | 0 | 8th                  |                       |

# HIGH ACTIVE

| External<br>Memory Code |   | Bass Arpeggio Output |                  | Alternate Bass Output |

|-------------------------|---|----------------------|------------------|-----------------------|

| С                       | В | A                    | (Automatic mode) | (Manual mode)         |

| 0                       | 0 | 0                    | No change        | No change             |

| 0                       | 0 | 1                    | Root             | 1st on the left       |

| 0                       | 1 | 0                    | 3rd              |                       |

| 0                       | 1 | 1                    | 4th              |                       |

| 1                       | 0 | 0                    | 5th              | 1st on the right      |

| 1                       | 0 | 1                    | 6th              |                       |

| 1                       | 1 | 0                    | 7th              |                       |

| 1                       | 1 | 1                    | 8th              |                       |

|                         |   |                      |                  |                       |

# **STATIC ELECTRICAL CHARACTERISTICS** (Positive Logic, $V_{DD}$ = +10 to +14V, $V_{SS}$ = 0V, $T_{amb}$ = 0 to 50°C unless otherwise specified)

| Parameter Test conditions Min. Typ. Max. Unit |

|-----------------------------------------------|

|-----------------------------------------------|

#### INPUT SIGNALS

| v <sub>ін</sub> | Input high voltage    | Note 1                        | V <sub>DD</sub> -1 |          | V <sub>DD</sub>      | v  |

|-----------------|-----------------------|-------------------------------|--------------------|----------|----------------------|----|

|                 |                       | Note 2                        | 4                  |          | 18                   | v  |

|                 |                       | Note 3                        | V <sub>DD</sub> -2 | <u>8</u> | V <sub>DD</sub>      | v  |

| VIL             | Input low voltage     | Note 1                        | V <sub>SS</sub>    |          | V <sub>SS</sub> +1   | v  |

|                 |                       | Note 2                        | V <sub>SS</sub>    |          | V <sub>SS</sub> +0.6 | v  |

|                 |                       | Note 3                        | V <sub>SS</sub>    |          | V <sub>SS</sub> +2   | v  |

| I <sub>LI</sub> | Input leakage current | $V_1$ = +14V $T_{amb}$ = 25°C |                    |          | 10                   | μA |

### LOGIC SIGNAL OUTPUTS

| R <sub>ON</sub> | Output resistance with respect to $V_{SS}$        |                                                       |                      | 300                  | 500                  | Ω  |

|-----------------|---------------------------------------------------|-------------------------------------------------------|----------------------|----------------------|----------------------|----|

| R <sub>ON</sub> | Output resistance with respect to V <sub>DD</sub> | V <sub>OUT</sub> = V <sub>DD</sub> -1<br>(driver off) |                      | 15                   | 25                   | kΩ |

| v <sub>он</sub> | Output high voltage                               |                                                       | V <sub>DD</sub> -0.4 |                      | V <sub>DD</sub>      | v  |

| VOL             | Output low voltage                                |                                                       |                      | V <sub>SS</sub> +0.2 | V <sub>SS</sub> +0.4 | v  |

# POWER DISSIPATION

| <b></b> |                |                         | 1 | <b></b> |    | ·  | 1 |

|---------|----------------|-------------------------|---|---------|----|----|---|

| DD      | Supply current | T <sub>amb</sub> = 25°C |   | 30      | 45 | mA |   |

# ANALOG SIGNAL OUTPUTS (the external load must be connected to $V_{DD}/2$ )

| <sup>I</sup> он | Output current with respect to V <sub>DD</sub> /2 | Outputs loaded with 1 K $\Omega$ resistor versus V <sub>DD</sub> /2 | 35  | 50  | 70  | μA |

|-----------------|---------------------------------------------------|---------------------------------------------------------------------|-----|-----|-----|----|

| lo∟             | Output current with respect to V <sub>SS</sub>    | Outputs loaded with 1 K $\Omega$ resistor versus V $_{DD}/2$        | -35 | -50 | -70 | μA |

Note 1 : Refers only to the clock inputs.

Note 2 : Refers only to the inputs from the external memory.

Note 3 : Refers only to the reset input.

# DYNAMIC ELECTRICAL CHARACTERISTICS

| Parameter          | Test conditions | Min. | Тур. | Max. | Unit |  |

|--------------------|-----------------|------|------|------|------|--|

| MASTER CLOCK INPUT |                 |      |      |      |      |  |

| fi                                 | Input clock frequency                        |             | 1000.12 |    | КНz |

|------------------------------------|----------------------------------------------|-------------|---------|----|-----|

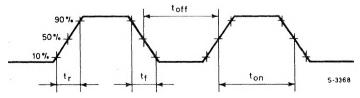

| t <sub>r</sub> , t <sub>f</sub>    | Input clock rise and fall time<br>10% to 90% | 1000.12 KHz |         | 40 | ns  |

| t <sub>on</sub> , t <sub>off</sub> | Input clock ON and OFF times                 | 1000 KHz    | 500     |    | ns  |

# T.O.S. CLOCK INPUT

| fi                                 | Input clock frequency                      |             | 100 | 1000.12 | 2500 | KHz |

|------------------------------------|--------------------------------------------|-------------|-----|---------|------|-----|

| t <sub>r</sub> , t <sub>f</sub>    | Input clock rise and fall times 10% to 90% | 1000.12 KHz |     |         | 40   | ns  |

| t <sub>on</sub> , t <sub>off</sub> | Input clock ON and OFF times               | 2000 KHz    |     | 250     |      | ns  |

# TDS and TDB OUTPUTS

| ton                             | Pulse duration                         | 1000 KHz | 9.216 | ms |

|---------------------------------|----------------------------------------|----------|-------|----|

| t <sub>r</sub> , t <sub>f</sub> | Outputs rise and fall times 10% to 90% | 1000 KHz | 100   | ns |

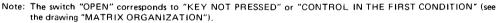

# INPUT CLOCK WAVEFORM

#### FREQUENCY RANGE OF EACH OCTAVE (16', 8', 4' footages) 16' 32 65 123 130 246 523 61 261 493 987 1046 R c с с c в в в в ċ 8' 65 123 130 261 987 246 493 523 1046 1975 2093 c c B c В В B c В ċ 523 C 4 130 246 261 493 987 1975 2093 1046 3951 4186 È c B P R B ċ B1 B 2 **B**3 84 **B**5 86 ACC. SECTION SOLO SECTION 5 3369m (ONLY M108) (ONLY M108) CONNECTION OF THE KEYBOARD AND CONTROL SWITCHES 1st OCTAVE on LAST KEY THE LEFT 2nd OCTAVE 3rd OCTAVE 4th OCTAVE 5th OCTAVE CONTROLS

M 108 M 208

Constitute Stands

#### TYPICAL APPLICATION CLOCK GEN VIBRATO 1000.12 KHz OSCILLATOR + 400 4 + VDD 40 19 160 39 20 F1 21 18 0 " 10 FI TO FIZ то 17 0 8' SOLO OUTPUTS F12 32 16 -0 16' AND CONTROL SWITCHES +VDD 3 -0 8th/7th 0 41/5th 4 ACC, OUTPUTS 5 -O 8'/ 3rd κΩ -O 16/ROOT 6 **B**6 33 7 O BASS OUTPUT 15 O KPS O TOS в5 34 13 14 O KPA **KEYBOARD** -O NPA 11 84 35 -O TOB 12 36 10 с в3 B ROM 9 82 37 8 2 B1 38 1 POWER - ON RESET CIRCUIT 5-3373

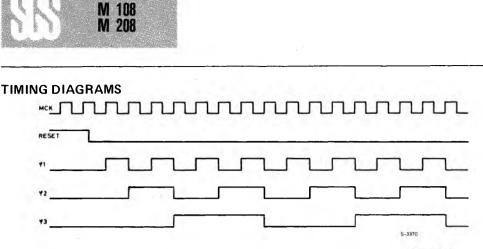

Note: MCK is the master clock input (matrix scanning),  $\varphi 1$ ,  $\varphi 2$ ,  $\varphi 3$  are internal phases to generate  $F1 \div F12$ .

Note: The matrix scanning starts (after the power on reset) at the second arrival in output of F1 (\*) from B1 to B6 in continuous sequence.