LC7074, 7074M Synchronous Error Correction IC for RDS Applications

# **Overview**

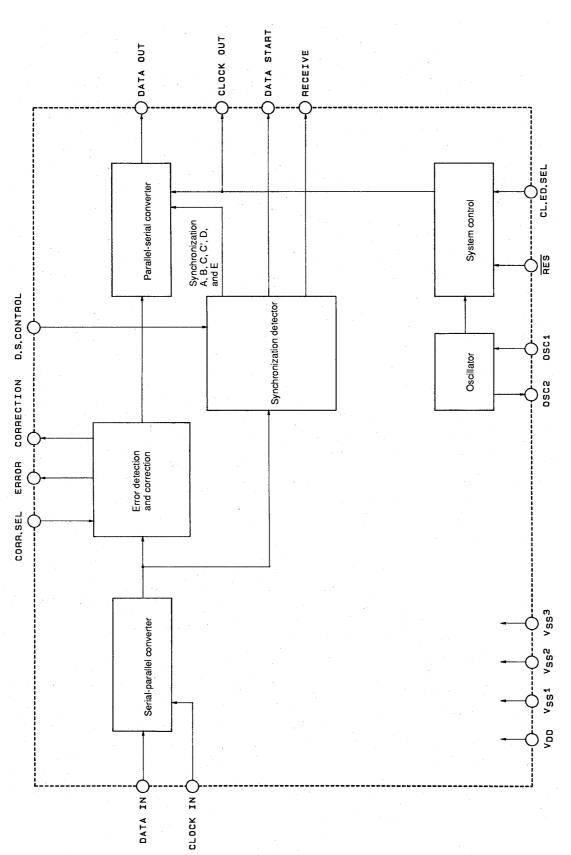

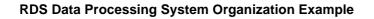

The LC7074 and the LC7074M are ICs for the RDS (radio data system) implemented by the EBU (European Broadcasting Union) and the RDBS (radio broadcast data system) implemented by the NRSC (National Radio System Committee) in the USA.

RDS and RBDS are standards that allow data to be broadcast multiplexed with other FM broadcasts. When combined with an IC in the LA2230 series, the LC7074/M synchronizes with data multiplexed in an FM broadcast and detects and corrects errors in that data. The synchronized data is output as a serial signal which can then be decoded and processed on the system control microprocessor.

# **Functions**

- Group synchronization. RDS group synchronization. MMBS/RDS group synchronization.

- Error detection and correction.

- Error detection and correction.

Error detection function enable/disable selection.

- Serial data output.

- Serial data clock polarity selection.

- Data block start signal output.

### **Features**

- System that decode, synchronize and detect and correct errors can easily be constructed by combining the LC7074/M with an LA2230 series product.

- Reduces overhead in the microprocessor that decodes and processes the RDS or MMBS/RDS data.

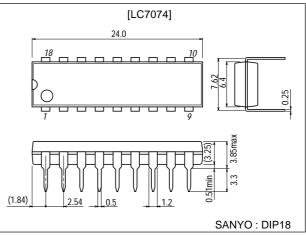

#### **Product-Package Relationship**

| Product No. | Package |  |

|-------------|---------|--|

| LC7074      | DIP18   |  |

| LC7074M     | MFP18   |  |

# **Package Dimensions**

# unit:mm

### 3007B-DIP18

# unit:mm

#

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co., Ltd. Semiconductor Company TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

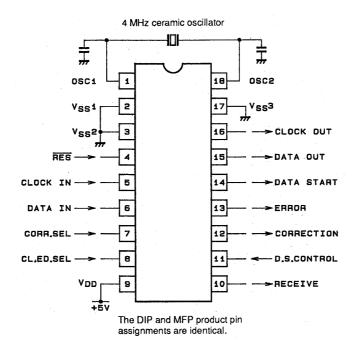

### **Pin Assignment**

### The LC7070 Series

This section describes the differences between the different products in the LC7070 series

### **Usage Notes**

This basic functions, including the pin functions and I/O timing, are identical in all products in the series. However, some pin circuits and function operation details differ.

- LC7070NM...While the LC7074M is pin compatible with this product, the circuit type of the three output pins differs as shown in table, Package and Output Driver Type Comparison. These products can be interchanged to match the output interface. However, since the data output method following synchronization detection differs as shown in table, Comparison of Functional Differences, care is required in writing programs that receive, decode and process the output data for the control microprocessor.

- LC7070N.....While the LC7074 is pin compatible with this product, the circuit type of the three output pins differs as shown in table, Package and Output Driver Type Comparison. These products can be interchanged to match the output interface. However, since the data output method following synchronization detection differs as shown in table, Comparison of Functional Differences, care is required in writing programs that receive, decode and process the output data for the control microprocessor.

- LC7071NM...The LC7074M is pin compatible with this product, and the pin circuit types, pin functions, and signal timings are identical. In principle, these products are interchangeable. However, since the data output method following synchronization detection differs as shown in table, Comparison of Functional Differences, care is required in writing programs that receive, decode and process the output data for the control microprocessor.

- LC7073.......The LC7074 is pin compatible with this product, and the pin circuit types, pin functions, and signal timings are identical. Furthermore, the synchronization detection method and the post-synchronization data output method are also identical. In principle, these products are interchangeable. However, since these products handle the block offset words E and F differently, and also handle MMBS/RDS data differently as shown in table, Comparison of Functional Differences, care is required in writing programs that receive, decode and process the output data for the control microprocessor.

- LC7073M.....The LC7074M is pin compatible with this product, and the pin circuit types, pin functions, and signal timings are identical. Furthermore, the synchronization detection method and the post-synchronization data output method are also identical. In principle, these products are interchangeable. However, since these products handle the block offset words E and F differently, and also handle MMBS/RDS data differently as shown in table, Comparison of Functional Differences, care is required in writing programs that receive, decode and process the output data for the control microprocessor.

# Package and Output Driver Type Comparison

| Product No. | Package | Output driver type difference*     | Function                 |  |

|-------------|---------|------------------------------------|--------------------------|--|

| LC7070N     | DIP18   |                                    |                          |  |

| LC7070NM    | MFP18   | - Open drain type                  | Identical functions      |  |

| LC7071NM    | MFP18   | Pull-up MOS transistor (CMOS type) | 1                        |  |

| LC7073      | DIP18   | Pull-up MOS transistor (CMOS type) |                          |  |

| LC7073M     | MFP18   |                                    | Functional Differences.  |  |

| LC7074      | DIP18   | Pull-up MOS transistor (CMOS type) | See table, Comparison of |  |

| LC7074M     | MFP18   |                                    | Functional Differences.  |  |

Note: \*Only applies to the three pins DATA START, DATA OUT and CLOCK OUT.

# **Comparison of Functional Differences**

|                                              | 1.070701                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                       |  |  |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Item                                         | LC7070N<br>LC7070NM<br>LC7071NM                                                                                                                                                                                                                                       | LC7070NM LC7073M                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                       |  |  |

| Offset word E<br>Offset word F               | These are taken to be offset words<br>and a group synchronization<br>detection operation is performed.                                                                                                                                                                | These are not seen as offset words. Offset words A, B, C, C', D<br>Only offset words A, B, C, C' and D<br>are detected. Offset word F is not detect                                                                                                                                                                                                             |                                                                                                                                       |  |  |

| All zero data<br>(corresponding to offset E) | All zero data is taken to be an offset<br>word E block. Accordingly, an offset<br>word E block synchronization<br>operation is performed.                                                                                                                             | All zero data is not seen as being an<br>offset word E block.<br>Rather, all zero data is taken to<br>mean that there is no input, and<br>synchronization detection is not<br>performed.<br>If all zero data is input, these<br>products decide that data input has<br>stopped, and they stop outputting<br>data and enter the pull-out<br>sequence.            | All zero data is seen as an offset<br>word E block. Accordingly, an offset<br>word E block synchronization<br>operation is performed. |  |  |

| MMBS/RDS compound data                       | For the transition from an RDS<br>group (ABCD) to an MMBS group<br>(EEEE) or the reverse transition,<br>these are taken to be the pull-out<br>and resynchronization sequences.<br>During transitions, data errors can<br>occur and data output can be<br>interrupted. | Since these products do not<br>synchronize on an offset word E<br>block, each time an RDS group is<br>inserted in an MMBS group, they<br>repeat the pull-out and<br>resynchronization sequences.                                                                                                                                                                | MMBS/RDS data is correctly output with no pull-out and no errors.                                                                     |  |  |

| Synchronization detection method             | Synchronization is achieved when<br>the offset words in five out of 12<br>blocks are detected in the correct<br>order.                                                                                                                                                | Synchronization is achieved when the offset words in two out of three blocks are detected in the correct order.                                                                                                                                                                                                                                                 |                                                                                                                                       |  |  |

| Post-synchronization detection data output   | Data output starts with the data from<br>the first block (the offset word A<br>block) in the group following the<br>group for which synchronization<br>detection was completed.                                                                                       | When synchronization detection completes with an offset word A block,<br>output starts with the data in the second block (the offset word B block)<br>from the same group.<br>When synchronization detection completes with an offset word B, C or D<br>block, output starts with the data in the first block (the offset word A block)<br>from the same group. |                                                                                                                                       |  |  |

| Pull-out determination method                | When the offset words from five or more consecutive blocks were not detected.                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                       |  |  |

| Error correction                             | In modes where error correction is en                                                                                                                                                                                                                                 | abled, up to five error bits are corrected                                                                                                                                                                                                                                                                                                                      | d for distances of 5 bits or less.                                                                                                    |  |  |

# Block Diagram

### **Pin Functions**

| Pin                                                                       | I/O    | Internal equivalent circuit | Function                                                                                                                                                                                                                                                                                                                                | Value at reset                 |

|---------------------------------------------------------------------------|--------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| V <sub>DD</sub> , V <sub>SS1</sub><br>V <sub>SS2</sub> , V <sub>SS3</sub> |        |                             | Power supply                                                                                                                                                                                                                                                                                                                            |                                |

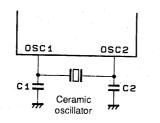

| OSC1<br>OSC2                                                              | I<br>O | A02079                      | Clock oscillator<br>Connect the external ceramic oscillator and capacitor at these pins.                                                                                                                                                                                                                                                |                                |

| CLOCK IN                                                                  | I      | A02080                      | RDS demodulation clock input<br>Connect to the clock output from the LA2230 series demodulation<br>IC.                                                                                                                                                                                                                                  |                                |

| DATA IN                                                                   | I      | A02080                      | RDS demodulation data input<br>Connect to the data output from the LA2230 series demodulation IC.                                                                                                                                                                                                                                       |                                |

| CORR.SEL                                                                  | I      | A020B0                      | Error correction selection input<br>This pin selects whether the IC corrects errors in the RDS<br>demodulated data.<br>Input=0: No correction performed*<br>Input=1: Error correction performed<br>In modes where error correction is enabled, up to five error bits are<br>corrected for distances of 5 bits or less.                  |                                |

| CL.ED.SEL                                                                 | I      | A02080                      | Serial data clock output polarity selection input<br>Input=0: Serial data output is valid on the rising edge of the output<br>clock. (Data output changes on the falling edge of the clock.)<br>Input=1: Serial data output is valid on the falling edge of the output<br>clock. (Data output changes on the rising edge of the clock.) |                                |

| D.S.CONTROL                                                               | I      | A02080                      | Block data start signal control input<br>Input=0: Output the DATA START signal for all blocks.<br>Input=1: Output the DATA START signal for only the second block.                                                                                                                                                                      |                                |

| RECEIVE                                                                   | Ο      |                             | RDS data reception in progress output<br>Outputs a low level while serial data is being output following<br>completion of synchronization detection. Outputs a high level at all<br>other times.<br>Open drain output                                                                                                                   | High level<br>(high impedance) |

| CORRECTION                                                                | ο      |                             | Error correction operation output<br>Outputs a low level when the serial data output data has been error<br>corrected, or could not be corrected. Outputs a high level (high<br>impedance) when correction is disabled.<br>Open drain output                                                                                            | High level<br>(high impedance) |

| ERROR                                                                     | 0      |                             | Error output<br>Outputs a low level when there were errors in the input data and<br>those errors could not be corrected. Outputs a high level (high<br>impedance) when there were no errors or the errors were corrected.<br>Open drain output                                                                                          | High level<br>(high impedance) |

| DATA START                                                                | 0      |                             | Serial data output block data start signal<br>The output type is controlled by the D.S.CONTOL input.<br>Pull-up MOS transistor (CMOS) output                                                                                                                                                                                            | High level                     |

|                                                                           |        | 1                           | 1                                                                                                                                                                                                                                                                                                                                       | I                              |

Continued on next page.

#### Continued from preceding page.

| Pin       | I/O | Internal equivalent circuit | Function                                                                                                                                                                                                                                                                                 | Value at reset |

|-----------|-----|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| DATA OUT  | 0   | A02082                      | Serial data output data output<br>Pull-up MOS transistor (CMOS) output                                                                                                                                                                                                                   | High level     |

| CLOCK OUT | 0   |                             | Serial data output clock output<br>Pull-up MOS transistor (CMOS) output                                                                                                                                                                                                                  | High level     |

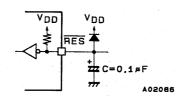

| RES       | I   |                             | Reset input<br>Input a low level pulse with a length of at least 4 clock cycles to reset<br>and restart IC operation. Note that when a 4 MHz oscillator is used,<br>since a single clock cycle is 0.25µs, four clock cycles is 1 µs.<br>Schmitt type input.<br>Built-in pull-up resistor |                |

Note: \*0: Low level input

1: High level input

# **Specifications**

# **Electrical Characteristics** at $Ta = 25^{\circ}C$ , $V_{SS1}$ , $V_{SS2}$ , $V_{SS3} = 0V$

| Parameter                   | Symbol              | Conditions                                                  | Ratings                      | Unit |

|-----------------------------|---------------------|-------------------------------------------------------------|------------------------------|------|

| Supply voltage              | V <sub>DD</sub> max | V <sub>DD</sub>                                             | -0.3 to +7.0                 | V    |

| Output valtage              | V <sub>O1</sub>     | OSC2, DATA START, DATA OUT, CLOCK OUT                       | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output voltage              | V <sub>O2</sub>     | RECEIVE, CORRECTION, ERROR                                  | -0.3 to +15                  | V    |

|                             | V <sub>I1</sub>     | RES, OSC1: *                                                | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Input voltage               | V <sub>I2</sub>     | CLOCK IN, DATA IN, CORR.SEL, CL.ED.SEL,<br>D.S.CONTROL      | -0.3 to +15                  | V    |

|                             | I <sub>O1</sub>     | RECEIVE, CORRECTION, ERROR: The output current<br>per pin   | 20                           | mA   |

| Output current              | I <sub>O2</sub>     | DATA START, DATA OUT, CLOCK OUT: The output current per pin | -2 to +20                    | mA   |

|                             | IO                  | All output pins: Total value                                | -14 to +90                   | mA   |

| Allowable power dissipation | Pd max              | DIP package product: Ta=-40 to +85°C                        | Up to 250                    | mW   |

|                             | Fulliax             | MFP package product: Ta=-40 to +85°C                        | Up to 150                    | mW   |

| Operating temperature       | Topr                |                                                             | -40 to +85                   | °C   |

| Storage temperature         | Tstg                |                                                             | -55 to +125                  | °C   |

Note: \*When driving the oscillator with the recommended constants shown in figure 1, values up to the oscillation amplitude that occurs are allowed.

# Allowable Operating Ranges at Ta = -40 to +85°C, $V_{SS1}$ , $V_{SS2}$ , $V_{SS3} = 0V$ , $V_{DD} = 4.5$ to 6.0V

| Parameter                    | Symbol           | Conditions                                             | Ratings                                                |     |                     | Unit |

|------------------------------|------------------|--------------------------------------------------------|--------------------------------------------------------|-----|---------------------|------|

| Falanetei                    | Symbol           |                                                        | min                                                    | typ | max                 | Onit |

| Operating supply voltage     | V <sub>DD</sub>  | V <sub>DD</sub>                                        | 4.5                                                    |     | 6.0                 | V    |

| Input high-level voltage     | VIH1             | CLOCK IN, DATA IN, CORR.SEL. CL.ED.SEL, D.S.CONTROL    | 0.7V <sub>DD</sub>                                     |     | 13.5                | V    |

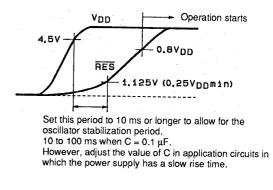

|                              | V <sub>IH2</sub> | RES                                                    | 0.8V <sub>DD</sub>                                     |     | V <sub>DD</sub>     | V    |

| Input low-level voltage      | V <sub>IL1</sub> | CLOCK IN, DATA IN, CORR.SEL. CL.ED.SEL,<br>D.S.CONTROL | VSS                                                    |     | 0.3V <sub>DD</sub>  | V    |

|                              | V <sub>IL2</sub> | RES                                                    | VSS                                                    |     | 0.25V <sub>DD</sub> | V    |

| Ceramic oscillator guarantee |                  | OSC1, OSC2: See figure 1                               | See the ceramic oscillator guaranteed constants table. |     | anteed              |      |

| Parameter                             | Symbol           | Conditions                                                                                              | Ratings              |                    |     | Unit |  |

|---------------------------------------|------------------|---------------------------------------------------------------------------------------------------------|----------------------|--------------------|-----|------|--|

| Falanlelei                            | Symbol           | Symbol                                                                                                  |                      | typ                | max | Unit |  |

| Input high-level current              | Чн               | CLOCK IN, DATA IN, CORR.SEL, CL.ED.SEL, D.S.CONTROL: VIN=13.5V                                          |                      |                    | 5.0 | μA   |  |

| Input low-level current               | I <sub>IL1</sub> | CLOCK IN, DATA IN, CORR.SEL, CL.ED.SEL, D.S.CONTROL: VIN=VSS                                            | -1.0                 |                    |     | μA   |  |

|                                       | I <sub>IL2</sub> | RES: VIN=VSS                                                                                            | -45                  | -10                |     | μA   |  |

| Output high-level voltage             | Vou              | DATA START, DATA OUT, CLOCK OUT:<br>I <sub>OH</sub> =–50µA                                              | V <sub>DD</sub> -1.2 |                    | V   |      |  |

|                                       | Vон              | DATA START, DATA OUT, CLOCK OUT:<br>I <sub>OH</sub> =-10µA                                              | V <sub>DD</sub> -0.5 |                    |     | v    |  |

|                                       |                  | RECEIVE, CORRECTION, ERROR, DATA<br>START, DATA OUT, CLOCK OUT: I <sub>OL</sub> =10mA                   |                      |                    | 1.5 |      |  |

| Output low-level voltage              | V <sub>OL</sub>  | RECEIVE, CORRECTION, ERROR, DATA<br>START, DATA OUT, CLOCK OUT:<br>I <sub>OL</sub> =1.8mA* <sup>1</sup> |                      |                    | 0.4 | V    |  |

| Output off leakage current            | IOFF             | RECEIVE, CORRECTION, ERROR:<br>V <sub>O</sub> =13.5V                                                    |                      |                    | 5.0 | μA   |  |

|                                       |                  | RECEIVE, CORRECTION, ERROR: VO=VSS                                                                      | -1.0                 |                    |     |      |  |

| Hysteresis voltage                    | VHIS             | RES                                                                                                     |                      | 0.1V <sub>DD</sub> |     | V    |  |

| Supply current                        | IDD              | V <sub>DD:</sub> *2                                                                                     |                      | 1.5                | 3.5 | mA   |  |

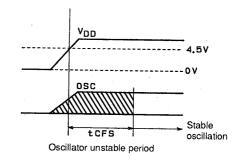

| Ceramic oscillator stabilization time | <sup>t</sup> CFS | OSC1, OSC2: See figure 2                                                                                |                      |                    | 10  | ms   |  |

| Reset time                            | tRST             |                                                                                                         | See figure 3         |                    |     |      |  |

# Electrical Characteristics at Ta = -40 to +85 °C, $V_{SS1}$ , $V_{SS2}$ , $V_{SS3}$ = 0V, $V_{DD}$ = 4.5 to 6.0V

Note: 1 When the I<sub>OL</sub> values for the remaining output pins (when an arbitrary 4 output pins are excluded) are all under 1 mA.

2 Using the oscillator circuit in figure 1, when there is no power dissipation in the output pins, and when the input pins are at the  $V_{DD}$  level.

### **Ceramic Oscillator Guaranteed Constants**

| 4 MHz ceramic oscillator           | C1, C2     |

|------------------------------------|------------|

| CSA4. 00MG (Murata Mfg. Co., Ltd.) | 30 pF ±10% |

| KBR4. 0M (Kyocera, Ltd.)           | 30 pF ±10% |

Figure 1. Oscillator Circuit

This example shows a simplified reset circuit. In actual applications, we recommend that the circuit be designed so that the reset signal can be applied from the control microprocessor to handle cases where IC operation becomes unstable due to power supply noise or other causes.

Figure 2. Oscillator Stabilization Period

Figure 3. Reset Circuit

### **System Operation**

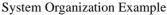

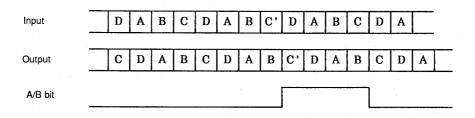

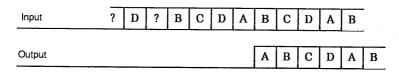

1. Relationship between RDS Demodulated Data (LA2230 series IC output) and LC7074/M Output Data

- The DATA START signal indicated with broken lines is the signal when the D.S.CONTROL input is low level.

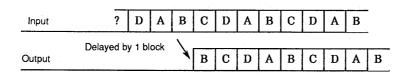

- The serial data output (DATA OUT) from the LC7074/M is data that is delayed by one block with respect to the data received from the LA2230 series IC.

- The ERROR and CORRECTION signals are output continuously when consecutive errors are detected.

- The RECEIVE output signal is output only in periods when output data is being output from the DATA OUT pin.

#### Relationship between the Demodulated Data and the Output Data

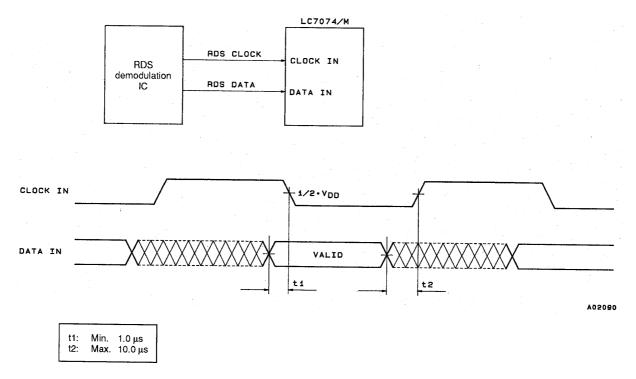

### 2. Input Data Timing

• Input data is acquired on the falling edge of the input clock.

• Input data must be stable just before and just after the falling edge of the input clock. This means that it is desirable that the input data change state on the rising edge of the input clock.

### Input Data Timing

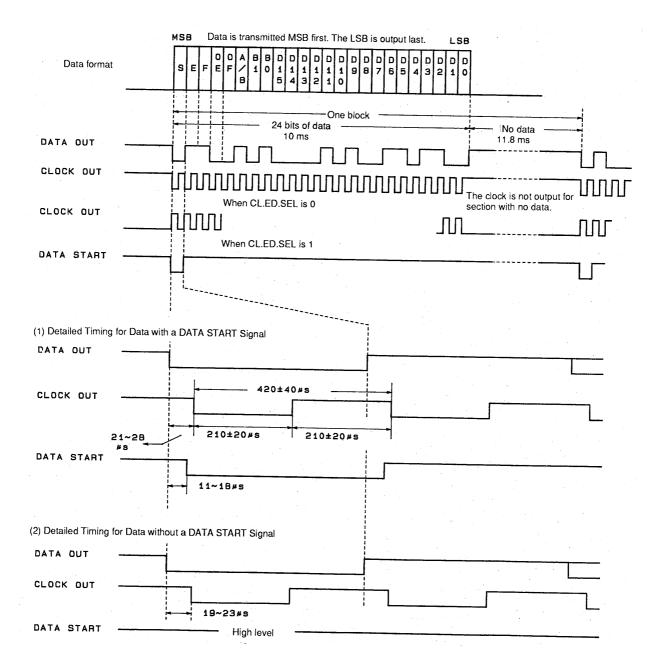

3. Serial Data Output Format and Timing

| S      | : Start bit (always "0")                               |      |

|--------|--------------------------------------------------------|------|

| E      | : Error flag } See table                               |      |

| F      | : Correction flag                                      |      |

| OE     | : Offset E                                             |      |

| OF     | : Offset F (always "0" : reserved for future expansion | ion) |

| A/B    | : Group type version 0: Version A                      |      |

|        | 1: Version B                                           | E    |

| B1, B0 | : Block number 00 : First block                        |      |

|        | 01 : Second block                                      | N    |

|        | 10 : Third block                                       | E    |

|        | 11 : Fourth block                                      |      |

|        |                                                        |      |

D0 to D15 : RDS data

# E and F Flags

|                      | E | F |

|----------------------|---|---|

| No errors            | 0 | 0 |

| Errors corrected     | 0 | 1 |

| Uncorrectable errors | 1 | 1 |

Note: When the CORR.SEL input pin is high level.

Serial Data Output Format and Timing

- 4. Informative Bits in the Serial Data Output

- Error Flag (E) and Correction Flag (F)

The error flag (E) and the correction flag (F) in the serial data output are identical to the ERROR and CORRECTION output pins, except that the logical levels are inverted.

The meaning of the error and correction flags differ slightly depending on the setting that determines whether input data error correction is to be performed (the CORR.SEL pin). The tables below show the relations between the output value combinations of the error and correction flags.

- When the CORR.SEL pin is high: Error correction enabled

|                      | Error flag (E) | Correction flag (F) | ERROR pin | CORRECTION pin |

|----------------------|----------------|---------------------|-----------|----------------|

| No errors            | 0              | 0                   | 1         | 1              |

| Errors corrected     | 0              | 1                   | 1         | 0              |

| Uncorrectable errors | 1              | 1                   | 0         | 0              |

The value combination where E is 1 and F is 0 (or equivalently, where the ERROR pin is 0 and the CORRECTION pin is 1) cannot occur.

- When the CORR.SEL pin is high: Error correction disabled

|                      | Error flag (E) | Correction flag (F) | ERROR pin | CORRECTION pin |

|----------------------|----------------|---------------------|-----------|----------------|

| No errors            | 0              | 0                   | 1         | 1              |

| Uncorrectable errors | 1              | 1                   | 0         | 0              |

The value combination where E is 1 and F is 0 (or equivalently, where the ERROR pin is 0 and the CORRECTION pin is 1) and where E is 0 and F is 1 (or equivalently, where the ERROR pin is 1 and the CORRECTION pin is 0) cannot occur.

In this case, the combination indicating no errors is output if there were no errors in the data, and the combination indicating uncorrectable errors is output when there are errors in the data whether or not those errors are correctable.

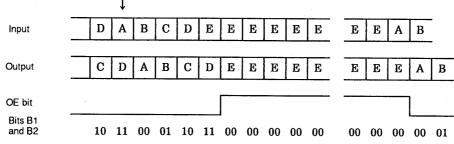

#### • Offset E (OE) and Offset F (OF)

When the IC has synchronized with the offset word E block data, the OE bit in the output data goes to "1". At this point the bits B1 and B0, which express the RDS block number, will be "00", i.e., both will be zero. The LC7074/M does not recognize an offset word F block as a correct offset word. Therefore, the OF bit in the output data will always be "0".

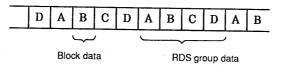

Block data. "A" indicates offset word A, that is, the first block.

**OE Bit Output**

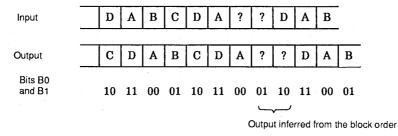

### • Block Number (B0 and B1)

The block number bits indicate the data block of the output data.

| B1 | B0 | Block                                       |

|----|----|---------------------------------------------|

| 0  | 0  | First block (the offset word A block)       |

| 0  | 1  | Second block (the offset word B block)      |

| 1  | 0  | Third block (the offset word C or C' block) |

| 1  | 1  | Fourth block (the offset word D block)      |

- The OE bit becomes one when the offset word E block data is output. At this point the bits B1 and B0 will be "00", i.e., both will be zero.

- Consider the situation where there is a block in the RDS group data output for which the input data offset word cannot be detected. Here, the IC assumes that the blocks were input in the correct offset word order, and outputs B0 to B1 accordingly.

#### **Block Number Output**

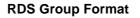

• Group Type Version (A/B)

The A/B bit is set based on the third block offset word of input data. If the offset word is "C", the A/B bit is set to "0", and if the offset word is "C", the A/B bit is set to "1".

Note that the version bit B0 in the second block (the offset word B block) data of input data is not used for group type version determination. As a result, the version bit A/B in the output data changes in the third block.

A/B Bit Output

- 5. Group Synchronization

- Recognized Offset Words

The LC7074/M recognizes the five offset words A, B, C, C' and D. The offset word F, which is stipulated by the EBU, is not recognized.

• Group Data Ordering and Synchronization

The LC7074/M recognizes the following three types of group data. However, there is no limitation on the number of blocks in groups consisting of offset E blocks (type 3).

(1) A - B - C - D(2) A - B - C' - D(3) E - E - E - EE - E - EE - EE

As a result, there are nine block data orders (listed as (1) to (9) below) that the LC7074/M recognizes, and any other order is determined to be an error.

| Correct data orders                                                                                                                                                                                    | Data orders handled as errors                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| (1) $A \rightarrow B$<br>(2) $B \rightarrow C$<br>(3) $B \rightarrow C'$<br>(4) $C \rightarrow D$<br>(5) $C' \rightarrow D$<br>(6) $D \rightarrow A$<br>(7) $D \rightarrow E$<br>(8) $E \rightarrow E$ | $A \rightarrow C$<br>$B \rightarrow E$<br>$E \rightarrow B$<br>•<br>• |

| $(9) E \to A$                                                                                                                                                                                          |                                                                       |

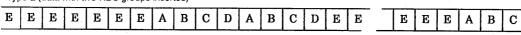

The data input wait state is called a synchronization sequence. When a clock signal is first input to the LC7074/M from the demodulation IC, the LC7074/M starts the operation of detecting offset words from data synchronized with the clock.

The LC7074/M synchronizes with the input data when it detects two blocks with correct offset words in correct positions.

- Synchronization with RDS Group Data

- RDS block data format

- Synchronization with RDS data

• Here the LC7074/M detects blocks D and A consecutively. Since it synchronizes at A, output starts with B from the same group.

• Here the LC7074/M detects the D and B blocks. Since it synchronizes at B, output starts with A from the next group.

### **RDS Synchronization Sequence**

- Synchronization with RDS/MMBS Group Data

- $-\operatorname{RDS}/\operatorname{MMBS}$  compound group data format

| Type 1 | (data with a | single RDS | group inserted) |

|--------|--------------|------------|-----------------|

|        |              | gie i ie e | group moontool) |

| Е | E | Е | Е | E | Е | Е | Α | В | С | D | Е | Е | Е | E | Е | Е | Е | Е | Е | Α | В | С |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |   |

Type 2 (data with two RDS groups inserted)

### **RDS/MMBS Group Data Format**

- Synchronization with MMBS Group Data

| Input  | ? | Е | Е | Е | Е | Е | Е | E | E | Е | Е | Е | • |

|--------|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Output |   |   |   |   | Е | Е | Е | Е | E | Е | Е | Е | Е |

• Detected for two consecutive blocks

| Input  | ? | Е | ? | Е | Е | Е | Е | Е | Е | Е | Е | Е | • • |

|--------|---|---|---|---|---|---|---|---|---|---|---|---|-----|

| Output |   |   |   |   |   | Е | Е | Е | Е | Е | Е | Е | Е   |

• Detected for two of three blocks

Note: The LC7074/M does not recognize that MMBS group data consists of four MMBS blocks (offset word E blocks).

### **MMBS Synchronization Sequence**

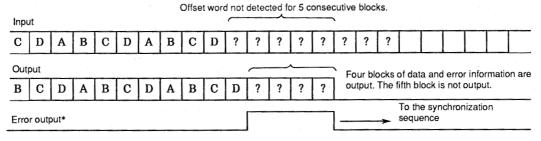

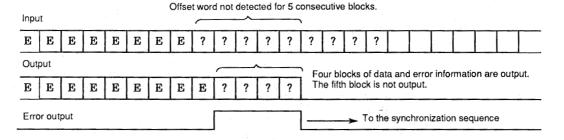

• Pull-Out

When a state occurs in which the LC7074/M is in the synchronized state and cannot detect the block data offset word, it enters a pull-out sequence.

When the LC7074/M is unable to detect the offset word in five consecutive blocks while in a pull-out sequence, it goes to the pull-out state. When the LC7074/M pulls out, it stops clock and data output and switches to the synchronization sequence.

Note that if the LC7074/M was unable to detect the offset word in fewer than five consecutive blocks, the synchronization state continues without change.

- Pull-out in RDS group data

Note: "Error output" refers to the E and F flags in the output data and to the ERROR and CORRECTION pins.

#### **RDS Pull-Out Sequence**

- Pull-out in MMBS group data

#### **MMBS Pull-Out Sequence**

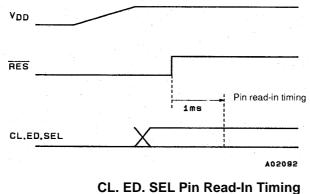

6. Control Input Pin Read Timing (Pins CL.ED.SEL, CORR.SEL and D.S.CONTROL)

• CL.ED.SEL

The LC7074/M reads in the state of the CL.ED.SEL pin about 1 ms after a reset clear. It uses this signal for the internal settings that determine the clock output polarity.

• CORR.SEL and D.S.CONTROL

The LC7074/M continuously checks the state of these pins. As a result, error correction can be turned on or off and the DATA START signal output form can be changed at any time.

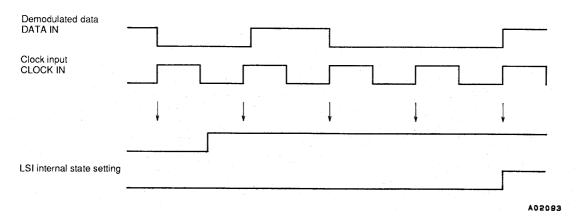

- During synchronization detection (synchronization sequence)

The pin states are read-in on each bit of demodulated data from the RDS demodulation IC (at the points shown by arrows in the figure). The state is read into the IC if the input values agree four times in a row.

### Pin Read-In Timing during Synchronization Detection

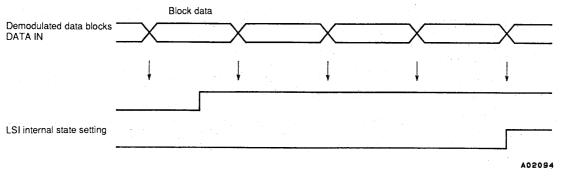

#### - Following synchronization detection (while synchronized)

The LC7074/M reads in the pin state at the start of each block in the demodulated data from the RDS demodulation IC (at the points shown by arrows in the figure). The state is read into the IC if the input values agree four times in a row.

Pin Read-In Timing Following Synchronization Detection