# IMS M212 disk processor

# **Product Preview**

## **FEATURES**

ST506/ST412, SA400/450 compatible interface Full disk interface logic on chip Minimum of external components required On-chip 16 bit processor 2 Kbytes on-chip RAM 4 Kbytes on-chip ROM disk control software External memory interface Hardware CRC/ECC generator Two bi-directional 8 bit data ports Two 10/20 Mbits/sec INMOS serial links External event interrupt Variable wait states for slow memory Internal timers Support for run-time error diagnostics Bootstraps from ROM, link or disk Single 5 MHz processor clock input Power dissipation less than 1 Watt

# 1 Introduction

The IMS M212 peripheral processor is an intelligent peripheral controller of the INMOS transputer family, configured for connection to soft sectored winchester and floppy disk drives. It satisfies the demand for increasing intelligence in peripheral controllers and maintains a high degree of flexibility, allowing designers to modify the controller function without altering the hardware.

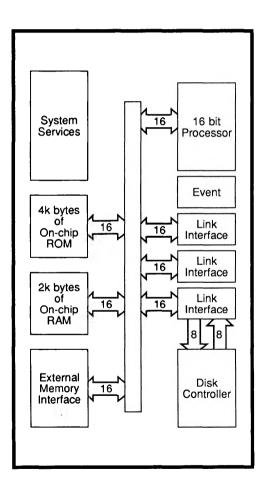

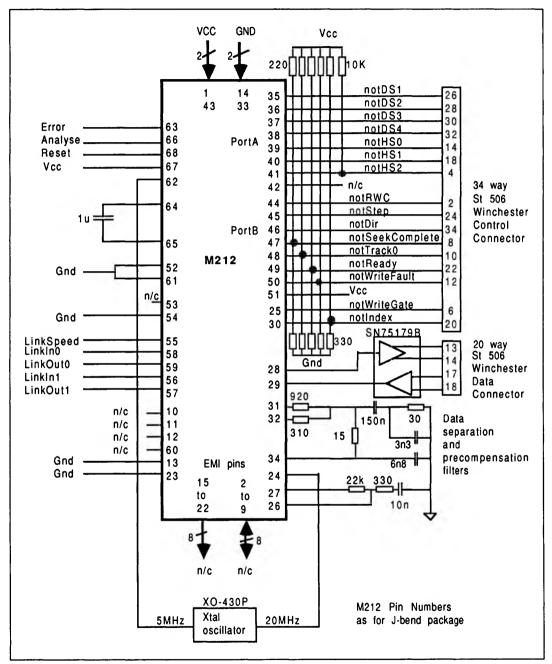

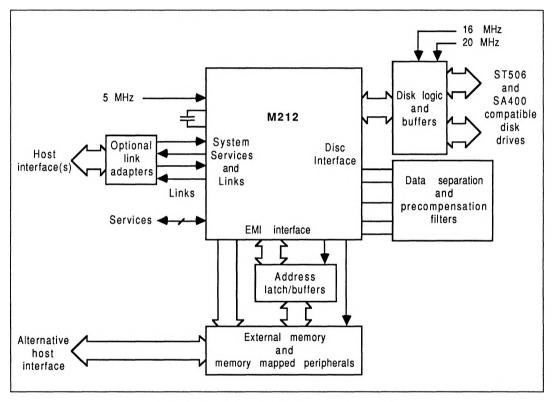

Figure 1.1 IMS M212 block diagram

The disk control function has been designed to provide easy connection, with minimal external hardware, to a standard winchester and/or floppy disk interface. Two byte-wide programmable bidirectional ports are provided to control and monitor disk functions such as head position, drive selection and disk status. A dedicated port is provided for serial data interfaces and critical timing signals.

The IMS M212 is programmed as a normal transputer, permitting extremely powerful peripheral control facilities to be built into the device and thus reducing the load on the traditional central processor of a computer. Full details are given in the IMS M212 Disk Processor Product Data manual.

#### 1.1 IMS M212 peripheral processor

#### 1.1.1 Central processor

At the heart of the IMS M212 is a 16 bit processor which is compatible with the transputer family. Its design achieves compact programs, efficient high level language implementation and provides direct support for the OCCAM model of concurrency. The processor shares its time between any number of concurrent processes. A process waiting for communication or a timer does not consume any processor time. Two levels of process priority enable fast interrupt response to be achieved.

The IMS M212 has been designed so that the on-chip processor performs as many functions as possible, providing flexible operation and minimising on-chip disk-specific hardware.

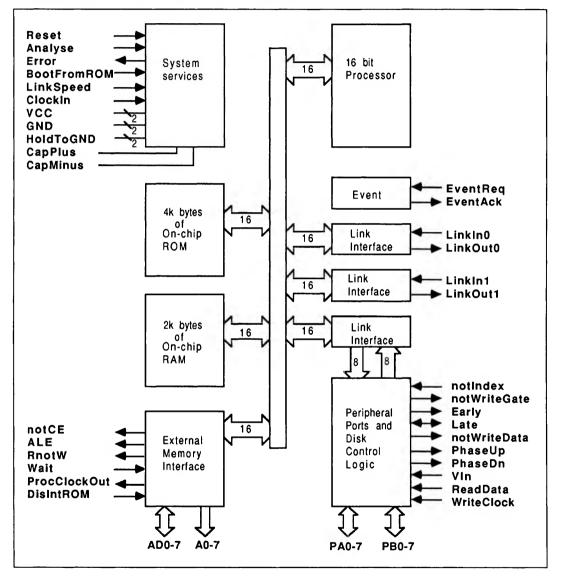

#### 1.1.2 Peripheral interface

The two 8 bit data ports **PA0-7** and **PB0-7** are controlled by the processor via a pair of channels. This allows the programmer to modify the function of these ports in order to implement a wide variety of applications.

The peripheral interface includes data output registers and TTL compatible input ports, as well as facilities for defining the direction of the pins on a bit-selectable basis. The interface contains logic to detect a change of state on the input pins and to store this change for interrogation by the program.

In addition to this, the external memory interface can support memory mapped peripherals on its byte-wide data bus. An event pin is also provided, so that peripherals can request attention.

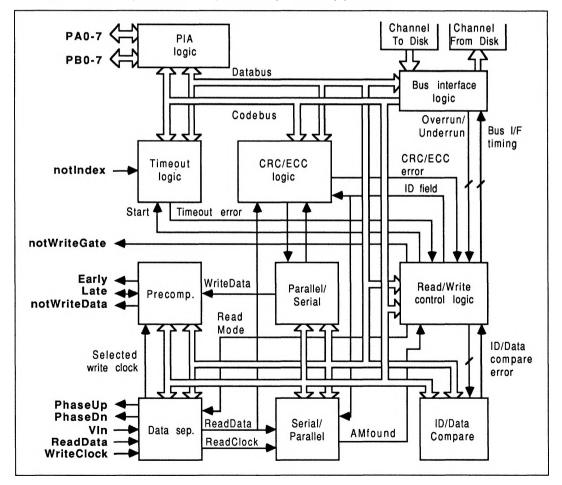

#### 1.1.3 Disk controller

The disk interface provides a simple interconnection to ST506/ST412 and SA400/SA450 compatible disk drives via ten dedicated disk control lines and the two general purpose 8 bit bidirectional data ports **PA0-7** and **PB0-7**. Although the on-chip disk control hardware handles much of the specialised data conversion, as many disk operations as possible are controlled by the processor, using sequences of control and data information.

The processor can program and interrogate all the registers controlling the disk functions and data ports, and thereby control the external interface lines. As a result of this versatility, the IMS M212 can also be used in applications other than disk control ones.

A versatile hardware 32 bit Error Correcting Codes (ECC) and 16 bit Cyclic Redundancy Codes (CRC) generator is included to check data integrity. ECC's allow certain classes of errors to be corrected as well as detected, whilst CRC's only allow detection.

When writing data to the disk the hardware serialises the data and encodes it into a Frequency Modulated (FM) or Modified Frequency Modulated (MFM) data stream. Any necessary precompensation is performed internally before outputting the data together with the necessary control signals. Any necessary modification of the data, for instance writing the Address Marks (AM) or inserting the CRC/ECC bytes, is automatically performed by the hardware.

When reading data from disk the raw read data is input and the function known as data separation is performed internally. The hardware examines the data stream for an Address Mark to achieve byte synchronisation and then searches for the desired sector information. When the required data is located it is decoded and a serial to parallel conversion is performed before the data is transferred to the processor.

#### 1.1.4 Links

The IMS M212 uses a DMA block transfer mechanism to transfer messages between memory and another transputer product via the INMOS links. The link interfaces and the processor all operate concurrently, allowing processing to continue while data is being transferred on all of the links.

The host interface of the IMS M212 is via two INMOS standard links, providing simple connection to any transputer based system or, via a link adaptor, to a conventional microprocessor system. Link speeds of 10 Mbits/sec and 20 Mbits/sec are available, making the device compatible with all other INMOS transputer products.

The on-chip disk control logic is controlled by the processor, using simple command sequences, via two channels which appear to the processor as a normal pair of hardware channels.

#### 1.1.5 Memory system

The 2 Kbytes of on-chip static RAM can be used for program or data storage, as a sector buffer or to store parameter and format information. It can be extended off chip, via the external memory interface, to provide a total of 64 Kbytes. Internal and external memory appear as a single contiguous address space.

Software contained in 4 Kbytes of internal ROM enables the IMS M212 to be used as a stand alone disk processor. The ROM can be disabled to free the address space for external memory.

#### 1.1.6 Error handling

High level language execution is made secure with array bounds checking, arithmetic overflow detection etc. A flag is set when an error is detected, and the error can be handled internally by software or externally by sensing the error pin. System state is preserved for subsequent analysis.

#### 2 Operation

The IMS M212 can be used in two modes: Mode 1, which uses the software in the internal ROM, and Mode 2, which relies upon custom designed software.

#### 2.1 Mode 1

Mode 1 operation uses code in the on-chip ROM to control the disk controller hardware, and little knowledge of the hardware is required to implement winchester and floppy disk drivers. The programming interface to all drive types is identical, and there is sufficient flexibility to allow a wide variety of formats and drive types to be used.

Both ST506/412 compatible winchester and SA400/450 compatible floppy drives are supported in standard double density formats; this includes common 5.25 and 3.5 inch drives. Up to 4096 cylinders are allowed. Floppy drives can have up to 8 heads and winchesters up to 16 heads. There can be between 1 and 256 sectors per track, with sector sizes of 128 to 16384 bytes in powers of 2. Drives with or without 'seek complete' and 'ready' lines are supported, and step rates can be from 64  $\mu$ s to 16 ms. A range of non-standard formats can also be set up for user-specific requirements.

As with transputers, the IMS M212 can be bootstrapped from ROM or via a link. In addition, the Mode 1 monitor process also provides a facility whereby the disk processor can bootstrap itself with code read from a disk; this code runs instead of the Mode 1 process. Another option sends a standard bootstrap message, read from a disk, out of link 0; the Mode 1 process then continues as normal. It is also possible in Mode 1 to send a command, at any time, to bootstrap from code in the sector buffer.

General workspace for Mode 1 is contained in on-chip RAM, which also provides 1280 bytes of sector buffer. Contiguous external RAM immediately past the internal RAM will automatically be used to extend the size of the sector buffer. As many sectors as will fit into the sector buffer can be stored in it at the same time.

In Mode 1 a separate data area, in on-chip RAM, contains all the required control information (parameters) for each of the four possible drives. Parameters may be read from or written to via the links, and contain such information as the capacity of the disk, current position of the heads, desired sector for reading or writing, drive type, timing details etc.

Command and data bytes are accepted down either of the IMS M212 links; an interlock system prevents conflict between commands received on both links simultaneously. Any results are returned on the link which received the command. Available commands are

| EndOfSequence | Initialise  | ReadParameter | WriteParameter |

|---------------|-------------|---------------|----------------|

| ReadBuffer    | WriteBuffer | ReadSector    | WriteSector    |

| Restore       | Seek        | SelectHead    | SelectDrive    |

| PollDrives    | FormatTrack | Boot          |                |

Disk access commands implicitly select the drive, perform a seek and select the head. If an ECC or CRC error is found when reading a sector, a programmable number of automatic retries are performed and a subsequent correction attempted if possible. Mode 1 supports two of the four IMS M212 ECC/CRC modes - ECC and CRC. Either CRC or ECC can be specified in either of the ID or Data fields, making it possible to have floppies with correctable Data fields.

All appropriate parameters are checked to ensure that, for example, an attempt is not made to access a non-existent sector, relieving the host processor of such checking. Another feature which reduces the load on the host processor is the logical sector mode, in which all the sectors are specified as a single linear address space rather than physical cylinder/head/sector.

The logical address can also be auto-incremented if desired, as can the sector buffer. This allows a number of consecutive sectors to be read from or written to the disk with little overhead. As a *sticky status* checking technique is used, the status only has to be checked once at the end of a stream of commands; if an error occurred then reading and writing is inhibited, so that the logical address can be inspected to find where the error occurred.

#### 2.2 Mode 2

In Mode 2 operation the internal ROM is bypassed, allowing the device to utilise user-defined software. This software can be held in external ROM, bootstrapped from a floppy or winchester disk, or loaded from the host processor via a link into internal or external RAM.

In this mode the user services the disk control hardware via a pair of on-chip high bandwidth channels. Using these channels the processor has access to the 49 registers which control the operation of the disk controller. Sequences of control codes and data bytes are sent by the processor to the disk controller logic via one of the hardware channels and data returned to the IMS M212 processor via the other. Each control code is a single byte, and may be followed by one or more data bytes.

In Mode 2 the designer can define new commands which are more complex than otherwise available. Examples include a *Format Disk* command as an extension to the *Format Track*; an application-specific directory structure; a software interface to optimise a particular file structure. Mode 2 also allows the user to optimise data transfer; thus, data could be read from a disk with no interleave, or data transfers could be re-ordered to minimise head movement. Disk searches can be arranged such that data transfer back to the host is minimised, as data comparisons can be performed by the on-chip processor.

Figure 2.1 Disk controller interface

# 3 Applications

Figure 3.1 Winchester disk controller

The IMS M212 can interface to a floppy or winchester disk with very little external circuitry when used in Mode 1 or if a program is bootstrapped from a link. A typical arrangement is shown in figure 3.1. Note the absence of any control port buffers; this is possible provided the drive characteristics are not infringed.

Additional external memory can easily be added to the IMS M212. In both Modes 1 and 2, external RAM can be added for extra sector storage, whilst in Mode 2 extra RAM or ROM can be provided for program storage.

With the addition of control buffers and suitable clocks, a single IMS M212 can interface to both floppy and winchester drives. Link adaptors provide a means of interfacing to conventional microprocessors.

The IMS B005 evaluation board is an example of an application with control for both types of drive. The board also has a fully populated memory interface.

Figure 3.2 Enhanced disk controller interface

The IMS M212 can interface with both floppy and winchester disk drives, and the data rate to and from the disk can be selected by software. As a result the device is suitable for interfacing to the new generation of floppy disk drives which use vertical recording. These drives have an increased data rate of 1 Mbit/sec, and quadruple the capacity of existing floppy disk drives to 4 Mbytes. A single IMS M212 can be used to control a mixture of standard floppy drives, winchester drives and the new high speed high capacity drives. This eases compatibility and portability problems, and provides a simple upgrade path from standard floppies to high capacity floppies to winchesters.

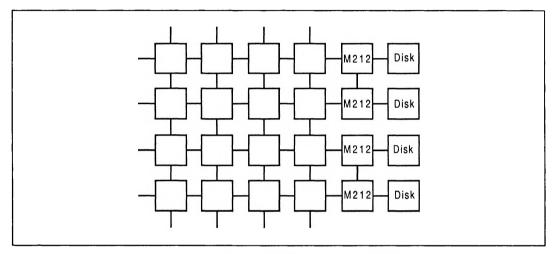

The IMS M212 provides a very simple and compact disk controller solution, making it very easy to replace a single large disk drive with an array of IMS M212's, each controlling a single smaller disk drive. This has several advantages: cheaper drives can be used; overall available disk bandwidth is increased; local processing is provided by a high performance processor at each disk node; fault tolerant operation. The latter can be achieved by holding duplicated data on several drives. This prevents the whole system from stopping, as would be the case if the single large drive failed.

These advantages are particularly applicable when transputers are connected in arrays to provide high performance concurrent systems (figure 3.3). The IMS M212's can be directly connected to the array via INMOS links and the spare link used to communicate with the adjacent IMS M212 to provide the fault tolerant operation.

Figure 3.3 Transputer network with disk processors

A high performance processor allows many operations to be performed locally to the disk. This not only frees the host processor for other work but also removes the need for large amounts of data to be needlessly transferred to the host. Operations which can be performed by the IMS M212 include: file management with directory management and pre-reading; data manipulation such as compression/de-compression and encryption/de-cryption; data search such as database key searching; performance optimisation such as head scheduling and cacheing.

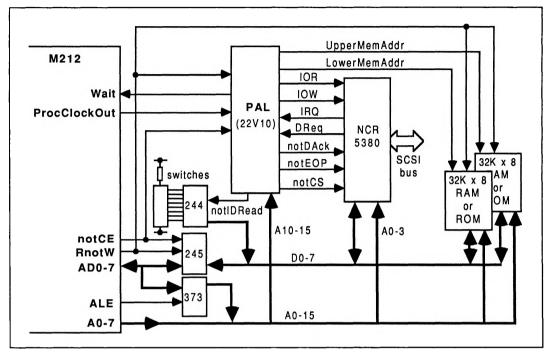

The IMS M212 external memory interface can be used to connect to memory mapped peripherals. One application of this is interfacing to a SCSI bus controller, permitting direct connection to the SCSI bus in a low part count system. The processor is used to control the SCSI bus controller and implements the required command interface, as well as controlling the disk or other peripheral.

This arrangement allows floppy and winchester disks to be simply connected to a SCSI bus. Because the command interface is controlled by a process running in the IMS M212, any future command upgrades can easily be incorporated.

The design can be used both as a target and an initiator interface, again controlled by the process running in the IMS M212. It provides a means of implementing a link to SCSI interface, as well as a SCSI controlled disk.

Figure 3.4 SCSI interface

### 4 Package specifications

#### 4.1 68 pin grid array package

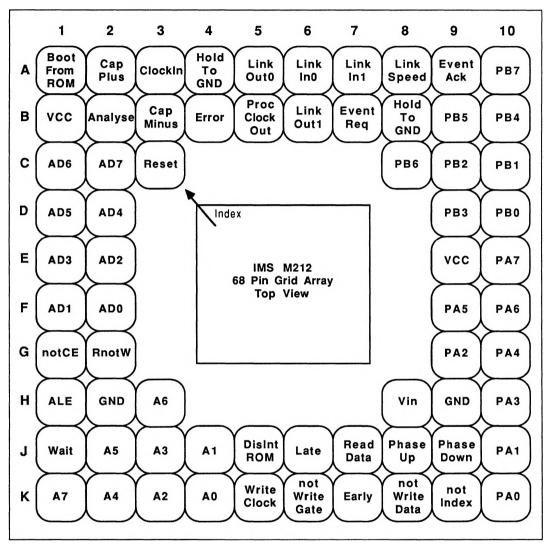

Figure 4.1 IMS M212 68 pin grid array package pinout

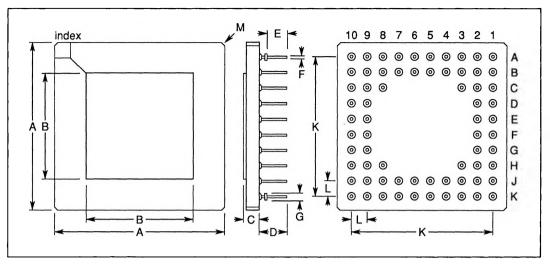

Figure 4.2 68 pin grid array package dimensions

|     | Millim | Millimetres |       | nes    |                 |

|-----|--------|-------------|-------|--------|-----------------|

| DIM | NOM    | TOL         | NOM   | TOL    | Notes           |

| A   | 26.924 | ±0.254      | 1.060 | ±0.010 |                 |

| В   | 17.019 | ±0.127      | 0.670 | ±0.008 |                 |

| С   | 2.466  | ±0.279      | 0.097 | ±0.011 |                 |

| D   | 4.572  | ±0.127      | 0.180 | ±0.005 |                 |

| E   | 3.302  | ±0.127      | 0.130 | ±0.005 |                 |

| F   | 0.457  | ±0.051      | 0.018 | ±0.002 | Pin diameter    |

| G   | 1.270  | ±0.127      | 0.050 | ±0.005 | Flange diameter |

| ĸ   | 22.860 | ±0.127      | 0.900 | ±0.005 |                 |

| L   | 2.540  | ±0.127      | 0.100 | ±0.005 |                 |

| м   | 0.508  |             | 0.020 |        | Chamfer         |

| Table 4.1 68 p | oin grid array | package | dimensions |

|----------------|----------------|---------|------------|

| 1401C 4.1 00 p | ni gilu allaj  | package | unichalona |

Package weight is approximately 6.8 grams

Table 4.2 68 pin grid array package junction to ambient thermal resistance

| SYMBOL | PARAMETER                                | MIN | NOM | MAX | UNITS | NOTE |

|--------|------------------------------------------|-----|-----|-----|-------|------|

| θJA    | At 400 linear ft/min transverse air flow |     |     | 35  | °C/W  |      |

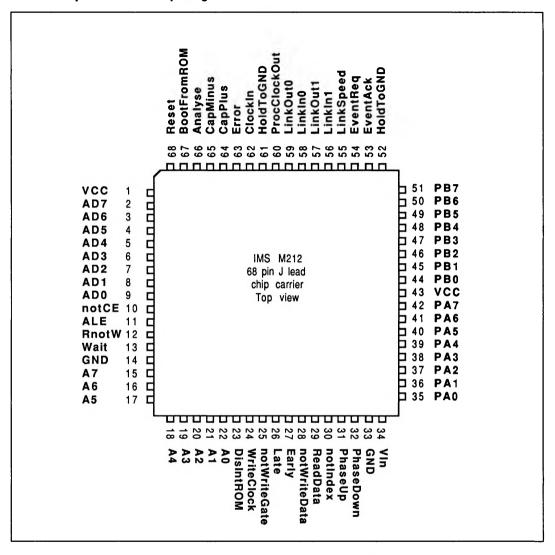

Figure 4.3 IMS M212 68 pin PLCC J-bend package pinout

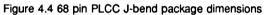

|     | Millim | Millimetres |       | les    |       |

|-----|--------|-------------|-------|--------|-------|

| DIM | NOM    | TOL         | NOM   | TOL    | Notes |

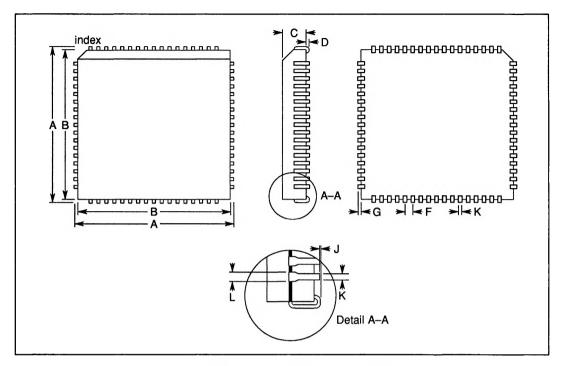

| A   | 25.146 | ±0.127      | 0.990 | ±0.005 |       |

| В   | 24.232 | ±0.127      | 0.954 | ±0.005 |       |

| C   | 3.810  | ±0.127      | 0.150 | ±0.005 |       |

| D   | 0.508  | ±0.127      | 0.020 | ±0.005 |       |

| F   | 1.270  | ±0.127      | 0.050 | ±0.005 |       |

| G   | 0.457  | ±0.127      | 0.018 | ±0.005 |       |

| J   | 0.000  | ±0.051      | 0.000 | ±0.002 |       |

| ĸ   | 0.457  | ±0.127      | 0.018 | ±0.005 |       |

| L   | 0.762  | ±0.127      | 0.030 | ±0.005 |       |

| Table 4.3 | 68 pin P | LCC J-bend | package | dimensions |

|-----------|----------|------------|---------|------------|

|-----------|----------|------------|---------|------------|

Package weight is approximately 5.0 grams

Table 4.4 68 pin PLCC J-bend package junction to ambient thermal resistance

| SYMBOL | PARAMETER                                | MIN | NOM | MAX | UNITS | NOTE |

|--------|------------------------------------------|-----|-----|-----|-------|------|

| θJA    | At 400 linear ft/min transverse air flow |     | 35  |     | °C/W  |      |

# 5 Ordering

This section indicates the designation of speed and package selections for the various devices. Speed of ClockIn is 5 MHz for all parts. Transputer processor cycle time is nominal; it can be calculated more exactly using the phase lock loop factor PLLx, as detailed in the external memory section.

For availability contact local INMOS sales office or authorised distributor.

| INMOS<br>designation | Processor<br>clock speed | Processor<br>cycle time | PLLx | Package             |

|----------------------|--------------------------|-------------------------|------|---------------------|

| IMS M212-G15S        | 15 MHz                   | 67 ns                   | 3.0  | Ceramic Pin Grid    |

| IMS M212-G20S        | 20 MHz                   | 50 ns                   | 4.0  | Ceramic Pin Grid    |

| IMS M212-J15S        | 15 MHz                   | 67 ns                   | 3.0  | Plastic PLCC J-Bend |

| IMS M212-J20S        | 20 MHz                   | 50 ns                   | 4.0  | Plastic PLCC J-Bend |

Table 5.1 IMS M212 ordering details