# National Semiconductor

### DM54166 8-Bit Parallel In/Serial Out Shift Registers

#### **General Description**

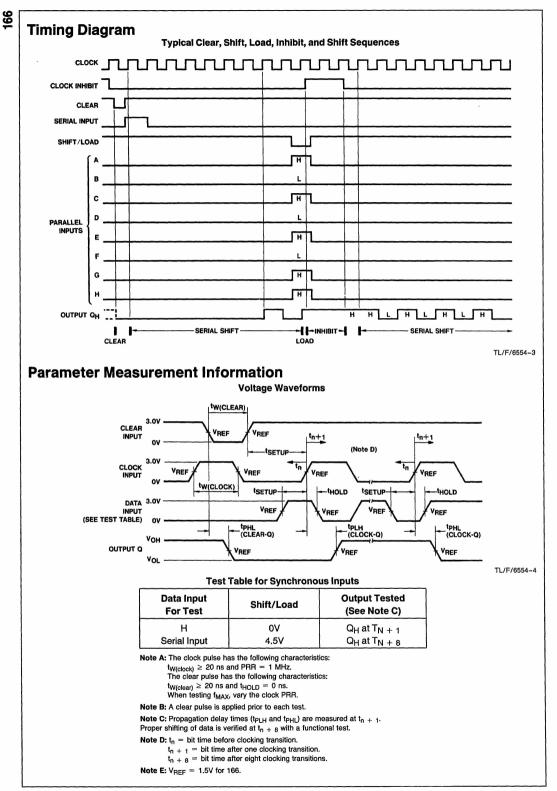

These parallel-in or serial-in, serial-out shift registers feature gated clock inputs and an overriding clear input. All inputs are buffered to lower the drive requirements to one normalized load, and input clamping diodes minimize switching transients to simplify system design. The load mode is established by the shift/load input. When high, this input enables the serial data input and couples the eight flip-flops for serial shifting with each clock pulse. When low, the parallel (broadside) data inputs are enabled and synchronous loading occurs on the next clock pulse. During parallel loading, serial data flow is inhibited. Clocking is accomplished on the low-to-high-level edge of the clock pulse through a twoinput NOR gate, permitting one input to be used as a clockenable or clock-inhibit function. Holding either of the clock inputs high inhibits clocking; holding either low enables the other clock input. This allows the system clock to be freerunning, and the register can be stopped on command with the other clock input. The clock-inhibit input should be changed to the high level only while the clock input is high. A buffered, direct clear input overrides all other inputs, including the clock, and sets all flip-flops to zero.

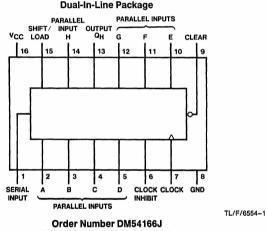

## Connection Diagram

See NS Package Number J16A

#### **Function Table**

| Inputs |        |         |            | Internal |          |                 |                 |                 |

|--------|--------|---------|------------|----------|----------|-----------------|-----------------|-----------------|

| Clear  | Shift/ | Clock   | Clock      | Serial   | Parallel | Out             |                 | Output          |

| U.U.I. | Load   | Inhibit | 0.001      | Contai   | АН       | QA              | QB              | а <sub>н</sub>  |

| L      | Х      | Х       | Х          | X        | X        | L               | L               | L               |

| н      | X      | L       | L          | X        | X        | Q <sub>A0</sub> | Q <sub>B0</sub> | Q <sub>H0</sub> |

| н      | L      | L       | I ↑        | X        | ah       | a               | b               | h               |

| н      | н      | L       | $\uparrow$ | н        | X        | н               | Q <sub>An</sub> | QGn             |

| н      | н      | L       | ↑          | L        | X        | L               | Q <sub>An</sub> | QGn             |

| Н      | Х      | Н       | <b>↑</b>   | Х        | Х        | Q <sub>A0</sub> | Q <sub>B0</sub> | Q <sub>H0</sub> |

H = High Level (steady state), L = Low Level (steady state)

X = Don't Care (any input, including transitions)

↑ = Transition from Low to High Level

a ... h = The level of stead-state input at inputs A through H, respectively

$Q_{A0},\,Q_{B0},\,Q_{H0}=$  The level of  $Q_A,\,Q_B,\,Q_H,$  respectively, before the indicated steady-state input conditions were established

QAn, QGn = The level of QA, QG, respectively, before the most recent  $\uparrow$  transition of the clock

166

99

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

| Supply Voltage                       | 7V              |

|--------------------------------------|-----------------|

| Input Voltage                        | 5.5V            |

| Operating Free Air Temperature Range |                 |

| DM54                                 | -55°C to +125°C |

| Storage Temperature Range            | -65°C to +150°C |

Note: The "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the "Electrical Characteristics" table are not guaranteed at the absolute maximum ratings. The "Recommended Operating Conditions" table will define the conditions for actual device operation.

#### **Recommended Operating Conditions**

| Symbol          | Paramet                        |       | DM54166 |     |       |     |

|-----------------|--------------------------------|-------|---------|-----|-------|-----|

| oymbol          | T alance                       | Min   | Nom     | Max | Units |     |

| V <sub>CC</sub> | Supply Voltage                 |       | 4.5     | 5   | 5.5   | v   |

| VIH             | High Level Input Voltage       |       | 2       |     |       | V   |

| VIL             | Low Level Input Voltage        |       |         |     | 0.8   | V   |

| IOH             | High Level Output Current      |       |         |     | -0.8  | mA  |

| IOL             | Low Level Output Current       |       |         |     | 16    | mA  |

| fCLK            | Clock Frequency (Note 4)       |       | 0       |     | 25    | MHz |

| tw              | Pulse Width (Note 4)           | Clock | 24      |     |       | ns  |

|                 |                                | Clear | 20      |     |       |     |

| tsu             | Setup Time (Note 4)            | Mode  | 30      |     |       | ns  |

|                 |                                | Data  | 20      |     |       | 113 |

| t <sub>H</sub>  | Data Hold Time (Note 4)        |       | 0       |     |       | ns  |

| T <sub>A</sub>  | Free Air Operating Temperature |       | -55     |     | 125   | °C  |

#### Electrical Characteristics over recommended operating free air temperature range (unless otherwise noted)

| Symbol          | Parameter                            | Conditions                                                   | Min | Typ<br>(Note 1) | Max  | Units |

|-----------------|--------------------------------------|--------------------------------------------------------------|-----|-----------------|------|-------|

| Vi              | Input Clamp Voltage                  | $V_{CC} = Min, I_I = -12 mA$                                 |     |                 | -1.5 | v     |

| V <sub>OH</sub> | High Level Output Voltage            | $V_{CC} = Min, I_{OH} = Max$<br>$V_{IL} = Max, V_{IH} = Min$ | 2.4 |                 |      | v     |

| V <sub>OL</sub> | Low Level Output Voltage             | $V_{CC} = Min, I_{OL} = Max$<br>$V_{IH} = Min, V_{IL} = Max$ |     |                 | 0.4  | v     |

| ų               | Input Current @ Max<br>Input Voltage | $V_{CC} = Max, V_{I} = 5.5V$                                 |     |                 | 1    | mA    |

| lін             | High Level Input Current             | $V_{CC} = Max, V_I = 2.4V$                                   |     |                 | 40   | μΑ    |

| ЦĽ              | Low Level Input Current              | $V_{CC} = Max, V_I = 0.4V$                                   |     |                 | -1.6 | mA    |

| los             | Short Circuit Output Current         | V <sub>CC</sub> = Max (Note 2)                               | -20 |                 | -57  | mA    |

| Icc             | Supply Current                       | V <sub>CC</sub> = Max (Note 3)                               |     | 72              | 104  | mA    |

Note 1: All typicals are at  $V_{CC} = 5V$ ,  $T_A = 25^{\circ}C$ .

Note 2: Not more than one output should be shorted at a time.

Note 3: With all outputs open, 4.5V applied to the SERIAL input, all other inputs except CLOCK grounded, I<sub>CC</sub> is measured after a momentary ground, then 4.5V, is applied to the CLOCK.

Note 4:  $T_A = 25^{\circ}C$  and  $V_{CC} = 5V$ .

| Symbol           | Parameter                                          | From (Input)<br>To (Output) | $R_L = 400\Omega, C_L = 15  pF$ |     | Units |

|------------------|----------------------------------------------------|-----------------------------|---------------------------------|-----|-------|

|                  |                                                    |                             | Min                             | Max | 01113 |

| f <sub>MAX</sub> | Maximum Clock Frequency                            |                             | 25                              |     | MHz   |

| <sup>t</sup> PLH | Propagation Delay Time<br>Low to High Level Output | Clock to<br>Output          | 8                               | 26  | ns    |

| t <sub>PHL</sub> | Propagation Delay Time<br>High to Low Level Output | Clock to<br>Output          | . 8                             | 30  | ns    |

| <sup>t</sup> PHL | Propagation Delay Time<br>High to Low Level Output | Clear to<br>Output          |                                 | 35  | ns    |

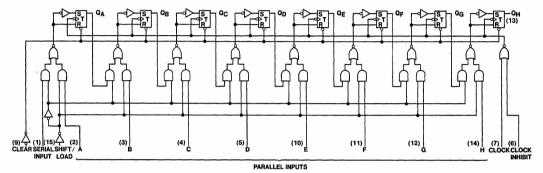

### Logic Diagram

TL/F/6554-2

.