# Lithium Ion Pack Supervisor for 3- and 4-Cell Packs

### **Features**

- ➤ Protects and individually monitors three or four Li-Ion series cells for overvoltage, undervoltage

- ➤ Monitors pack for overcurrent

- ➤ Designed for battery pack integration

- ➤ Minimal external components

- ➤ Drives external FET switches

- ➤ Selectable overvoltage (Vov) thresholds

- Mask-programmable by Texas Instruments

- Standard version-4.25V

- ➤ Supply current: 25µA typical

- ➤ Sleep current: 0.7µA typical

- ➤ 16-pin 150-mil narrow SOIC

### **General Description**

The bq2058 Lithium Ion Pack Supervisor is designed to control the charge and discharge cell voltages for three or four lithium ion (Li-Ion) series cells, accommodating battery packs containing series/parallel configurations. The low operating current does not overdischarge the cells during periods of storage and does not significantly increase the system discharge load. The bq2058 can be part of a low-cost Li-Ion charge control system within the battery pack.

The bq2058 controls two external FETs to limit the charge and discharge potentials. The bq2058 allows charging when each individual cell voltage is below  $V_{OV}$  (overvoltage limit). If the voltage on any cell exceeds  $V_{OV}$  for a user-configurable delay period ( $t_{OVD}$ ), the  $\overline{CHG}$  pin is driven high, shutting off charge to the battery pack. This safety feature pre-

vents overcharge of any cell within the battery pack. After an overvoltage condition occurs, each cell must fall below  $V_{\rm CE}$  (charge enable voltage) for the bq2058 to re-enable charging.

The bq2058 protects batteries from overdischarge. If the voltage on any cell falls below  $V_{UV}$  (undervoltage limit) for a user-configurable delay period ( $t_{UVD}$ ), the  $\overline{DSG}$  output is driven high, shutting off the battery discharge. This safety feature prevents overdischarge of any cell within the battery pack.

The bq2058 also stops discharge on detection of an overcurrent condition, such as a short circuit. If an overcurrent condition occurs for a user-configurable delay period (tocd), the DSG output is driven high, disconnecting the load from the pack. DSG remains high until removal of the short circuit or overcurrent condition.

### **Pin Connections**

# CHG 1 16 DSG CTL 2 15 NSEL VSS 3 14 UVD CSL 4 13 OVD BAT4N 5 12 OCD BAT3N 6 11 VCC BAT2N 7 10 CSH BAT1N 8 9 BAT1P 16-Pin Narrow SOIC

### **Pin Names**

| CHG           | Change control cutmut    | DSG        | Discharge control output |

|---------------|--------------------------|------------|--------------------------|

|               | Charge control output    | NSEL       | 3- or 4-cell selection   |

| CTL           | Pack disable input       | UVD        | Undervoltage delay input |

| $V_{SS}$      | Low potential input      | OVD        | 2 7 1                    |

| CSL           | Current sense low-side   | ~          | Overvoltage delay input  |

|               | input                    | OCD        | Overcurrent delay input  |

| $BAT_{4N}$    | Battery 4 negative input | $V_{CC}$   | High potential input     |

| $BAT_{3N}$    | Battery 3 negative input | CSH        | Current sense high-side  |

| $BAT_{2N} \\$ | Battery 2 negative input |            | input                    |

| $BAT_{1N}$    | Battery 1 negative input | $BAT_{1P}$ | Battery 1 positive input |

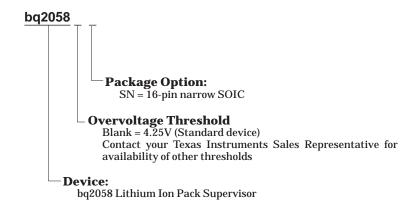

# bq2058

| Pin De            | escriptions                                                                                                                                                                  |                   | This input is connected to $BAT_{1P}$ in a three-cell configuration.                                                                       |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| <b>CHG</b>        | Charge control output                                                                                                                                                        | DSG               | Discharge control output                                                                                                                   |

|                   | This push-pull output controls the charge path to the battery pack. Charging is allowed when low.                                                                            |                   | This push-pull output controls the discharge path to the battery pack. Discharge is allowed when low.                                      |

| CTL               | Pack disable input                                                                                                                                                           | NSEL              | Number of cells input                                                                                                                      |

|                   | When high, this input allows an external source to disable the pack by making both $\overline{DSG}$ and $\overline{CHG}$ inactive. For normal operation, the CTL pin is low. |                   | This input selects the number of series cells in the pack. NSEL should connect to $V_{CC}$ for four cells and to $V_{SS}$ for three cells. |

| Vss               | Low potential input                                                                                                                                                          | UVD               | Undervoltage delay input                                                                                                                   |

| CSL               | Overcurrent sense low-side input                                                                                                                                             |                   | This input uses an external capacitor to $\ensuremath{V_{CC}}$ to set the undervoltage delay timing.                                       |

|                   | This input is connected between the low-side                                                                                                                                 | OVD               | Overvoltage delay input                                                                                                                    |

|                   | discharge FET (or sense resistor) and BAT <sub>4N</sub> to enable overcurrent sensing in the battery pack's ground path.                                                     |                   | This input uses an external capacitor to $\ensuremath{V_{CC}}$ to set the overvoltage delay timing.                                        |

| BAT <sub>4N</sub> | Battery 4 negative input                                                                                                                                                     | OCD               | Overcurrent delay input                                                                                                                    |

|                   | This input is connected to the negative terminal of the cell designated BAT4 in Figure 2.                                                                                    |                   | This input uses an external capacitor to $\ensuremath{V_{CC}}$ to set the overcurrent delay timing.                                        |

| BAT <sub>3N</sub> | Battery 3 negative input                                                                                                                                                     | $\mathbf{V_{CC}}$ | High potential input                                                                                                                       |

|                   | This input is connected to the negative terminal                                                                                                                             | CSH               | Overcurrent sense high-side input                                                                                                          |

|                   | of the cell designated BAT3 in Figure 2.                                                                                                                                     |                   | This input is connected between the                                                                                                        |

| BAT <sub>2N</sub> | Battery 2 negative input                                                                                                                                                     |                   | high-side discharge FET (or sense resistor) and BAT <sub>1P</sub> to enable overcurrent sense in                                           |

|                   | This input is connected to the negative terminal of the cell designated BAT2 in Figure 2.                                                                                    |                   | the battery pack's positive supply path.                                                                                                   |

| BAT <sub>1N</sub> | Battery 1 negative input                                                                                                                                                     | BAT <sub>1P</sub> | Battery 1 positive input                                                                                                                   |

| 2712 114          | This input is connected to the negative terminal of the cell designated BAT1 in Figure 2.                                                                                    |                   | This input is connected to the positive terminal of the cell designated BAT1 in Figure 2.                                                  |

Table 1. Pin Configuration for 3- and 4-Series Cells

| Number of Cells | Configuration Pins                          | Battery Pins                                         |

|-----------------|---------------------------------------------|------------------------------------------------------|

|                 |                                             | BAT <sub>1N</sub> – Positive terminal of first cell  |

| 0 11            | BAT <sub>1N</sub> tied to BAT <sub>1P</sub> | BAT <sub>2N</sub> - Negative terminal of first cell  |

| 3 cells         | $NSEL = V_{SS}$                             | BAT <sub>3N</sub> - Negative terminal of second cell |

|                 |                                             | BAT <sub>4N</sub> - Negative terminal of third cell  |

|                 | 4 cells $NSEL = V_{CC}$                     | BAT <sub>1P</sub> – Positive terminal of first cell  |

|                 |                                             | BAT <sub>1N</sub> - Negative terminal of first cell  |

| 4 cells         |                                             | BAT <sub>2N</sub> – Negative terminal of second cell |

|                 |                                             | BAT <sub>3N</sub> - Negative terminal of third cell  |

|                 |                                             | BAT <sub>4N</sub> – Negative terminal of fourth cell |

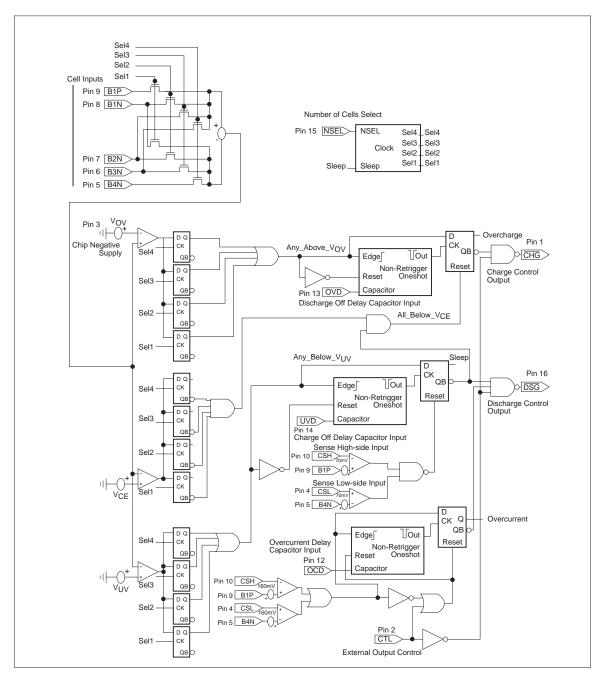

Figure 1. Block Diagram

## **Functional Description**

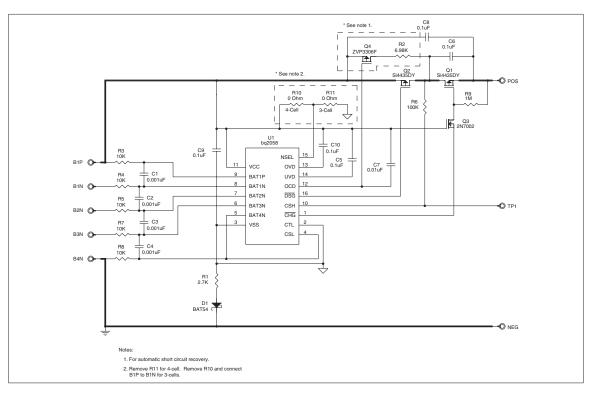

Figure 1 is a block diagram outlining the major components of the bq2058. Figure 2 shows a 3- or 4-cell pack supervisor circuit. The following sections detail the various functional aspects of the bq2058.

### **Thresholds**

The bq2058 monitors the lithium ion pack for the conditions listed below. Shown with these conditions are the respective thresholds used to determine if that condition exists:

Overvoltage (VoV)

Undervoltage (V<sub>UV</sub>)

Overcurrent (Voch, Vocl)

Charge Enable (VCE)

Charge Detect (V<sub>CD</sub>)

The bq2058 samples a cell every 40ms (typical). Every sample is a fully differential measurement of each cell. During this sample period, the bq2058 compares the measurements with these thresholds to determine if any of the these conditions exist:  $V_{OV}$ ,  $V_{UV}$ , and  $V_{CE}$ .

Overcurrent and charge detect are conditions that are not sampled, but are continuously monitored.

### Initialization

On initial power-up, such as connecting the battery pack for the first time to the bq2058, the  $\underline{bq2058}$  enters the low-power sleep mode, disabling the  $\overline{DSG}$  output. It is recommended that a top to bottom cell connection be made at pack assembly for proper initialization. A charging supply must be applied to the bq2058 circuit to enable the pack. See Low-Power Sleep Mode and Charge Detect sections.

Figure 2. 3- or 4-Cell Li-Ion Battery Pack Supervisor

### **Low-Power Sleep Mode**

The bq2058 enters the low-power sleep mode in two different ways:

- 1. On initial power-up

- 2. After the detection of an undervoltage condition–  $V_{\rm UV}$

When the bq2058 enters the low-power sleep mode,  $\overline{DSG}$  is driven high and the device consumes 0.7 $\mu$ A (typical). The bq2058 only comes out of low-power sleep mode when a valid charge-detect condition exists.

### **Charge Detect**

The bq2058 continuously monitors for a charge-detect condition. A valid charge-detect condition exists when either of the conditions is true:

$$\begin{split} &CSL < BAT_{4N} \text{ - } 70mV \text{ } (V_{CD}) \\ &CSH > BAT_{1P} + 70mV \text{ } (V_{CD}) \end{split}$$

A valid charge-detect enables the  $\overline{DSG}$  output, allowing charging of the lithium ion cells. This is accomplished by applying the charging supply to the pack.

### Undervoltage

Undervoltage (or overdischarge) protection is asserted when any cell voltage drops below the  $V_{UV}$  threshold and remains below the  $V_{UV}$  threshold for a time exceeding a user-configurable delay (t $_{UVD}$ ). The  $\overline{DSG}$  output is driven high disabling the discharge of the pack. The bq2058 then enters the low-power sleep mode.

### Overvoltage

Overvoltage (or overcharge) protection is asserted when any cell voltage exceeds the  $V_{\rm OV}$  threshold and remains above the  $V_{\rm OV}$  threshold for a time exceeding a user-configurable delay (t\_{\rm OVD}). The  $\overline{\rm CHG}$  pin is driven high, disabling charge into the battery pack. Charging is disabled until a valid charge enable exists. See Charge Enable section

Important note: If any battery pin floats (BAT $_{1P}$ , BAT $_{1N^-4N}$ ), the bq2058 assumes an overvoltage has occurred.

Because of different manufacturers specifications for overvoltage thresholds, the bq2058 can be available with different  $V_{\rm OV}$  options. Table 2 summarizes these different voltage thresholds.

Table 2. Overvoltage Threshold Options

| Part No. | V <sub>OV</sub> Limit |

|----------|-----------------------|

| bq2058   | 4.25V                 |

| bq2058C  | 4.325V                |

| bq2058R  | 4.35V                 |

The overvoltage threshold limits are programmed by Texas Instruments. The bq2058 is the standard option that is more readily available for sampling and prototyping purposes. Please contact your Texas Instruments Sales Representative for other voltage threshold and tolerance options.

### **Charge Enable**

A valid charge enable indicates that an overvoltage (overcharge) condition no longer exists and that the pack is ready to accept further charge. Once overvoltage protection is asserted, charging will not be enabled until all cell voltages fall below  $V_{CE}.$  The  $V_{CE}$  threshold is a function of  $V_{OV}$  and changes with different  $V_{OV}$  limits.

$$V_{CE} = V_{OV} - 150 mV$$

### **Overcurrent**

The bq2058 detects an overcurrent (or short circuit) condition only in the discharge direction. Overcurrent protection is asserted when either of the conditions occurs and remains for a time exceeding a user-configurable delay ( $t_{\rm OCD}$ ):

$$CSL > BAT_{4N} + V_{OCL}$$

$CSH < BAT_{1P} - V_{OCH}$

where

$V_{OCL} = 160 \text{mV}$  (low-side detect)

$V_{OCH} = 160 mV$  (high-side detect)

When either of these conditions occurs,  $\overline{DSG}$  is driven high, disconnecting the load from the pack.  $\overline{DSG}$  remains high until both of the voltage conditions are false, indicating removal of the short-circuit condition. The user can facilitate clearing these conditions by inserting the battery pack into a charger.

The low-side overcurrent sense can be disabled by connecting CSL to BAT $_{4N}$ . This ensures that CSL is never greater than BAT $_{4N}$ . If low-side detection is disabled, high-side detection must be used with CSH.

$\frac{The\ FETs\ in\ the\ charge/discharge\ path\ controlled\ by\ the}{CHG\ and\ DSG\ pins\ affect\ the\ overcurrent\ level.}\ The\ on-resistance\ of\ these\ FETs\ need\ to\ be\ taken\ into\ account\ when\ determining\ overcurrent\ levels.}$

| Condition              | CHG pin | DSG pin       |

|------------------------|---------|---------------|

| Normal operation       | Low     | Low           |

| Overvoltage            | High    | Low           |

| Undervoltage           | Low     | High          |

| Overcurrent            | Low     | High          |

| Floating battery input | High    | Indeterminate |

| CTL = high             | High    | High          |

### CHG and DSG States

The  $\overline{CHG}$  and  $\overline{DSG}$  output truth table is shown below.

The polarities of CHG and DSG are mask programmable at Texas Instruments. Push-pull vs. open-drain configuration is also mask-configurable at Texas Instruments. Please contact your Texas Instruments Sales Representative for availability of these variations.

### **Number of Cells**

The user must configure the bq2058 for three- or four-series cell operation. For a three-cell pack, NSEL should be tied directly to  $V_{SS}.\;$  For a four-cell pack,  $N_{SEL}$  should be connected directly to  $V_{CC}.\;$

| Number of Series Cells | NSEL                    |

|------------------------|-------------------------|

| 3-cell                 | Tied to V <sub>SS</sub> |

| 4-cell                 | Tied to Vcc             |

### Pack Disable Input-CTL

The CTL pin is used to electrically disconnect the battery from the pack terminals through an externally supplied signal. When CTL is taken high, CHG and DSG are driven high. Any load on the pack terminals will be interpreted as an overcurrent condition by the bq2058 with the overcurrent delay timer held in reset. When the CTL pin is driven low, the overcurrent delay timer is allowed to start. If the programmed delay  $(t_{OCD})$  is too short, the overcurrent recovery circuit, if implemented, will be unable to correct the overcurrent situation prior to the delay time-out. It is recommended that a delay time of greater than  $10ms\ (C_{OCD}\ \geq\ 0.01\mu F)$  be used if the CTL pin function is used.

Important note: If CTL  $\underline{floats}$ , it  $\underline{is}$  internally pulled high making both  $\overline{DSG}$  and  $\overline{CHG}$  inactive, thus disabling the pack. If CTL is not used, it should be tied to  $V_{SS}$ .

The polarity of CTL is mask programmable at Texas Instruments. Please contact your Texas Instruments Sales Representative for other polarity options.

### **Protection Delay Timers**

The delay time between the detection of an overcurrent, overvoltage, or undervoltage condition and the deactivation of the  $\overline{CHG}$  and/or  $\overline{DSG}$  outputs is user-configurable by the selection of capacitor values between  $V_{CC}$  and OCD, OVD, and UVD pins (respectively). See Table 3 below.

The fault condition must persist through the entire delay period, or the bq2058 may not deactivate either FET control output.

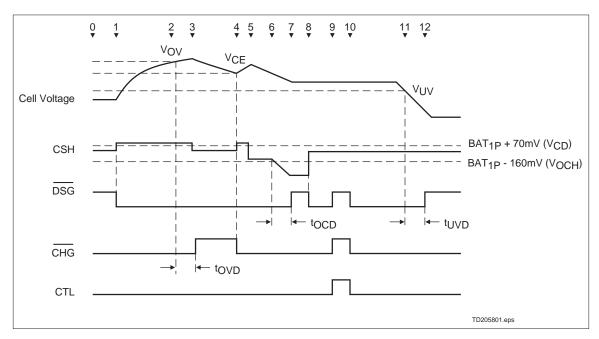

Figure 3 shows a step-by-step event cycle for the bq2058.

Table 3. Protection Delay Timers

| Protection Delay C |                  | Capacitor from      | Тур       |       |           |

|--------------------|------------------|---------------------|-----------|-------|-----------|

| Feature            | Period           | V <sub>CC</sub> to: | Capacitor | Time  | Tolerance |

| Overcurrent        | t <sub>OCD</sub> | OCD                 | 0.010μF   | 12ms  | ±40%      |

| Overvoltage        | tovD             | OVD                 | 0.100μF   | 950ms | ±40%      |

| Undervoltage       | t <sub>UVD</sub> | UVD                 | 0.100μF   | 950ms | ±40%      |

Notes:

- 1. The delay time versus capacitance can be approximated by the following equations: For tocd:  $t_{(s)}\approx 1.2*C_{(\mu f)}, \quad \text{where } C\geq 0.001 \mu F$

- For t<sub>OVD</sub>, t<sub>UVD</sub>:  $t_{(s)} \approx 1.2 \times C_{(\mu f)}$ , where  $C \ge 0.001 \mu F$  where  $C \ge 0.01 \mu F$

- 2. Overvoltage and undervoltage conditions are sampled by the bq2058. The delay in Table 2 is in addition to the time required for the bq2058 to detect the violation, which may vary from 0 to 160ms depending on where in the sampling period the violation occurs. Overcurrent is continuously monitored and is subject to a delay of approximately 1.5ms.

Figure 3. Protector Event Diagram

### **Event Definition**

- 0: The bq2058 is in the low-power sleep mode because one or more of the cell voltages are below  $V_{\rm UV}$ .

- 1: A charger is applied to the pack, causing the difference between CSH and  $BAT_{1P}$  to become greater than 70mV. This awakens the bq2058, and the discharge pin  $\overline{DSG}$  goes low.

- 2: One or more cells charge to a voltage equal to  $V_{\text{OV}}$ , initiating the overvoltage delay timer.

- 3: The overvoltage delay time expires, causing  $\overline{\text{CHG}}$  to be driven high.

- 4: All cell voltages fall below V<sub>CE</sub>, causing <del>CHG</del> to be driven low.

- 5: Stop charging; apply a load.

- 6: An overcurrent condition is detected, initiating the overcurrent delay timer.

- 7: The overcurrent delay time expires, causing  $\overline{DSG}$  to be driven high.

- 8: The overcurrent condition is no longer present;  $\overline{DSG}$  is driven low.

- 9: Pin CTL is driven high; both  $\overline{DSG}$  and  $\overline{CHG}$  are driven high.

- 10: Pin CTL is driven low; both  $\overline{DSG}$  and  $\overline{CHG}$  resume their normal function.

- 11: One or more cells fall below V<sub>UV</sub>, initiating the overdischarge delay timer.

- 12:  $\frac{Once \text{ the overdischarge delay timer expires, if any of the cells is below } V_{UV}, \text{ the bq2058 drives}}{\overline{DSG} \text{ high and enters the low-power sleep mode.}}$

# **Absolute Maximum Ratings**

| Symbol              | Parameter             | Value       | Unit | Conditions                                        |

|---------------------|-----------------------|-------------|------|---------------------------------------------------|

| $V_{\rm CC}$        | Supply voltage        | 18          | V    | Relative to V <sub>SS</sub>                       |

| T <sub>OPR</sub>    | Operating temperature | -30 to +70  | °C   |                                                   |

| T <sub>STG</sub>    | Storage temperature   | -55 to +125 | °C   |                                                   |

| T <sub>SOLDER</sub> | Soldering temperature | 260         | °C   | For 10 seconds                                    |

| I <sub>IN</sub>     | Maximum input current | ±100        | μΑ   | All pins except V <sub>CC</sub> , V <sub>SS</sub> |

### Notes:

- 1 Permanent device damage may occur if **Absolute Maximum Ratings** are exceeded. Functional operation should be limited to the Recommended DC Operating Conditions detailed in this data sheet. Exposure to conditions beyond the operational limits for extended periods of time may affect device reliability.

- 2. Internal protection diodes are in place on every pin relative to  $V_{\text{CC}}$  and  $V_{\text{SS}}.$  See Figure 4.

**Figure 4. Internal Protection Diodes**

# DC Electrical Characteristics (TA = TOPR)

| Symbol           | Parameter           | Minimum               | Typical | Maximum               | Unit | Conditions/Notes                                   |

|------------------|---------------------|-----------------------|---------|-----------------------|------|----------------------------------------------------|

| V <sub>OH</sub>  | Output high voltage | V <sub>CC</sub> - 0.5 | -       | -                     | V    | $I_{OH} = 10\mu A, \overline{CHG}, \overline{DSG}$ |

| $V_{OL}$         | Output low voltage  | -                     | -       | $V_{SS} + 0.5$        | V    | $I_{OL} = 10\mu A, \overline{CHG}, \overline{DSG}$ |

| Vop              | Operating voltage   | 4                     | -       | 18.0                  | V    | V <sub>CC</sub> relative to V <sub>SS</sub>        |

| $V_{IL}$         | Input low voltage   | -                     | -       | V <sub>SS</sub> + 0.5 | V    | Pin CTL                                            |

| V <sub>IH</sub>  | Input high voltage  | V <sub>SS</sub> + 2.0 | -       | -                     | V    | Pin CTL                                            |

| $V_{\rm IL}$     | Input low voltage   | -                     | -       | V <sub>SS</sub> + 0.5 | V    | Pin NSEL                                           |

| V <sub>IH</sub>  | Input high voltage  | V <sub>CC</sub> - 0.5 | -       | -                     | -    | Pin NSEL                                           |

| I <sub>CCA</sub> | Active current      | -                     | 25      | 40                    | μΑ   |                                                    |

| I <sub>CCS</sub> | Sleep current       | -                     | 0.7     | 1.5                   | μΑ   |                                                    |

# DC Thresholds (TA = TOPR)

| Symbol           | Parameter                    | Value                   | Unit    | Tolerance    | Condition                                                      |

|------------------|------------------------------|-------------------------|---------|--------------|----------------------------------------------------------------|

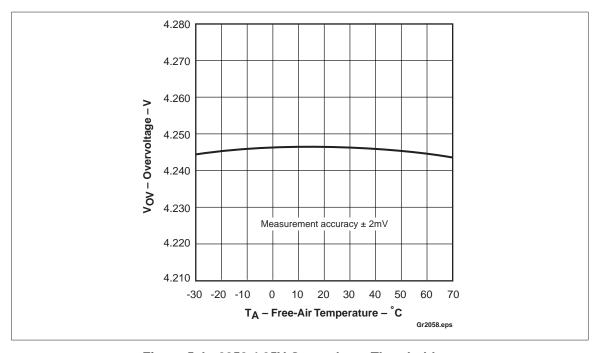

| V                | Overvoltage threshold        | 4.25                    | V       | ±50mV        | See note 1.                                                    |

| Vov              | (See Figure 5.)              |                         | Table 2 | 2            | Customer option                                                |

| VCE              | Charge enable threshold      | V <sub>OV</sub> - 150mV | V       | ±50mV        |                                                                |

| $V_{UV}$         | Undervoltage threshold       | 2.25                    | V       | ±100mV       |                                                                |

| V <sub>OCH</sub> | Overcurrent detect high-side | 160                     | mV      | ±35mV        |                                                                |

| V <sub>OCL</sub> | Overcurrent detect low-side  | 160                     | mV      | ±35mV        |                                                                |

| $V_{CD}$         | Charge detect threshold      | 70                      | mV      | -60mV, +80mV |                                                                |

| t <sub>OVD</sub> | Overvoltage delay threshold  | 950                     | ms      | ±40%         | $C_{OVD}$ = 0.100 $\mu$ F, $T_A$ = 30 $^{\circ}$ C See note 2. |

| t <sub>UVD</sub> | Undervoltage delay threshold | 950                     | ms      | ±40%         | $C_{UVD} = 0.100 \mu F, T_A = 30^{\circ} C$ See note 2.        |

| t <sub>OCD</sub> | Overcurrent delay threshold  | 12                      | ms      | ±40%         | $C_{OCD} = 0.01 \mu F, T_A = 30^{\circ} C$                     |

### **Notes:**

- $1. \ Standard \ device. \ Contact \ your \ Texas \ Instruments \ Sales \ Representative \ for \ different \ thresholds \ and \ tolerance \ options.$

- 2. Does not include cell sampling delay, which may add up to 160ms of additional delay until the condition is detected.

# bq2058

# **Impedance**

| Symbol            | Parameter       | Minimum | Typical | Maximum | Unit | Notes                                                  |

|-------------------|-----------------|---------|---------|---------|------|--------------------------------------------------------|

| R <sub>CELL</sub> | Input impedance | -       | 10      | -       | ΜΩ   | Pins BAT <sub>1P,</sub> BAT <sub>1N-4N,</sub> CSH, CSL |

Figure 5. bq2058 4.25V Overvoltage Threshold vs. Free-Air Temperature

### **Data Sheet Revision History**

| Change No. | Page No. | Description                                                                | Nature of Change                                                                                                                                                                                                                  |  |  |

|------------|----------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1          | 1, 2, 5  | PACK+, PACK-                                                               | Pins renamed to CSH and CSL respectively                                                                                                                                                                                          |  |  |

| 1          | 1        | Pin description                                                            | Added CSH/CSL description                                                                                                                                                                                                         |  |  |

| 1          | 3        | Block diagram                                                              | Update Block diagram                                                                                                                                                                                                              |  |  |

| 1          | 4        | Figure 2                                                                   | Update typical application circuit                                                                                                                                                                                                |  |  |

| 1          | 4        | Configuration description                                                  | Correction to description                                                                                                                                                                                                         |  |  |

| 1, 2       | 5        | Overcurrent limits                                                         | $\begin{aligned} Was: V_{OCH} &= 150 mV \pm 25 mV \\ V_{OCL} &= 85 mV \pm 25 mV \\ Is: V_{OCH} &= 160 mV \pm 25 mV \\ V_{OCL} &= 100 mV \pm 25 mV \end{aligned}$                                                                  |  |  |

| 1          | 7        | Figure 3                                                                   | Update Event diagram                                                                                                                                                                                                              |  |  |

| 1, 2       | 9        | DC threshold                                                               | $\begin{aligned} Was: V_{OCH} &= 150 mV \pm 25 mV \\ V_{OCL} &= 100 mV \pm 80 mV \\ V_{CD} &= 70 mV - 60, +50 mV \\ Is: V_{OCH} &= 160 mV \pm 25 mV \\ V_{OCL} &= 100 mV \pm 25 mV \\ V_{CD} &= 70 mV - 60, +80 mV \end{aligned}$ |  |  |

| 3          | 1, 3, 5  | High-side overcurrent monitored                                            | Was: Between V <sub>CC</sub> and CSH,<br>Is: Between BAT <sub>1P</sub> and CSH                                                                                                                                                    |  |  |

| 3          | 4        | Overvoltage threshold options                                              | Added bq2058R                                                                                                                                                                                                                     |  |  |

| 3          | 3, 5     | Overcurrent limit                                                          | Was: $V_{OCL} = 100 \text{mV}$ , Is: $V_{OCL} = 150 \text{mV}$                                                                                                                                                                    |  |  |

| 4          | 4        | Figure 2                                                                   | Corrected schematic                                                                                                                                                                                                               |  |  |

| 4          | 6, 8     | Protection Delay Times                                                     | $\begin{array}{l} Was: t_{OCD} = 10ms \pm 30\% \\ t_{OVD} = 800ms \ \pm 30\% \\ t_{UVD} = 800ms \pm 40\% \\ Is: t_{OCD} = 12ms \pm 40\% \\ t_{OVD} = 950ms \ \pm 40\% \\ t_{UVD} = 950ms \pm 40\% \end{array}$                    |  |  |

| 4          | 10       | Overcurrent limits                                                         |                                                                                                                                                                                                                                   |  |  |

| 5          | 5, 9     | Overvoltage threshold<br>Charge enable threshold<br>Undervoltage threshold | Added bq2058W                                                                                                                                                                                                                     |  |  |

| 6          | 9        | DC electrical characteristics                                              | Was: Minimum $V_{OP} = 0V$ , Is: Minimum $V_{OP} = 4V$                                                                                                                                                                            |  |  |

| 7          | 5, 9     | Overvoltage threshold                                                      | Added bq2058C and bq2058G                                                                                                                                                                                                         |  |  |

| 8          | 4        | Reference circuit amended                                                  | Moved D1 to new location                                                                                                                                                                                                          |  |  |

| 9          | 5, 9     | Overvoltage thresholds                                                     | Removed bq2058D, bq2058F, bq2058G, bq2058J, bq2058K, bq2058M, and bq2058W                                                                                                                                                         |  |  |

Notes: Change 1 = Feb. 1997 B changes from Jan. 1997 A. Change 2 = April 1997 C changes from Feb. 1997 B. Change 3 = June 1997 D changes from April 1997 C. Change 4 = July 1997 E changes from June 1997 D. Change 5 = Feb. 1998 F changes from July 1997 E. Change 6 = May 1998 G changes from Feb. 1998 F. Change 7 = June 1998 H changes from May 1998 G. Change 8 = Jan. 1999 I changes from June 1998 H. Change 9 = July 2000 SLUS070A changes from Jan. 1999 I.

# **Ordering Information**

| Package Devices      |               |                         |  |

|----------------------|---------------|-------------------------|--|

| TA                   | Vov Threshold | 16-pin Narrow SOIC (SN) |  |

| -30°C<br>to<br>+70°C | 4.25V         | bq2058SN                |  |

|                      | 4.325         | bq2058CSN               |  |

|                      | 4.35V         | bq2058RSN               |  |

Notes: bq2058SN is Standard Device. Contact your Texas Instruments Sales Representative for availability of other thresholds and tolerances.

### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| Applications       |                           |

|--------------------|---------------------------|

| Audio              | www.ti.com/audio          |

| Automotive         | www.ti.com/automotive     |

| Broadband          | www.ti.com/broadband      |

| Digital Control    | www.ti.com/digitalcontrol |

| Medical            | www.ti.com/medical        |

| Military           | www.ti.com/military       |

| Optical Networking | www.ti.com/opticalnetwork |

| Security           | www.ti.com/security       |

| Telephony          | www.ti.com/telephony      |

| Video & Imaging    | www.ti.com/video          |

| Wireless           | www.ti.com/wireless       |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated