# ADC12DS080 Dual 12-Bit, 80 MSPS A/D Converter with Serial LVDS Outputs

Check for Samples: ADC12DS080

# **FEATURES**

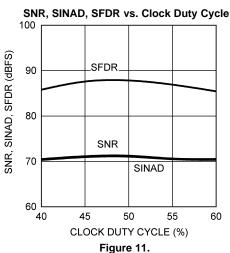

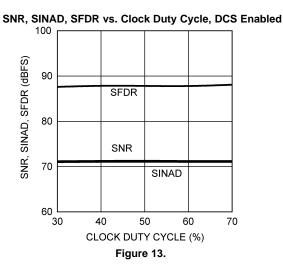

- Clock Duty Cycle Stabilizer

- Single +3.0 or 3.3V Supply Operation

- **Serial LVDS Outputs**

- **Serial Control Interface**

- **Overrange Outputs**

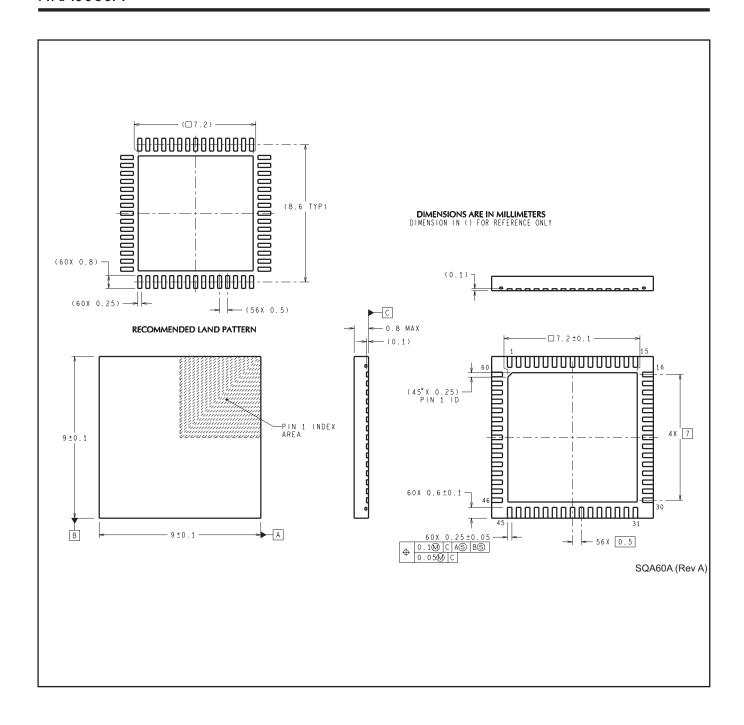

- 60-pin WQFN Package, (9x9x0.8mm, 0.5mm pin-pitch)

# **APPLICATIONS**

- **High IF Sampling Receivers**

- **Wireless Base Station Receivers**

- **Test and Measurement Equipment**

- Communications Instrumentation

- **Portable Instrumentation**

### **KEY SPECIFICATIONS**

Resolution: 12 Bits

**Conversion Rate: 80 MSPS**

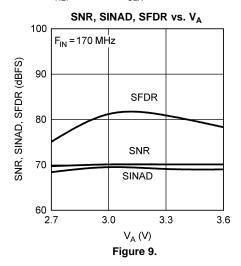

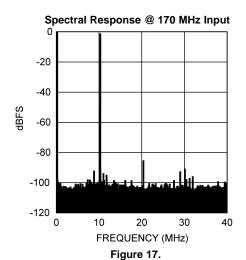

SNR ( $f_{IN} = 170 \text{ MHz}$ ): 70 dBFS (typ) SFDR ( $f_{IN} = 170 \text{ MHz}$ ): 81 dBFS (typ) Full Power Bandwidth: 1 GHz (typ)

Power Consumption: 800 mW (typ)

### DESCRIPTION

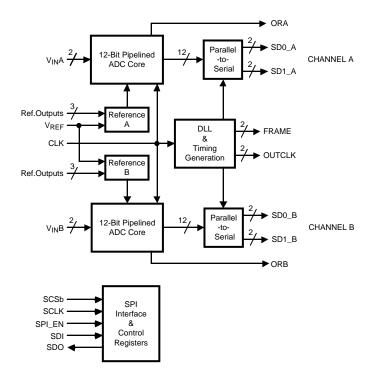

The ADC12DS080 is a high-performance CMOS analog-to-digital converter capable of converting two analog input signals into 12-bit digital words at rates up to 80 Mega Samples Per Second (MSPS). The digital outputs are serialized and provided on differential LVDS signal pairs. This converter uses a differential, pipelined architecture with digital error correction and an on-chip sample-and-hold circuit to minimize power consumption and the external component count, while providing excellent dynamic performance. The ADC12DS080 may be operated from a single +3.0V or 3.3V power supply. A powerdown feature reduces the power consumption to very low levels while still allowing fast wake-up time to full operation. The differential inputs accept a 2V full scale differential input swing. A stable 1.2V internal voltage reference is provided, or the ADC12DS080 can be operated with an external 1.2V reference. The selectable duty cycle stabilizer maintains performance over a wide range of clock duty cycles. A serial interface allows access to the internal registers for full control of the ADC12DS080's functionality. The ADC12DS080 is available in a 60lead WQFN package and operates over the industrial temperature range of -40°C to +85°C

# TEXAS INSTRUMENTS

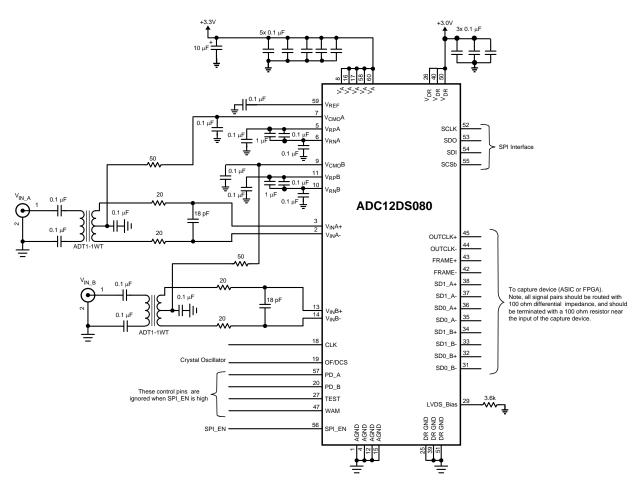

# **Connection Diagram**

Figure 1. WQFN Package See Package Number NKA0060A

# **Block Diagram**

# **Pin Descriptions and Equivalent Circuits**

| Pin Descriptions and Equivalent Circuits |                                          |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|------------------------------------------|------------------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin No.                                  | Symbol                                   | Equivalent Circuit                                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| ANALOG I/O                               |                                          | V                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 3 13                                     | V <sub>IN</sub> A+<br>V <sub>IN</sub> B+ |                                                            | Differential analog input pins. The differential full-scale input signal level is $2V_{P-P}$ with each input pin signal centered on a common mode                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 2<br>14                                  | V <sub>IN</sub> A-<br>V <sub>IN</sub> B- | AGND                                                       | voltage, V <sub>CM</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 5<br>11                                  | V <sub>RP</sub> A<br>V <sub>RP</sub> B   | V <sub>A</sub> V <sub>A</sub>                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 7<br>9                                   | V <sub>CMO</sub> A<br>V <sub>CMO</sub> B | $\Psi \qquad \stackrel{\downarrow}{\bullet} \qquad \qquad$ | These pins should each be bypassed to AGND with a low ESL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 6 10                                     | V <sub>RN</sub> A<br>V <sub>RN</sub> B   | VA VA VA VA AGND                                           | (equivalent series inductance) 0.1 $\mu$ F capacitor placed very close to the pin to minimize stray inductance. An 0201 size 0.1 $\mu$ F capacitor should be placed between V <sub>RP</sub> and V <sub>RN</sub> as close to the pins as possible, and a 1 $\mu$ F capacitor should be placed in parallel. V <sub>RP</sub> and V <sub>RN</sub> should not be loaded. V <sub>CMO</sub> may be loaded to 1mA for use as a temperature stable 1.5V reference. It is recommended to use V <sub>CMO</sub> to provide the common mode voltage, V <sub>CM</sub> , for the differential analog inputs. |  |  |  |  |

| 59                                       | V <sub>REF</sub>                         | VA<br>T                                                    | Reference Voltage. This device provides an internally developed 1.2V reference. When using the internal reference, $V_{REF}$ should be decoupled to AGND with a 0.1 $\mu F$ and a $1\mu F$ , low equivalent series inductance (ESL) capacitor. This pin may be driven with an external 1.2V reference voltage. This pin should not be used to source or sink current.                                                                                                                                                                                                                         |  |  |  |  |

| 29                                       | LVDS_Bias                                | AGND                                                       | LVDS Driver Bias Resistor is applied from this pin to Analog Ground. The nominal value is $3.6 \text{K}\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| DIGITAL I/O                              |                                          |                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 18                                       | CLK                                      | V <sub>A</sub>                                             | The clock input pin. The analog inputs are sampled on the rising edge of the clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 28                                       | Reset_DLL                                | AGND                                                       | Reset_DLL input. This pin is normally low. If the input clock frequency is changed abruptly, the internal timing circuits may become unlocked. Cycle this pin high for 1 microsecond to re-lock the DLL. The DLL will lock in several microseconds after Reset_DLL is asserted.                                                                                                                                                                                                                                                                                                               |  |  |  |  |

TEXAS INSTRUMENTS

SNAS443 – MARCH 2008 www.ti.com

# Pin Descriptions and Equivalent Circuits (continued)

| Pin No.  | Symbol             | Equivalent Circuit | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19       | OF/DCS             | VA<br>AGND         | This is a four-state pin controlling the input clock mode and output data format. $ \text{OF/DCS} = V_A, \text{ output data format is 2's complement without duty cycle stabilization applied to the input clock } \text{OF/DCS} = \text{AGND}, \text{ output data format is offset binary, without duty cycle stabilization applied to the input clock. } \text{OF/DCS} = (2/3)^*V_A, \text{ output data is 2's complement with duty cycle stabilization applied to the input clock } \text{OF/DCS} = (1/3)^*V_A, \text{ output data is offset binary with duty cycle stabilization applied to the input clock. } \text{Note: This signal has no effect when SPI_EN is high and the SPI interface is enabled.} $ |

| 57<br>20 | PD_A<br>PD_B       |                    | This is a two-state input controlling Power Down.<br>$PD = V_A$ , Power Down is enabled and power dissipation is reduced.<br>PD = AGND, Normal operation.<br>Note: This signal has no effect when SPI_EN is high and the SPI interface is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 27       | TEST               | V <sub>A</sub>     | Test Mode. When this signal is asserted high, a fixed test pattern (101001100011 msb->lsb) is sourced at the data outputs.  With this signal deasserted low, the device is in normal operation mode.  Note: This signal has no effect when SPI_EN is high and the SPI interface is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 47       | WAM                | AGND               | Word Alignment Mode. In single-lane mode this pin must be set to logic-0. In dual-lane mode only, when this signal is at logic-0 the serial data words are offset by half-word. With this signal at logic-1 the serial data words are aligned with each other. Note: This signal has no effect when SPI_EN is high and the SPI interface is enabled.                                                                                                                                                                                                                                                                                                                                                              |

| 48       | DLC                |                    | Dual-Lane Configuration. The dual-lane mode is selected when this signal is at logic-0. With this signal at logic-1, all data is sourced on a single lane (SD1_x) for each channel.  Note: This signal has no effect when SPI_EN is high and the SPI interface is enabled.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 45<br>44 | OUTCLK+<br>OUTCLK- | V <sub>DR</sub>    | Serial Clock. This pair of differential LVDS signals provides the serial clock that is synchronous with the Serial Data outputs. A bit of serial data is provided on each of the active serial data outputs with each falling and rising edge of this clock. This differential output is always enabled while the device is powered up. In power-down mode this output is held in logic-low state. A 100-ohm termination resistor must always be used between this pair of signals at the far end of the transmission line.                                                                                                                                                                                       |

| 43<br>42 | FRAME+<br>FRAME-   | DRGND              | Serial Data Frame. This pair of differential LVDS signals transitions at the serial data word boundaries. The SD1_A+/- and SD1_B+/- output words always begin with the rising edge of the Frame signal. The falling edge of the Frame signal defines the start of the serial data word presented on the SD0_A+/- and SD0_B+/- signal pairs in the Dual-Lane mode. This differential output is always enabled while the device is powered up. In power-down mode this output is held in logic-low state. A 100-ohm termination resistor must always be used between this pair of signals at the far end of the transmission line.                                                                                  |

# Pin Descriptions and Equivalent Circuits (continued)

| Pin No.  | Symbol           | Equivalent Circuit             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 38<br>37 | SD1_A+<br>SD1_A- |                                | Serial Data Output 1 for Channel A. This is a differential LVDS pair of signals that carries channel A ADC's output in serialized form. The serial data is provided synchronous with the OUTCLK output. In Single-Lane mode each sample's output is provided in succession. In Dual-Lane mode every other sample output is provided on this output. This differential output is always enabled while the device is powered up. In power-down mode this output holds the last logic state. A 100-ohm termination resistor must always be used between this pair of signals at the far end of the transmission line. |

| 34<br>33 | SD1_B+<br>SD1_B- | V <sub>DR</sub>                | Serial Data Output 1 for Channel B. This is a differential LVDS pair of signals that carries channel B ADC's output in serialized form. The serial data is provided synchronous with the OUTCLK output. In Single-Lane mode each sample's output is provided in succession. In Dual-Lane mode every other sample output is provided on this output. This differential output is always enabled while the device is powered up. In power-down mode this output holds the last logic state. A 100-ohm termination resistor must always be used between this pair of signals at the far end of the transmission line. |

| 36<br>35 | SD0_A+<br>SD0_A- | + - I DRGND                    | Serial Data Output 0 for Channel A. This is a differential LVDS pair of signals that carries channel A ADC's alternating samples' output in serialized form in Dual-Lane mode. The serial data is provided synchronous with the OUTCLK output. In Single-Lane mode this differential output is held in high impedance state. This differential output is always enabled while the device is powered up. In power-down mode this output holds the last logic state. A 100-ohm termination resistor must always be used between this pair of signals at the far end of the transmission line.                        |

| 32<br>31 | SD0_B+<br>SD0_B- |                                | Serial Data Output 0 for Channel B. This is a differential LVDS pair of signals that carries channel B ADC's alternating samples' output in serialized form in Dual-Lane mode. The serial data is provided synchronous with the OUTCLK output. In Single-Lane mode this differential output is held in high impedance state. This differential output is always enabled while the device is powered up. In power-down mode this output holds the last logic state. A 100-ohm termination resistor must always be used between this pair of signals at the far end of the transmission line.                        |

| 56       | SPI_EN           | VA                             | SPI Enable: The SPI interface is enabled when this signal is asserted high. In this case the direct control pins have no effect. When this signal is deasserted, the SPI interface is disabled and the direct control pins are enabled.                                                                                                                                                                                                                                                                                                                                                                            |

| 55       | SCSb             |                                | Serial Chip Select: While this signal is asserted SCLK is used to accept serial data present on the SDI input and to source serial data on the SDO output. When this signal is deasserted, the SDI input is ignored and the SDO output is in tri-state mode.                                                                                                                                                                                                                                                                                                                                                       |

| 52       | SCLK             |                                | Serial Clock: Serial data are shifted into and out of the device synchronous with this clock signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 54       | SDI              |                                | Serial Data-In: Serial data are shifted into the device on this pin while SCSb signal is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 53       | SDO              | V <sub>DR</sub> V <sub>A</sub> | Serial Data-Out: Serial data are shifted out of the device on this pin while SCSb signal is asserted. This output is in tri-state mode when SCSb is deasserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 46<br>30 | ORA<br>ORB       |                                | Overrange. These CMOS outputs are asserted logic-high when their respective channel's data output is out-of-range in either high or low direction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 24       | DLL_Lock         | DRGND DGND                     | DLL_Lock Output. When the internal DLL is locked to the input CLK, this pin outputs a logic high. If the input CLK is changed abruptly, the internal DLL may become unlocked and this pin will output a logic low. Cycle Reset_DLL (pin 28) to re-lock the DLL to the input CLK.                                                                                                                                                                                                                                                                                                                                   |

Product Folder Links: ADC12DS080

### Pin Descriptions and Equivalent Circuits (continued)

| Pin No.                      | Symbol                                                                                                                                                                                 | Equivalent Circuit | Description                                                                                                                                                                         |  |  |  |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 8, 16, 17, 58,<br>60         | $V_{A}$                                                                                                                                                                                |                    | Positive analog supply pins. These pins should be connected to a quiet source and be bypassed to AGND with 0.1 µF capacitors located close to the power pins.                       |  |  |  |

| 1, 4, 12, 15,<br>Exposed Pad | AGND                                                                                                                                                                                   |                    | The ground return for the analog supply.                                                                                                                                            |  |  |  |

| DIGITAL POW                  | ER                                                                                                                                                                                     |                    |                                                                                                                                                                                     |  |  |  |

| 26, 40, 50                   | Positive driver supply pin for the output drivers. This pin should connected to a quiet voltage source and be bypassed to DRGN with a 0.1 µF capacitor located close to the power pin. |                    |                                                                                                                                                                                     |  |  |  |

| 25, 39, 51                   | DRGND                                                                                                                                                                                  |                    | The ground return for the digital output driver supply. This pins should be connected to the system digital ground, but not be connected in close proximity to the ADC's AGND pins. |  |  |  |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# Absolute Maximum Ratings (1)(2)(3)

| Abbolate maximum rat                               | About the American Teaming                           |                                                         |  |  |  |  |  |

|----------------------------------------------------|------------------------------------------------------|---------------------------------------------------------|--|--|--|--|--|

| Supply Voltage (V <sub>A</sub> , V <sub>DR</sub> ) |                                                      | -0.3V to 4.2V                                           |  |  |  |  |  |

| Voltage on Any Pin (Not to excee                   | d 4.2V)                                              | -0.3V to (V <sub>A</sub> +0.3V)                         |  |  |  |  |  |

| Input Current at Any Pin other tha                 | n Supply Pins <sup>(4)</sup>                         | ±5 mA                                                   |  |  |  |  |  |

| Package Input Current <sup>(4)</sup>               | ckage Input Current <sup>(4)</sup>                   |                                                         |  |  |  |  |  |

| Max Junction Temp (T <sub>J</sub> )                | +150°C                                               |                                                         |  |  |  |  |  |

| Thermal Resistance (θ <sub>JA</sub> )              |                                                      | 30°C/W                                                  |  |  |  |  |  |

| ESD Rating                                         | Human Body Model (5)                                 | 2500V                                                   |  |  |  |  |  |

|                                                    | Machine Model <sup>(5)</sup>                         |                                                         |  |  |  |  |  |

| Storage Temperature                                | −65°C to +150°C                                      |                                                         |  |  |  |  |  |

| Soldering process must comply w                    | rith National Semiconductor's Reflow Temperature Pro | file specifications. Refer to www.ti.com/packaging. (6) |  |  |  |  |  |

|                                                    |                                                      |                                                         |  |  |  |  |  |

- (1) All voltages are measured with respect to GND = AGND = DRGND = 0V, unless otherwise specified.

- (2) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is guaranteed to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the maximum Operating Ratings is not recommended.

- (3) If Military/Aerospace specified devices are required, please contact the Texas Instruments Sales Office/ Distributors for availability and specifications.

- (4) When the input voltage at any pin exceeds the power supplies (that is, V<sub>IN</sub> < AGND, or V<sub>IN</sub> > V<sub>A</sub>), the current at that pin should be limited to ±5 mA. The ±50 mA maximum package input current rating limits the number of pins that can safely exceed the power supplies with an input current of ±5 mA to 10.

- (5) Human Body Model is 100 pF discharged through a 1.5 kΩ resistor. Machine Model is 220 pF discharged through 0 Ω

- (6) Reflow temperature profiles are different for lead-free and non-lead-free packages.

# Operating Ratings (1)(2)

|                                                  | -40°C ≤ T <sub>A</sub> ≤ +85°C |

|--------------------------------------------------|--------------------------------|

| upply Voltage (V <sub>A</sub> =V <sub>DR</sub> ) |                                |

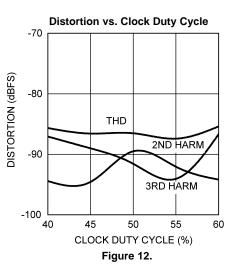

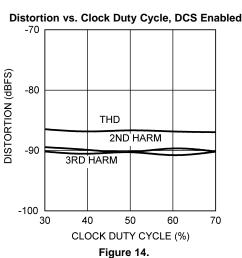

| (DCS Enabled)                                    | 30/70 %                        |

| (DCS disabled)                                   | 45/55 %                        |

|                                                  | 1.4V to 1.6V                   |

|                                                  | ≤100mV                         |

|                                                  | ,                              |

- (1) Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is guaranteed to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions. Operation of the device beyond the maximum Operating Ratings is not recommended.

- (2) All voltages are measured with respect to GND = AGND = DRGND = 0V, unless otherwise specified.

# **Converter Electrical Characteristics**

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A = V_{DR} = +3.0V$ , Internal  $V_{REF} = +1.2V$ ,  $f_{CLK} = 80$  MHz,  $V_{CM} = V_{CMO}$ ,  $C_L = 5$  pF/pin. Typical values are for  $T_A = 25$ °C. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A = 25$ °C  $T_{MAX} = 75$ °C  $T_$

|                         | Parameter                                      | Test Cond                                    | ditions    | Typical <sup>(3)</sup> | Limits         | Units<br>(Limits)  |

|-------------------------|------------------------------------------------|----------------------------------------------|------------|------------------------|----------------|--------------------|

| STATIC (                | CONVERTER CHARACTERISTICS                      |                                              |            | •                      |                |                    |

|                         | Resolution with No Missing Codes               |                                              |            |                        | 12             | Bits (min)         |

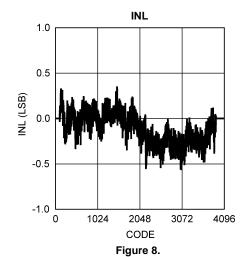

| INII                    | Internal Name Linearity                        |                                              |            | .0.5                   | 1.5            | LSB (max)          |

| INL                     | Integral Non Linearity                         |                                              |            | ±0.5                   | -1.5           | LSB (min)          |

| DNL                     | Differential New Linearity                     |                                              |            | 0.05                   | 0.5            | LSB (max)          |

| DNL                     | Differential Non Linearity                     |                                              |            | ±0.25                  | -0.5           | LSB (min)          |

| PGE                     | Positive Gain Error                            |                                              |            | 0.1                    | ±1             | %FS (max)          |

| NGE                     | Negative Gain Error                            |                                              |            | 0.1                    | ±1             | %FS (max)          |

| V <sub>OFF</sub>        | Offset Error                                   |                                              |            | 0.2                    | <b>±0.6</b> 5  | %FS (max)          |

|                         | Under Range Output Code                        |                                              |            | 0                      | 0              |                    |

|                         | Over Range Output Code                         |                                              |            | 4095                   | 4095           |                    |

| REFERE                  | NCE AND ANALOG INPUT CHARACTER                 | RISTICS                                      |            | •                      | 1              |                    |

| V <sub>CMO</sub>        | Common Mode Output Voltage                     |                                              |            | 1.5                    | 1.4<br>1.6     | V (min)<br>V (max) |

| V <sub>CM</sub>         | Analog Input Common Mode Voltage               |                                              |            | 1.5                    | 1.4<br>1.6     | V (min)<br>V (max) |

| _                       | V <sub>IN</sub> Input Capacitance (each pin to | V 45.VI 05.V                                 | (CLK LOW)  | 8.5                    |                | pF                 |

| C <sub>IN</sub>         | GND) <sup>(4)</sup>                            | $V_{IN} = 1.5 \text{ Vdc} \pm 0.5 \text{ V}$ | (CLK HIGH) | 3.5                    |                | pF                 |

| $V_{REF}$               | Internal Reference Voltage                     |                                              |            | 1.18                   | 1.15<br>1.21   | V (min)<br>V (max) |

| TC V <sub>REF</sub>     | Internal Reference Voltage Tempco              | -40°C ≤ T <sub>A</sub> ≤ +85°C               |            | 18                     |                | ppm/°C             |

| V <sub>RP</sub>         | Internal Reference Top                         |                                              |            | 2.0                    |                | V                  |

| V <sub>RN</sub>         | Internal Reference Bottom                      |                                              |            | 1.0                    |                | V                  |

|                         | Internal Reference Accuracy                    | (V <sub>RP</sub> -V <sub>RN</sub> )          |            | 0.97                   | 0.89<br>1.06   | V (min)<br>V (max) |

| EXT<br>V <sub>REF</sub> | External Reference Voltage                     |                                              |            | 1.2                    | 1.176<br>1.224 | V (min)<br>V (max) |

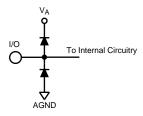

<sup>(1)</sup> The inputs are protected as shown below. Input voltage magnitudes above V<sub>A</sub> or below GND will not damage this device, provided current is limited per Note 4. However, errors in the A/D conversion can occur if the input goes above 2.6V or below GND as described in the Operating Ratings section. See Figure 2.

- (2) With a full scale differential input of  $2V_{P-P}$ , the 12-bit LSB is 488  $\mu$ V.

- (3) Typical figures are at T<sub>A</sub> = 25°C and represent most likely parametric norms at the time of product characterization. The typical specifications are not quaranteed.

- (4) The input capacitance is the sum of the package/pin capacitance and the sample and hold circuit capacitance.

Figure 2.

Product Folder Links: ADC12DS080

# **Dynamic Converter Electrical Characteristics**

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A = V_{DR} = +3.0V$ , Internal  $V_{REF} = +1.2V$ ,  $f_{CLK} = 80$  MHz,  $V_{CM} = V_{CMO}$ ,  $C_L = 5$  pF/pin, . Typical values are for  $T_A = 25^{\circ}C$ . **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A = 25^{\circ}C$

|        | Parameter                                    | Test Conditions                                   | Typical <sup>(3)</sup> | Limits | Units<br>(Limits) <sup>(4)</sup> |

|--------|----------------------------------------------|---------------------------------------------------|------------------------|--------|----------------------------------|

| DYNAMI | C CONVERTER CHARACTERISTICS, A <sub>II</sub> | = -1dBFS                                          | ,                      | 1      |                                  |

| FPBW   | Full Power Bandwidth                         | -1 dBFS Input, -3 dB Corner                       | 1.0                    |        | GHz                              |

|        |                                              | f <sub>IN</sub> = 10 MHz                          | 71                     |        | dBFS                             |

| SNR    | Signal-to-Noise Ratio                        | f <sub>IN</sub> = 70 MHz                          | 70.5                   |        | dBFS                             |

|        |                                              | f <sub>IN</sub> = 170 MHz                         | 70                     | 68.5   | dBFS                             |

|        |                                              | f <sub>IN</sub> = 10 MHz                          | 88                     |        | dBFS                             |

| SFDR   | Spurious Free Dynamic Range                  | f <sub>IN</sub> = 70 MHz                          | 85                     |        | dBFS                             |

|        |                                              | f <sub>IN</sub> = 170 MHz                         | 81                     | 76.5   | dBFS                             |

|        |                                              | f <sub>IN</sub> = 10 MHz                          | 11.5                   |        | Bits                             |

| ENOB   | Effective Number of Bits                     | f <sub>IN</sub> = 70 MHz                          | 11.4                   |        | Bits                             |

|        |                                              | f <sub>IN</sub> = 170 MHz                         | 11.3                   | 10.9   | Bits                             |

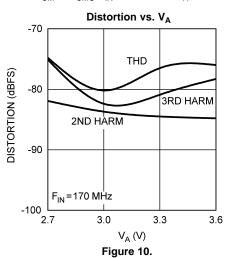

|        | Total Harmonic Disortion                     | f <sub>IN</sub> = 10 MHz                          | -86                    |        | dBFS                             |

| THD    |                                              | f <sub>IN</sub> = 70 MHz                          | -85                    |        | dBFS                             |

|        |                                              | f <sub>IN</sub> = 170 MHz                         | -80                    | -75    | dBFS                             |

|        |                                              | f <sub>IN</sub> = 10 MHz                          | -90                    |        | dBFS                             |

| H2     | Second Harmonic Distortion                   | f <sub>IN</sub> = 70 MHz                          | -88                    |        | dBFS                             |

|        |                                              | f <sub>IN</sub> = 170 MHz                         | -83                    | -76.5  | dBFS                             |

|        |                                              | f <sub>IN</sub> = 10 MHz                          | -88                    |        | dBFS                             |

| H3     | Third Harmonic Distortion                    | f <sub>IN</sub> = 70 MHz                          | -85                    |        | dBFS                             |

|        |                                              | f <sub>IN</sub> = 170 MHz                         | -81                    | -76.5  | dBFS                             |

|        |                                              | f <sub>IN</sub> = 10 MHz                          | 70.8                   |        | dBFS                             |

| SINAD  | Signal-to-Noise and Distortion Ratio         | f <sub>IN</sub> = 70 MHz                          | 70.3                   |        | dBFS                             |

|        |                                              | f <sub>IN</sub> = 170 MHz                         | 69.6                   | 67.6   | dBFS                             |

| IMD    | Intermodulation Distortion                   | f <sub>IN</sub> =19.5 and 20.5MHz,<br>each -7dBFS | -84                    |        | dBFS                             |

<sup>(1)</sup> The inputs are protected as shown below. Input voltage magnitudes above V<sub>A</sub> or below GND will not damage this device, provided current is limited per Note 4. However, errors in the A/D conversion can occur if the input goes above 2.6V or below GND as described in the Operating Ratings section. See Figure 2.

<sup>(2)</sup> With a full scale differential input of  $2V_{P-P}$ , the 12-bit LSB is 488  $\mu$ V.

<sup>(3)</sup> Typical figures are at T<sub>A</sub> = 25°C and represent most likely parametric norms at the time of product characterization. The typical specifications are not guaranteed.

<sup>(4)</sup> This parameter is specified in units of dBFS - indicating the value that would be attained with a full-scale input signal.

# **Logic and Power Supply Electrical Characteristics**

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A = V_{DR} = +3.0V$ , Internal  $V_{REF} = +1.2V$ ,  $f_{CLK} = 80$  MHz,  $V_{CM} = V_{CMO}$ ,  $C_L = 5$  pF/pin. Typical values are for  $T_A = 25$ °C. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A = 25$ °C  $T_{MIN} \le T_A \le T_{MAX}$ .

|                     | Parameter                           | Test Conditions                    | Typical <sup>(3)</sup> | Limits | Units<br>(Limits) |

|---------------------|-------------------------------------|------------------------------------|------------------------|--------|-------------------|

| DIGITAL             | INPUT CHARACTERISTICS (CLK, PD_A    | A,PD_B,SCSb,SPI_EN,SCLK,SDI,TEST,V | VAM,DLC)               |        | 1                 |

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage           | V <sub>D</sub> = 3.6V              |                        | 2.0    | V (min)           |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage           | V <sub>D</sub> = 3.0V              |                        | 0.8    | V (max)           |

| I <sub>IN(1)</sub>  | Logical "1" Input Current           | V <sub>IN</sub> = 3.3V             | 10                     |        | μA                |

| I <sub>IN(0)</sub>  | Logical "0" Input Current           | V <sub>IN</sub> = 0V               | -10                    |        | μA                |

| C <sub>IN</sub>     | Digital Input Capacitance           |                                    | 5                      |        | pF                |

| DIGITAL             | OUTPUT CHARACTERISTICS (ORA,OF      | RB,SDO,DLL_Lock)                   |                        |        |                   |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage          | I <sub>OUT</sub> = −0.5 mA         |                        | 1.2    | V (min)           |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage          | I <sub>OUT</sub> = 1.6 mA          |                        | 0.4    | V (max)           |

| +I <sub>SC</sub>    | Output Short Circuit Source Current | V <sub>OUT</sub> = 0V              | -10                    |        | mA                |

| -I <sub>SC</sub>    | Output Short Circuit Sink Current   | $V_{OUT} = V_{DR}$                 | 10                     |        | mA                |

| C <sub>OUT</sub>    | Digital Output Capacitance          |                                    | 5                      |        | pF                |

| POWER               | SUPPLY CHARACTERISTICS              | •                                  | •                      |        |                   |

| I <sub>A</sub>      | Analog Supply Current               | Full Operation                     | 204                    | 230    | mA (max)          |

| I <sub>DR</sub>     | Digital Output Supply Current       | Full Operation                     | 62                     | 70     | mA                |

|                     | Power Consumption                   |                                    | 800                    | 900    | mW (max)          |

|                     | Power Down Power Consumption        | Clock disabled                     | 30                     |        | mW                |

<sup>(1)</sup> The inputs are protected as shown below. Input voltage magnitudes above V<sub>A</sub> or below GND will not damage this device, provided current is limited per Note 4. However, errors in the A/D conversion can occur if the input goes above 2.6V or below GND as described in the Operating Ratings section. See Figure 2.

(2) With a full scale differential input of  $2V_{P-P}$ , the 12-bit LSB is 488  $\mu$ V.

# **Timing and AC Characteristics**

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A = V_{DR} = +3.0V$ , Internal  $V_{REF} = +1.2V$ ,  $f_{CLK} = 80$  MHz,  $V_{CM} = V_{CMO}$ ,  $C_L = 5$  pF/pin. Typical values are for  $T_A = 25$ °C. Timing measurements are taken at 50% of the signal amplitude. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A = 25$ °C<sup>(1)(2)</sup>

|                   | Parameter               | Test Conditions                                                            | Typical <sup>(3)</sup> | Limits        | Units<br>(Limits) |

|-------------------|-------------------------|----------------------------------------------------------------------------|------------------------|---------------|-------------------|

|                   | Maximum Clock Frequency | In Single-Lane Mode<br>In Dual-Lane Mode                                   |                        | 65<br>80      | MHz (max)         |

|                   | Minimum Clock Frequency | In Single-Lane Mode<br>In Dual-Lane Mode                                   |                        | 25<br>52.5    | MHz (min)         |

| t <sub>CONV</sub> | Conversion Latency      | Single-Lane Mode<br>Dual-Lane, Offset Mode<br>Dual-Lane, Word Aligned Mode |                        | 7.5<br>8<br>9 | Clock Cycles      |

| t <sub>AD</sub>   | Aperture Delay          |                                                                            | 0.6                    |               | ns                |

| $t_{AJ}$          | Aperture Jitter         |                                                                            | 0.1                    |               | ps rms            |

<sup>(1)</sup> The inputs are protected as shown below. Input voltage magnitudes above V<sub>A</sub> or below GND will not damage this device, provided current is limited per Note 4. However, errors in the A/D conversion can occur if the input goes above 2.6V or below GND as described in the Operating Ratings section. See Figure 2.

(2) With a full scale differential input of  $2V_{P-P}$ , the 12-bit LSB is 488  $\mu$ V.

Product Folder Links: ADC12DS080

<sup>(3)</sup> Typical figures are at T<sub>A</sub> = 25°C and represent most likely parametric norms at the time of product characterization. The typical specifications are not guaranteed.

<sup>(3)</sup> Typical figures are at T<sub>A</sub> = 25°C and represent most likely parametric norms at the time of product characterization. The typical specifications are not guaranteed.

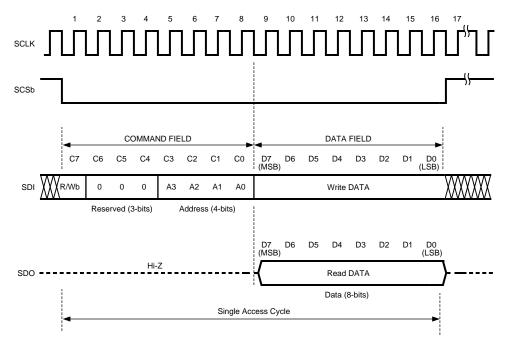

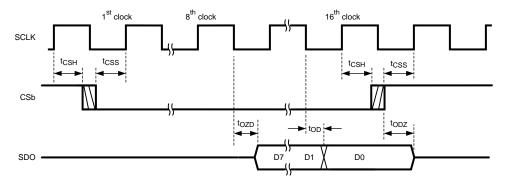

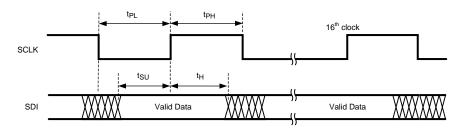

# Serial Control Interface Timing and AC Characteristics

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A = V_{DR} = +3.0V$ , Internal  $V_{REF} = +1.2V$ ,  $f_{CLK} = 80$  MHz,  $V_{CM} = V_{CMO}$ ,  $C_L = 5$  pF/pin. Typical values are for  $T_A = 25^{\circ}C$ . Timing measurements are taken at 50% of the signal amplitude. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A = 25^{\circ}C^{(1)(2)}$

| Parameter         |                              | Test Conditions                                       | Typical <sup>(3)</sup> | Limits   | Units<br>(Limits)  |

|-------------------|------------------------------|-------------------------------------------------------|------------------------|----------|--------------------|

| f <sub>SCLK</sub> | Serial Clock Frequency       | $f_{SCLK} = f_{CLK}/10$                               |                        | 8        | MHz (max)          |

| t <sub>PH</sub>   | SCLK Pulse Width - High      | % of SCLK Period                                      |                        | 40<br>60 | % (min)<br>% (max) |

| t <sub>PL</sub>   | SCLK Pulse Width - Low       | % of SCLK Period                                      |                        | 40<br>60 | % (min)<br>% (max) |

| t <sub>SU</sub>   | SDI Setup Time               |                                                       |                        | 5        | ns (min)           |

| t <sub>H</sub>    | SDI Hold Time                |                                                       |                        | 5        | ns (min)           |

| t <sub>ODZ</sub>  | SDO Driven-to-Tri-State Time |                                                       | 40                     | 50       | ns (max)           |

| t <sub>OZD</sub>  | SDO Tri-State-to-Driven Time |                                                       | 15                     | 20       | ns (max)           |

| t <sub>OD</sub>   | SDO Output Delay Time        |                                                       | 15                     | 20       | ns (max)           |

| t <sub>CSS</sub>  | SCSb Setup Time              |                                                       | 5                      | 10       | ns (min)           |

| t <sub>CSH</sub>  | SCSb Hold Time               |                                                       | 5                      | 10       | ns (min)           |

| t <sub>IAG</sub>  | Inter-Access Gap             | Minimum time SCSb must be deasserted between accesses | 3                      |          | Cycles of SCLK     |

<sup>(1)</sup> The inputs are protected as shown below. Input voltage magnitudes above V<sub>A</sub> or below GND will not damage this device, provided current is limited per Note 4. However, errors in the A/D conversion can occur if the input goes above 2.6V or below GND as described in the Operating Ratings section. See Figure 2.

(2) With a full scale differential input of  $2V_{P-P}$ , the 12-bit LSB is 488  $\mu V$ .

# **LVDS Electrical Characteristics**

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A = V_{DR} = +3.0V$ , Internal  $V_{REF} = +1.2V$ ,  $f_{CLK} = 80$  MHz,  $V_{CM} = V_{CMO}$ ,  $C_L = 5$  pF/pin. Typical values are for  $T_A = 25$ °C. Timing measurements are taken at 50% of the signal amplitude. **Boldface limits apply for T\_{MIN} \le T\_A \le T\_{MAX}.** All other limits apply for  $T_A = 25$ °C<sup>(1)(2)</sup>

|                          | Parameter                                                        | Test Conditions                  | Typical <sup>(3)</sup> | Limits         | Units<br>(Limits)    |

|--------------------------|------------------------------------------------------------------|----------------------------------|------------------------|----------------|----------------------|

| LVDS DC                  | CHARACTERISTICS                                                  |                                  |                        |                |                      |

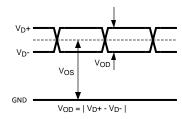

| V <sub>OD</sub>          | Output Differential Voltage (SDO+) - (SDO-)                      | $R_L = 100\Omega$                | 350                    | 250<br>450     | mV (min)<br>mV (max) |

| delta<br>V <sub>OD</sub> | Output Differential Voltage Unbalance                            | $R_L = 100\Omega$                |                        | ±25            | mV (max)             |

| Vos                      | Offset Voltage                                                   | $R_L = 100\Omega$                | 1.25                   | 1.125<br>1.375 | V (min)<br>V (max)   |

| delta V <sub>OS</sub>    | Offset Voltage Unbalance                                         | $R_L = 100\Omega$                |                        | ±25            | mV (max)             |

| IOS                      | Output Short Circuit Current                                     | DO = 0V, V <sub>IN</sub> = 1.1V, | -10                    |                | mA (max)             |

| LVDS OU                  | TPUT TIMING AND SWITCHING CHARAC                                 | TERISTICS                        |                        |                |                      |

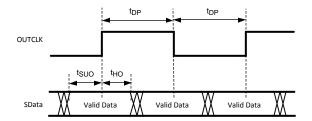

| t <sub>DP</sub>          | Output Data Bit Period                                           | Dual-Lane Mode                   | 2.08                   |                | ns                   |

| t <sub>HO</sub>          | Output Data Edge to Output Clock Edge Hold Time (4)              | Dual-Lane Mode                   | 990                    | 550            | ps (min)             |

| t <sub>SUO</sub>         | Output Data Edge to Output Clock Edge Set-Up Time <sup>(4)</sup> | Dual-Lane Mode                   | 1100                   | 600            | ps (min)             |

| t <sub>FP</sub>          | Frame Period                                                     | Dual-Lane Mode                   | 25                     |                | ns                   |

<sup>(1)</sup> The inputs are protected as shown below. Input voltage magnitudes above V<sub>A</sub> or below GND will not damage this device, provided current is limited per Note 4. However, errors in the A/D conversion can occur if the input goes above 2.6V or below GND as described in the Operating Ratings section. See Figure 2.

10

<sup>(3)</sup> Typical figures are at T<sub>A</sub> = 25°C and represent most likely parametric norms at the time of product characterization. The typical specifications are not guaranteed.

<sup>(2)</sup> With a full scale differential input of  $2V_{P-P}$ , the 12-bit LSB is 488  $\mu V$ .

<sup>(3)</sup> Typical figures are at T<sub>A</sub> = 25°C and represent most likely parametric norms at the time of product characterization. The typical specifications are not guaranteed.

<sup>(4)</sup> This parameter is guaranteed by design and/or characterization and is not tested in production.

# LVDS Electrical Characteristics (continued)

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A = V_{DR} = +3.0V$ , Internal  $V_{REF} = +1.2V$ ,  $f_{CLK} = 80$  MHz,  $V_{CM} = V_{CMO}$ ,  $C_L = 5$  pF/pin. Typical values are for  $T_A = 25$ °C. Timing measurements are taken at 50% of the signal amplitude. **Boldface limits apply for T**<sub>MIN</sub>  $\leq$  **T**<sub>A</sub>  $\leq$  **T**<sub>MAX</sub>. All other limits apply for  $T_A = 25$ °C<sup>(1)(2)</sup>

| Parameter         |                                       | Parameter Test Conditions                |    | Limits   | Units<br>(Limits)  |

|-------------------|---------------------------------------|------------------------------------------|----|----------|--------------------|

| t <sub>FDC</sub>  | Frame Clock Duty Cycle <sup>(5)</sup> |                                          | 50 | 45<br>55 | % (min)<br>% (max) |

| t <sub>DFS</sub>  | Data Edge to Frame Edge Skew          | 50% to 50%                               | 15 |          | ps                 |

| t <sub>ODOR</sub> | Output Delay of OR output             | From rising edge of CLK to ORA/ORB valid | 4  |          | ns                 |

<sup>(5)</sup> This parameter is guaranteed by design and/or characterization and is not tested in production.

# **Specification Definitions**

**APERTURE DELAY** is the time after the falling edge of the clock to when the input signal is acquired or held for conversion.

**APERTURE JITTER (APERTURE UNCERTAINTY)** is the variation in aperture delay from sample to sample. Aperture jitter manifests itself as noise in the output.

**CLOCK DUTY CYCLE** is the ratio of the time during one cycle that a repetitive digital waveform is high to the total time of one period. The specification here refers to the ADC clock input signal.

**COMMON MODE VOLTAGE (V<sub>CM</sub>)** is the common DC voltage applied to both input terminals of the ADC.

**CONVERSION LATENCY** is the number of clock cycles between initiation of conversion and when that data is presented to the output driver stage. Data for any given sample is available at the output pins the Pipeline Delay plus the Output Delay after the sample is taken. New data is available at every clock cycle, but the data lags the conversion by the pipeline delay.

**CROSSTALK** is coupling of energy from one channel into the other channel.

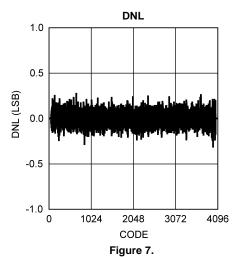

**DIFFERENTIAL NON-LINEARITY (DNL)** is the measure of the maximum deviation from the ideal step size of 1 LSB.

**EFFECTIVE NUMBER OF BITS (ENOB, or EFFECTIVE BITS)** is another method of specifying Signal-to-Noise and Distortion Ratio or SINAD. ENOB is defined as (SINAD - 1.76) / 6.02 and says that the converter is equivalent to a perfect ADC of this (ENOB) number of bits.

**FULL POWER BANDWIDTH** is a measure of the frequency at which the reconstructed output fundamental drops 3 dB below its low frequency value for a full scale input.

GAIN ERROR is the deviation from the ideal slope of the transfer function. It can be calculated as:

It can also be expressed as Positive Gain Error and Negative Gain Error, which are calculated as:

**INTEGRAL NON LINEARITY (INL)** is a measure of the deviation of each individual code from a best fit straight line. The deviation of any given code from this straight line is measured from the center of that code value.

**INTERMODULATION DISTORTION (IMD)** is the creation of additional spectral components as a result of two sinusoidal frequencies being applied to the ADC input at the same time. It is defined as the ratio of the power in the intermodulation products to the total power in the original frequencies. IMD is usually expressed in dBFS.

**LSB (LEAST SIGNIFICANT BIT)** is the bit that has the smallest value or weight of all bits. This value is  $V_{FS}/2^n$ , where " $V_{FS}$ " is the full scale input voltage and "n" is the ADC resolution in bits.

Product Folder Links: ADC12DS080

**LVDS Differential Output Voltage (V\_{OD})** is the absolute value of the difference between the differential output pair voltages ( $V_D$ + and  $V_D$ -), each measured with respect to ground.

**MISSING CODES** are those output codes that will never appear at the ADC outputs. The ADC is guaranteed not to have any missing codes.

MSB (MOST SIGNIFICANT BIT) is the bit that has the largest value or weight. Its value is one half of full scale.

**NEGATIVE FULL SCALE ERROR** is the difference between the actual first code transition and its ideal value of ½ LSB above negative full scale.

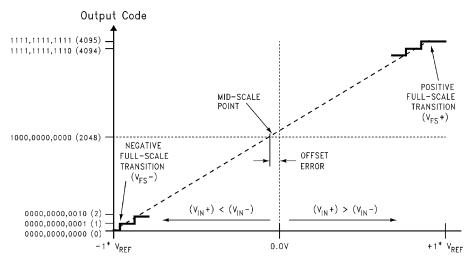

**OFFSET ERROR** is the difference between the two input voltages  $[(V_{IN}+) - (V_{IN}-)]$  required to cause a transition from code 2047 to 2048.

**OUTPUT DELAY** is the time delay after the falling edge of the clock before the data update is presented at the output pins.

PIPELINE DELAY (LATENCY) See CONVERSION LATENCY.

**POSITIVE FULL SCALE ERROR** is the difference between the actual last code transition and its ideal value of 1½ LSB below positive full scale.

**POWER SUPPLY REJECTION RATIO (PSRR)** is a measure of how well the ADC rejects a change in the power supply voltage. PSRR is the ratio of the Full-Scale output of the ADC with the supply at the minimum DC supply limit to the Full-Scale output of the ADC with the supply at the maximum DC supply limit, expressed in dB.

**SIGNAL TO NOISE RATIO (SNR)** is the ratio, expressed in dB, of the rms value of the input signal to the rms value of the sum of all other spectral components below one-half the sampling frequency, not including harmonics or DC.

**SIGNAL TO NOISE PLUS DISTORTION (S/N+D or SINAD)** Is the ratio, expressed in dB, of the rms value of the input signal to the rms value of all of the other spectral components below half the clock frequency, including harmonics but excluding d.c.

**SPURIOUS FREE DYNAMIC RANGE (SFDR)** is the difference, expressed in dB, between the rms values of the input signal and the peak spurious signal, where a spurious signal is any signal present in the output spectrum that is not present at the input.

**TOTAL HARMONIC DISTORTION (THD)** is the ratio, expressed in dB, of the rms total of the first six harmonic levels at the output to the level of the fundamental at the output. THD is calculated as

THD = 20 x log

$$\sqrt{\frac{f_2^2 + \dots + f_7^2}{f_1^2}}$$

(3)

where  $f_1$  is the RMS power of the fundamental (output) frequency and  $f_2$  through  $f_7$  are the RMS power of the first six harmonic frequencies in the output spectrum.

**SECOND HARMONIC DISTORTION (2ND HARM)** is the difference expressed in dB, between the RMS power in the input frequency at the output and the power in its 2nd harmonic level at the output.

**THIRD HARMONIC DISTORTION (3RD HARM)** is the difference, expressed in dB, between the RMS power in the input frequency at the output and the power in its 3rd harmonic level at the output.

# **Timing Diagrams**

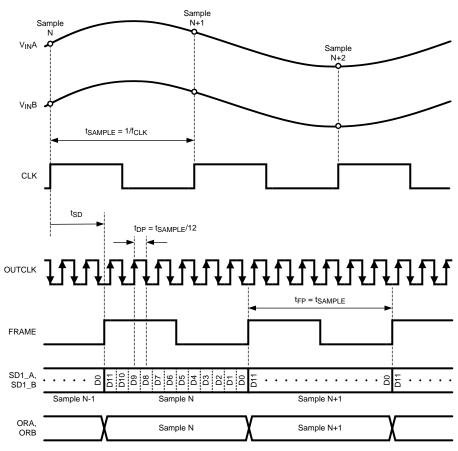

Figure 3. Serial Output Data Timing

Figure 4. Serial Output Data Format in Single-Lane Mode

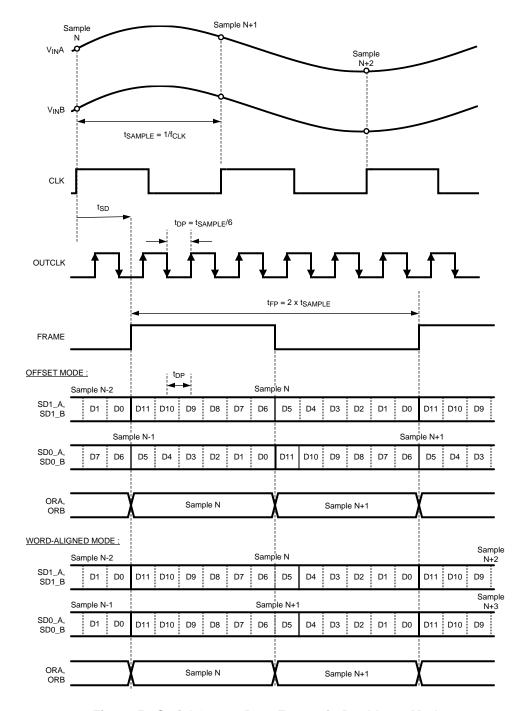

Figure 5. Serial Output Data Format in Dual-Lane Mode

### **Transfer Characteristic**

Analog Input Voltage  $(V_{IN} +) - (V_{IN} -)$

Figure 6. Transfer Characteristic

# Typical Performance Characteristics DNL, INL

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A = V_{DR} = +3.0V$ , Internal  $V_{REF} = +1.2V$ ,  $f_{CLK} = 80$  MHz, 50% Duty Cycle, DCS disabled,  $V_{CM} = V_{CMO}$ ,  $T_A = 25^{\circ}C$ .

# **Typical Performance Characteristics**

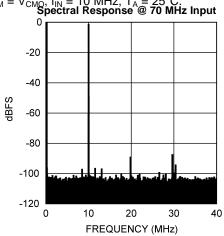

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A = V_{DR} = +3.0V$ , Internal  $V_{REF} = +1.2V$ ,  $f_{CLK} = 80$  MHz, 50% Duty Cycle, DCS disabled,  $V_{CM} = V_{CMO}$ ,  $f_{IN} = 10$  MHz,  $T_A = 25^{\circ}C$ .

STRUMENTS

# **Typical Performance Characteristics (continued)**

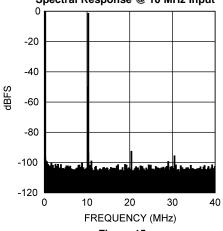

Unless otherwise specified, the following specifications apply: AGND = DRGND = 0V,  $V_A = V_{DR} = +3.0V$ ,

$\begin{array}{l} \text{Internal V}_{\text{REF}} = +1.2 \text{V}, \, f_{\text{CLK}} = 80 \,\,\text{MHz}, \, 50\% \,\, \text{Duty Cycle}, \, \text{DCS disabled}, \, \text{V}_{\text{CM}} = \text{V}_{\text{CMO}}, \, f_{\text{IN}} = 10 \,\,\text{MHz}, \, \text{T}_{\text{A}} = 25 \,^{\circ}\text{C}. \\ \text{Spectral Response @ 10 MHz Input} \\ \end{array}$

Figure 15.

Figure 16.

Figure 18.

TEXAS INSTRUMENTS

SNAS443 – MARCH 2008 www.ti.com

#### **FUNCTIONAL DESCRIPTION**

Operating on a single +3.3V supply, the ADC12DS080 digitizes two differential analog input signals to 12 bits, using a differential pipelined architecture with error correction circuitry and an on-chip sample-and-hold circuit to ensure maximum performance. The user has the choice of using an internal 1.2V stable reference, or using an external 1.2V reference. Any external reference is buffered on-chip to ease the task of driving that pin. Duty cycle stabilization and output data format are selectable using the quad state function OF/DCS pin (pin 19). The output data can be set for offset binary or two's complement.

### **Applications Information**

#### **OPERATING CONDITIONS**

We recommend that the following conditions be observed for operation of the ADC12DS080:

$$2.7V \le V_A \le 3.6V$$

$2.7V \le V_{DR} \le V_A$

$25 \text{ MHz} \le f_{CLK} \le 105 \text{ MHz}$

$1.2V \text{ internal reference}$

$V_{REF} = 1.2V \text{ (for an external reference)}$

$V_{CM} = 1.5V \text{ (from } V_{CMO)}$

#### **ANALOG INPUTS**

#### Signal Inputs

### **Differential Analog Input Pins**

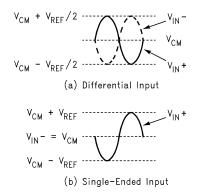

The ADC12DS080 has a pair of analog signal input pins for each of two channels.  $V_{IN}$ + and  $V_{IN}$ - form a differential input pair. The input signal,  $V_{IN}$ , is defined as

$$V_{IN} = (V_{IN} +) - (V_{IN} -) \tag{4}$$

Figure 19 shows the expected input signal range. Note that the common mode input voltage,  $V_{CM}$ , should be 1.5V. Using  $V_{CMO}$  (pins 7,9) for  $V_{CM}$  will ensure the proper input common mode level for the analog input signal. The positive peaks of the individual input signals should each never exceed 2.6V. Each analog input pin of the differential pair should have a maximum peak-to-peak voltage of 1V, be 180° out of phase with each other and be centered around  $V_{CM}$ . The peak-to-peak voltage swing at each analog input pin should not exceed the 1V or the output data will be clipped.

Figure 19. Expected Input Signal Range

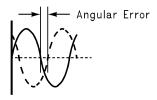

For single frequency sine waves the full scale error in LSB can be described as approximately

$$E_{FS} = 4096 (1 - \sin(90^{\circ} + \text{dev}))$$

(5)

18

Where dev is the angular difference in degrees between the two signals having a 180° relative phase relationship to each other (see Figure 20). For single frequency inputs, angular errors result in a reduction of the effective full scale input. For complex waveforms, however, angular errors will result in distortion.

Figure 20. Angular Errors Between the Two Input Signals Will Reduce the Output Level or Cause Distortion

It is recommended to drive the analog inputs with a source impedance less than  $100\Omega$ . Matching the source impedance for the differential inputs will improve even ordered harmonic performance (particularly second harmonic).

Table 1 indicates the input to output relationship of the ADC12DS080.

|                                       |                                       | •              | •                     |                     |

|---------------------------------------|---------------------------------------|----------------|-----------------------|---------------------|

| V <sub>IN</sub> ⁺                     | V <sub>IN</sub> -                     | Binary Output  | 2's Complement Output |                     |

| V <sub>CM</sub> - V <sub>REF</sub> /2 | V <sub>CM</sub> + V <sub>REF</sub> /2 | 0000 0000 0000 | 1000 0000 0000        | Negative Full-Scale |

| V <sub>CM</sub> - V <sub>REF</sub> /4 | V <sub>CM</sub> + V <sub>REF</sub> /4 | 0100 0000 0000 | 1100 0000 0000        |                     |

| V <sub>CM</sub>                       | V <sub>CM</sub>                       | 1000 0000 0000 | 0000 0000 0000        | Mid-Scale           |

| V <sub>CM</sub> + V <sub>REF</sub> /4 | V <sub>CM</sub> - V <sub>REF</sub> /4 | 1100 0000 0000 | 0100 0000 0000        |                     |

| V <sub>CM</sub> + V <sub>REE</sub> /2 | V <sub>CM</sub> - V <sub>REE</sub> /2 | 1111 1111 1111 | 0111 1111 1111        | Positive Full-Scale |

**Table 1. Input to Output Relationship**

#### **Driving the Analog Inputs**

The  $V_{IN}^+$  and the  $V_{IN}^-$  inputs of the ADC12DS080 have an internal sample-and-hold circuit which consists of an analog switch followed by a switched-capacitor amplifier.

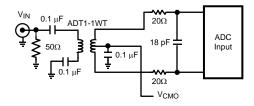

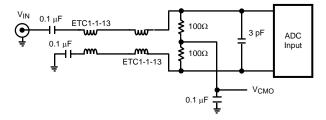

Figure 21 and Figure 22 show examples of single-ended to differential conversion circuits. The circuit in Figure 21 works well for input frequencies up to approximately 70MHz, while the circuit in Figure 22 works well above 70MHz.

Figure 21. Low Input Frequency Transformer Drive Circuit

Figure 22. High Input Frequency Transformer Drive Circuit

Copyright © 2008, Texas Instruments Incorporated

One short-coming of using a transformer to achieve the single-ended to differential conversion is that most RF transformers have poor low frequency performance. A differential amplifier can be used to drive the analog inputs for low frequency applications. The amplifier must be fast enough to settle from the charging glitches on the analog input resulting from the sample-and-hold operation before the clock goes high and the sample is passed to the ADC core.

#### **Input Common Mode Voltage**

The input common mode voltage,  $V_{CM}$ , should be in the range of 1.4V to 1.6V and be a value such that the peak excursions of the analog signal do not go more negative than ground or more positive than 2.6V. It is recommended to use  $V_{CMO}$  (pins 7,9) as the input common mode voltage.

#### Reference Pins

The ADC12DS080 is designed to operate with an internal or external 1.2V reference. The internal 1.2 Volt reference is the default condition when no external reference input is applied to the  $V_{REF}$  pin. If a voltage is applied to the  $V_{REF}$  pin, then that voltage is used for the reference. The  $V_{REF}$  pin should always be bypassed to ground with a 0.1  $\mu$ F capacitor close to the reference input pin.

It is important that all grounds associated with the reference voltage and the analog input signal make connection to the ground plane at a single, quiet point to minimize the effects of noise currents in the ground path.

The Reference Bypass Pins ( $V_{RP}$ ,  $V_{CMO}$ , and  $V_{RN}$ ) for channels A and B are made available for bypass purposes. These pins should each be bypassed to AGND with a low ESL (equivalent series inductance) 1  $\mu$ F capacitor placed very close to the pin to minimize stray inductance. A 0.1  $\mu$ F capacitor should be placed between  $V_{RP}$  and  $V_{RN}$  as close to the pins as possible, and a 1  $\mu$ F capacitor should be placed in parallel. This configuration is shown in Figure 23. It is necessary to avoid reference oscillation, which could result in reduced SFDR and/or SNR.  $V_{CMO}$  may be loaded to 1mA for use as a temperature stable 1.5V reference. The remaining pins should not be loaded.

Smaller capacitor values than those specified will allow faster recovery from the power down mode, but may result in degraded noise performance. Loading any of these pins, other than  $V_{CMO}$  may result in performance degradation.

The nominal voltages for the reference bypass pins are as follows:

$V_{CMO} = 1.5 \text{ V}$

$V_{RP} = 2.0 \text{ V}$

$V_{RN} = 1.0 \text{ V}$

### OF/DCS Pin