### 16-Bit, 1.2 MSPS CMOS, Sigma-Delta ADC

**AD7723**

#### **FEATURES**

16-Bit Sigma-Delta ADC

1.2 MSPS Output Word Rate

32×/16× Oversampling Ratio

Low-Pass and Band-Pass Digital Filter

Linear Phase

On-Chip 2.5 V Voltage Reference

Standby Mode

Flexible Parallel or Serial Interface

Crystal Oscillator

Single 5 V Supply

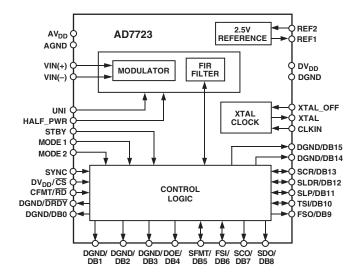

### **FUNCTIONAL BLOCK DIAGRAM**

### **GENERAL DESCRIPTION**

The AD7723 is a complete 16-bit, sigma-delta ADC. The part operates from a 5 V supply. The analog input is continuously sampled, eliminating the need for an external sample-and-hold. The modulator output is processed by a finite impulse response (FIR) digital filter. The on-chip filtering combined with a high oversampling ratio reduces the external antialias requirements to first order in most cases. The digital filter frequency response can be programmed to be either low-pass or band-pass.

The AD7723 provides 16-bit performance for input bandwidths up to 460 kHz at an output word rate up to 1.2 MHz. The sample rate, filter corner frequencies, and output word rate are set by the crystal oscillator or external clock frequency.

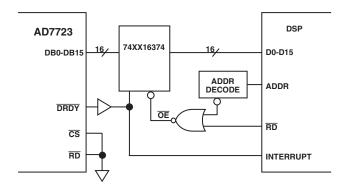

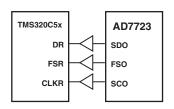

Data can be read from the device in either serial or parallel format. A stereo mode allows data from two devices to share a single serial data line. All interface modes offer easy, high speed connections to modern digital signal processors.

The part provides an on-chip 2.5 V reference. Alternatively, an external reference can be used.

A power-down mode reduces the idle power consumption to 200  $\mu$ W.

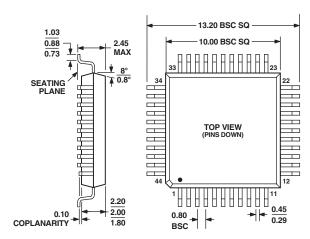

The AD7723 is available in a 44-lead PQFP package and is specified over the industrial temperature range from -40°C to +85°C.

Two input modes are provided, allowing both unipolar and bipolar input ranges.

# $\textbf{AD7723-SPECIFICATIONS}^{1} \text{ (AV}_{DD} = DV_{DD} = 5 \text{ V} \pm 5\%; \text{ AGND} = \text{AGND1} = \text{AGND2} = \text{DGND} = 0 \text{ V}; \\ \textbf{f}_{CLKIN} = 19.2 \text{ MHz}; \text{ REF2} = 2.5 \text{ V}; \textbf{T}_{A} = \textbf{T}_{MIN} \text{ to } \textbf{T}_{MAX}, \text{ unless otherwise noted.)}$

| Parameter                                                         | Test Conditions/Comments                       | Min        | B Version<br>Typ         | Max                       | Unit     |

|-------------------------------------------------------------------|------------------------------------------------|------------|--------------------------|---------------------------|----------|

| DYNAMIC SPECIFICATIONS <sup>2, 3</sup>                            | HALF_PWR = 0 or 1                              |            |                          |                           |          |

|                                                                   | $f_{CLKIN} = 10 \text{ MHz When HALF_PWR} = 1$ |            |                          |                           |          |

| Decimate by 32                                                    |                                                |            |                          |                           |          |

| Bipolar Mode                                                      |                                                |            |                          |                           |          |

| Signal to Noise                                                   | 2.5 M.D. C                                     | 0.5        | 0.0                      |                           | 170      |

| Full Power                                                        | 2.5 V Reference<br>3 V Reference               | 87<br>88.5 | 90<br>91                 |                           | dB<br>dB |

| Half Power                                                        | 3 V Reference                                  | 86.5       | 89                       |                           | dВ       |

| Total Harmonic Distortion <sup>4</sup>                            |                                                | 00.5       | -96                      | -90                       | dB       |

| Spurious-Free Dynamic Range <sup>4</sup>                          | 2.5 V Reference                                |            |                          | -92                       | dB       |

|                                                                   | 3 V Reference                                  |            |                          | -90                       | dB       |

| Unipolar Mode                                                     |                                                |            |                          |                           |          |

| Signal to Noise                                                   |                                                |            | 87                       |                           | dB       |

| Total Harmonic Distortion <sup>4</sup>                            |                                                |            | -89                      |                           | dB       |

| Spurious-Free Dynamic Range <sup>4</sup>                          |                                                |            | -90                      |                           | dB       |

| Band-Pass Filter Mode                                             |                                                |            |                          |                           |          |

| Bipolar Mode<br>Signal to Noise                                   |                                                | 76         | 79                       |                           | dB       |

| Decimate by 16                                                    |                                                | 10         | 19                       |                           | uD       |

| Bipolar Mode                                                      |                                                |            |                          |                           |          |

| Signal to Noise                                                   | Measurement Bandwidth = $0.383 \times F_0$     |            |                          |                           |          |

| C                                                                 | 2.5 V Reference                                | 82         | 86                       |                           | dB       |

|                                                                   | 3 V Reference                                  | 83         | 87                       |                           | dB       |

| Signal to Noise                                                   | Measurement Bandwidth = $0.5 \times F_0$       | 78         | 81.5                     |                           | dB       |

| Total Harmonic Distortion <sup>4</sup>                            | 2.5 V Reference                                |            |                          | -88                       | dB       |

|                                                                   | 3 V Reference                                  |            |                          | -86                       | dB       |

| Spurious-Free Dynamic Range <sup>4</sup>                          | 2.5 V Reference                                |            |                          | -90                       | dB       |

| Unipolar Mode                                                     | 3 V Reference                                  |            |                          | -88                       | dB       |

| Signal to Noise                                                   | Measurement Bandwidth = $0.383 \times F_0$     |            | 84                       |                           | dB       |

| Signal to Noise                                                   | Measurement Bandwidth = $0.5 \times F_0$       |            | 81                       |                           | dB       |

| Total Harmonic Distortion <sup>4</sup>                            | 0                                              |            | -89                      |                           | dB       |

| DIGITAL FILTER RESPONSE                                           |                                                |            |                          |                           |          |

| Low-Pass Decimate by 32                                           |                                                |            |                          |                           |          |

| 0 kHz to f <sub>CLKIN</sub> /83.5                                 |                                                |            |                          | $\pm 0.001$               | dB       |

| $f_{\rm CLKIN}/66.9$                                              |                                                | -3         |                          |                           | dB       |

| $ m f_{CLKIN}/64$                                                 |                                                | -6         |                          |                           | dB       |

| $f_{\rm CLKIN}/51.9$ to $f_{\rm CLKIN}/2$                         |                                                |            |                          | -90                       | dB       |

| Group Delay                                                       |                                                |            | 1293/2f <sub>CLKIN</sub> |                           |          |

| Settling Time Low-Pass Decimate by 16                             |                                                |            | $1293/f_{CLKIN}$         |                           |          |

| 0 kHz to f <sub>CLKIN</sub> /41.75                                |                                                |            |                          | ±0.001                    | dB       |

| f <sub>CLKIN</sub> /33.45                                         |                                                | -3         |                          | ±0.001                    | dB       |

| f <sub>CLKIN</sub> /32                                            |                                                | -6         |                          |                           | dB       |

| $f_{CLKIN}/25.95$ to $f_{CLKIN}/2$                                |                                                |            |                          | -90                       | dB       |

| Group Delay                                                       |                                                |            | $541/2f_{CLKIN}$         |                           |          |

| Settling Time                                                     |                                                |            | $541/f_{CLKIN}$          |                           |          |

| Band-Pass Decimate by 32                                          |                                                |            |                          |                           |          |

| $f_{CLKIN}/51.90$ to $f_{CLKIN}/41.75$                            |                                                |            |                          | $\pm 0.001$               | dB       |

| $f_{\text{CLKIN}}/62.95, f_{\text{CLKIN}}/33.34$                  |                                                | -3         |                          |                           | dB       |

| f <sub>CLKIN</sub> /64, f <sub>CLKIN</sub> /32                    | . /2                                           | -6         |                          | 00                        | dB<br>dB |

| 0 kHz to $f_{CLKIN}/83.5$ , $f_{CLKIN}/25.95$ to f<br>Group Delay | CLKIN <sup>, 2</sup>                           |            | 1293/2f <sub>CLKIN</sub> | -90                       | ub       |

| Settling Time                                                     |                                                |            | 1293/f <sub>CLKIN</sub>  |                           |          |

| Output Data Rate, F <sub>O</sub>                                  |                                                |            | JI-CLKIN                 |                           |          |

| Decimate by 32                                                    |                                                |            | $f_{CLKIN}/32$           |                           |          |

| Decimate by 16                                                    |                                                |            | f <sub>CLKIN</sub> /16   |                           |          |

| ANALOG INPUTS                                                     |                                                |            |                          |                           |          |

| Full-Scale Input Span                                             | VIN(+) – VIN(–)                                |            |                          |                           |          |

| Bipolar Mode                                                      | (')                                            |            |                          | $\pm 4/5 \times V_{REF2}$ | v        |

| Unipolar Mode                                                     |                                                | 0          |                          | $8/5 \times V_{REF2}$     | v        |

-2-

REV. A

| Parameter                                                                                                                  | Test Conditions/Comments                                     | Min  | B Version<br>Typ                | Max                      | Unit                     |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|------|---------------------------------|--------------------------|--------------------------|

| ANALOG INPUTS (Continued) Absolute Input Voltage Input Sampling Capacitance Input Sampling Rate, f <sub>CLKIN</sub>        | VIN(+) and/or VIN(-)                                         | AGND | 2                               | AV <sub>DD</sub><br>19.2 | V<br>pF<br>MHz           |

| CLOCK<br>CLKIN Duty Ratio                                                                                                  |                                                              | 45   |                                 | 55                       | %                        |

| REFERENCE REF1 Output Resistance Using Internal Reference REF2 Output Voltage                                              |                                                              | 2.39 | 3 2.54                          | 2.69                     | kΩ<br>V                  |

| REF2 Output Voltage Drift Using External Reference REF2 Input Impedance REF2 External Voltage Range                        | REF1 = AGND                                                  | 1.2  | 60<br>4<br>2.5                  | 3.15                     | ppm/°C<br>kΩ<br>V        |

| STATIC PERFORMANCE Resolution Differential Nonlinearity Integral Nonlinearity DC CMRR Offset Error Gain Error <sup>5</sup> | Guaranteed Monotonic                                         | 16   | ±0.5<br>±2<br>80<br>±20<br>±0.5 | ±1                       | Bits LSB LSB dB mV % FSR |

| LOGIC INPUTS (Excluding CLKIN) $V_{\rm INH}$ , Input High Voltage $V_{\rm INL}$ , Input Low Voltage                        |                                                              | 2.0  |                                 | 0.8                      | V<br>V                   |

| CLOCK INPUT (CLKIN)  V <sub>INH</sub> , Input High Voltage  V <sub>INL</sub> , Input Low Voltage                           |                                                              | 3.8  |                                 | 0.4                      | V<br>V                   |

| ALL LOGIC INPUTS  I <sub>IN</sub> , Input Current  C <sub>IN</sub> , Input Capacitance                                     | $V_{IN} = 0 \text{ V to } DV_{DD}$                           |      |                                 | ±10<br>10                | μA<br>pF                 |

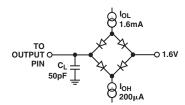

| LOGIC OUTPUTS $V_{OH}$ , Output High Voltage $V_{OL}$ , Output Low Voltage                                                 | $ I_{OUT}  = 200 \mu\text{A}$<br>$ I_{OUT}  = 1.6 \text{mA}$ | 4.0  |                                 | 0.4                      | V<br>V                   |

| POWER SUPPLIES $\begin{array}{c} AV_{DD} \\ I_{AVDD} \end{array}$                                                          | HALF_PWR = Logic Low<br>HALF_PWR = Logic High                | 4.75 | 50<br>25                        | 5.25<br>60<br>33         | V<br>mA<br>mA            |

| $rac{	ext{DV}_{	ext{DD}}}{	ext{I}_{	ext{DVDD}}}$ Power Consumption $^6$                                                   | HALF_PWR = Logic Low HALF_PWR = Logic High Standby Mode      | 4.75 | 25<br>15                        | 5.25<br>35<br>20<br>200  | V<br>mA<br>mA<br>μW      |

| 1 ower Consumption                                                                                                         | Standby Mode                                                 |      |                                 | 200                      | μw                       |

Specifications subject to change without notice.

REV. A -3-

<sup>&</sup>lt;sup>1</sup>Operating temperature range is as follows: B Version: -40°C to +85°C. <sup>2</sup>Typical values for SNR apply for parts soldered directly to a printed circuit board ground plane.

$<sup>^3</sup>$ Dynamic specifications apply for input signal frequencies from dc to  $0.0240 \times f_{CLKIN}$  in decimate by 16 Mode, and from dc to  $0.0120 \times f_{CLKIN}$  in decimate by 32 Mode.  $^4$ When using the internal reference, THD and SFDR specifications apply only to input signals above 10 kHz with a 10  $\mu$ F decoupling capacitor between REF2 and AGND2. At frequencies below 10 kHz, THD degrades to 84 dB and SFDR degrades to 86 dB.

<sup>&</sup>lt;sup>5</sup>Gain Error excludes reference error.

$<sup>^6\</sup>text{CLKIN}$  and digital inputs static and equal to 0 or  $DV_{DD}.$

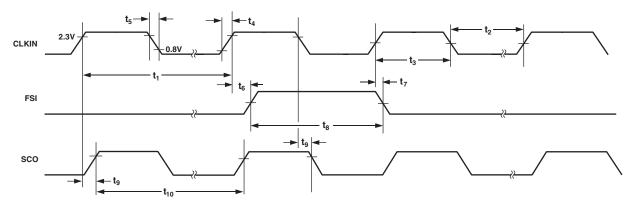

##

| Parameter                                                       | Symbol          | Min               | Typ | Max               | Unit             |

|-----------------------------------------------------------------|-----------------|-------------------|-----|-------------------|------------------|

| CLKIN Frequency                                                 | $f_{CLK}$       | 1                 |     | 19.2              | MHz              |

| CLKIN Period ( $t_{CLK} = 1/f_{CLK}$ )                          | $t_1$           | 0.052             |     | 1                 | μs               |

| CLKIN Low Pulsewidth                                            | $t_2$           | $0.45 \times t_1$ |     | $0.55 \times t_1$ |                  |

| CLKIN High Pulsewidth                                           | t <sub>3</sub>  | $0.45 \times t_1$ |     | $0.55 \times t_1$ |                  |

| CLKIN Rise Time                                                 | $t_4$           | 5                 |     |                   | ns               |

| CLKIN Fall Time                                                 | t <sub>5</sub>  | 5                 |     |                   | ns               |

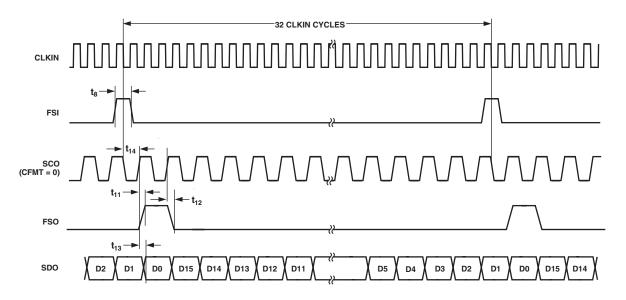

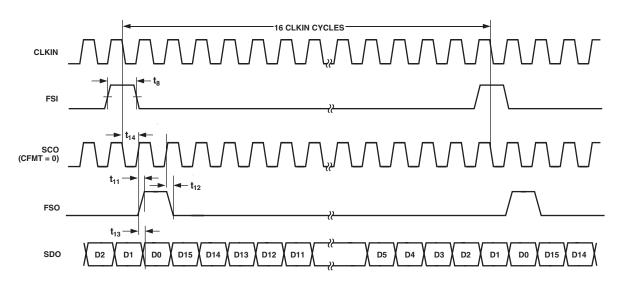

| FSI Setup Time                                                  | t <sub>6</sub>  | 0                 |     | 5                 | ns               |

| FSI Hold Time                                                   | t <sub>7</sub>  | 0                 |     | 5                 | ns               |

| FSI High Time <sup>1</sup>                                      | t <sub>8</sub>  |                   |     | 1                 | t <sub>CLK</sub> |

| CLKIN to SCO Delay                                              | t <sub>9</sub>  |                   | 25  | 40                | ns               |

| SCO Period <sup>2</sup> , SCR = 1                               | t <sub>10</sub> |                   | 2   |                   | t <sub>CLK</sub> |

| SCO Period <sup>2</sup> , SCR = $0$                             | t <sub>10</sub> |                   | 1   |                   | t <sub>CLK</sub> |

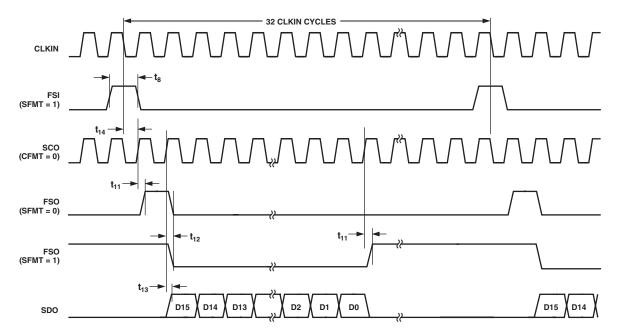

| SCO Transition to FSO High Delay                                | t <sub>11</sub> |                   | 0   | 5                 | ns               |

| SCO Transition to FSO Low Delay                                 | t <sub>12</sub> |                   | 0   | 5                 | ns               |

| SCO Transition to SDO Valid Delay                               | t <sub>13</sub> |                   | 5   | 12                | ns               |

| SCO Transition from FSI <sup>3</sup>                            | t <sub>14</sub> |                   | 60  | $t_{CLK} + t_2$   |                  |

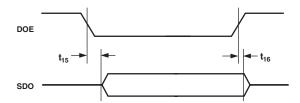

| SDO Enable Delay Time                                           | t <sub>15</sub> |                   | 5   | 20                | ns               |

| SDO Disable Delay Time                                          | t <sub>16</sub> |                   | 5   | 20                | ns               |

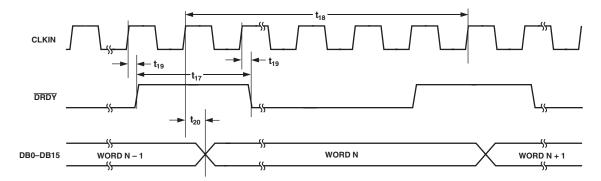

| DRDY High Time <sup>2</sup>                                     | t <sub>17</sub> | 2                 |     |                   | t <sub>CLK</sub> |

| Conversion Time <sup>2</sup> (Refer to Tables I and II)         | t <sub>18</sub> | 16/32             |     |                   | t <sub>CLK</sub> |

| CLKIN to $\overline{\text{DRDY}}$ Transition                    | t <sub>19</sub> |                   | 35  | 50                | ns               |

| CLKIN to DATA Valid                                             | t <sub>20</sub> |                   | 20  | 35                | ns               |

| $\overline{\text{CS}}/\overline{\text{RD}}$ Setup Time to CLKIN | t <sub>21</sub> | 0                 |     |                   | ns               |

| CS/RD Hold Time to CLKIN                                        | t <sub>22</sub> | 20                |     |                   | ns               |

| Data Access Time                                                | t <sub>23</sub> |                   | 20  | 35                | ns               |

| Bus Relinquish Time                                             | t <sub>24</sub> |                   | 20  | 35                | ns               |

| SYNC Input Pulsewidth                                           | t <sub>25</sub> | 1                 |     |                   | t <sub>CLK</sub> |

| SYNC Low Time before CLKIN Rising                               | t <sub>26</sub> | 0                 |     |                   | ns               |

| DRDY High Delay after Rising SYNC                               | t <sub>27</sub> |                   | 25  | 35                | ns               |

| DRDY Low Delay after SYNC Low                                   | t <sub>28</sub> |                   |     | 2049              | t <sub>CLK</sub> |

### NOTES

Specifications subject to change without notice.

Figure 1. Load Circuit for Timing Specifications

-4- REV. A

<sup>&</sup>lt;sup>1</sup>FSO pulses are gated by the release of FSI (going low).

<sup>&</sup>lt;sup>2</sup>Guaranteed by design.

<sup>&</sup>lt;sup>3</sup>Frame sync is initiated on the falling edge of CLKIN.

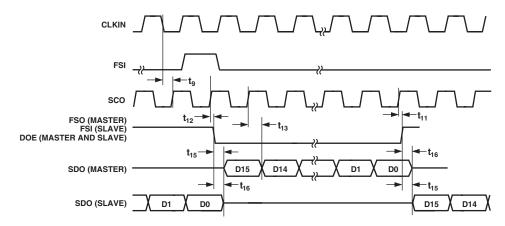

Figure 2. Serial Mode Timing for Clock Input, Frame Sync Input, and Serial Clock Output

Figure 3. Serial Mode 1. Timing for Frame Sync Input, Frame Sync Output, Serial Clock Output, and Serial Data Output (Refer to Table I for Control Inputs, TSI = DOE)

Figure 4. Serial Mode 2. Timing for Frame Sync Input, Frame Sync Output, Serial Clock Output, and Serial Data Output (Refer to Table I for Control Inputs, TSI = DOE)

REV. A

Figure 5. Serial Mode 3. Timing for Frame Sync Input, Frame Sync Output, Serial Clock Output, and Serial Data Output (Refer to Table I for Control Inputs, TSI = DOE)

Table I. Serial Interface (Mode1 = 0, Mode2 = 0)

| Serial Mode | Decimation<br>Ratio (SLDR) | Digital Filter<br>Mode (SLP) | SCO Frequency<br>(SCR) | Output Data<br>Rate    | Cont<br>SLDR | rol Inp<br>SLP | uts<br>SCR |

|-------------|----------------------------|------------------------------|------------------------|------------------------|--------------|----------------|------------|

| 1           | 32                         | Low-Pass                     | $f_{CLKIN}$            | f <sub>CLKIN</sub> /32 | 1            | 1              | 0          |

| 1           | 32                         | Band-Pass                    | f <sub>CLKIN</sub>     | f <sub>CLKIN</sub> /32 | 1            | 0              | 0          |

| 2           | 32                         | Low-Pass                     | $f_{CLKIN}/2$          | f <sub>CLKIN</sub> /32 | 1            | 1              | 1          |

| 2           | 32                         | Band-Pass                    | $f_{CLKIN}/2$          | f <sub>CLKIN</sub> /32 | 1            | 0              | 1          |

| 3           | 16                         | Low-Pass                     | $f_{CLKIN}$            | $f_{CLKIN}/16$         | 0            | 1              | 0          |

Table II. Parallel Interface

| Digital Filter<br>Mode | Decimation<br>Ratio | Output<br>Data Rate    |   | l Inputs<br>MODE2 |

|------------------------|---------------------|------------------------|---|-------------------|

| Band-Pass              | 32                  | f <sub>CLKIN</sub> /32 | 0 | 1                 |

| Low-Pass               | 32                  | f <sub>CLKIN</sub> /32 | 1 | 0                 |

| Low-Pass               | 16                  | f <sub>CLKIN</sub> /16 | 1 | 1                 |

Figure 6. Serial Mode Timing for Data Output Enable and Serial Data Output

-6-

REV. A

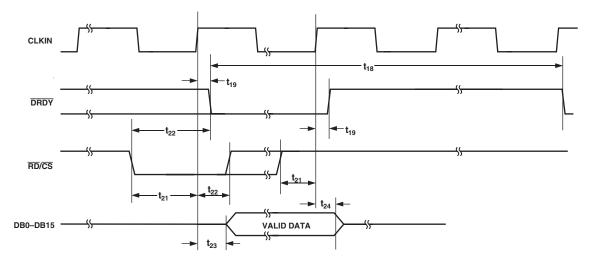

Figure 7a. Parallel Mode Read Timing,  $\overline{CS}$  and  $\overline{RD}$  Tied Logic Low

Figure 7b. Parallel Mode Read Timing,  $\overline{CS} = \overline{RD}$

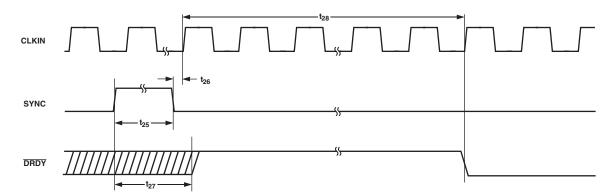

Figure 8. SYNC Timing

REV. A -7-

### ABSOLUTE MAXIMUM RATINGS\*

$(T_A = 25^{\circ}C, \text{ unless otherwise noted.})$

| DV <sub>DD</sub> to DGND                                                       |

|--------------------------------------------------------------------------------|

| $AV_{DD}$ , $AV_{DD1}$ to $AGND$                                               |

| $AV_{DD}$ , $AV_{DD1}$ to $DV_{DD}$                                            |

| AGND, AGND1 to DGND0.3 V to +0.3 V                                             |

| Digital Inputs to DGND $-0.3 \text{ V}$ to DV <sub>DD</sub> + 0.3 V            |

| Digital Outputs to DGND $-0.3 \text{ V}$ to DV <sub>DD</sub> + $0.3 \text{ V}$ |

| VIN(+), VIN(-) to AGND $\dots -0.3 \text{ V}$ to AV <sub>DD</sub> + 0.3 V      |

| REF1 to AGND                                                                   |

| REF2 to AGND $\dots -0.3 \text{ V}$ to AV <sub>DD</sub> + 0.3 V                |

| Operating Temperature Range40°C to +85°C                                       |

| Storage Temperature Range65°C to +150°C                                        |

| Junction Temperature 150°C                                                     |

| $\theta_{JA}$ Thermal Impedance                                                |

| Lead Temperature, Soldering                                                    |

| Vapor Phase (60 sec)                                                           |

| Infrared (15 sec)                                                              |

<sup>\*</sup>Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ORDERING GUIDE**

| Model    | Temperature<br>Range |                       | Package<br>Option |

|----------|----------------------|-----------------------|-------------------|

| AD7723BS | −40°C to +85°C       | Plastic Quad Flatpack | S-44              |

### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD7723 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

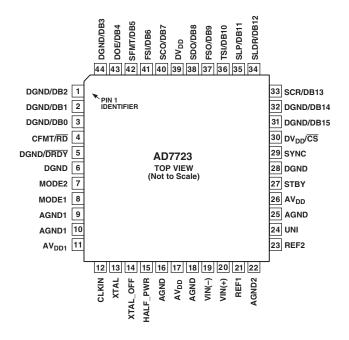

### PIN CONFIGURATION

### PIN FUNCTION DESCRIPTIONS

| Mnemonic                     | Pin No.    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DGND                         | 6, 28      | Ground Reference for Digital Circuitry                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| MODE1/<br>MODE2              | 8, 7       | Mode Control Inputs. The MODE1 and MODE2 Pins choose either parallel or serial data interface operation and select the operating mode for the digital filter in Parallel Mode. Refer to Tables I and II.                                                                                                                                                                                                                                                                                        |

| AGND1                        | 9, 10      | Digital Logic Power Supply Ground for the Analog Modulator                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| $\mathrm{AV}_{\mathrm{DD1}}$ | 11         | Digital Logic Power Supply Voltage for the Analog Modulator                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CLKIN                        | 12         | Clock Input. An external clock source can be applied directly to this pin with XTAL_OFF tied high. Alternatively, a parallel resonant fundamental frequency crystal, in parallel with a 1 $M\Omega$ resistor, can be connected between the XTAL Pin and the CLKIN Pin with XTAL_OFF tied low. External capacitors are then required from the CLKIN and XTAL Pins to ground. Consult the crystal manufacturer's recommendation for the load capacitors.                                          |

| XTAL                         | 13         | Input to Crystal Oscillator Amplifier. If an external clock is used, XTAL should be tied to AGND1.                                                                                                                                                                                                                                                                                                                                                                                              |

| XTAL_OFF                     | 14         | Oscillator Enable Input. A logic high disables the crystal oscillator amplifier to allow use of an external clock source. Set low when using an external crystal between the CLKIN and XTAL Pins.                                                                                                                                                                                                                                                                                               |

| HALF_PWR                     | 15         | When set high, the power dissipation is reduced by approximately one-half, and a maximum CLKIN frequency of 10 MHz applies.                                                                                                                                                                                                                                                                                                                                                                     |

| AGND                         | 16, 18, 25 | Power Supply Ground for the Analog Modulator                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| $\mathrm{AV}_{\mathrm{DD}}$  | 17, 26     | Positive Power Supply Voltage for the Analog Modulator                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| VIN(-)                       | 19         | Negative Terminal of the Differential Analog Input                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| VIN(+)                       | 20         | Positive Terminal of the Differential Analog Input                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| REF1                         | 21         | Reference Output. REF1 connects through 3 k $\Omega$ to the output of the internal 2.5 V reference and to a buffer amplifier that drives the $\Sigma$ - $\Delta$ modulator.                                                                                                                                                                                                                                                                                                                     |

| AGND2                        | 22         | Power Supply Ground Return to the Reference Circuitry, REF2, of the Analog Modulator                                                                                                                                                                                                                                                                                                                                                                                                            |

| REF2                         | 23         | Reference Input. REF2 connects to the output of an internal buffer amplifier that drives the $\Sigma$ - $\Delta$ modulator. When REF2 is used as an input, REF1 must be connected to AGND to disable the internal buffer amplifier.                                                                                                                                                                                                                                                             |

| UNI                          | 24         | Analog Input Range Select Input. The UNI Pin selects the analog input range for either bipolar or unipolar operation. A logic high input selects unipolar operation and a logic low selects bipolar operation.                                                                                                                                                                                                                                                                                  |

| STBY                         | 27         | Standby Logic Input. A logic high sets the AD7723 into the power-down state.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SYNC                         | 29         | Synchronization Logic Input. When using more than one AD7723 operated from a common master clock, SYNC allows each ADC to simultaneously sample its analog input and update its output register. A rising edge resets the AD7723 digital filter sequencer counter to zero. When the rising edge of CLKIN senses a logic low on SYNC, the reset state is released. Because the digital filter and sequencer are completely reset during this action, SYNC pulses cannot be applied continuously. |

| $DV_{DD}$                    | 39         | Digital Power Supply Voltage; 5 V ± 5%                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

REV. A -9-

### PARALLEL MODE PIN FUNCTION DESCRIPTIONS

| Mnemonic                | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DGND/DB2                | 1       | Data Output Bit                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DGND/DB1                | 2       | Data Output Bit                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DGND/DB0                | 3       | Data Output Bit (LSB)                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CFMT/RD                 | 4       | Read Logic Input. Used in conjunction with $\overline{CS}$ to read data from the parallel bus. The output databus is enabled when the rising edge of CLKIN senses a logic low level on $\overline{RD}$ if $\overline{CS}$ is also low. When $\overline{RD}$ is sensed high, the output data bits, DB15–DB0, will be high impedance.                                                                                                               |

| DGND/ <del>DRDY</del>   | 5       | Data Ready Logic Output. A falling edge indicates a new output word is available to be read from the output data register. $\overline{DRDY}$ will return high upon completion of a read operation. If a read operation does not occur between output updates, $\overline{DRDY}$ will pulse high for two CLKIN cycles before the next output update. $\overline{DRDY}$ also indicates when conversion results are available after a SYNC sequence. |

| $DV_{DD}/\overline{CS}$ | 30      | Chip Select Logic Input                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DGND/DB15               | 31      | Data Output Bit (MSB)                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DGND/DB14               | 32      | Data Output Bit                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SCR/DB13                | 33      | Data Output Bit                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SLDR/DB12               | 34      | Data Output Bit                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SLP/DB11                | 35      | Data Output Bit                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| TSI/DB10                | 36      | Data Output Bit                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| FSO/DB9                 | 37      | Data Output Bit                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SDO/DB8                 | 38      | Data Output Bit                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SCO/DB7                 | 40      | Data Output Bit                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| FSI/DB6                 | 41      | Data Output Bit                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SFMT/DB5                | 42      | Data Output Bit                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DOE/DB4                 | 43      | Data Output Bit                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| DGND/DB3                | 44      | Data Output Bit                                                                                                                                                                                                                                                                                                                                                                                                                                   |

-10- REV. A

### SERIAL MODE PIN FUNCTION DESCRIPTIONS

| Mnemonic                | Pin No. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DGND/DB2                | 1       | Tie to DGND                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DGND/DB1                | 2       | Tie to DGND                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DGND/DB0                | 3       | Tie to DGND                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CFMT/RD                 | 4       | Serial Clock Format Logic Input. The Clock Format Pin selects whether the serial data, SDO, is valid on the rising or falling edge of the serial clock, SCO. When CFMT is logic low, serial data is valid on the falling edge of the serial clock, SCO. If CFMT is logic high, SDO is valid on the rising edge of SCO.                                                                                                                                      |

| $DGND/\overline{DRDY}$  | 5       | Tie to DGND                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| $DV_{DD}/\overline{CS}$ | 30      | Tie to DV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| DGND/DB15               | 31      | Tie to DGND                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DGND/DB14               | 32      | Tie to DGND                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| SCR/DB13                | 33      | Serial Clock Rate Select Input. With SCR set logic low, the serial clock output frequency, SCO, is equal to the CLKIN frequency. A logic high sets it equal to one-half the CLKIN frequency.                                                                                                                                                                                                                                                                |

| SLDR/DB12               | 34      | Serial Mode Low/High Output Data Rate Select Input. With SLDR set logic high, the low data rate is selected. A logic low selects the high data rate. The high data rate corresponds to data at the output of the fourth decimation filter (Decimate by 16). The low data rate corresponds to data at the output of the fifth decimation filter (Decimate by 32).                                                                                            |

| SLP/DB11                | 35      | Serial Mode Low-Pass/Band-Pass Filter Select Input. With SLP set logic high, the low-pass filter response is selected. A logic low selects band-pass.                                                                                                                                                                                                                                                                                                       |

| TSI/DB10                | 36      | Time Slot Logic Input. The logic level on TSI sets the active state of the DOE Pin. With TSI set logic high, DOE will enable the SDO output buffer when it is a logic high and vice versa. TSI is used when two AD7723s are connected to the same serial databus. When this function is not needed, TSI and DOE should be tied low.                                                                                                                         |

| FSO/DB9                 | 37      | Frame Sync Output. FSO indicates the beginning of a word transmission on the SDO Pin. Depending on the logic level of the SFMT Pin, the FSO signal is either a positive pulse approximately one SCO period wide or a frame pulse that is active low for the duration of the 16-data bit transmission.                                                                                                                                                       |

| SDO/DB8                 | 38      | Serial Data Output. The serial data is shifted out MSB first, synchronous with the SCO. Serial Mode 1 data transmissions last 32 SCO cycles. After the LSB is output, trailing zeros are output for the remaining 16 SCO cycles. Serial Modes 2 and 3 data transmissions last 16 SCO cycles.                                                                                                                                                                |

| SCO/DB7                 | 40      | Serial Clock Output                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| FSI/DB6                 | 41      | Frame Synchronization Logic Input. The FSI input is used to synchronize the AD7723 serial output data register to an external source and to allow more than one AD7723, operated from a common master clock, to simultaneously sample its analog input and update its output register.                                                                                                                                                                      |

| SFMT/DB5                | 42      | Serial Data Format Logic Input. The logic level on the SFMT Pin selects the format of the FSO signal for Serial Mode 1. A logic low makes the FSO output a pulse one SCO cycle wide at the beginning of a serial data transmission. With SFMT set to a logic high, the FSO signal is a frame pulse that is active low for the duration of the 16-bit transmission. For Serial Modes 2 and 3, SFMT should be tied high.                                      |

| DOE/DB4                 | 43      | Data Output Enable Logic Input. The DOE Pin controls the three-state output buffer of the SDO Pin. The active state of DOE is determined by the logic level on the TSI Pin. When the DOE logic level equals the level on the TSI Pin, the serial data output, SDO, is active. Otherwise SDO will be high impedance. SDO can be three-state after a serial data transmission by connecting DOE to FSO. In normal operations, TSI and DOE should be tied low. |

| DGND/DB3                | 44      | Tie to DGND                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

REV. A -11-

### **TERMINOLOGY**

### Signal-to-Noise Ratio (SNR)

SNR is the measured signal-to-noise ratio at the output of the ADC. The signal is the rms magnitude of the fundamental. Noise is the rms sum of all of the nonfundamental signals up to half the output data rate ( $F_{\rm O}/2$ ), excluding dc. The ADC is evaluated by applying a low noise, low distortion sine wave signal to the input pins. By generating a Fast Fourier Transform (FFT) plot, the SNR data can then be obtained from the output spectrum.

### **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of the harmonics to the rms value of the fundamental. THD is defined as:

$$THD = 20 \log \frac{\sqrt{{V_2}^2 + {V_3}^2 + {V_4}^2 + {V_5}^2 + {V_6}^2}}{V_1}$$

where  $V_1$  is the rms amplitude of the fundamental and  $V_2$ ,  $V_3$ ,  $V_4$ ,  $V_5$ , and  $V_6$  are the rms amplitudes of the second through sixth harmonics. The *THD* is also derived from the FFT plot of the ADC output spectrum.

### Spurious-Free Dynamic Range (SFDR)

Defined as the difference, in dB, between the peak spurious or harmonic component in the ADC output spectrum (up to  $F_0/2$  and excluding dc) and the rms value of the fundamental. Normally, the value of this specification will be determined by the largest harmonic in the output spectrum of the FFT. For input signals whose second harmonics occur in the stop-band region of the digital filter, the spur in the noise floor limits the SFDR.

### Pass-Band Ripple

The frequency response variation of the AD7723 in the defined pass-band frequency range.

### **Pass-Band Frequency**

The frequency up to which the frequency response variation is within the pass-band ripple specification.

### **Cutoff Frequency**

The frequency below which the AD7723's frequency response will not have more than 3 dB of attenuation.

### **Stop-Band Frequency**

The frequency above which the AD7723's frequency response will be within its stop-band attenuation.

### **Stop-Band Attenuation**

The AD7723's frequency response will not have less than 90 dB of attenuation in the stated frequency band.

### **Integral Nonlinearity**

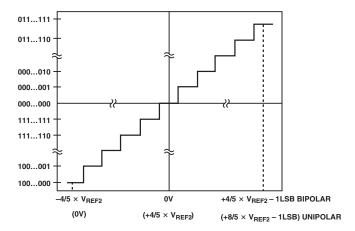

This is the maximum deviation of any code from a straight line passing through the endpoints of the transfer function. The endpoints of the transfer function are minus full scale, a point 0.5 LSB below the first code transition (100...00 to 100...01 in Bipolar Mode, 000...00 to 000...01 in Unipolar Mode), and plus full scale, a point 0.5 LSB above the last code transition (011...10 to 011...11 in Bipolar Mode, 111...10 to 111...11 in Unipolar Mode). The error is expressed in LSBs.

### **Differential Nonlinearity**

This is the difference between the measured and the ideal 1 LSB change between two adjacent codes in the ADC.

### Common-Mode Rejection Ratio

The ability of a device to reject the effect of a voltage applied to both input terminals simultaneously—often through variation of a ground level—is specified as a common–mode rejection ratio. CMRR is the ratio of gain for the differential signal to the gain for the common–mode signal.

### **Unipolar Offset Error**

Unipolar offset error is the deviation of the first code transition (10...000 to 10...001) from the ideal differential voltage (VIN(+) - VIN(-) + 0.5 LSB) when operating in the Unipolar Mode.

### **Bipolar Offset Error**

This is the deviation of the midscale transition code (111...11 to 000...00) from the ideal differential voltage (VIN(+) – VIN(-) – 0.5 LSB) when operating in the Bipolar Mode.

### **Gain Error**

The first code transition should occur at an analog value 1/2 LSB above –full scale. The last transition should occur for an analog value 1 1/2 LSB below the nominal full scale. Gain error is the deviation of the *actual* difference between first and last code transitions and the *ideal* difference between first and last code transitions.

–12– REV. A

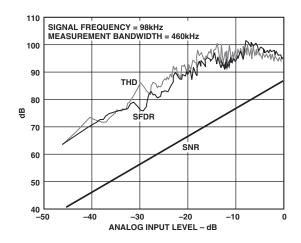

### **Typical Performance Characteristics—AD7723**

$(AV_{DD} = DV_{DD} = 5 \text{ V}; T_A = 25^{\circ}\text{C}; CLKIN = 19.2 \text{ MHz}; External 2.5 V Reference, unless otherwise noted.)$

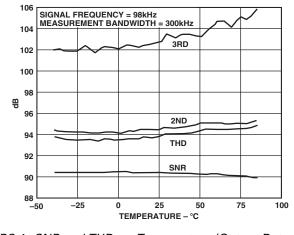

TPC 1. SNR, THD, and SFDR vs. Analog Input Level Relative to Full Scale (Output Data Rate = 1.2 MHz)

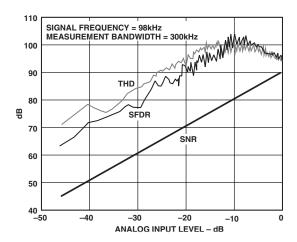

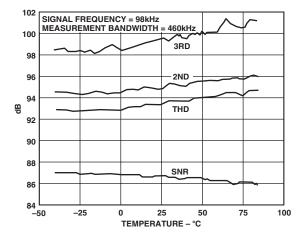

TPC 4. SNR and THD vs. Temperature (Output Data Rate = 600 kHz)

TPC 2. SNR, THD, and SFDR vs. Analog Input Level Relative to Full Scale (Output Data Rate = 600 kHz)

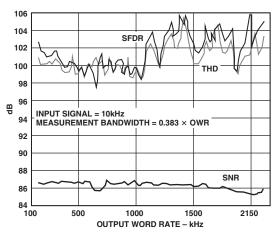

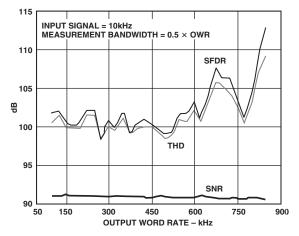

TPC 5. SNR, THD, and SFDR vs. Sampling Frequency (Decimate by 16)

TPC 3. SNR and THD vs. Temperature (Output Data Rate = 1.2 MHz)

TPC 6. SNR, THD, and SFDR vs. Sampling Frequency (Decimate by 32)

REV. A -13-

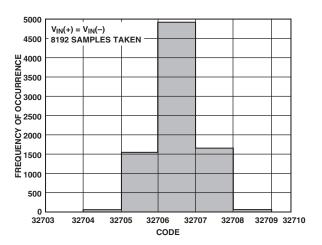

TPC 7. Histogram of Output Codes with DC Input (Output Data Rate = 1.2 MHz)

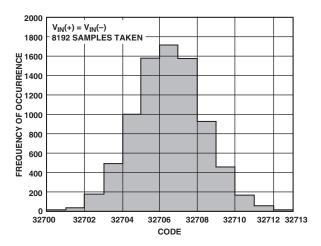

TPC 8. Histogram of Output Codes with DC Input (Output Data Rate = 600 kHz)

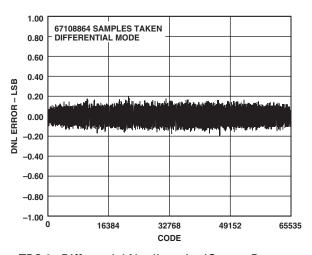

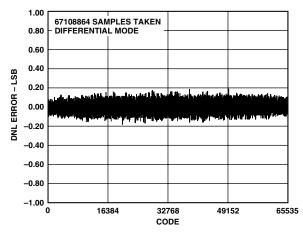

TPC 9. Differential Nonlinearity (Output Data Rate = 1.2 MHz)

TPC 10. Differential Nonlinearity (Output Data Rate = 600 kHz)

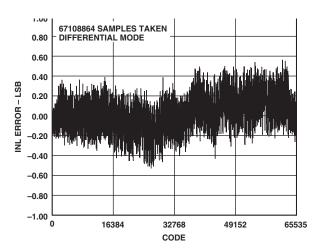

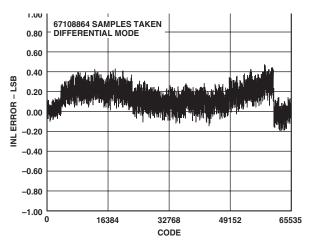

TPC 11. Integral Nonlinearity (Output Data Rate = 1.2 MHz)

TPC 12. Integral Nonlinearity (Output Data Rate = 600 kHz)

-14- REV. A

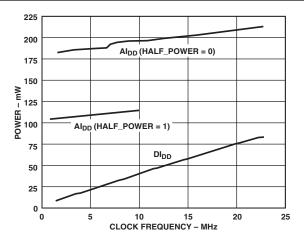

TPC 13. Power Consumption vs. CLKIN Frequency

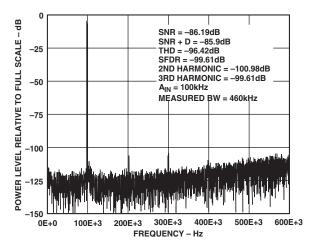

TPC 14. 16 K Point FFT (Output Data Rate = 1.2 MHz)

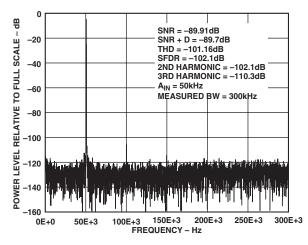

TPC 15. 16 K Point FFT (Output Data Rate = 600 kHz)

#### CIRCUIT DESCRIPTION

The AD7723 ADC employs a sigma-delta conversion technique to convert the analog input into an equivalent digital word. The modulator samples the input waveform and outputs an equivalent digital word at the input clock frequency,  $f_{\rm CLKIN}$ .

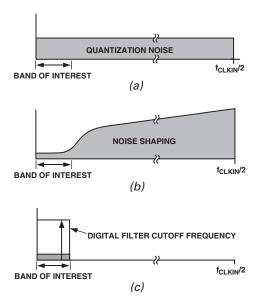

Due to the high oversampling rate that spreads the quantization noise from 0 to  $f_{CLKIN}/2$ , the noise energy contained in the band of interest is reduced (Figure 9a). To further reduce the quantization noise, a high order modulator is employed to shape the noise spectrum so that most of the noise energy is shifted out of the band of interest (Figure 9b).

The digital filter that follows the modulator removes the large out-of-band quantization noise (Figure 9c) while also reducing the data rate from  $f_{\rm CLKIN}$  at the input of the filter to  $f_{\rm CLKIN}/32$  or  $f_{\rm CLKIN}/16$  at the output of the filter, depending on the state on the MODE1/MODE2 Pins in Parallel Interface Mode or the SLDR Pin in Serial Interface Mode. The AD7723 output data rate is a little over twice the signal bandwidth, which guarantees that there is no loss of data in the signal band.

Digital filtering has certain advantages over analog filtering. First since digital filtering occurs after the A/D conversion, it can remove noise injected during the conversion process. Analog filtering cannot remove noise injected during conversion. Second, the digital filter combines low pass-band ripple with a steep roll-off while also maintaining a linear phase response.

Figure 9. Sigma-Delta ADC

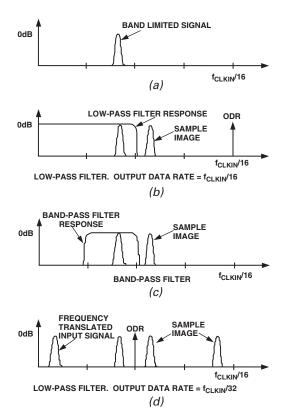

The AD7723 employs four or five finite impulse response (FIR) filters in series. Each individual filter's output data rate is half that of the filter's input data rate. When data is fed to the interface from the output of the fourth filter, the output data rate is  $f_{\rm CLKIN}/16$  and the resulting oversampling ratio (OSR) of the converter is 16. Data fed to the interface from the output of the fifth filter results in an output data rate of  $f_{\rm CLKIN}/32$  and a corresponding OSR for the converter of 32. When an output data rate (ODR) of  $f_{\rm CLKIN}/32$  is selected, the digital filter response can be set to either low-pass or band-pass. The band-pass response is useful when the input signal is band limited since the resulting output data rate is half that required to convert the band when the low-pass operating mode is used. To illustrate the operation of this mode, consider a

REV. A -15-

band-limited signal as shown in Figure 10a. This signal band can be correctly converted by selecting the (low-pass) ODR =  $f_{\rm CLKIN}/16$  Mode, as shown in Figure 10b. Note that the output data rate is a little over twice the maximum frequency in the frequency band. Alternatively, the Band-Pass Mode can be selected as shown in Figure 10c. The band-pass filter removes unwanted signals from dc to just below  $f_{\rm CLKIN}/64$ . Rather than outputting data at  $f_{\rm CLKIN}/16$ , the output of the band-pass filter is sampled at  $f_{\rm CLKIN}/32$ . This effectively translates the wanted band to a maximum frequency of a little less than  $f_{\rm CLKIN}/64$ , as shown in Figure 10d. Halving the output data rate reduces the workload of any following signal processor and also allows a lower serial clock rate to be used.

Figure 10. Band-Pass Operation

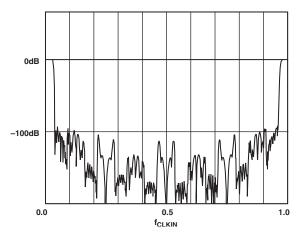

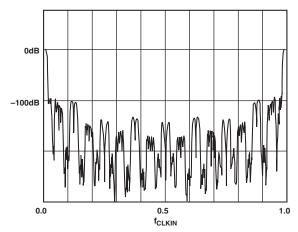

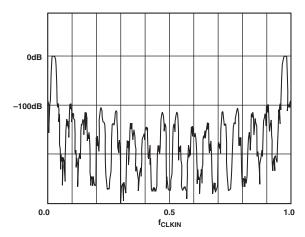

The frequency response of the three digital filter operating modes is shown in Figures 11a, 11b, and 11c.

Figure 11a. Low-Pass Filter Decimate by 16

Figure 11b. Low-Pass Filter Decimate by 32

Figure 11c. Band-Pass Filter Decimate by 32

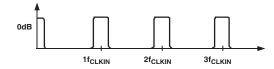

Figure 12a shows the frequency response of the digital filter in both Low-Pass and Band-Pass Modes. Due to the sampling nature of the converter, the pass-band response is repeated about the input sampling frequency,  $f_{\rm CLKIN}$ , and at integer multiples of  $f_{\rm CLKIN}$ . Out-of-band noise or signals coincident with any of the filter images are aliased down to the pass band. However, due to the AD7723's high oversampling ratio, these bands occupy only a small fraction of the spectrum, and most broadband noise is attenuated by at least 90 dB. In addition, as shown in Figure 12b, with even a low order filter, there is significant attenuation at the first image frequency. This contrasts with a normal Nyquist rate converter where a very high order antialias filter is required to allow most of the bandwidth to be used while ensuring sufficient attenuation at multiples of  $f_{\rm CLKIN}$ .

Figure 12a. Digital Filter Frequency Response

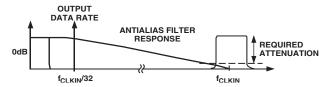

Figure 12b. Frequency Response of Antialias Filter

–16– REV. A

### **APPLYING THE AD7723**

### **Analog Input Range**

The AD7723 has differential inputs to provide common-mode noise rejection. In Unipolar Mode, the analog input range is 0 to  $8/5 \times V_{REF2}$ , while in Bipolar Mode the analog input range is  $\pm 4/5 \times V_{REF2}$ . The output code is two's complement binary in both modes with 1 LSB = 61  $\mu$ V. The ideal input/output transfer characteristics for the two modes are shown in Figure 13. In both modes, the absolute voltage on each input must remain within the supply range AGND to AV<sub>DD</sub>. The Bipolar Mode allows either single-ended or complementary input signals.

Figure 13. Bipolar (Unipolar) Mode Transfer Function

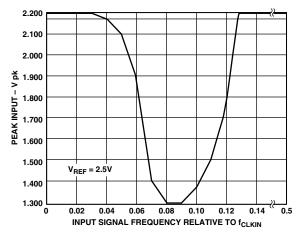

The AD7723 will accept full-scale in-band signals. However, large scale out of band signals can overload the modulator inputs. Figure 14 shows the maximum input signal level as a function of frequency. A minimal single-pole RC antialias filter set to  $f_{\rm CLKIN}/24$  will allow full-scale input signals over the entire frequency spectrum.

Figure 14. Peak Input Signal Level vs. Signal Frequency

### **Analog Input**

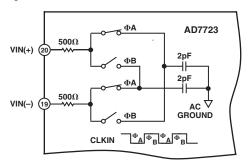

The analog input of the AD7723 uses a switched capacitor technique to sample the input signal. For the purpose of driving the AD7723, an equivalent circuit of the analog inputs is shown in Figure 15. For each half clock cycle, two highly linear sampling capacitors are switched to both inputs, converting the input signal into an equivalent sampled charge. A signal source driving the analog inputs must be able to source this charge

while also settling to the required accuracy by the end of each half-clock phase.

Figure 15. Analog Input Equivalent Circuit

### **Driving the Analog Inputs**

To interface the signal source to the AD7723, at least one op amp will generally be required. Choice of op amp will be critical to achieving the full performance of the AD7723. The op amp not only has to recover from the transient loads that the ADC imposes on it but must also have good distortion characteristics and very low input noise. Resistors in the signal path will also add to the overall thermal noise floor, necessitating the choice of low value resistors.

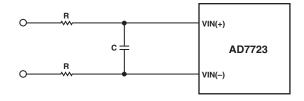

Placing an RC filter between the drive source and the ADC inputs, as shown in Figure 16, has a number of beneficial affects. Transients on the op amp outputs are significantly reduced since the external capacitor now supplies the instantaneous charge required when the sampling capacitors are switched to the ADC input pins and input circuit noise at the sample images is now significantly attenuated, resulting in improved overall SNR. The external resistor serves to isolate the external capacitor from the ADC output, thus improving op amp stability while also isolating the op amp output from any remaining transients on the capacitor. By experimenting with different filter values, the optimum performance can be achieved for each application. As a guideline, the RC time constant  $(R \times C)$  should be less than a quarter of the clock period to avoid nonlinear currents from the ADC inputs being stored on the external capacitor and degrading distortion. This restriction means that this filter cannot form the main antialias filter for the ADC.

Figure 16. Input RC Network

With the Unipolar Input Mode selected, just one op amp is required to buffer single-ended input signals. However, driving the AD7723 with complementary signals and with the bipolar input range selected has some distinct advantages: even order harmonics in both the drive circuits and the AD7723 front end are attenuated and the peak-to-peak input signal range on both inputs is halved. Halving the input signal range allows some op amps to be powered from the same supplies as the AD7723. Although a complementary driver will require the use of two op amps per ADC, it may avoid the need to generate additional supplies just for these op amps.

REV. A -17-

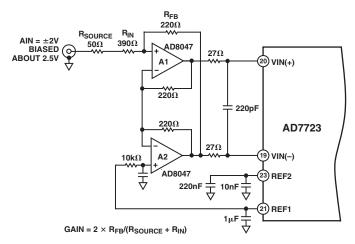

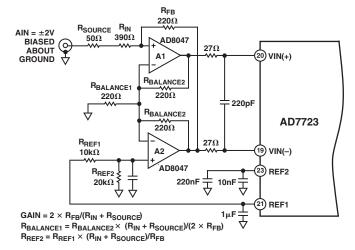

Figures 17 and 18 show two such circuits for driving the AD7723. Figure 17 is intended for use when the input signal is biased about 2.5 V, while Figure 18 is used when the input signal is biased about ground. While both circuits convert the input signal into a complementary signal, the circuit in Figure 18 also level shifts the signal so that both outputs are biased about 2.5 V.

Suitable op amps include the AD8047, AD8044, AD8041, and its dual equivalent, the AD8042. The AD8047 has lower input noise than the AD8041/AD8042 but has to be supplied from a +7.5 V/-2.5 V supply. The AD8041/AD8042 will typically degrade SNR from 90 dB to 88 dB but can be powered from the same single 5 V supply as the AD7723.

Figure 17. Single-Ended-to-Differential Input Circuit for Bipolar Mode Operation (Analog Input Biased About 2.5 V)

Figure 18. Single-Ended-to-Differential Input Circuit for Bipolar Mode Operation (Analog Input Biased About Ground)

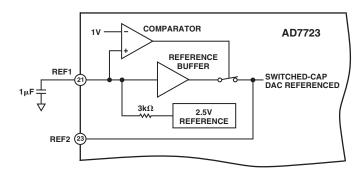

### Applying the Reference

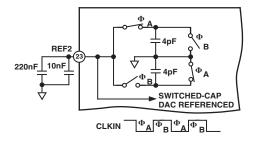

The reference circuitry used in the AD7723 includes an on-chip 2.5 V band-gap reference and a reference buffer circuit. The block diagram of the reference circuit is shown in Figure 19. The internal reference voltage is connected to REF1 through a 3 k $\Omega$  resistor and is internally buffered to drive the analog modulator's

switched cap DAC (REF2). When using the internal reference, a  $1 \mu F$  capacitor is required between REF1 and AGND to decouple the band-gap noise. If the internal reference is required to bias external circuits, use an external precision op amp to buffer REF1.

Figure 19. Reference Circuit Block Diagram

Where gain error or gain error drift requires the use of an external reference, the reference buffer in Figure 19 can be turned off by grounding the REF1 Pin and the external reference can be applied directly to REF2 Pin. The AD7723 will accept an external reference voltage between 1.2 V to 3.15 V. By applying a 3 V rather than a 2.5 V reference, SNR is typically improved by about 1 dB. Where the output common-mode range of the amplifier driving the inputs is restricted, the full-scale input signal span can be reduced by applying a lower than 2.5 V reference. For example, a 1.25 V reference would make the bipolar input span  $\pm 1$  V but would degrade SNR.

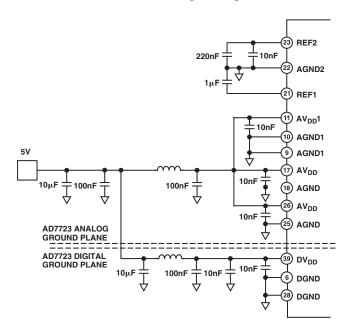

In all cases, since the REF2 voltage connects to the analog modulator, a 220 nF and 10 nF capacitor must connect directly from REF2 to AGND. The external capacitor provides the charge required for the dynamic load presented at the REF2 Pin (see Figure 20).

Figure 20. REF2 Equivalent Input Circuit

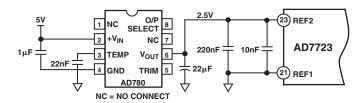

The AD780 is ideal to use as an external reference with the AD7723. Figure 21 shows a suggested connection diagram. Grounding Pin 8 on the AD780 selects the 3 V output mode.

Figure 21. External Reference Circuit Connection

–18– REV. A

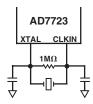

### **Clock Generation**

The AD7723 contains an oscillator circuit to allow a crystal or an external clock signal to generate the master clock for the ADC. The connection diagram for use with a crystal is shown in Figure 22. Consult the manufacturer's recommendation for the load capacitors. To enable the oscillator circuit on board the AD7723, XTAL\_OFF should be tied low.

Figure 22. Crystal Oscillator Connection

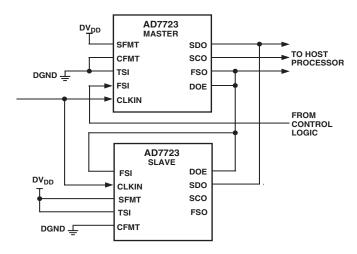

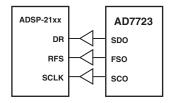

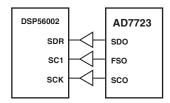

When an external clock source is being used, the internal oscillator circuit can be disabled by tying XTAL\_OFF high. A low phase noise clock should be used to generate the ADC sampling clock because sampling clock jitter effectively modulates the input signal and raises the noise floor. The sampling clock generator should be isolated from noisy digital circuits, grounded, and heavily decoupled to the analog ground plane.