82S12-F.N • 82S112-F.N

#### DESCRIPTION

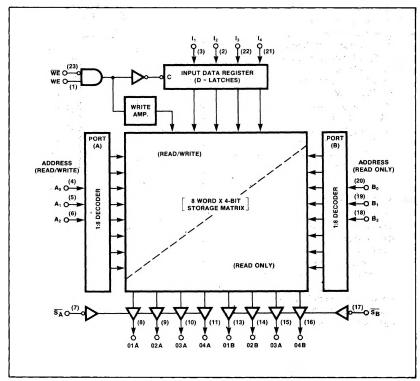

Data is stored in a single storage matrix which is addressed via 2 independent sets of address inputs, designated respectively as Port A and Port B.

Data can be read from memory via either Port A or B, through their respective output sets. However, input data (latched on the leading edge of write enable in the input data latches) is written only in memory locations specified by the address on Port A, regardless of Port B.

When both Port addresses are equal, data from the same location can be read in either or both Port output sets by means of output select lines  $S_A$  and  $S_B$ . During Write, new data stored in memory is immediately transferred on both Port output sets.

When both Port addresses are different, 2 different locations can be simultaneously read from memory. It is also possible to simultaneously read through Port B while writing new input data through Port A by utilizing the "A<sub>N</sub>" address to specify the location of the word to be written, and the "B<sub>N</sub>" address to specify the word to be read.

Both devices are ideally suited for high speed accumulator and buffer memories, and can be readily expanded to form larger arrays by means of their output select and write enable lines.

Both the 82S12 and 82S112 are available over the limited temperature range of +10° C to +75° C. Over this temperature range, specify N82S12/82S112F,N.

#### **FEATURES**

- Address access time: 40ns max

- Write cycle time: 65ns max

- Power dissipation: 8.5mW/bit typ

- Input loading: -250μA max

- On-chip address decoding

- Output options: 82S12 Open collector 82S112 Tri-state

- Non-inverting outputs

- Input data latches

- Two write enable lines

- Separate output enable lines

- · Output follows data input during write

- TTL compatible

## **APPLICATIONS**

- Buffer memory

- Accumulator register

- Data routing/shifting

- ALU control

- Multiprocessor memory management

- Bandwidth increase by multi-operand fetch

- Communication controllers

- I/O data packing/unpacking

- Large FIFO memories

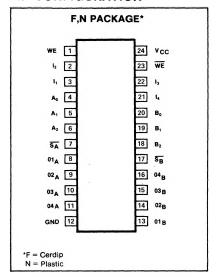

#### PIN CONFIGURATION

#### TRUTH TABLE

|          |    |    | }   |    |    | PORT    | 82S12          |                | 825            | 112               |

|----------|----|----|-----|----|----|---------|----------------|----------------|----------------|-------------------|

| MODE     | WE | WE | IN  | SA | SB | ADDRESS | (ON)A          | (ON)B          | (ON)A          | (ON)B             |

| Disabled |    |    |     | 1  | 1  | Х       | 1              | 1              | Hi-Z           | Hi-Z              |

|          | 0  | x  |     | 0  | 1  |         | Stored<br>Data | 1              | Stored<br>Data | Hi-Z              |

| Read     |    | r  | x   | 1  | 0  | A = B   | 1              | Stored<br>Data | Hi-Z           | Stored<br>Data    |

|          | x  |    |     | 0  | 0  |         | Stored<br>Data | Stored<br>Data | Stored<br>Data | Stored<br>Data    |

|          |    | 1  |     | 0  | 1  |         | [AN]           | 1              | [AN]           | Hi-Z              |

|          | l  |    |     | 1  | 0  | A≠B     | 1              | [BN]           | Hi-Z           | (BN)              |

|          |    |    | Ĺ   | 0  | 0  | İ       | [AN]           | (BN)           | [AN]           | [B <sub>N</sub> ] |

|          |    |    |     | 1  | 1  |         | 1              | 1              | Hi-Z           | Hi-Z              |

| Write    | ł  |    |     | 0  | 1  | A = B   | IN             | 1              | IN             | Hi-Z              |

|          | 1  | 0  | 1/0 | 1  | 0  |         | 1              | IN             | Hi-Z           | IN                |

|          |    |    |     | 0  | 0  |         | IN             | IN             | IN             | IN                |

|          | l  |    |     | 1  | 1  |         | 1              | 1              | Hi-Z           | Hi-Z              |

|          | ł  |    | }   | 0  | 1  | A≠B     | IN             | 1              | IN             | Hi-Z              |

|          | 1  |    | l   | 1  | 0  | l       | 1              | [BN]           | Hi-Z           | [B <sub>N</sub> ] |

|          | (  | 1  | i   | lo | Ιo | 1       | l IN           | гВит           | IN             | (BNI              |

X = Don't care

<sup>| ] =</sup> Contents of

# **BLOCK DIAGRAM**

# **ABSOLUTE MAXIMUM RATINGS**

| P    | ARAMETER1          | RATING      | UNIT  |  |

|------|--------------------|-------------|-------|--|

| Vcc  | Supply voltage     | +7          | Vdc   |  |

| VIN  | Input voltage      | +5.5        | Vdc   |  |

|      | Output voltage     |             | Vdc   |  |

| Voh  | High (82S12)       | +5.5        | o     |  |

| Vo   | Off-state (82S112) | -+5.5       | 11.11 |  |

| lin  | Input current      | ±30         | mA    |  |

| lout | Output current     | +100        | mA    |  |

|      | Temperature range  |             | •c    |  |

| TA   | Operating          | 0 to +75    | -     |  |

| TSTG | Storage            | -65 to +150 |       |  |

#### **DC ELECTRICAL CHARACTERISTICS** $+10^{\circ}$ C $\leq$ T<sub>A</sub> $\leq$ 75°C, 4.75V $\leq$ V<sub>CC</sub> $\leq$ 5.25V

|                   |                                                                                                   | TEAT COMPLETIONS                                                                                                                     | 82S12 |                  |              | 82S112 |                  |                  |                |

|-------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------|------------------|--------------|--------|------------------|------------------|----------------|

| P#                | ARAMETER1                                                                                         | TEST CONDITIONS                                                                                                                      | Min   | Typ <sup>2</sup> | Max          | Min    | Typ <sup>2</sup> | Max              | UNIT           |

| VIH<br>VIL<br>VIC | Input voltage<br>High <sup>1</sup><br>Low <sup>1</sup><br>Clamp <sup>1,3</sup>                    | V <sub>CC</sub> = 5.25V<br>V <sub>CC</sub> = 4.75V<br>V <sub>CC</sub> = 4.75V, I <sub>IN</sub> = -18mA                               | 2     | -0.8             | 0.85<br>-1.2 | 2      | -0.8             | 0.85<br>-1.2     | ٧              |

| Vон<br>Vol        | Output voltage<br>High1,4<br>Low1,5                                                               | $V_{CC} = 4.75V$ $I_{OH} = -2mA$ $I_{OL} = 9.6mA$                                                                                    |       | 0.35             | 0.45         | 2.4    | 0.35             | 0.45             | ٧              |

| Iн<br>IIL         | Input current<br>High<br>Low                                                                      | V <sub>IN</sub> = 5.5V<br>V <sub>IN</sub> = 0.45V                                                                                    |       | 1<br>-10         | 25<br>-250   |        | 1<br>-10         | 25<br>-250       | μΑ             |

| lolk<br>lo(off)   | Output current<br>Leakage <sup>6</sup><br>Hi-Z state <sup>6</sup><br>Short circuit <sup>3,7</sup> | V <sub>CC</sub> = 5.25V<br>V <sub>OUT</sub> = 5.25V<br>V <sub>OUT</sub> = 5.25V<br>V <sub>OUT</sub> = 0.45V<br>V <sub>OUT</sub> = 0V |       | 1                | 40           | -20    | 1 -1             | 40<br>-40<br>-70 | μA<br>μA<br>mA |

| Icc               | Vcc supply current8                                                                               | V <sub>CC</sub> = 5.25V                                                                                                              |       | 110              | 160          |        | 110              | 160              | mA             |

| Cin<br>Vout       | Capacitance<br>Input<br>Output                                                                    | $V_{CC} = 5.0V$ $V_{IN} = 2.0V$ $V_{OUT} = 2.0V$                                                                                     |       | 5<br>8           |              |        | 5<br>8           |                  | pF             |

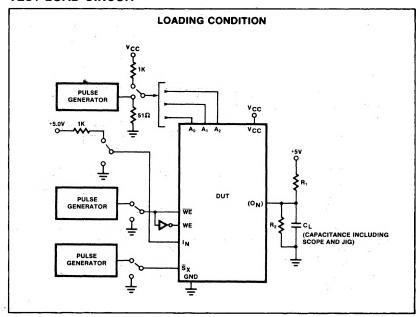

### AC ELECTRICAL CHARACTERISTICS $+10^{\circ}$ C $\leq$ T<sub>A</sub> $\leq$ +75° C, 4.75V $\leq$ V<sub>CC</sub> $\leq$ 5.25V, R<sub>1</sub> = 470 $\Omega$ , R<sub>2</sub> = 1k $\Omega$ , C<sub>L</sub> = 30pF

|                 |                                                |                  |                          | LIMITS   |                  |                  |      |  |

|-----------------|------------------------------------------------|------------------|--------------------------|----------|------------------|------------------|------|--|

| l               | PARAMETER                                      | то               | FROM                     | Min      | Typ <sup>2</sup> | <b>Max</b> 40 30 | UNIT |  |

| TAA<br>Tse      | Access time<br>Address<br>Port select          | Output<br>Output | Address<br>Output enable |          |                  |                  | ns   |  |

| T <sub>SD</sub> | Disable time<br>Port deselect                  | Output           | Output enable            |          |                  | 30               | ns   |  |

| Two             | Valid time                                     | Output           | Write enable             |          |                  | 40               | ns   |  |

| Twsa<br>Twha    | Setup and hold time<br>Setup time<br>Hold time | Write enable     | Address                  | 15<br>5  | 10<br>0          |                  | ns   |  |

| Twsd<br>Twhd    | Setup time<br>Hold time                        | Write enable     | Data in                  | 15<br>10 |                  |                  |      |  |

| Twp             | Pulse width<br>Write enable                    | *                |                          | 45       |                  |                  | ns   |  |

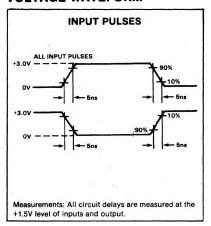

- 1. All voltage values are with respect to network ground terminal. 2. All typical values are at  $V_{CC}=5V,\,T_A=25^{\circ}C.$

- 3. Test one at the time.

- Measured with V<sub>IL</sub> applied to S<sub>X</sub> and a logic high stored.

- 5. Measured with a logic low stored. Output sink current is supplied through a resistor to Vcc.

- 6. Measured with VIH applied to Sx.

- 7. Duration of short circuit should not exceed 1 second.

- 8. Icc is measured with all inputs at 4.5V and the outputs open.

# **TEST LOAD CIRCUIT**

# **VOLTAGE WAVEFORM**

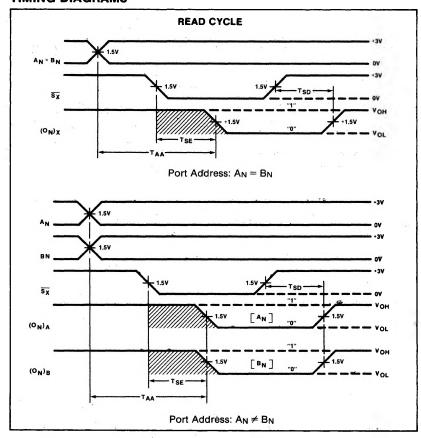

#### **TIMING DIAGRAMS**

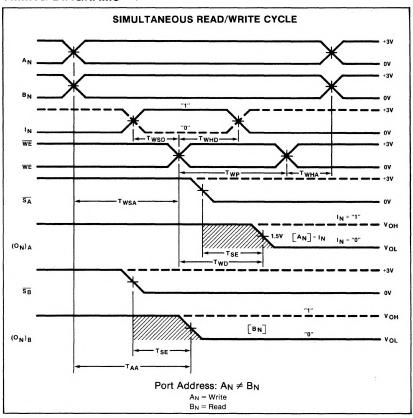

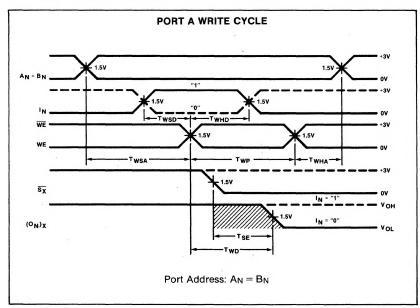

#### TIMING DIAGRAMS (Cont'd)

# MEMORY TIMING DEFINITIONS

- TSE Delay between beginning of Output Enable low (with Address valid) and when Data Output becomes valid.

- T<sub>SD</sub> Delay between when Output Enable becomes high and Data Output is in Hi-Z or high state.

- TAA Delay between beginning of valid Address (with Output Enable low) and when Data Output becomes valid.

- TWHD Required delay between end of Write Enable pulse and end of valid Input Data.

- TWP Width of Write Enable pulse.

TWSA Required delay between beginning of valid Address and begin-

- Twsp ning of Write Enable pulse.

Required delay between beginning of valid Data Input and end of Write Enable pulse.

- TwD Delay between beginning of Write Enable pulse and when Data Output reflects the Data Input.

- TWHA Required delay between end of Write Enable pulse and end of valid Address.